单片机的IO引脚结构

- 格式:ppt

- 大小:445.00 KB

- 文档页数:24

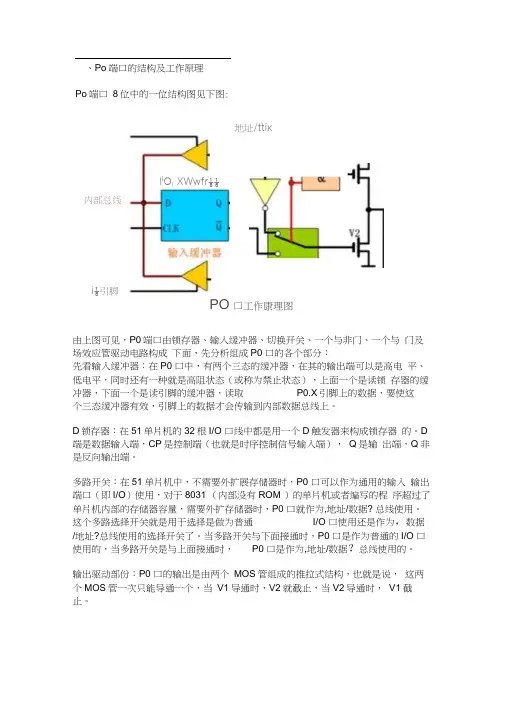

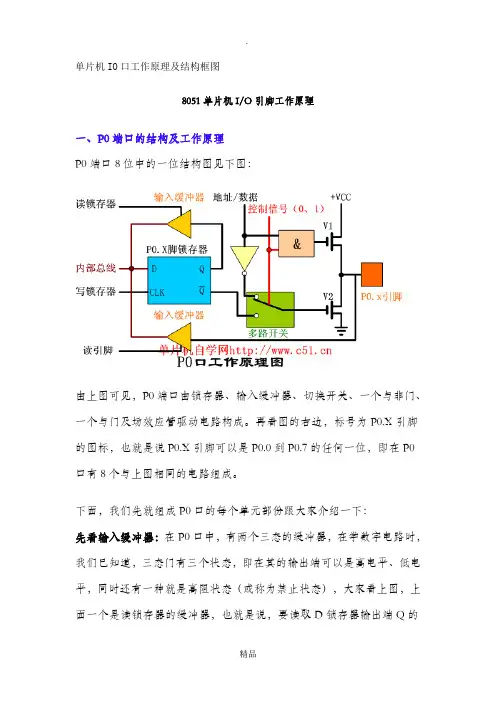

51单片机I/O引脚IO口工作原理一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q 及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

单片机IO口结构及工作原理单片机(Microcontroller Unit,MCU)的IO口是指可用来输入输出数据的引脚,在单片机系统中具有重要的作用。

本文将详细介绍单片机IO口的结构和工作原理。

一、单片机IO口的结构单片机的所有IO口都可以看作是一个通用的数字引脚。

常用的单片机IO口主要包括输入端和输出端两个部分。

1.输入端:单片机IO口的输入端包含一个输入缓冲区,用于对输入信号进行缓冲和驱动。

输入缓冲区通常由一个高阻抗的MOSFET器件构成,可以对输入信号进行放大和处理。

输入端能够接收来自外界的高电平和低电平信号,通过输入缓冲区将信号传递给单片机的内部电路。

2.输出端:单片机IO口的输出端是由一个输出缓冲器和驱动电路构成的。

输出缓冲器一般由一个强驱动能力的MOSFET器件构成,可以对输出信号进行放大和驱动。

输出端能够将单片机内部的数据通过输出缓冲器传递给外部电路,形成相应的高电平或低电平电压信号。

3. 接口电路:为了提高单片机IO口的抗干扰能力和适应外部电路的需求,通常在IO口的输入和输出端之间设置了一些接口电路,如上拉电阻(Pull-Up Resistor)和下拉电阻(Pull-Down Resistor)。

上拉电阻和下拉电阻可以对输入或输出信号进行稳定的电平处理和电流限制,使得单片机的IO口在复杂的电路环境中能够正常工作。

二、单片机IO口的工作原理单片机的IO口工作原理主要包括输入和输出两种模式。

1.输入模式:当IO口被设定为输入模式时,输入信号可以通过外部电路或者内部电路输入到IO口,并经过输入缓冲器进行电平放大和处理。

在输入模式下,可以通过软件对IO口进行设置,使其能够读取外部电路的电平状态。

通过输入模式,单片机可以读取外部的开关状态、传感器的输出以及其他的输入信号,实现数据的采集和处理。

2.输出模式:当IO口被设定为输出模式时,单片机可以将内部处理的数据通过输出缓冲器驱动外部电路。

单片机 ------stc89c52引脚说明STC89C52是一款常用的单片机芯片,其引脚功能十分重要。

本文将对STC89C52的引脚进行详细说明,帮助读者更好地了解和使用这款单片机。

1. P0口(引脚1~引脚8),P0口是STC89C52的8位IO口,可以配置为输入口或输出口。

在默认情况下,P0口为输出口。

用户可以通过软件控制来配置P0口的工作模式。

2. P1口(引脚10~引脚17),P1口也是8位IO口,同样可以配置为输入口或输出口。

在默认情况下,P1口为输出口。

用户可以通过软件控制来配置P1口的工作模式。

3. P2口(引脚21~引脚28),P2口是8位IO口,同样可以配置为输入口或输出口。

在默认情况下,P2口为输出口。

用户可以通过软件控制来配置P2口的工作模式。

4. P3口(引脚10~引脚17),P3口也是8位IO口,同样可以配置为输入口或输出口。

在默认情况下,P3口为输出口。

用户可以通过软件控制来配置P3口的工作模式。

5. RST引脚(引脚9),RST引脚是复位引脚,当RST引脚为低电平时,单片机将被复位。

用户可以通过外部电路来控制RST引脚的复位功能。

6. ALE/PROG引脚(引脚30),ALE/PROG引脚是地址锁存器使能引脚,当ALE/PROG引脚为高电平时,地址锁存器有效。

当ALE/PROG引脚为低电平时,地址锁存器无效。

7. PSEN引脚(引脚29),PSEN引脚是程序存储器使能引脚,当PSEN引脚为低电平时,程序存储器有效。

当PSEN引脚为高电平时,程序存储器无效。

8. EA/VPP引脚(引脚31),EA/VPP引脚是外部访问使能引脚,当EA/VPP引脚为高电平时,单片机从外部程序存储器中取指令。

当EA/VPP引脚为低电平时,单片机从内部程序存储器中取指令。

9. XTAL1引脚(引脚18)和XTAL2引脚(引脚19),XTAL1和XTAL2引脚是晶体振荡引脚,用户可以通过外部晶振来提供时钟信号。

单片机的IO引脚结构单片机(MCU)的IO引脚结构是指单片机芯片上的输入输出引脚的组织结构和功能。

单片机的引脚结构通常由内部逻辑电路和外部物理引脚组成,它们通过输入输出方式与外部电路或器件进行信息交互。

下面将对单片机的IO引脚结构进行详细描述。

一、输入输出引脚组织结构单片机的输入输出引脚通常由三个主要组成部分构成:引脚功能区、输入输出缓冲区和引脚控制寄存器。

1.引脚功能区:是指单片机芯片上与外部引脚相连接的内部逻辑电路部分。

该电路决定了引脚的功能,包括输入、输出、模拟输入、模拟输出、复用功能等。

2.输入输出缓冲区:是单片机芯片内部的电路,用于将引脚与CPU内部总线之间的电平信号进行相互转换。

输入缓冲器用于输入引脚,将外部电平信号转换为内部电平信号;输出缓冲器用于输出引脚,将内部电平信号转换为外部电平信号。

3.引脚控制寄存器:是用于配置和控制引脚的寄存器。

它可以设置引脚的输入/输出模式、上拉/下拉电阻、中断使能等功能。

通过对引脚控制寄存器的设置,可以实现对引脚功能和特性的灵活配置。

二、引脚的功能和特性1.输入功能:可以将外部电平信号输入到单片机内部。

输入引脚通常具有输入缓冲器,用于接收外部电平信号。

可以通过设置引脚控制寄存器来配置输入功能的参数,如输入模式、上拉/下拉电阻、中断使能等。

2.输出功能:可以将单片机内部的电平信号输出到外部。

输出引脚通常具有输出缓冲器,用于将内部电平信号转换为外部电平信号。

可以通过设置引脚控制寄存器来配置输出功能的参数,如输出模式、上拉/下拉电阻等。

3.模拟输入功能:部分单片机的引脚具有模拟输入功能,可以接收模拟电压信号并转换为数字信号输入到单片机内部。

此类引脚通常具有模拟输入通道和采样电路,可以支持模拟信号的采样和转换。

4.模拟输出功能:部分单片机的引脚具有模拟输出功能,可以将单片机内部的数字信号转换为模拟电压信号输出到外部。

此类引脚通常具有数字模拟转换器(DAC)和输出缓冲器,可以实现数字信号到模拟信号的转换。

、Po端口的结构及工作原理Po端口8位中的一位结构图见下图:地址∕ttiκI i O i XWwfr⅛⅛内部总线i⅛引脚PO 口工作康理图由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成下面,先分析组成P0 口的各个部分:先看输入缓冲器:在P0 口中,有两个三态的缓冲器,在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),上面一个是读锁存器的缓冲器,下面一个是读引脚的缓冲器,读取P0.X引脚上的数据,要使这个三态缓冲器有效,引脚上的数据才会传输到内部数据总线上。

D锁存器:在51单片机的32根I/O 口线中都是用一个D触发器来构成锁存器的。

D 端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

多路开关:在51单片机中,不需要外扩展存储器时,P0 口可以作为通用的输入输出端口(即I/O)使用,对于8031 (内部没有ROM )的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0 口就作为,地址/数据? 总线使用。

这个多路选择开关就是用于选择是做为普通I/O 口使用还是作为,数据/地址?总线使用的选择开关了。

当多路开关与下面接通时,P0 口是作为普通的I/O 口使用的,当多路开关是与上面接通时,P0 口是作为,地址/数据?总线使用的。

输出驱动部份:P0 口的输出是由两个MOS管组成的推拉式结构,也就是说,这两个MOS管一次只能导通一个,当V1导通时,V2就截止,当V2导通时,V1截止。

Po 口作为I/O端口使用时,多路开关的控制信号为0 (低电平),V1管截止, 多路开关是与锁存器的Q非端相接的(即P0 口作为I/O 口线使用)。

作为地址/数据线使用时,多路开关的控制信号为1,V1管由地址/数据线决定,多路开关与地址/数据线连接。

输出过程:1、I/O输出工作过程:当写锁存器信号CP有效,数据总线的信号→锁存器的输入端D→锁存器的反向输出Q非端→多路开关→V2管的栅极→V2的漏极到输出端P0.X。

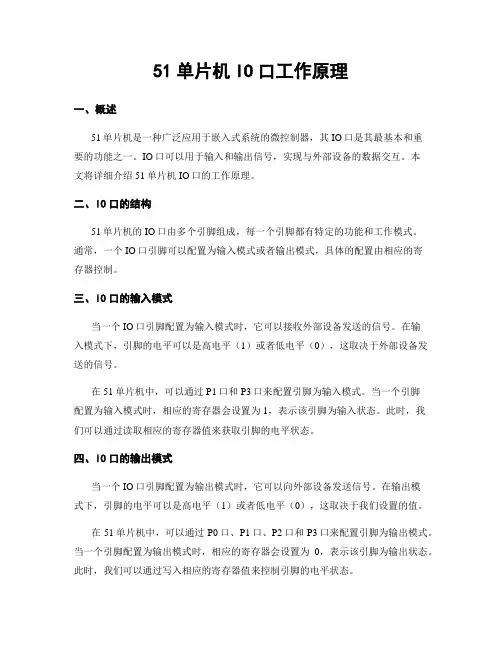

51单片机IO口工作原理一、概述51单片机是一种广泛应用于嵌入式系统的微控制器,其IO口是其最基本和重要的功能之一。

IO口可以用于输入和输出信号,实现与外部设备的数据交互。

本文将详细介绍51单片机IO口的工作原理。

二、IO口的结构51单片机的IO口由多个引脚组成,每一个引脚都有特定的功能和工作模式。

通常,一个IO口引脚可以配置为输入模式或者输出模式,具体的配置由相应的寄存器控制。

三、IO口的输入模式当一个IO口引脚配置为输入模式时,它可以接收外部设备发送的信号。

在输入模式下,引脚的电平可以是高电平(1)或者低电平(0),这取决于外部设备发送的信号。

在51单片机中,可以通过P1口和P3口来配置引脚为输入模式。

当一个引脚配置为输入模式时,相应的寄存器会设置为1,表示该引脚为输入状态。

此时,我们可以通过读取相应的寄存器值来获取引脚的电平状态。

四、IO口的输出模式当一个IO口引脚配置为输出模式时,它可以向外部设备发送信号。

在输出模式下,引脚的电平可以是高电平(1)或者低电平(0),这取决于我们设置的值。

在51单片机中,可以通过P0口、P1口、P2口和P3口来配置引脚为输出模式。

当一个引脚配置为输出模式时,相应的寄存器会设置为0,表示该引脚为输出状态。

此时,我们可以通过写入相应的寄存器值来控制引脚的电平状态。

五、IO口的工作原理在51单片机中,IO口的工作原理是通过寄存器的读写操作来实现的。

通过读取或者写入相应的寄存器值,我们可以配置引脚的工作模式和控制引脚的电平状态。

对于输入模式,我们可以通过读取相应的寄存器值来获取引脚的电平状态。

通过读取P1口和P3口的寄存器值,我们可以判断引脚的电平是高电平还是低电平。

对于输出模式,我们可以通过写入相应的寄存器值来控制引脚的电平状态。

通过写入P0口、P1口、P2口和P3口的寄存器值,我们可以将引脚的电平设置为高电平或者低电平。

六、IO口的应用场景51单片机的IO口广泛应用于各种嵌入式系统中,如电子设备、家用电器、工业控制等。

单片机引脚分类引言:单片机是一种封装了中央处理器、内存和各种输入输出接口的集成电路芯片。

它广泛应用于数字电子技术领域,通过引脚与外界设备进行通信和控制。

本文将对单片机引脚进行分类,以帮助读者更好地理解和应用单片机技术。

一、引脚分类的重要性在接触单片机之前,了解引脚分类的重要性是必要的。

单片机引脚按照其功能和用途分类,有助于我们理解单片机芯片的结构和工作原理,便于正确连接外部元器件和进行电路设计。

二、按照电源引脚分类1. Vcc引脚:Vcc引脚是单片机的电源引脚,通常接5V或3.3V的直流电源。

它负责为单片机芯片提供稳定的电压供电,确保单片机正常运行。

2. GND引脚:GND引脚是单片机的地引脚,用于形成电路的参考点。

它与Vcc 引脚相连,构成了电源回路,确保电路的工作正常。

三、按照输入输出引脚分类1. 输入引脚:输入引脚用于接收外部信号或数据,将其输入至单片机内部进行处理。

例如,用来接收传感器的信号或外部开关的状态。

2. 输出引脚:输出引脚用于将单片机内部处理的信号或数据输出至外部设备,控制其工作状态。

例如,控制LED灯的亮灭或控制电机的运转。

四、按照功能分类1. 普通IO引脚:普通IO引脚既可以作为输入引脚,也可以作为输出引脚。

它们的功能可以通过程序控制来切换。

2. 定时器/计数器引脚:定时器/计数器引脚用于计数外部脉冲信号,实现计时或计数功能。

它们可以用来测量时间间隔或控制脉冲输出。

3. 中断引脚:中断引脚用于与外部设备进行中断交互。

当外部设备触发中断条件时,单片机会立即暂停当前操作,转而处理中断程序。

4. 串口通信引脚:串口通信引脚用于实现单片机与计算机或其他外部设备之间的数据传输。

它们可以将数据转换成串行格式进行传输。

5. 脉宽调制引脚:脉宽调制引脚用于产生特定脉冲波形。

通过改变脉冲的高电平时间和低电平时间的比例,可以调整输出信号的频率和占空比。

六、总结单片机引脚的分类是了解和应用单片机技术的基础。

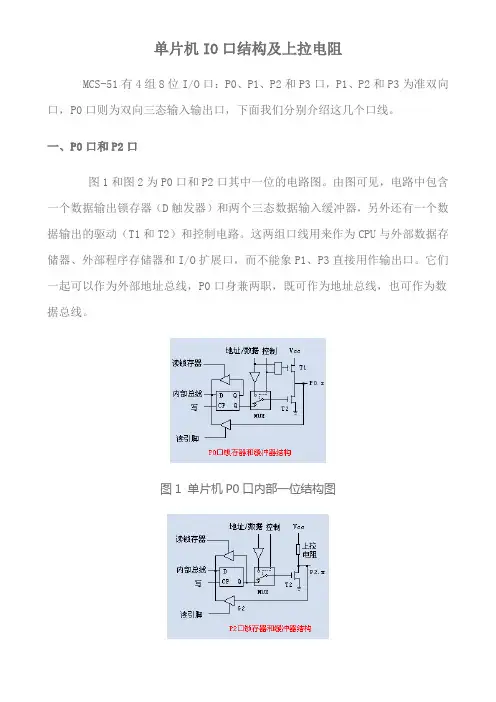

单片机IO口结构及上拉电阻MCS-51有4组8位I/O口:P0、P1、P2和P3口,P1、P2和P3为准双向口,P0口则为双向三态输入输出口,下面我们分别介绍这几个口线。

一、P0口和P2口图1和图2为P0口和P2口其中一位的电路图。

由图可见,电路中包含一个数据输出锁存器(D触发器)和两个三态数据输入缓冲器,另外还有一个数据输出的驱动(T1和T2)和控制电路。

这两组口线用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口,而不能象P1、P3直接用作输出口。

它们一起可以作为外部地址总线,P0口身兼两职,既可作为地址总线,也可作为数据总线。

图1 单片机P0口内部一位结构图图2 单片机P0口内部一位结构图P2口作为外部数据存储器或程序存储器的地址总线的高8位输出口AB8-AB15,P0口由ALE选通作为地址总线的低8位输出口AB0-AB7。

外部的程序存储器由PSEN信号选通,数据存储器则由WR和RD读写信号选通,因为2^16=64k,所以MCS-51最大可外接64kB的程序存储器和数据存储器。

二、P1口图3为P1口其中一位的电路图,P1口为8位准双向口,每一位均可单独定义为输入或输出口,当作为输入口时,1写入锁存器,Q(非)=0,T2截止,内上拉电阻将电位拉至"1",此时该口输出为1,当0写入锁存器,Q(非)=1,T2导通,输出则为0。

图3 单片机P2口内部一位结构图作为输入口时,锁存器置1,Q(非)=0,T2截止,此时该位既可以把外部电路拉成低电平,也可由内部上拉电阻拉成高电平,正因为这个原因,所以P1口常称为准双向口。

需要说明的是,作为输入口使用时,有两种情况:1.首先是读锁存器的内容,进行处理后再写到锁存器中,这种操作即读—修改—写操作,象JBC(逻辑判断)、CPL(取反)、INC(递增)、DEC(递减)、ANL(与逻辑)和ORL(逻辑或)指令均属于这类操作。

2.读P1口线状态时,打开三态门G2,将外部状态读入CPU。

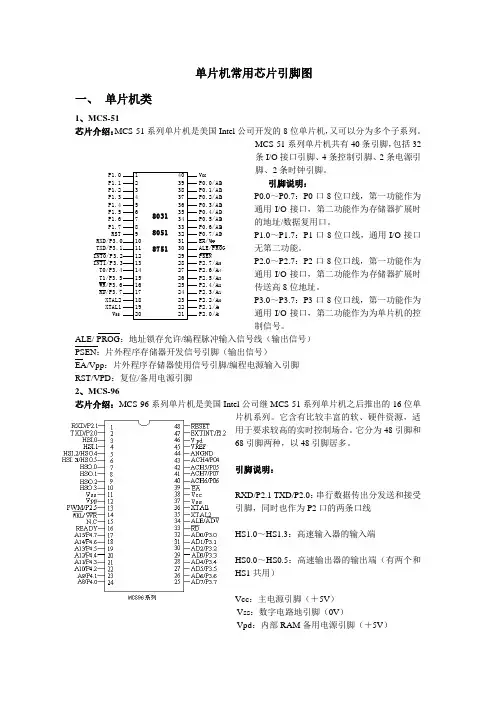

单片机常用芯片引脚图一、单片机类1、MCS-51芯片介绍:MCS-51系列单片机是美国Intel公司开发的8位单片机,又可以分为多个子系列。

MCS-51系列单片机共有40条引脚,包括32条I/O接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。

引脚说明:P0.0~P0.7:P0口8位口线,第一功能作为通用I/O接口,第二功能作为存储器扩展时的地址/数据复用口。

P1.0~P1.7:P1口8位口线,通用I/O接口无第二功能。

P2.0~P2.7:P2口8位口线,第一功能作为通用I/O接口,第二功能作为存储器扩展时传送高8位地址。

P3.0~P3.7:P3口8位口线,第一功能作为通用I/O接口,第二功能作为为单片机的控制信号。

ALE/ PROG:地址锁存允许/编程脉冲输入信号线(输出信号)PSEN:片外程序存储器开发信号引脚(输出信号)EA/Vpp:片外程序存储器使用信号引脚/编程电源输入引脚RST/VPD:复位/备用电源引脚2、MCS-96芯片介绍:MCS-96系列单片机是美国Intel公司继MCS-51系列单片机之后推出的16位单片机系列。

它含有比较丰富的软、硬件资源,适用于要求较高的实时控制场合。

它分为48引脚和68引脚两种,以48引脚居多。

引脚说明:RXD/P2.1 TXD/P2.0:串行数据传出分发送和接受引脚,同时也作为P2口的两条口线HS1.0~HS1.3:高速输入器的输入端HS0.0~HS0.5:高速输出器的输出端(有两个和HS1共用)Vcc:主电源引脚(+5V)Vss:数字电路地引脚(0V)Vpd:内部RAM备用电源引脚(+5V)RSTINT0/P3.2INT1/P3.3WR/P3.6RD/P3.7V SSV REF:A/D转换器基准电源引脚(+5V)AGND:A/D转换器参考地引脚XTAL1、XTAL2:内部振荡器反相器输入、输出端,常外接晶振。

CLKOUT:内部时钟发生器的输出引脚,提供频率位晶振频率的1/3的脉冲供外部使用。

单片机IO口工作原理及结构框图8051单片机I/O引脚工作原理一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP 没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

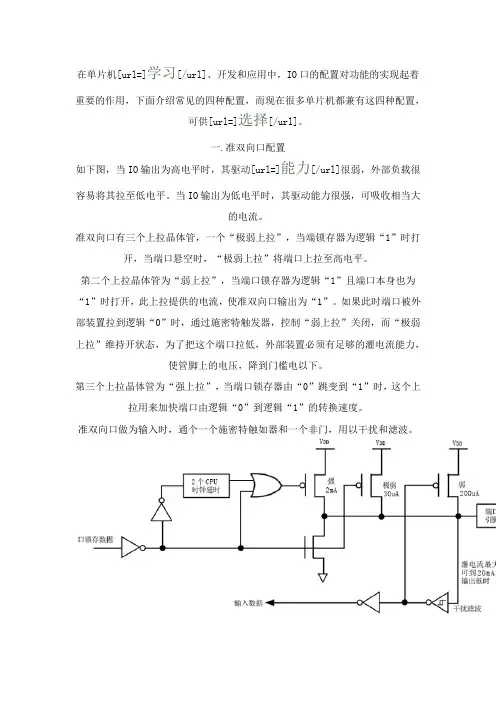

在单片机[url=]学习[/url]、开发和应用中,IO口的配置对功能的实现起着重要的作用,下面介绍常见的四种配置,而现在很多单片机都兼有这四种配置,可供[url=]选择[/url]。

一.准双向口配置如下图,当IO输出为高电平时,其驱动[url=]能力[/url]很弱,外部负载很容易将其拉至低电平。

当IO输出为低电平时,其驱动能力很强,可吸收相当大的电流。

准双向口有三个上拉晶体管,一个“极弱上拉”,当端锁存器为逻辑“1”时打开,当端口悬空时,“极弱上拉”将端口上拉至高电平。

第二个上拉晶体管为“弱上拉”,当端口锁存器为逻辑“1”且端口本身也为“1”时打开,此上拉提供的电流,使准双向口输出为“1”。

如果此时端口被外部装置拉到逻辑“0”时,通过施密特触发器,控制“弱上拉”关闭,而“极弱上拉”维持开状态,为了把这个端口拉低,外部装置必须有足够的灌电流能力,使管脚上的电压,降到门槛电以下。

第三个上拉晶体管为“强上拉”,当端口锁存器由“0”跳变到“1”时,这个上拉用来加快端口由逻辑“0”到逻辑“1”的转换速度。

准双向口做为输入时,通个一个施密特触如器和一个非门,用以干扰和滤波。

准双向口用作输入时,可对地接按键,如下图1,当然也可以去掉R1直接接按键,当按键闭合时,端口被拉至低电平,当按键松开时,端口被内部“极弱上拉”晶体管拉至高电平。

当端口作为输出时,不应对地外接LED如图形控制,这样端口的驱动能力很弱,LED只能发很微弱的光,如果要驱动LED,要采用图 3的方法,这样准双向口在输出为低时,可吸收20mA的电流,故能驱动LED。

图4的方法也可以,不过LED不发光时,端口要吸收收很大电流。

二.开漏输出配置这种配置,关闭所有上拉晶体管,只驱动下拉晶体管,下拉与准双向口下拉配置相同,因此只能输出低电平(吸收电流),和高阻状态。

不能输出高电平(输也电流)。

如果要作为逻辑输出,必须接上拉电阻到VCC。

这种配置也可以通过上图3和图4来驱动LED。

单片机引脚介绍STC89C52 单片机引脚功能介绍首先我们来认识一下51 单片机芯片的引脚图,具体功能在下面介绍。

单片机的40 个引脚大致可分为4 类:电源、时钟、控制和IO 引脚。

⒈电源⑴ VCC - 芯片电源,接+5V;当然也有3.3V 供电的芯片。

⑵ VSS - 接地端;⒉时钟XTAL1、XTAL2 - 晶体振荡电路反相输入端和输出端。

⒊控制线控制线共有4 根,⑴ ALEPROG 地址锁存允许片内EPROM 编程脉冲(旧的AT89C51 用到,最新的51 芯片可以在线编程,一条USB 线搞定单片机,下面的说明不理解的可以不用看,因为最新的51 芯片都没有了VPP 功能了。

)① ALE 功能:用来锁存P0 口送出的低8 位地址② PROG 功能:片内有EPROM 的芯片,在EPROM 编程期间,此引脚输入编程脉冲。

⑵ PSEN 外ROM 读选通信号。

⑶ RSTVPD 复位备用电源。

① RST(Reset)功能:复位信号输入端。

② VPD 功能:在Vcc 掉电情况下,接备用电源。

⑷ EAVpp 内外ROM 选择片内EPROM 编程电源。

① EA 功能:内外ROM 选择端。

② Vpp 功能:片内有EPROM 的芯片,在EPROM 编程期间,施加编程电源Vpp。

⒋ IO 线STC89C52 共有4 个8 位并行IO 端口:P0、P1、P2、P3 口,共32 个引脚。

P3 口还具有第二功能,用于特殊信号输入输出和控制信号(属控制总线)。

拿到一块芯片,想要使用它,首先必须要知道怎样连线,我们用的一块称之为STC89C52的芯片,下面我们就看一下如何给它连线。

1、电源:这当然是必不可少的了。

单片机使用的是5V 电源,其中正极接40 管脚,负极(地)接20 管脚。

2、振蒎电路:单片机是一种时序电路,必须供给脉冲信号才能正常工作,在单片机内部已集成了振荡器,使用晶体振荡器,接18、19 脚。

只要买来晶体震荡器,电容,连上就能了,按图1 接上即可。

单片机IO口结构及工作原理单片机(Microcontroller Unit,MCU)是一种集成了微处理器核心、主存储器、输入/输出端口和计时/定时器等功能部件的微型计算机系统。

它被广泛应用于各种电子设备中,如家电、汽车、工业控制等。

单片机的IO口是其中一个重要的功能部件,它负责与外部设备进行数据传输、信号输入输出等工作。

一、单片机IO口的结构单片机的IO口通常由GPIO(General Purpose Input/Output)端口组成。

GPIO是一种通用输入/输出口,具有多种工作模式的功能输入/输出,可以通过软件配置和控制来实现不同的功能。

一个GPIO引脚既可以作为输入口,也可以作为输出口。

当它作为输入口时,可以接收外部设备的输入信号,并由单片机内部进行处理和分析;当它作为输出口时,可以向外部设备发送数据信号或控制信号。

GPIO口的结构一般由以下几个部分组成:1.引脚:GPIO口与外部设备连接的接口,通常是芯片封装的金属引脚,可以引出到芯片外部的引脚脚座上。

2.输入/输出电路:GPIO口的输入/输出电路用于接收外部设备的信号或向外部设备发送信号。

对于输入电路,通常包括输入缓冲器、滤波器和电平转换器等部分;对于输出电路,通常包括输出驱动器和电平转换器等部分。

3.寄存器:GPIO口的寄存器用于存储和控制输入/输出的数据和参数。

单片机内部的软件可以通过对寄存器的读/写操作来实现对GPIO口的控制。

二、单片机IO口的工作原理1.配置GPIO口的工作模式:单片机的GPIO口通常有多种工作模式可选,如输入模式、输出模式、外部中断模式等。

在使用GPIO口之前,需要通过寄存器配置来选择所需的工作模式。

2.设置GPIO口的状态:GPIO口的状态通常分为高电平状态和低电平状态。

在输出模式下,可以通过寄存器设置GPIO口的输出值,从而控制输出的电平状态;在输入模式下,GPIO口将根据外部设备的输入信号自动判断电平状态。

单片机IO口工作原理及结构框图8051单片机I/O引脚工作原理一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP 没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

单片机的IO引脚结构单片机(Microcontroller)是一种集成了处理器核心、存储器和各种外设接口的集成电路芯片。

常见的单片机包括MCS-51系列、PIC系列、AVR系列以及ARM系列等。

每个单片机都有一组IO引脚,用于输入和输出各种信号。

IO引脚的结构可以分为三个主要部分:引脚复用器、引脚电路和IO口电路。

引脚复用器(Pin Mux)是用于配置引脚功能的部分。

一些引脚可以通过设置寄存器的值来选择不同的功能,例如作为输入引脚、输出引脚、模拟引脚或控制引脚等。

引脚复用器功能的不同,不同IO引脚的使用方式也会有所不同。

引脚电路(Pin circuitry)包括输入和输出电路。

输入电路用于将外部信号连接到引脚,以接收来自外部器件的信号。

输出电路用于将单片机内部的信号输出到外部器件。

引脚电路还包括保护电路,用于防止引脚受到静电放电或过电流等损坏。

IO口电路(IO Port)是实现IO功能的核心电路。

每个IO引脚通常都有一个对应的IO口,IO口由一个或多个寄存器组成,用于控制引脚的输入和输出。

在一些简单的单片机中,IO口只能实现基本的输入输出功能,例如控制LED灯的亮灭。

而在一些高级的单片机中,IO口具有更多的功能,可以实现更复杂的外设控制,例如串口通信、模拟信号采集、PWM输出、定时器控制等。

每个IO口通常包括一个或多个寄存器。

常见的寄存器包括数据寄存器(Data Register)、方向寄存器(Direction Register)、中断寄存器(Interrupt Register)和配置寄存器(Configuration Register)等。

数据寄存器用于存储输入和输出的数据。

当IO口为输出模式时,将数据写入数据寄存器会将该数据输出到引脚;当IO口为输入模式时,读取数据寄存器可以获取引脚上的输入数据。

方向寄存器用于设置IO口的输入输出方向。

可以通过设置方向寄存器的位值将IO口配置为输入或输出模式。

51单片机IO引脚IO口工作原理1.IO口的分类1.1口线口线是指单向传输数据的引脚,它可以把数据发送给外部设备或接收来自外部设备的数据。

其中P0、P2和P3是口线,在默认情况下,它们的工作方式是输出模式。

1.2双向总线双向总线是指可以同时发送和接收数据的引脚,它常用于与外部设备进行通信,例如LCD显示屏。

其中P1是双向总线,在默认情况下,它的工作方式是输入模式。

2.IO口的工作模式2.1输入模式在输入模式下,IO口从外部设备接收信号。

当IO口设置为输入模式时,它会使用内部上拉电阻或外部电阻来保持引脚电平。

2.1.1内部上拉电阻内部上拉电阻使得当没有外部设备连接到IO引脚时,引脚会保持高电平。

要使用内部上拉电阻,可以将IO口设置为输入模式,并将其对应的引脚设置为逻辑1,例如:P1=0xFF。

2.1.2外部电阻如果需要连接外部设备到IO引脚,并保持引脚电平,可以使用外部电阻来实现。

在此情况下,需要将IO口设置为输入模式,并且外部设备需要连接一个电阻,使引脚电平保持在逻辑1或逻辑0。

2.2输出模式在输出模式下,IO口向外部设备发送信号。

当IO口设置为输出模式时,输出引脚可以被设置为逻辑1或逻辑0。

2.2.1输出高电平要将IO引脚设置为逻辑1,可以将IO口设置为输出模式,并将其对应的引脚设置为逻辑1,例如:P1=0xFF。

2.2.2输出低电平要将IO引脚设置为逻辑0,可以将IO口设置为输出模式,并将其对应的引脚设置为逻辑0,例如:P1=0x00。

2.3双向模式在双向模式下,IO口可以同时发送和接收数据。

要设置IO口为双向模式,可以将IO口设置为输入输出模式,并加上一个特定的配置。

3.IO口的配置为了设置IO口的功能,需要使用特定的控制寄存器和位操作。

以下是一些常用的51单片机IO口配置示例:3.1设置为输入模式要将IO口设置为输入模式,可以使用特定的控制寄存器和位操作。

例如,要将P1的第2位设置为输入模式,可以使用以下代码:```cP1=P1&(~(1<<2));//将P1的第2位设置为0,即输入模式```3.2设置为输出模式要将IO口设置为输出模式,可以使用特定的控制寄存器和位操作。

单片机未使用引脚的合理处理方法

通常我们并不会把全部的单片机的引脚都用完,有时候我们也在同一个产品上分凹凸配,因此如何对待一些不使用的引脚就成了一个问题。

首先我们看一下单片机引脚的结构。

我们可以发觉,一般单片机的IO口都是可以配置的。

CMOS 器件引脚由N沟道和P沟道场效应管,通常在一个时刻,只有一个管子是开通的,但是,有一个特别短的时间转换期,这两种管子都会部分导通,在一个管子关闭而另一个开启的时候。

一个没有端接的输入口可能振荡或在一个中间电平上浮动,导致全部场效应管设备都将在一个微导通的状态,导致了管子的损耗,增加了噪声,并要消耗额外的电源电流。

(Input Only)输入专用管脚

1.使用上拉或下拉电阻,将每个未使用的引脚拉到VSS或VDD,这是推举的使用方法

2.捆绑在一起,并用单个电阻上拉/下拉到VDD或地,节约元件数量和成本,但是这削减了削减的敏捷性。

(Input/Output)输入/输出引脚

1.每个引脚的下拉一个电阻到地(VSS)。

2.几个引脚连下拉同一个电阻到地(VSS)。

3.不连接的针脚,软件程序配置IO口为输出口,并将它们设置为输出低。

4.连接一个电阻到Vss,软件程序配置IO口为输出低。

5.直接连接到地,软件程序把端口配置成高阻抗输入口,设置寄存器为输出低状态。

留意这将引发双发失误导致的问题(引脚从输入到输出的变化,输出从低到高状态变化)。

风险在于:

最终,我觉得还是每个电阻接到地比较平安。