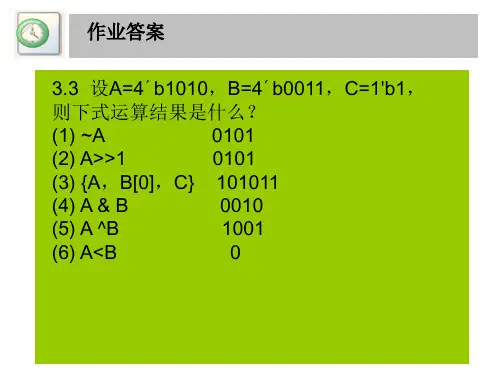

《基于FPGA的现代数字系统设计》作业参考答案

- 格式:ppt

- 大小:325.00 KB

- 文档页数:24

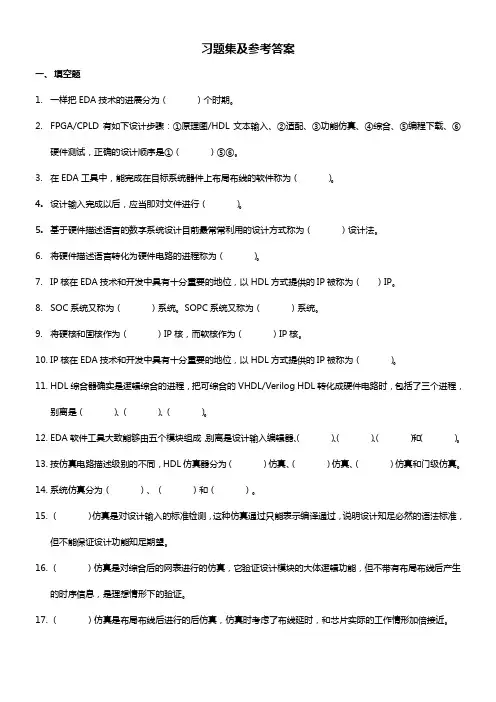

习题集及参考答案一、填空题 1. 一般把EDA技术的发展分为()个阶段。

2. FPGA/CPLD有如下设计步骤:①原理图/HDL文本输入、②适配、③功能仿真、④综合、⑤编程下载、⑥硬件测试,正确的设计顺序是①()⑤⑥。

3. 在EDA工具中,能完成在目标系统器件上布局布线的软件称为()。

4. 设计输入完成之后,应立即对文件进行()。

5. 基于硬件描述语言的数字系统设计目前最常用的设计方法称为()设计法。

6. 将硬件描述语言转化为硬件电路的过程称为()。

7. IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为()IP。

8. SOC系统又称为()系统。

SOPC系统又称为()系统。

9. 将硬核和固核作为()IP核,而软核作为()IP核。

10. IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为()。

11. HDL综合器就是逻辑综合的过程,把可综合的VHDL/Verilog HDL转化成硬件电路时,包含了三个过程,分别是()、()、()。

12. EDA软件工具大致可以由五个模块构成,分别是设计输入编辑器、()、()、()和()。

13. 按仿真电路描述级别的不同,HDL仿真器分为()仿真、()仿真、()仿真和门级仿真。

14. 系统仿真分为()、()和()。

15. ()仿真是对设计输入的规范检测,这种仿真通过只能表示编译通过,说明设计满足一定的语法规范,但不能保证设计功能满足期望。

16.()仿真是对综合后的网表进行的仿真,它验证设计模块的基本逻辑功能,但不带有布局布线后产生的时序信息,是理想情况下的验证。

17. ()仿真是布局布线后进行的后仿真,仿真时考虑了布线延时,和芯片实际的工作情况更加接近。

18. 目前Xilinx公司生产的FPGA主要采用了()配置存储器结构。

19. 描述测试信号的变化和测试工程的模块叫做()。

20. 现代电子系统设计领域中的EDA采用()的设计方法。

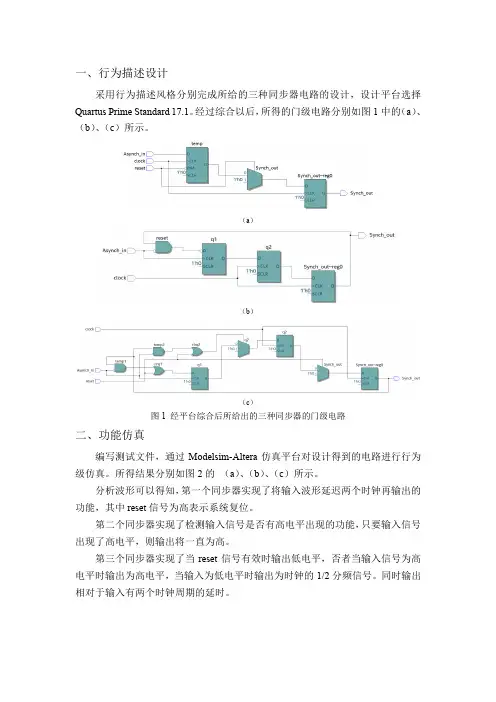

一、行为描述设计采用行为描述风格分别完成所给的三种同步器电路的设计,设计平台选择Quartus Prime Standard 17.1。

经过综合以后,所得的门级电路分别如图1中的(a)、(b)、(c)所示。

(a)(b)(c)图1 经平台综合后所给出的三种同步器的门级电路二、功能仿真编写测试文件,通过Modelsim-Altera仿真平台对设计得到的电路进行行为级仿真。

所得结果分别如图2的(a)、(b)、(c)所示。

分析波形可以得知,第一个同步器实现了将输入波形延迟两个时钟再输出的功能,其中reset信号为高表示系统复位。

第二个同步器实现了检测输入信号是否有高电平出现的功能,只要输入信号出现了高电平,则输出将一直为高。

第三个同步器实现了当reset信号有效时输出低电平,否者当输入信号为高电平时输出为高电平,当输入为低电平时输出为时钟的1/2分频信号。

同时输出相对于输入有两个时钟周期的延时。

(a)(b)(c)图2 三种同步器分别进行门级仿真的结果三、时序仿真分别对三个同步器进行时序仿真所得结果如图3的(a)、(b)、(c)所示。

可以很清楚的发现,时序仿真中的输出相比于功能仿真会有一个延时。

而且这还导致了第三个同步器的一个输出错误,本来应该输出分频信号,却输出了低电平。

(a)(b)(c)图3 三种同步器分别进行时序仿真的结果附件:同步器一:module HomeWorkOne(input Asynch_in ,input clock ,input reset , output regSynch_out);reg temp = 1'b0;always@(posedge clock) beginif(reset) beginSynch_out <= 1'b0 ;endelse beginSynch_out = temp ;temp = Asynch_in ;endendendmodule测试代码:`timescale 1 ns/ 1 psmodule HomeWorkOne_test();// test vector input registersreg Asynch_in;reg clock;reg reset;// wireswire Synch_out;// assign statements (if any)HomeWorkOne i1 (// port map - connection between master ports and signals/registers .Asynch_in(Asynch_in),.Synch_out(Synch_out),.clock(clock),.reset(reset));initial beginclock = 1'b0 ;reset = 1'b1 ;Asynch_in = 1'b0 ;#100 reset = 1'b0 ;#40 Asynch_in = 1'b1 ;#40 Asynch_in = 1'b0 ;#40 reset = 1'b1 ;#40 Asynch_in = 1'b1 ;#40 Asynch_in = 1'b0 ;#40 $stop ;$display("Running testbench");endalways begin#10 clock = ~clock ;endendmodule同步器二:module HomeWorkTwo(input clock ,input Asynch_in ,output reg Synch_out);reg q1 = 1'b0 ;reg q2 = 1'b0 ;wire reset ;assign reset = Synch_out&(~Asynch_in) ;always@(posedge clock) beginSynch_out = q2 ;q2 = q1 ; endalways@(posedge Asynch_in) beginif(reset) beginq1 = 1'b0 ;endelse beginq1 = 1'b1 ;endendendmodule测试代码:`timescale 1 ns/ 1 psmodule HomeWorkTwo_test();// test vector input registersreg Asynch_in;reg clock;// wireswire Synch_out;// assign statements (if any)HomeWorkTwo i1 (// port map - connection between master ports and signals/registers.Asynch_in(Asynch_in),.Synch_out(Synch_out),.clock(clock));initial beginclock = 1'b0 ;Asynch_in = 1'b0 ;#40 Asynch_in = 1'b1 ;#40 Asynch_in = 1'b0 ;#40 Asynch_in = 1'b1 ;#40 Asynch_in = 1'b0 ;#40 $stop ;$display("Running testbench");endalways begin#10 clock = ~clock ;endendmodule同步器三:module HomeWorkThree(input Asynch_in ,input clock ,input reset ,output reg Synch_out);reg q1 = 1'b0 ;reg q2 = 1'b0 ;wire temp ;wire temp2 ;wire clrq1 ;wire clrq2 ;assign temp1 = Synch_out&(~Asynch_in) ;assign temp2 = Synch_out&(~Asynch_in) ;assign clrq1 = reset|temp1 ;assign clrq2 = reset|temp2 ;always@(posedge clock) beginif(reset) beginSynch_out = 1'b0 ;endelse beginSynch_out = q2 ;endendalways@(posedge clock) beginif(clrq2) beginq2 = 1'b0 ;endelse beginq2 = q1 ;endendalways@(posedge Asynch_in) beginif(clrq1) beginq1 = 1'b0 ;endelse beginq1 = 1'b1 ;endendendmodule测试代码:`timescale 1 ns/ 1 psmodule HomeWorkThree_test();// test vector input registersreg Asynch_in;reg clock;reg reset;// wireswire Synch_out;// assign statements (if any)HomeWorkThree i1 (// port map - connection between master ports and signals/registers.Asynch_in(Asynch_in),.Synch_out(Synch_out),.clock(clock),.reset(reset));initial beginclock = 1'b0 ;reset = 1'b1 ;Asynch_in = 1'b0 ;#100 reset = 1'b0 ;#40 Asynch_in = 1'b1 ;#40 Asynch_in = 1'b0 ;#40 Asynch_in = 1'b1 ;#40 Asynch_in = 1'b0 ;#40 Asynch_in = 1'b1 ;#40 Asynch_in = 1'b0 ;#40 Asynch_in = 1'b0 ;#40 Asynch_in = 1'b1 ;#40 reset = 1'b1 ;#40 Asynch_in = 1'b1 ;#40 Asynch_in = 1'b0 ;#40 $stop ;$display("Running testbench");endalways begin#1 clock = ~clock ;endendmodule。

精品文档习题集及参考答案填空题 一般把EDA 技术的发展分为( )个阶段。

FPGA/CPLD 有如下设计步骤:①原理图/HDL 文本输入、②适配、 ⑤编程下载、⑥硬件测试,正确的设计顺序是◎()⑤⑥。

在EDA 工具中,能完成在目标系统器件上布局布线的软件称为( 设计输入完成之后,应立即对文件进行(IP 核在EDA 技术和开发中具有十分重要的地位, 以HDL 方式提供的IP 被称为( HDL 综合器就是逻辑综合的过程,把可综合的 VHDL/Verilog HDL 包含了三个过程,分别是( )、()、(EDA 软件工具大致可以由五个模块构成, 分别是设计输入编辑器、和(1. 2. 3. 4. 5. 6. 7. 8.9. 10. 11. 12.13. 14. 15. 16. 17. 18. 19. 20. 21. 22. 23. 24. 25. 26. 27. 28. 29. 30.基于硬件描述语言的数字系统设计目前最常用的设计方法称为( 将硬件描述语言转化为硬件电路的过程称为( IP 核在EDA技术和开发中具有十分重要的地位,以 IP ° SOC 系统又称为( )系统。

SOPC 系统又称为将硬核和固核作为( )IP 核,而软核作为()° HDL 方式提供的 )系统。

)IP核。

)设计法。

IP 被称为(按仿真电路描述级别的不同, HDL 仿真器分为(仿真和门级仿真。

系统仿真分为( )、( )和()仿真、( )仿真、( )。

( )仿真是对设计输入的规范检测,这种仿真通过只能表示编译通过,说明设计满足一定的语法规范,但不能保证设计功能满足期望。

( )仿真是对综合后的网表进行的仿真,它验证设计模块的基本逻辑功能,但不 带有布局布线后产生的时序信息,是理想情况下的验证。

()仿真是布局布线后进行的后仿真,仿真时考虑了布线延时,和芯片实际的工 作情况更加接近。

目前Xilinx 公司生产的FPGA 主要采用了( 描述测试信号的变化和测试工程的模块叫做( 现代电子系统设计领域中的 E DA 采用( 有限状态机可分为( )状态机和( Verilog HDL 中的端口类型有三类: Verilog HDL 常用两大数据类型: FPGA / CPLD 设计流程为:原理图 编程下载-硬件测试。

习题集及参考答案一、填空题1.一般把EDA技术的发展分为()个阶段。

2.FPGA/CPLD有如下设计步骤:①原理图/HDL文本输入、②适配、③功能仿真、④综合、⑤编程下载、⑥硬件测试,正确的设计顺序是①()⑤⑥。

3.在EDA工具中,能完成在目标系统器件上布局布线的软件称为()。

4.设计输入完成之后,应立即对文件进行()。

5.基于硬件描述语言的数字系统设计目前最常用的设计方法称为()设计法。

6.将硬件描述语言转化为硬件电路的过程称为()。

7.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为()IP。

8.SOC系统又称为()系统。

SOPC系统又称为()系统。

9.将硬核和固核作为()IP核,而软核作为()IP核。

10.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为()。

11.HDL综合器就是逻辑综合的过程,把可综合的VHDL/Verilog HDL转化成硬件电路时,包含了三个过程,分别是()、()、()。

12.EDA软件工具大致可以由五个模块构成,分别是设计输入编辑器、()、()、()和()。

13.按仿真电路描述级别的不同,HDL仿真器分为()仿真、()仿真、()仿真和门级仿真。

14.系统仿真分为()、()和()。

15.()仿真是对设计输入的规范检测,这种仿真通过只能表示编译通过,说明设计满足一定的语法规范,但不能保证设计功能满足期望。

16.()仿真是对综合后的网表进行的仿真,它验证设计模块的基本逻辑功能,但不带有布局布线后产生的时序信息,是理想情况下的验证。

17.()仿真是布局布线后进行的后仿真,仿真时考虑了布线延时,和芯片实际的工作情况更加接近。

18.目前Xilinx公司生产的FPGA主要采用了()配置存储器结构。

19.描述测试信号的变化和测试工程的模块叫做()。

20.现代电子系统设计领域中的EDA采用()的设计方法。

21.有限状态机可分为()状态机和()状态机两类。

fpga cpld参考答案FPGA和CPLD是现代数字电路设计中常用的可编程逻辑器件。

它们在电子工程领域中扮演着重要的角色,广泛应用于各种领域,如通信、嵌入式系统、计算机硬件等。

本文将介绍FPGA和CPLD的基本概念、特点以及应用,并提供一些参考答案来帮助读者更好地理解和应用这些器件。

FPGA,即现场可编程门阵列(Field-Programmable Gate Array),是一种可编程逻辑器件,它由大量的逻辑门、存储单元和可编程互连资源组成。

与传统的专用集成电路(ASIC)相比,FPGA具有灵活性高、开发周期短的优势。

它可以通过编程来实现各种不同的数字电路功能,而无需进行物理上的改变。

这使得FPGA成为了快速原型设计、快速验证和低成本量产的理想选择。

CPLD,即复杂可编程逻辑器件(Complex Programmable Logic Device),与FPGA类似,也是一种可编程逻辑器件。

但与FPGA相比,CPLD规模较小,资源有限。

它由可编程的逻辑单元、触发器和互连资源组成。

CPLD适用于一些规模较小、逻辑较简单的应用场景,如时序逻辑控制、接口逻辑等。

FPGA和CPLD的特点使得它们在各种领域得到广泛应用。

在通信领域,FPGA和CPLD可以用于实现各种协议的解析、编解码、调制解调等功能。

在嵌入式系统中,FPGA和CPLD可以用于实现各种外设接口、时序控制、状态机等。

在计算机硬件领域,FPGA和CPLD可以用于实现高性能计算、逻辑仿真、硬件加速等。

接下来,我们将提供一些参考答案,帮助读者更好地理解和应用FPGA和CPLD。

1. FPGA和CPLD的主要区别是什么?FPGA和CPLD的主要区别在于规模和资源。

FPGA规模较大,资源丰富,适用于复杂的逻辑设计;而CPLD规模较小,资源有限,适用于简单的逻辑设计。

此外,FPGA的可编程互连资源更灵活,可以实现更复杂的互连结构;而CPLD的互连资源相对固定,适用于一些简单的逻辑互连。

习题集及参考答案一、填空题1.一样把EDA技术的进展分为()个时期。

2.FPGA/CPLD有如下设计步骤:①原理图/HDL文本输入、②适配、③功能仿真、④综合、⑤编程下载、⑥硬件测试,正确的设计顺序是①()⑤⑥。

3.在EDA工具中,能完成在目标系统器件上布局布线的软件称为()。

4.设计输入完成以后,应当即对文件进行()。

5.基于硬件描述语言的数字系统设计目前最常常利用的设计方式称为()设计法。

6.将硬件描述语言转化为硬件电路的进程称为()。

7.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为()IP。

8.SOC系统又称为()系统。

SOPC系统又称为()系统。

9.将硬核和固核作为()IP核,而软核作为()IP核。

10.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为()。

11.HDL综合器确实是逻辑综合的进程,把可综合的VHDL/Verilog HDL转化成硬件电路时,包括了三个进程,别离是()、()、()。

12.EDA软件工具大致能够由五个模块组成,别离是设计输入编辑器、()、()、()和()。

13.按仿真电路描述级别的不同,HDL仿真器分为()仿真、()仿真、()仿真和门级仿真。

14.系统仿真分为()、()和()。

15.()仿真是对设计输入的标准检测,这种仿真通过只能表示编译通过,说明设计知足必然的语法标准,但不能保证设计功能知足期望。

16.()仿真是对综合后的网表进行的仿真,它验证设计模块的大体逻辑功能,但不带有布局布线后产生的时序信息,是理想情形下的验证。

17.()仿真是布局布线后进行的后仿真,仿真时考虑了布线延时,和芯片实际的工作情形加倍接近。

18.目前Xilinx公司生产的FPGA要紧采纳了()配置存储器结构。

19.描述测试信号的转变和测试工程的模块叫做()。

20.现代电子系统设计领域中的EDA采纳()的设计方式。

21.有限状态机可分为()状态机和()状态机两类。

习题集及参考答案一、填空题1.一般把EDA技术的发展分为()个阶段。

2.FPGA/CPLD有如下设计步骤:①原理图/HDL文本输入、②适配、③功能仿真、④综合、⑤编程下载、⑥硬件测试,正确的设计顺序是①()⑤⑥。

3.在EDA工具中,能完成在目标系统器件上布局布线的软件称为()。

4.设计输入完成之后,应立即对文件进行()。

5.基于硬件描述语言的数字系统设计目前最常用的设计方法称为()设计法。

6.将硬件描述语言转化为硬件电路的过程称为()。

7.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为()IP。

8.SOC系统又称为()系统。

SOPC系统又称为()系统。

9.将硬核和固核作为()IP核,而软核作为()IP核。

10.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为()。

11.HDL综合器就是逻辑综合的过程,把可综合的VHDL/Verilog HDL转化成硬件电路时,包含了三个过程,分别是()、()、()。

12.EDA软件工具大致可以由五个模块构成,分别是设计输入编辑器、()、()、()和()。

13.按仿真电路描述级别的不同,HDL仿真器分为()仿真、()仿真、()仿真和门级仿真。

14.系统仿真分为()、()和()。

15.()仿真是对设计输入的规范检测,这种仿真通过只能表示编译通过,说明设计满足一定的语法规范,但不能保证设计功能满足期望。

16.()仿真是对综合后的网表进行的仿真,它验证设计模块的基本逻辑功能,但不带有布局布线后产生的时序信息,是理想情况下的验证。

17.()仿真是布局布线后进行的后仿真,仿真时考虑了布线延时,和芯片实际的工作情况更加接近。

18.目前Xilinx公司生产的FPGA主要采用了()配置存储器结构。

19.描述测试信号的变化和测试工程的模块叫做()。

20.现代电子系统设计领域中的EDA采用()的设计方法。

21.有限状态机可分为()状态机和()状态机两类。

习题集及参考答案一、填空题1.一般把EDA技术的发展分为()个阶段。

2.FPGA/CPLD有如下设计步骤:①原理图/HDL文本输入、②适配、③功能仿真、④综合、⑤编程下载、⑥硬件测试,正确的设计顺序是①()⑤⑥。

3.在EDA工具中,能完成在目标系统器件上布局布线的软件称为()。

4.设计输入完成之后,应立即对文件进行()。

5.基于硬件描述语言的数字系统设计目前最常用的设计方法称为()设计法。

6.将硬件描述语言转化为硬件电路的过程称为()。

7.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为()IP。

8.SOC系统又称为()系统。

SOPC系统又称为()系统。

9.将硬核和固核作为()IP核,而软核作为()IP核。

10.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为()。

11.HDL综合器就是逻辑综合的过程,把可综合的VHDL/Verilog HDL转化成硬件电路时,包含了三个过程,分别是()、()、()。

12.EDA软件工具大致可以由五个模块构成,分别是设计输入编辑器、()、()、()和()。

13.按仿真电路描述级别的不同,HDL仿真器分为()仿真、()仿真、()仿真和门级仿真。

14.系统仿真分为()、()和()。

15.()仿真是对设计输入的规范检测,这种仿真通过只能表示编译通过,说明设计满足一定的语法规范,但不能保证设计功能满足期望。

16.()仿真是对综合后的网表进行的仿真,它验证设计模块的基本逻辑功能,但不带有布局布线后产生的时序信息,是理想情况下的验证。

17.()仿真是布局布线后进行的后仿真,仿真时考虑了布线延时,和芯片实际的工作情况更加接近。

18.目前Xilinx公司生产的FPGA主要采用了()配置存储器结构。

19.描述测试信号的变化和测试工程的模块叫做()。

20.现代电子系统设计领域中的EDA采用()的设计方法。

21.有限状态机可分为()状态机和()状态机两类。