晶圆封装可靠性实验项目

- 格式:pdf

- 大小:120.55 KB

- 文档页数:2

电子封装中的可靠性问题电子器件是一个较复杂的系统,其封装过程的缺陷和失效也是比较复杂的。

因此,研究封装缺陷和失效需要对封装过程有一个系统性的了解,这样才能从多个角度去分析缺陷产生的原因。

封装的失效机理可以分为两类:过应力和磨损。

过应力失效往往是瞬时的、灾难性的;磨损失效是长期的累积损坏,往往首先表示为性能退化,接着才是器件失效。

失效的负载类型又可以分为机械、热、电气、辐射和化学负载等。

影响封装缺陷和失效的因素是多种多样的,材料成分和属性、封装设计、环境条件和工艺参数等都会有所影响。

确定影响因素和预防封装缺陷和失效的基本前提。

影响因素可以通过试验或者模拟仿真的方法来确定,一般多采用物理模型法和数值参数法。

对于较复杂的缺陷和失效机理,常常采用试差法确定关键的影响因素,但是这个方法需要较长的试验时间和设备修正,效率低、花费高。

在分析失效机理的过程中,采用鱼骨图(因果图)展示影响因素是行业通用的方法。

鱼骨图可以说明复杂的原因及影响因素和封装缺陷之间的关系,也可以区分多种原因并将其分门别类。

生产应用中,有一类鱼骨图被称为6Ms:从机器、方法、材料、量度、人力和自然力等六个维度分析影响因素。

这一张图所示的是展示塑封芯片分层原因的鱼骨图,从设计、工艺、环境和材料四个方面进行了分析。

通过鱼骨图,清晰地展现了所有的影响因素,为失效分析奠定了良好基础。

引发失效的负载类型01机械载荷包括物理冲击、振动、填充颗粒在硅芯片上施加的应力(如收缩应力)和惯性力(如宇宙飞船的巨大加速度)等。

材料对这些载荷的响应可能表现为弹性形变、塑性形变、翘曲、脆性或柔性断裂、界面分层、疲劳裂缝产生和扩展、蠕变以及蠕变开裂等等。

02热载荷包括芯片黏结剂固化时的高温、引线键合前的预加热、成型工艺、后固化、邻近元器件的再加工、浸焊、气相焊接和回流焊接等等。

外部热载荷会使材料因热膨胀而发生尺寸变化,同时也会改变蠕变速率等物理属性。

如发生热膨胀系数失配(CTE失配)进而引发局部应力,并最终导致封装结构失效。

半导体可靠性实验项目概述半导体可靠性实验项目是一个重要的研究领域,旨在评估和验证半导体器件在长时间运行和不同环境条件下的可靠性。

通过该实验项目,我们可以获取半导体器件的寿命、故障率以及在各种应力条件下的性能指标。

这些数据对于半导体产品的生产和使用具有重要意义,可以帮助制造商改进产品设计和制造工艺,提高产品的质量和可靠性。

实验目的该实验项目的主要目的是通过测试和分析来评估半导体器件的可靠性,具体目标包括:1. 了解半导体器件的寿命特性;2. 评估半导体器件在不同环境条件下的可靠性;3. 分析半导体器件的故障率以及故障模式。

实验内容半导体可靠性实验项目的内容主要包括以下几个方面: 1.试验准备:确定实验所需的半导体器件和测试设备,并准备相关的试验方案和流程。

2. 加速寿命试验:将半导体器件放置在高温、高湿、高电压等应力环境下进行长时间运行,记录器件的运行时间和性能变化。

3. 温度循环试验:将半导体器件在高温和低温之间进行循环变温,观察其在温度变化过程中的性能表现和故障情况。

4. 电压应力试验:在给定电压条件下,对半导体器件进行长时间稳定运行,记录器件的故障率和性能变化。

5. 湿度应力试验:将半导体器件置于高湿度环境中,观察其性能变化和故障情况。

6. 试验数据分析:对实验过程中获得的数据进行统计和分析,绘制可靠性曲线、寿命曲线等,评估半导体器件的可靠性指标。

实验步骤1.确定要测试的半导体器件的型号和数量,并选取适当的测试设备。

2.按照实验方案和流程进行试验准备工作,包括清洁和校准设备,搭建测试电路,设置参数等。

3.进行加速寿命试验,将半导体器件置于高温、高湿、高电压等应力环境下运行,记录器件的运行时间和性能变化。

4.进行温度循环试验,将半导体器件在高温和低温之间进行循环变温,观察其性能表现和故障情况。

5.进行电压应力试验,对半导体器件进行长时间稳定运行,记录器件的故障率和性能变化。

6.进行湿度应力试验,将半导体器件置于高湿度环境中,观察其性能变化和故障情况。

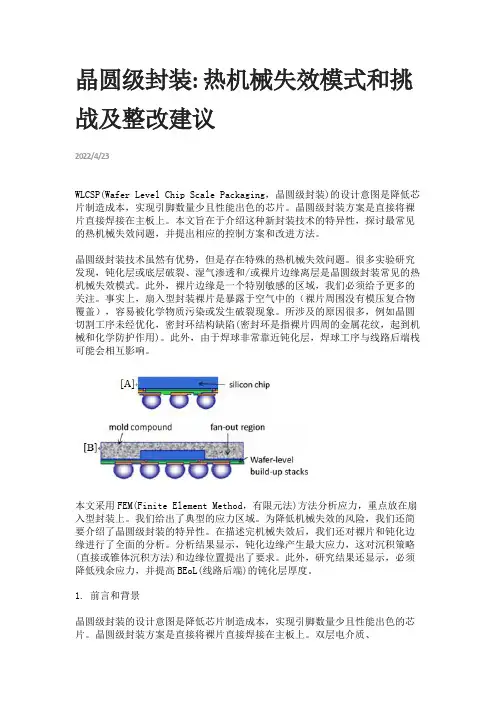

晶圆级封装: 热机械失效模式和挑战及整改建议2022/4/23WLCSP(Wafer Level Chip Scale Packaging,晶圆级封装)的设计意图是降低芯片制造成本,实现引脚数量少且性能出色的芯片。

晶圆级封装方案是直接将裸片直接焊接在主板上。

本文旨在于介绍这种新封装技术的特异性,探讨最常见的热机械失效问题,并提出相应的控制方案和改进方法。

晶圆级封装技术虽然有优势,但是存在特殊的热机械失效问题。

很多实验研究发现,钝化层或底层破裂、湿气渗透和/或裸片边缘离层是晶圆级封装常见的热机械失效模式。

此外,裸片边缘是一个特别敏感的区域,我们必须给予更多的关注。

事实上,扇入型封装裸片是暴露于空气中的(裸片周围没有模压复合物覆盖),容易被化学物质污染或发生破裂现象。

所涉及的原因很多,例如晶圆切割工序未经优化,密封环结构缺陷(密封环是指裸片四周的金属花纹,起到机械和化学防护作用)。

此外,由于焊球非常靠近钝化层,焊球工序与线路后端栈可能会相互影响。

本文采用FEM(Finite Element Method,有限元法)方法分析应力,重点放在扇入型封装上。

我们给出了典型的应力区域。

为降低机械失效的风险,我们还简要介绍了晶圆级封装的特异性。

在描述完机械失效后,我们还对裸片和钝化边缘进行了全面的分析。

分析结果显示,钝化边缘产生最大应力,这对沉积策略(直接或锥体沉积方法)和边缘位置提出了要求。

此外,研究结果还显示,必须降低残余应力,并提高BEoL(线路后端)的钝化层厚度。

1. 前言和背景晶圆级封装的设计意图是降低芯片制造成本,实现引脚数量少且性能出色的芯片。

晶圆级封装方案是直接将裸片直接焊接在主板上。

双层电介质、RDL(ReDistribution Layer, 重新布线层)、UBM (可焊接薄层,用于焊球底部金属化)和焊球都位于标准BEoL栈之上。

因此,这些层级扩展了传统晶片制程(多层沉积薄膜配合光刻工艺)范围。

MEMS封装可靠性测试规范MEMS 封装可靠性测试规范华中科技大学微系统中心MEMS 封装可靠性测试规范1. 引言1.1 MEMS 概念微光机电系统(Micro ElectroMechanical Systems—MEMS),以下简称 MEMS。

MEMS 是融合了硅微加工、LIGA(光刻、电铸和塑铸)和精密机械加工等多种微加工技术,并应用现代信息技术构成的微型系统。

它在微电子技术的基础上发展起来的,但又区别于微电子技术。

它包括感知外界信息 (力、热、光、磁、电、声等)的传感器和控制对象的执行器,以及进行信号处理和控制的电路。

MEMS 器件和传统的机器相比,具有体积小、重量轻、耗能低、温升小、工作速度快、成本低、功能强、性能好等特点。

MEMS 封装可靠性测试规范所含范围 1.2本可靠性测试规范涉及到在 MEMS 封装工艺中的贴片(包括倒装焊、载带自动焊)、引线键合、封盖等几个重要工艺的可靠性测试。

每步工艺的测试项目可根据具体器件要求选用。

2. 贴片工艺测试2.1 贴片工艺测试要求贴片工艺是将芯片用胶接或焊接的方式连接到基座上的工艺过程。

胶接或焊接的质量要受到加工环境与工作环境的影响,因此要对胶接或焊接的质量与可靠性进行测试。

胶接或焊接处表面应均匀连接,无气孔,不起皮,无裂纹,内部无空洞,并能承受一定的疲劳强度。

在热循环、热冲击、机械冲击、振动、恒定加速度等环境工作时,芯片与基座应连接牢固,不能产生过大的热应力。

芯片与基座无裂纹。

2.2 贴片工艺测试项目测试项目测试说明失效判据外部目检外观缺陷 50 倍放大镜检查芯片剪切强度大于最小剪切强度加力方向应与衬底表面方向平行芯片与基座的附拉力方向应与衬底表面方向垂直大于最小抗拉力着强度芯片与基座连接沿横截面贴光栅,用云纹干涉仪来测应变大于 0.1, 其应力应变场处的应力应变检测焊点或胶接处内部的空隙 X 射线照相空隙长度和宽度小于接触面积的 10, 芯片脱离、有裂纹高温高湿 85?、85,RH、1000h芯片脱离、有裂纹恒定加速度一般 30000g一般 1500g、0.5ms 芯片脱离、有裂纹机械冲击一般-65?,150?、10 次温度循环芯片脱离、有裂纹一般-40?,100?、5min/10sec 热冲击芯片脱离、有裂纹一般 20,2000Hz,20g 芯片脱离、有裂纹扫频振动沿芯片表面法线方向无冲击地拉芯片小于最小外加应力倒装片拉脱试验3.1 引线键合工艺测试要求引线键合工艺是用金或铝线将芯片上的信号引出到封装外壳的管脚上的工艺过程。

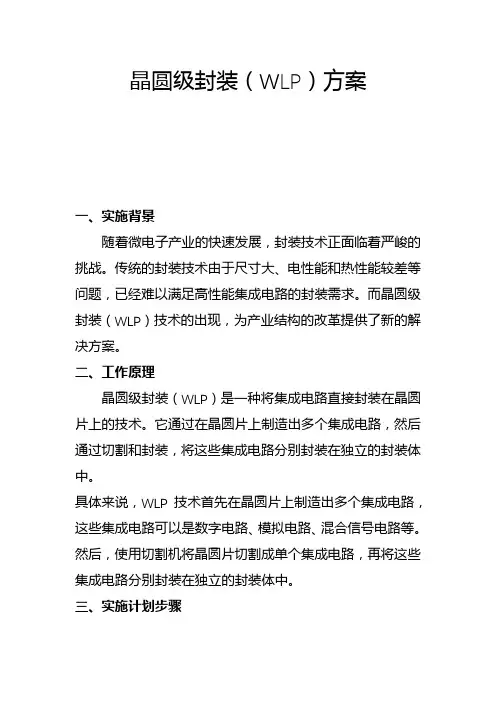

晶圆级封装(WLP)方案一、实施背景随着微电子产业的快速发展,封装技术正面临着严峻的挑战。

传统的封装技术由于尺寸大、电性能和热性能较差等问题,已经难以满足高性能集成电路的封装需求。

而晶圆级封装(WLP)技术的出现,为产业结构的改革提供了新的解决方案。

二、工作原理晶圆级封装(WLP)是一种将集成电路直接封装在晶圆片上的技术。

它通过在晶圆片上制造出多个集成电路,然后通过切割和封装,将这些集成电路分别封装在独立的封装体中。

具体来说,WLP技术首先在晶圆片上制造出多个集成电路,这些集成电路可以是数字电路、模拟电路、混合信号电路等。

然后,使用切割机将晶圆片切割成单个集成电路,再将这些集成电路分别封装在独立的封装体中。

三、实施计划步骤1.设备采购:需要采购制造集成电路所需的设备,如光刻机、刻蚀机、薄膜沉积设备等。

2.工艺研发:需要研发适合WLP技术的制造工艺,包括光刻工艺、刻蚀工艺、薄膜沉积工艺等。

3.样品制作:在研发阶段,需要制作样品以验证工艺的可行性。

4.测试与验证:对制作的样品进行测试和验证,确保其性能符合要求。

5.批量生产:当样品测试通过后,可以开始批量生产。

四、适用范围WLP技术适用于各种高性能集成电路的封装,如CPU、GPU、FPGA等。

它具有以下优点:1.体积小:由于WLP技术将集成电路直接封装在晶圆片上,因此可以大大减小封装体积。

2.电性能和热性能优异:WLP技术可以提供更好的电性能和热性能,从而提高集成电路的性能和可靠性。

3.制造成本低:由于WLP技术可以在晶圆片上制造多个集成电路,因此可以分摊制造成本,降低单个集成电路的制造成本。

4.可扩展性强:WLP技术可以轻松扩展到更大的晶圆尺寸和更高的产量。

五、创新要点1.制造工艺的创新:WLP技术需要研发适合其特点的制造工艺,包括光刻工艺、刻蚀工艺、薄膜沉积工艺等。

2.封装技术的创新:WLP技术需要开发新的封装技术,以实现集成电路的高性能、小型化和可靠性。

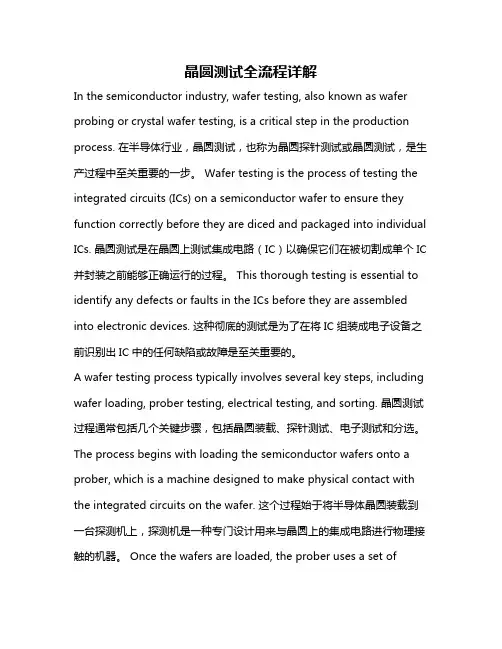

晶圆测试全流程详解In the semiconductor industry, wafer testing, also known as wafer probing or crystal wafer testing, is a critical step in the production process. 在半导体行业,晶圆测试,也称为晶圆探针测试或晶圆测试,是生产过程中至关重要的一步。

Wafer testing is the process of testing the integrated circuits (ICs) on a semiconductor wafer to ensure they function correctly before they are diced and packaged into individual ICs. 晶圆测试是在晶圆上测试集成电路(IC)以确保它们在被切割成单个IC 并封装之前能够正确运行的过程。

This thorough testing is essential to identify any defects or faults in the ICs before they are assembled into electronic devices. 这种彻底的测试是为了在将IC组装成电子设备之前识别出IC中的任何缺陷或故障是至关重要的。

A wafer testing process typically involves several key steps, including wafer loading, prober testing, electrical testing, and sorting. 晶圆测试过程通常包括几个关键步骤,包括晶圆装载、探针测试、电子测试和分选。

The process begins with loading the semiconductor wafers onto a prober, which is a machine designed to make physical contact with the integrated circuits on the wafer. 这个过程始于将半导体晶圆装载到一台探测机上,探测机是一种专门设计用来与晶圆上的集成电路进行物理接触的机器。

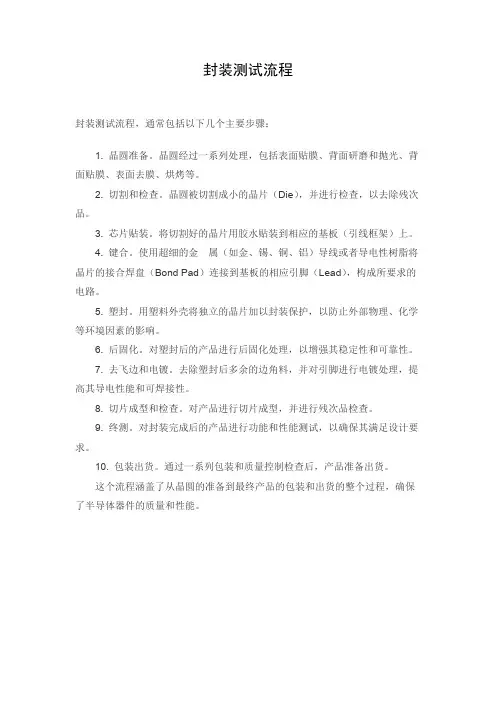

封装测试流程

封装测试流程,通常包括以下几个主要步骤:

1. 晶圆准备。

晶圆经过一系列处理,包括表面贴膜、背面研磨和抛光、背面贴膜、表面去膜、烘烤等。

2. 切割和检查。

晶圆被切割成小的晶片(Die),并进行检查,以去除残次品。

3. 芯片贴装。

将切割好的晶片用胶水贴装到相应的基板(引线框架)上。

4. 键合。

使用超细的金属(如金、锡、铜、铝)导线或者导电性树脂将晶片的接合焊盘(Bond Pad)连接到基板的相应引脚(Lead),构成所要求的电路。

5. 塑封。

用塑料外壳将独立的晶片加以封装保护,以防止外部物理、化学等环境因素的影响。

6. 后固化。

对塑封后的产品进行后固化处理,以增强其稳定性和可靠性。

7. 去飞边和电镀。

去除塑封后多余的边角料,并对引脚进行电镀处理,提高其导电性能和可焊接性。

8. 切片成型和检查。

对产品进行切片成型,并进行残次品检查。

9. 终测。

对封装完成后的产品进行功能和性能测试,以确保其满足设计要求。

10. 包装出货。

通过一系列包装和质量控制检查后,产品准备出货。

这个流程涵盖了从晶圆的准备到最终产品的包装和出货的整个过程,确保了半导体器件的质量和性能。

晶圆级芯片封装生产建设项目可行性研究报告一、项目背景晶圆级芯片封装是指在晶圆制造完成后将芯片进行封装,以便将其引脚暴露在外,并提供保护和盖板,从而实现芯片的电气连接、保护和散热等功能。

随着电子技术的快速发展,晶圆级芯片封装行业需求不断增长,市场潜力巨大。

二、项目目标本项目旨在建设一条晶圆级芯片封装生产线,实现国内自主生产晶圆级芯片封装产品,提高国内芯片封装产业竞争力,并满足国内市场需求,减少对进口产品的依赖。

三、市场分析据统计和预测数据显示,晶圆级芯片封装市场规模逐年增加,市场需求旺盛。

目前国内市场主要依赖进口产品,出口产品占比较低,存在较大的市场空白。

同时,随着5G技术的快速推广和应用,对新一代芯片封装技术的需求也不断增长,市场潜力更加广阔。

四、可行性分析1.技术可行性:项目所需的晶圆级芯片封装生产技术已经成熟并在国内外得到广泛应用,具备较高的技术可行性。

2.经济可行性:项目将在满足国内市场需求的同时,拓展国际市场,实现规模生产,预计在较短时间内收回投资,并具备稳定的盈利能力。

3.市场可行性:市场需求旺盛且增长速度快,国内市场空白较大,项目具备良好的市场前景。

4.法律可行性:项目经营活动符合国家相关法律法规,不存在法律障碍。

五、项目投资1.土地建设:购买或租赁一块适宜的土地,用于建设晶圆级芯片封装生产线。

2.建设厂房:建设符合生产需要的现代化厂房,包括生产区、办公区、物流区等。

3.设备采购:购买先进的晶圆级芯片封装设备,包括封装机、焊接设备、测试设备等。

4.人员配备:招聘技术人员、生产人员和管理人员等,建立专业高效的团队。

5.营销推广:进行产品推广和营销活动,拓展国内外市场。

六、风险与对策1.技术风险:加强技术研发与创新,提高产品竞争力。

2.市场风险:积极了解市场需求并灵活调整生产策略,确保产品符合市场需求。

3.人员管理风险:建立科学的人员管理制度,激励员工积极性和创造力。

4.资金风险:合理安排资金投入,并建立健全的风险管理体系。

晶圆制造质量测试报告晶圆制造质量测试报告为了确保晶圆制造的质量,我们进行了详细的测试和评估。

以下是我们的测试报告。

1. 测试目的:评估晶圆的物理和电学性能。

2. 测试方法:我们使用了一系列测试设备和工具,包括:显微镜、化学分析仪、力学测试机和电子测试仪器等。

3. 测试内容:a. 物理性能测试:(1) 晶圆外观检查:检查晶圆表面的平整度、光洁度和是否有明显的缺陷。

(2) 尺寸测量:使用显微镜和光学测量仪器测量晶圆的直径和厚度。

(3) 硬度测试:使用硬度计测量晶圆表面的硬度。

b. 化学性能测试:(1) 成分分析:使用化学分析仪检测晶圆材料的化学成分。

(2) 杂质检测:通过化学分析和显微镜检测晶圆中是否存在杂质。

c. 电学性能测试:(1) 导电性测试:使用电阻计测量晶圆的导电性能。

(2) 电容性测试:使用电容计测量晶圆的电容性能。

4. 测试结果:a. 物理性能:(1) 晶圆外观:晶圆表面平整、光洁,无明显缺陷。

(2) 尺寸:晶圆直径为30mm,厚度为2mm。

(3) 硬度:晶圆表面硬度为70HRC。

b. 化学性能:(1) 成分分析:晶圆材料主要成分为硅(Si),杂质含量小于0.1%。

(2) 杂质检测:未检测到明显的杂质。

c. 电学性能:(1) 导电性:晶圆导电性良好,电阻率为1x10^-6 Ω·cm。

(2) 电容性:晶圆电容性稳定,电容值为2μF。

5. 结论:根据以上测试结果,晶圆的质量良好,符合制造要求。

晶圆具有良好的物理、化学和电学性能,适用于后续半导体制造工艺。

我们将持续监控和改进晶圆制造过程,以确保产品质量的稳定性和可靠性。

晶圆级封装(WLP)方案一、实施背景随着微电子行业的快速发展,传统的封装技术已经无法满足市场对高性能、高集成、低成本及更快上市时间的需求。

在此背景下,晶圆级封装(Wafer Level Packaging,WLP)技术应运而生,成为微电子行业未来的重要发展方向。

WLP技术在提高封装密度、降低成本、缩短上市时间等方面具有显著优势,对于推动产业结构改革具有重大意义。

二、工作原理晶圆级封装(WLP)是一种将集成电路裸芯片直接封装在晶圆上的一种技术。

它利用先进的薄膜制造和晶圆加工技术,将芯片与晶圆相结合,形成一个完整的封装体。

WLP技术具有以下特点:1.高集成度:WLP技术可将多个裸芯片集成在一个封装体内,实现更高的集成度。

2.低成本:WLP技术简化了封装流程,减少了封装材料和加工成本,实现了更低的成本。

3.快速上市:WLP技术缩短了封装周期,提高了生产效率,从而加快了产品上市时间。

三、实施计划步骤1.需求分析:对市场需求进行调研,明确WLP技术的应用领域和市场需求。

2.技术研发:开展WLP技术研发,掌握核心技术,提升自主创新能力。

3.设备采购:根据技术研发需求,采购必要的设备和材料。

4.样品制作:制作WLP样品,对样品进行检测和验证。

5.批量生产:根据市场需求,进行批量生产。

6.市场推广:开展市场推广活动,扩大WLP技术的市场份额。

四、适用范围WLP技术适用于以下领域:1.通信:WLP技术可用于制造高频、高速的通信芯片,如5G通信、光通信等。

2.汽车:WLP技术可用于制造高可靠性的汽车电子器件,如发动机控制芯片、安全气囊控制芯片等。

3.医疗:WLP技术可用于制造高精度的医疗电子设备,如监护仪、超声等。

4.消费电子:WLP技术可用于制造小型、高性能的消费电子产品,如手机、平板电脑等。

五、创新要点1.技术创新:WLP技术是一种先进的封装技术,需要掌握核心技术,不断提升自主创新能力。

2.模式创新:WLP技术改变了传统的封装模式,实现了更高效、更低成本的生产模式。

半导体生产技术从晶圆制备到封装测试的全过程半导体产业是当今信息技术的核心和驱动力之一。

在电子设备中,几乎所有的芯片都是通过半导体生产技术制造而成的。

半导体生产技术从晶圆制备到封装测试,经历了一系列复杂的工艺流程,本文将对其全过程进行详细介绍。

一、晶圆制备晶圆制备是半导体生产技术的第一步,也是整个生产流程中的核心环节之一。

晶圆是一种具有高纯度的硅材料,制备晶圆需要经过以下几个步骤:1. 衬底准备:衬底是晶圆的基础材料,常用的材料是硅。

在制备晶圆之前,需要对衬底进行清洗和化学处理,以确保其表面的纯净度和平整度。

2. 晶体生长:晶体生长是指将衬底材料通过化学反应或物理沉积的方法制成高纯度的硅晶体。

常用的晶体生长方法包括气相沉积法、液相生长法和溅射法等。

3. 切割晶圆:经过晶体生长后的硅块被切割成薄片,即晶圆。

晶圆的厚度和直径可以根据具体需求进行调整。

二、晶圆加工晶圆加工是指对晶圆进行一系列的工艺处理,以形成电子器件的结构和功能。

晶圆加工主要包括以下几个步骤:1. 清洗和去膜:晶圆在加工之前需要进行清洗,以去除表面的杂质和污染物。

同时,一些表面氧化层也需要去除,以提高器件的性能。

2. 氧化和沉积:晶圆的表面经过氧化或沉积处理,形成一层薄膜。

这些薄膜可以用于控制电子器件的电流、电压和介电性能等。

3. 光刻和蚀刻:光刻是指通过光源照射,将芯片设计图案转移到晶圆表面的技术。

而蚀刻则是使用化学物质去除晶圆表面的材料,形成电子器件的结构。

4. 渗透和离子注入:渗透是指将掺杂物质通过高温处理,使之渗入晶圆表面。

而离子注入则是通过离子轰击的方式,将离子注入晶圆内部,改变其导电性能。

5. 金属化和封装:晶圆经过金属化处理,以形成电子器件的引脚和电路连接。

然后,通过封装技术将晶圆封装成芯片。

三、封装测试封装测试是半导体生产技术的最后一步,也是确保电子器件质量和性能的重要环节。

封装测试主要包括以下几个步骤:1. 封装工艺:将芯片放置在塑料或陶瓷封装体中,并使用焊接或粘接技术将引脚与芯片连接起来。

晶圆的测试方法与流程(一)晶圆的测试方法与流程一、测试方法的选择 - 引言 - 传统测试方法 - 1. 探针测试 -2. 凸显光刻技术测试 -3. 基于射频电路测试 - 现代测试方法 - 1. 基于MEMS技术的测试 - 2. 声波检测测试 - 3. 无线通信测试二、探针测试流程 - 引言 - 测试前准备 - 1. 制备测试样品 -2. 准备测试设备 - 探针测试步骤 - 1. 设置测试参数 - 2. 探针接触测试样品 -3. 进行电性能测试 -4. 分析测试结果 - 测试结论与改进 - 1. 提取测试数据 - 2. 判定测试结果 - 3. 提出改进措施三、凸显光刻技术测试流程 - 引言 - 测试前准备 - 1. 准备测试材料 - 2. 安装光刻仪设备 - 光刻技术测试步骤 - 1. 设计测试图案 - 2. 草图转换为光刻模板 - 3. 将模板与样品结合 - 4. 进行光刻曝光 - 测试结果分析与改进 - 1. 观察光刻结果 - 2. 分析测试数据 - 3. 提出改进建议四、基于射频电路测试流程 - 引言 - 测试前准备 - 1. 准备测试样品 - 2. 配置测试设备 - 射频电路测试步骤 - 1. 设计测试方案- 2. 搭建测试电路 - 3. 进行信号发射与接收 - 4. 分析信号质量 - 测试结论与改进 - 1. 汇总测试数据 - 2. 判定信号性能 - 3. 提出改进方案五、基于MEMS技术的测试流程 - 引言 - 测试前准备 - 1. 准备测试样品 - 2. 配置测试设备 - MEMS测试步骤 - 1. 设计测试方案 - 2. 搭建测试平台 - 3. 施加测试力或电场 - 4. 观察及测量变化 -测试结果分析与改进 - 1. 提取测试数据 - 2. 分析测试结果 - 3.提出改进建议六、声波检测测试流程 - 引言 - 测试前准备 - 1. 准备测试样品 - 2. 安装测试设备 - 声波检测测试步骤 - 1. 设计声波测试模板- 2. 激发声波 - 3. 接收并分析声波信号 - 4. 提取声波特征 - 测试结论与改进 - 1. 汇总测试数据 - 2. 判定测试结果 - 3. 提出改进建议七、无线通信测试流程 - 引言 - 测试前准备 - 1. 准备测试设备 - 2. 配置测试环境 - 无线通信测试步骤 - 1. 设计测试方案 - 2. 进行信号发送与接收 - 3. 分析通信质量 - 4. 评估测试结果 - 测试结论与改进 - 1. 汇总测试数据 - 2. 判定通信质量 - 3. 提出改进建议综上所述,晶圆的测试方法与流程涉及多个方面的技术,包括探针测试、凸显光刻技术测试、基于射频电路的测试、基于MEMS技术的测试、声波检测测试和无线通信测试等。

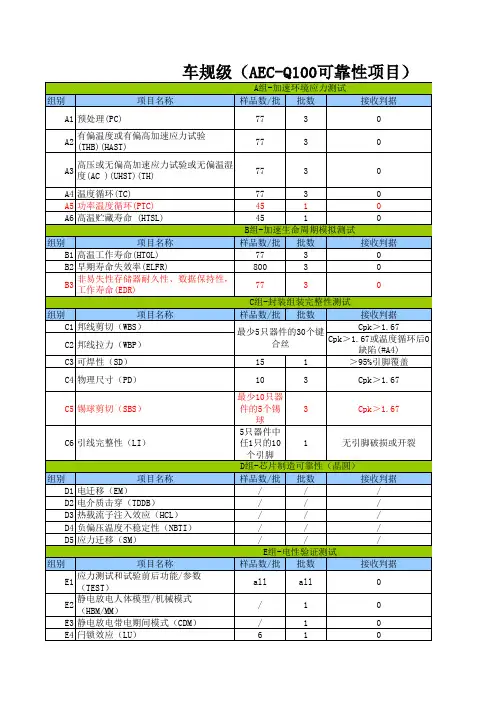

可靠性试验项目 项目 参考标准 检测目的

预处理PRE JESD22-A113F

模拟贴装产品在运输、贮存直到回流焊上整机受

到温度、湿度等环境变化的影响。

此试验应在可

靠性试验之前进行,仅代表产品的封装等级。

湿气敏感等级试验MSL IPC/JEDEC

J-STD-020

确定那些由湿气所诱发应力敏感的非气密固态

表面贴装元器件的分类, 以便对其进行正确的封

装, 储存和处理, 以防回流焊和维修时损伤元器

件。

稳态湿热THT GB/T2423.3

JESD22-A101

评定产品经长时间施加湿度应力和温度应力作

用的能力。

温度循环TCT JESD22-A104

GB/T 2423.22

评定产品封装承受极端高温和极端低温的能力,

以及极端高温和极端低温交替变化的影响。

高温试验HTST GB/T 2423.2

JESD22-A103

评定产品承受长时间高温应力作用的能力。

低温试验LTST GB/T 2423.1

JESD22-A119

评定产品承受长时间低温应力作用的能力。

高压蒸煮PCT JESD22-A102

评定产品封装的抗潮湿能力。

高速老化寿命试验(u)HAST JESD22-A110

JESD22-A118

评定非气密性封装在(无)偏置条件下的抗潮湿能

力。

回流焊Reflow JESD22-A113

评定产品在回流焊接过程中所产生之热阻力及

效应。

电耐久BURN-IN GB/T 4587

评定器件经长时间施加电应力(电压、电流)和

温度应力(产品因负载造成的温升)作用的能力。

高温反偏HTRB GB/T 4587

JESD22-A108

评定器件承受长时间电应力(电压)和温度应力

作用的能力。

耐焊接热SHT GB/T 2423.28

JESD22-B106

评定产品在其焊接时的耐热能力。

可焊性Solderability GB/T 2423.28

EIA/IPC/JEDEC

J-STD-002

评定产品的可焊性能力。

锡须生长

Tin Whisker Test JESD201

JESD22-A121

评定产品承受长时间施加温湿度应力作用下锡

须生长情况。

电性测试Electrical Test GB/T 4589.1

GB/T 4587

GB/T 4586

GB/T 4023

GB/T 6571

评定产品电性能力。

主要针对分立器件产品测

试。