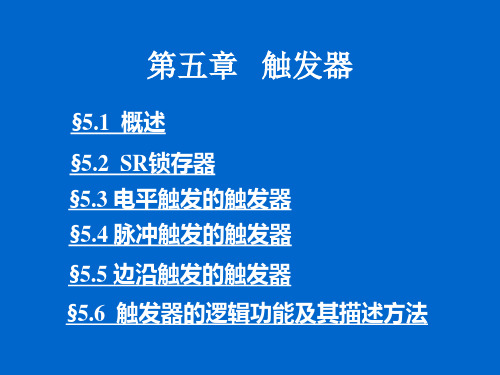

触发器

- 格式:doc

- 大小:1.39 MB

- 文档页数:8

触发器(基本的SR触发器、同步触发器、D触发器)⼀、能够存储1位⼆值信号的基本单元电路统称为触发器(Filp-Flop) 触发器是构成时序逻辑电路的基本逻辑部件。

它有两个稳定状态:“0”和“1”。

在不同的输⼊情况下,它可以被置0状态或1状态,当输⼊信号消失后,所置成的状态能够保持不变。

所以触发器可以记忆1位⼆值的信号。

根据逻辑功能的不同,触发器可以分为SR触发器、D触发器、JK触发器、T和T'触发器。

按照结构形式的不同,⼜可分基本SR触发器、同步触发器、主从触发器和边沿触发器。

其状态图:a、当触发器处在0状态,即Q = 0,若S'R' = 10或11时,触发器仍为0状态。

若S'R' = 01,触发器翻转成为1状态。

b、当触发器处在1状态,即Q = 1,若S'R' = 01或11时,触发器仍为1状态。

若S'R' = 10,触发器翻转成为0状态。

约束条件是S’R’不能同时为0。

代码实现:module RS(rst_n,r,s,q,qn);input rst_n;input r;input s;output q;output qn;reg q;reg i;always @(rst_n or q)if(!rst_n)i = 0;else if(!q)i = 0;elsei = 1;always @(rst_n or r or s)if(!rst_n)q = 0;elsecase(i)0://置0if(({r,s} == 2'b01) || ({r,s} == 2'b11))q = 0;else if(({r,s} == 2'b10))q = 1;1://置1if(({r,s} == 2'b10) || ({r,s} == 2'b11))q = 1;else if(({r,s} == 2'b01))q = 0;endcaseassign qn = ~q;endmoduleView Code仿真代码:`timescale 1ns/1nsmodule RS_top;reg rst_n;reg r;reg s;wire q;wire qn;initial beginrst_n = 0;#10;rst_n = 1;beginr = 0;s = 1;#20;r = 1;s = 1;#20;r = 1;s = 0;#20;r = 1;s = 1;#20;endendRS rs1(.rst_n(rst_n),.r(r),.s(s),.q(q),.qn(qn));endmoduleView Code仿真波形:可以看到仿真结果是对的。

111第12章 集成触发器教学重点:1.掌握基本RS 触发器的电路组成、工作原理。

2.掌握同步RS 触发器的电路组成、工作原理。

3.掌握主从RS 触发器、JK 触发器、D 触发器、T 触发器的逻辑功能。

教学难点:1.基本RS 触发器的工作原理。

2.空翻现象出现的原因。

3.主从触发器的工作原理分析。

4.触发器的应用。

学时分配:12.1 集成触发器的基本形式触发器是一种具有记忆功能并且其状态能在触发脉冲作用下迅速翻转的逻辑电路。

基本RS 触发器是各种触发器的基础。

12.1.1 基本RS 触发器一、电路组成将两个集成与非门的输出端和输入端交叉反馈相接,就组成了基本RS 触发器。

1.电路组成基本RS 触发器如图12.1.1(a )所示。

图12.1.1 基本RS 触发器112两个与非门G 1、G 2;两个输入端D D S R 、;两个输出端Q 、Q ,逻辑状态是互补的。

2.工作原理动画 基本RS 触发器 Q 端的状态为触发器的状态。

工作状态:10==Q Q ,时触发器处于“0”态(稳定状态);01==Q Q ,时触发器处于“1”态(稳定状态)。

二、逻辑功能1.逻辑符号基本RS 触发器的逻辑符号参见图11.1.1(b )。

2.逻辑功能基本RS 触发器的逻辑功能如下: 当10D D ==S R ,时,则)(10==Q Q ; 当01D D ==S R ,时,则)(01==Q Q ; 当11D D ==S R ,时, 则Q 不变(Q 不变);当00D D ==S R ,时,则Q 不定(Q 不定);这是不允许的。

3.真值表表12.1.1给出了基本RS 触发器真值表表12.1.1 基本RS 触发器真值表D R ——置0端、D S ——置1端,均由负脉冲触发,符号R D 、S D上加了非号,表示低电平有效。

4.概念触发器的翻转:触发器状态在外加信号作用下状态转换的过程。

触发脉冲:能使触发器发生翻转的外加信号。

12.1.2 钟控同步RS 触发器一、电路组成1.电路组成如图12.1.2(a )所示。

一个基本RS 触发器;两控制门(G3、G4)。

2.逻辑符号如图12.1.2(b )所示。

CP 端无小圆圈――正脉冲(CP 上升沿)触发有效。

3.主控脉冲 (协同工作触发脉冲时钟脉冲):图12.1.2 钟控同步RS 触发器113控制数字系统中各触发器,用CP 表示。

二、工作原理 1.工作原理CP = 0时,G3、G4输出为1,触发器维持原态; CP = 1时,触发器状态由R 、S 决定(见真值表)。

2.真值表表12.1.2 钟控同步RS 触发器真值表3.说明n Q 表示时钟作用前触发器的状态,称原状态;1+n Q 表示时钟作用后触发器的状态,称现状态。

当S n = 1、R n = 1时,时钟脉冲过后,电路状态不定,这是不允许的。

4.钟控同步RS 触发器:由时钟脉冲控制的RS 触发器。

5.注意D S 、D R ,只在时钟脉冲工作前使用;在时钟脉冲工作过程中应将其悬空或接高电平。

12.2 计数触发型钟控同步RS 触发器及其空翻现象12.2.1 计数触发型钟控同步RS 触发器触发器的主要用途之一就是构成计数电路,完成计数功能。

1.计数触发型钟控同步RS 触发器:电路构成特点:在一个钟控同步RS 触发器基础上,将控制门G 3、G 4的输入端R 、S 分别与触发器的输出端Q 和Q 相连。

如图12.2.1所示。

2.工作原理设触发器的初始状态为0,则0,1====Q R S ;当第一个计数脉冲到来(即CP = 1)时,Q 由0变1、Q 由1变0;当第一个CP 作用后,S = Q = 0、R = Q = 1:当第二个CP 到来时,触发器置0。

结论,每来一个计数脉冲,触发器就翻转一次,触发器翻转的次数反映了计数脉冲的数目,实现了计数功能。

12.2.2 计数触发型钟控同步RS 触发器的空翻现象1.正常工作条件:时钟脉冲的宽度必须足够窄。

1142.出现问题:空翻现象。

空翻现象――若时钟脉冲较宽,造成触发器动作混乱,在一个时钟脉冲内出现多次翻转。

12.3 防止空翻的触发器举例主从RS 触发器是一种能防止空翻的触发器。

1.电路结构电路结构如图12.3.1所示。

由两个同步触发器构成:主触发器由G 5、G 6、G 7、、G 8组成;从触发器由G 1、G 2、G 3、G 4组成。

2.工作原理设触发器始态为Q = 0(即从触发器Q = 0,主触发器Q '= 0),计数脉冲从CP 处输入。

当CP = 1时,主触发器状态翻转,Q ' = 1;从触发器不能翻转,输出Q = 0不变。

当CP = 0时,主触发器不翻转,Q ' = 1不变;从触发器翻转,Q = 1。

3.工作特点从触发器的状态由主触发器决定;主从触发器只在每个输入CP 脉冲的下降沿翻转一次,与CP 脉冲的宽度无关,从而避免空翻现象。

12.4 几种逻辑功能不同的触发器12.4.1 JK 触发器一、电路结构电路结构和逻辑符号如图12.4.1所示。

动画 JK 触发器图12.2.1 钟控同步RS 触发器接成计数器 图12.3.1 主从触发器逻辑图115边沿触发器:触发器状态只取决于CP 上升(或下降)沿时刻的输入信号状态(例如:J 端或K 端电平)的触发器。

图12.4.2 主从JK 触发器的工作波形 图12.4.3 用JK 触发器接成的T 型触发器12.4.2 T 触发器一、电路结构 如图12.4.3所示。

结构特点:把JK 触发器的J 端和K 端相接作为控制端,称为T 端。

如图12.4.3所示。

动画 T 触发器 二、逻辑功能1.逻辑功能当J = K = 0时,触发脉冲不起作用;当J = K = 1时,每来一次触发脉冲,触发器翻转一次,即n n Q Q =+1。

2.真值表表12.4.2 T 型触发器真值表图12.4.1 JK 触发器1163.用途:计数。

当T = 0时,触发器无计数功能; 当T = 1时,触发器具有计数功能。

12.4.3 D 触发器一、电路结构在JK 触发器的K 端,串接一个非门,再接到J 端,引出一个控制端D ,就组成D 触发器。

如图12.4.4所示。

二、逻辑功能 1.逻辑功能D 型触发器是JK 触发器在J ≠ K 条件下的特殊情况电路。

在时钟脉冲作用后,触发器状态与D 端状态相同,即D Q n =+12.真值表表12.4.3 D 型触发器真值表12.5 触发器的型号及应用举例12.5.1 触发器的型号及外引线示例类型:有TTL 和CMOS 两种电路。

如图12.5.1所示说明:1.符号上加横线的,表示负脉冲(低电平)有效;不加横线的,表示正脉冲(高电平)有效。

NC 表示空脚。

2.双触发器以上其输入、输出符号前写同一数字的,表示属于同一触发器。

3.V CC 电源一般为 +5 V ,V DD 电源一般为 + 3 ~ 18V 。

12.5.2 触发器简单应用实例一、分频器图12.4.4 用JK 触发器接成的D 型触发器图12.5.1 几种JK 和D 型触发器外引线排列图117如图12.5.2所示。

应用一片CC4027双JK 集成触发器中一个单元电路,可构成2分频器。

从1CP 端输入2个时钟脉冲,则在1Q 的输出端只输出1个脉冲,实现了2分频。

即I O 21f f图12.5.2 二分频器 图12.5.3 多路控制的开关电路二、多路控制的开关电路如图12.5.3所示。

用一片CC4013正边沿触发双D 集成触发器中的一个D 触发器构成多路控制开关电路。

设未接通任何开关时,D 触发器处于0态,继电器失电不工作。

当按动任意一只开关后,继电器得电工作;开关断开后,不影响继电器工作。

再按动任意一只开关,继电器失电而停止工作。

三、抢答电路如图12.5.4所示。

用一片CT74LS175四D 触发器可构成四人智力竞赛抢答电路。

图12.5.4 四人抢答电路抢答前,各触发器清零,四只发光二极管均不亮。

抢答开始后,假设S 1先按通,则1D先为1,当CP脉冲上升沿出现时,点亮LED1;其他按钮随后按下相应的发光二极管不会亮。

若要再次进行抢答,只要清零即可。

本章小结一、触发器是一种具有记忆功能而且在触发脉冲作用下会翻转状态的电路。

它具有两种可能的稳态――0态或1态。

当触发脉冲过后,触发器状态仍维持不变,这就是记忆能力。

二、触发器按逻辑功能分为:RS型、JK型、D型、T型等等。

基本RS触发器――是各种触发器的基础;钟控同步RS触发器――具有计数功能,但易发生空翻现象;主从RS触发器――可以防止空翻现象发生,同时具有计忆功能。

JK触发器、D触发器是应用广泛的触发器;T触发器具有计数功能。

118。