dSPACE串口通信.

- 格式:ppt

- 大小:520.50 KB

- 文档页数:29

dSPACE*** 基于Matlab/Simulink平台***实时快速原型及硬件在回路仿真的一体化解决途径1概述在当今社会,市场对产品的需求呈现多样性、快速性的趋势,这就使企业的新品开发面临着多样性需求与快速开发之间的矛盾;同时对控制系统鲁棒性及可靠性的要求也日益增加;另外并行工程(即:设计、实现、测试和生产准备同时进行)被提上了日程。

DSPACE 的产品为并行工程的实现创造了一个良好的环境。

对于进行控制算法研究的工程师而言,最头疼的莫过于没有一个方便而又快捷的途径,可以将他们用控制系统设计软件 (如MATLAB/Simulink) 开发的控制算法在一个实时的硬件平台上实现,以便观察与实际的控制对象相连时,控制算法的性能;而且,如果控制算法不理想,还能够很快地进行反复设计、反复试验直到找到理想的控制方案。

对一些大型的科研应用项目,如果完全遵循过去的开发过程,由于开发过程中存在着需求更改,软件代码甚至代码运行硬件环境不可靠(如:新设计制造的控制单元存在缺陷)等问题,最终导致项目周期长、费用高,缺乏必要的可靠性,甚至还可能导致项目以失败告终。

这就要求在开发的初期阶段就引入各种试验手段,并有可靠性高的实时软/硬件环境做支持。

另外,当产品型控制器生产出来后,测试工程师又将面临一个严重的问题。

由于并行工程的需求,控制对象可能还处于研制阶段,或者控制对象很难得到,用什么方法才能在早期独立地完成对控制器的测试呢?我们将这些问题概括为两种:快速控制原型(RCP)和硬件在回路仿真(HILS)。

d SPACE 提供了这两方面应用的统一平台。

2Dspace介绍dSPACE实时仿真系统是由dSPACE公司开发的一套基于MA TLAB/Simulink的控制系统开发及测试的工作平台,实现了和MATLAB/Simulink的完全无缝连接。

dSPACE实时系统拥有具有高速计算能力的硬件系统,包括处理器、I/O等,还拥有方便易用的实现代码生成/下载和试验/调试的软件环境。

(完整版)DSPACE应⽤简介dSPACE 实时仿真平台软件环境及应⽤⼀、dSPACE 简介dSPACE实时仿真系统是由德国dSPACE公司开发的⼀套基于MATLAB/Simulink 的控制系统在实时环境下的开发及测试⼯作平台,实现了和MATLAB/Simulink 的⽆缝连接。

dSPACE 实时系统由两⼤部分组成,⼀是硬件系统,⼆是软件环境。

其中硬件系统的主要特点是具有⾼速计算能⼒,包括处理器和I/O 接⼝等;软件环境可以⽅便地实现代码⽣成/下载和试验调试等⼯作。

dSPACE 具有强⼤的功能,可以很好地完成控制算法的设计、测试和实现,并为这⼀套并⾏⼯程提供了⼀个良好的环境。

dSPACE 的开发思路是将系统或产品开发诸功能与过程的集成和⼀体化,即从⼀个产品的概念设计到数学分析和仿真,从实时仿真实验到实验结果的监控和调节都可以集成到⼀套平台中来完成。

dSPACE 的软件环境主要由两⼤部分组成,⼀部分是实时代码的⽣成和下载软件RTI(Real-Time Interface),它是连接dSPACE 统与MATLAB/Simulink 纽带,通过对RTW(Real-Time Workshop)进⾏扩展,可以实现从Simulink 模型到dSPACE 实时硬件代码的⾃动下载。

另⼀部分为测试软件,其中包含了综合实验与测试环境(软件)ControlDesk、⾃动试验及参数调整软件MLIB/MTRACE、PC 与实时处理器通信软件CLIB 以及实时动画软件RealMotion 等。

⼆、dSPACE的优点dSPACE 实时仿真系统具有许多其它仿真系统具有的⽆法⽐拟的优点:1、dSPACE 组合性很强。

2、dSPACE 的过渡性和快速性好。

由于dSPACE 和MATLAB 的⽆缝连接,使MATLAB ⽤户可以轻松掌握dSPACE 的使⽤,⽅便地从⾮实时分析、设计过渡到实时的分析和设计上来,⼤⼤节省了时间和费⽤。

3、性能价格⽐⾼。

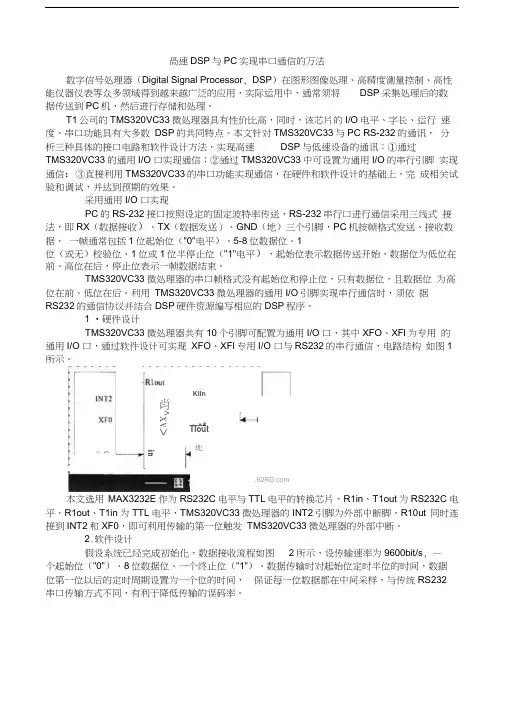

咼速DSP与PC 实现串口通信的万法数字信号处理器(Digital Signal Processor , DSP )在图形图像处理、高精度测量控制、高性能仪器仪表等众多领域得到越来越广泛的应用,实际运用中,通常须将 DSP 采集处理后的数 据传送到PC 机,然后进行存储和处理。

T1公司的TMS320VC33微处理器具有性价比高,同时,该芯片的I/O 电平、字长、运行 速度、串口功能具有大多数 DSP 的共同特点。

本文针对TMS320VC33与PC RS-232的通讯, 分析三种具体的接口电路和软件设计方法,实现高速 DSP 与低速设备的通讯:①通过TMS320VC33的通用I/O 口实现通信;②通过TMS320VC33中可设置为通用I/O 的串行引脚 实现通信;③直接利用TMS320VC33的串口功能实现通信,在硬件和软件设计的基础上,完 成相关试验和调试,并达到预期的效果。

采用通用I/O 口实现PC 的RS-232接口按照设定的固定波特率传送,RS-232串行口进行通信采用三线式 接法,即RX (数据接收)、TX (数据发送)、GND (地)三个引脚,PC 机按帧格式发送、接收数据, 一帧通常包括1位起始位("0"电平)、5-8位数据位、1位(或无)校验位、1位或1位半停止位("1"电平),起始位表示数据传送开始,数据位为低位在 前、高位在后,停止位表示一帧数据结束。

TMS320VC33微处理器的串口帧格式没有起始位和停止位,只有数据位,且数据位 为高位在前、低位在后。

利用 TMS320VC33微处理器的通用I/O 引脚实现串行通信时,须依 据RS232的通信协议并结合DSP 硬件资源编写相应的DSP 程序。

1 •硬件设计TMS320VC33微处理器共有10个引脚可配置为通用I/O 口,其中XFO 、XFl 为专用 的通用I/O 口,通过软件设计可实现 XFO 、XFl 专用I/O 口与RS232的串行通信,电路结构 如图1所示。

实验八、UART串口通信实验一、实验目的1. 了解RS232通信接口的基本原理;2. 熟悉通信接口芯片(TL16C550C)在DSP I/O空间寄存器的地址映射及工作原理;3.了解异步通信中串口模式选择、设置数据传输格式、设置波特率、建立连接、传输数据和断开连接等功能。

二、实验设备1. 集成开发环境CCS2. 实验开发板TMS320VC5402DSK、RS232接口电缆线及附件3.程序“串口调试程序v2.2.exe”三、实验内容及步骤实验操作流程参照前面实验。

1 在汇编环境调试Uart:(实现字符或文件的发送和回发功能)a. 实验代码main.s54、uartasm.cmd和uart_init.s54、dsp_init.s54以及uartasm.h54,c5402_dsk.gel(说明同前)。

b. 串口调试程序“串口调试程序v2.2.exe” , 汇编调试中Buildoption设置情况与CODEC实验中的汇编调试设置及出错情况相同。

c. 程序文件介绍:1)“uart.h54”定义了一些寄存器的地址以及函数类型。

2)“dsp_init.s54”与dsp工作有关的寄存器ST1、PMST、IMR、IFR和SWWSR,并且清除INTM位以及设定时钟模式。

3)“uart_init.s54”先检测UART模块是否工作正常,然后设定UART模块的寄存器,如CNTL1、CNTL2、LCR、MSB&LSB(设定波特率)、FCR、IER 等。

4)“main.s54”主程序查看标志位,检测是否UART存在有效接收数据。

若有,则执行一定的处理,包括亮LED以及将接收的数据从UART回发。

d. 执行程序时,只要发送数据时,可在串口调试程序的接收窗口立即看到回发的数据。

e. 程序中UART工作参数设置如下:1)波特率9600(或更低)、无数据校验、字符长度8比特、停止位1、2 均可;2) 接收区自动清空不选、十六进制显示可选可不选;发送区不能选十六进制发送,可发送字符和文件两种方式;3) IER允许数据就绪中断和线路状态中断;4) FIFO不使能,所以,在用串口程序调试时,只能单个字符发送,如“x”。

摘要进入21世纪之后,数字化浪潮正在席卷全球,数字信号处理器DSP(Digital Signal Processor)正是这场数字化革命的核心,无论在其应用的广度还是深度方面,都在以前所未有的速度向前发展。

数字信号处理是利用计算机或专用处理设备,以数字的形式对信号进行分析、采集、合成、变换、滤波、估算、压缩、识别等加工处理,以便提取有用的信息并进行有效的传输与应用。

DSP可以代表数字信号处理技术(Digital Signal Processing),也可以代表数字信号处理器(Digital Signal Processor)。

前者是理论和计算方法上的技术,后者是指实现这些技术的通用或专用可编程微处理器芯片。

本文就是就是基于DSP原理及应用编写设计的同步串口通信在TMS320C643上实现。

其集成开发环境为CCS,工作平台是SEED-DTK 。

CCS 是TI公司推出的用于开发DSP芯片的集成开发环境,它采用Windows风格界面,集编辑、编译、链接、软件仿真、硬件调试以及实时跟踪等功能于一体,极大地方便了DSP芯片的开发与设计,是目前使用最为广泛的DSP开发软件之一。

SEED-DTK(DSP Teaching Kit)是一套可以满足大学本科、研究生和教师科研工作的综合实验设备。

SEED-DTK 是我公司在总结以往产品的基础上,以独特的多DSP 结构、强大的DSP 主板功能、丰富的外围实验电路、精心设计的实验程序、精湛的产品工艺形成的高性能产品。

关键字:同步串口通信 DSP CCS SEED-DTK目录一.功能描述 ---------------------------------------------------------- 3二.概要设计 ---------------------------------------------------------- 32.1 McBSP 介绍------------------------------------------------- 32.2 设计目的------------------------------------------------------ 42.3 设计概要------------------------------------------------------ 4三.详细设计 ---------------------------------------------------------- 43.1 实验程序功能与结构说明 -------------------------------- 43.2 程序流程图 ---------------------------------------------------- 5四.调试过程及效果 ------------------------------------------------- 54.1 实验准备------------------------------------------------------ 54.2 调试过程及效果 -------------------------------------------- 64.2.1 创建源文件 -------------------------------------------- 64.2.2 创建工程文件 ----------------------------------------- 74.2.2 设置编译与连接选项 -------------------------------- 84.2.3 工程编译与调试 ------------------------------------ 10 五.存在问题 -------------------------------------------------------- 12 六. 心得-------------------------------------------------------------- 12 七.参考文献 -------------------------------------------------------- 12 附录(源程序) ----------------------------------------------------- 13一.功能描述数字信号处理器由于具有高性能和灵活可编程的优点而得到广泛的应用 ,在许多应用系统中,实现DSP与 PC机之间有效可靠的通信是系统设计的重要部分。

DSP与PC间高速串口通信的实现DSP与PC间高速串口通信的实现类别:通信网络 作者:北京理工大学电子工程系信息系统实验室王卫江陶然徐元军来源:《电子产品世界》摘要:利用UART解决DSP与PC机间通信时速率匹配问题,并给出了具体实现电路。

关键词:DSPUART 串行通信 FIFODSP是一种专门用来实现信号处理算法的微处理器芯片,主要优点有:硬件乘法器,哈佛总线结构,多种寻址方式,零耗循环(zero overhead loop),程序执行时间可预测等。

正是由于DSP的诸多优点能够满足密集的数学计算,而且DSP应用的另一个突出特点是实时性,使其在通信、雷达、数字电视等领域得到了广泛的应用,而且日益渗透到人们的日常生活的各个方面。

在实时信号处理中已经离不开DSP,这些处理系统中包含了各种数据通信,例如DSP与DSP间数据通信,DSP与PC机间数据通信等。

如何能够快速、准确的完成通信是每个硬件工程师所关心的问题。

由于DSP的工作频率较高,如TMS320C6201时钟频率为200MHz,ADSP21060时钟频率为40MHz,故其数据读写周期很短,然而PC机串口读写速度较低,最大数据吞吐量约为115kbps,尽管DSP在与这些慢速外设进行数据交换时可以加入额外的等待周期,但是在实时性要求苛刻,算法复杂的场合,将DSP从这些冗长的等待周期中解放出来,将其时间重点放在处理关键的实时任务中去,有着重要的实际意义。

故DSP与PC机之间串口通信的速度匹配是保证快速、准确通信的关键。

PC机一般带有一个或两个内置串口,每个端口的机箱背后有一个9针或25针的公插口。

串口是以bit来传输数据的,传输速率取决于UART芯片。

该芯片将PC总线上的并行数据(单字节或多字节)分割成以比特为单位的串行数据流,从而实现在串口线缆中的数据传输。

现在几乎所有的PC机都带有16550UART用以实现并行数据和串行数据的格式转换,它的最大数据吞吐量为115kbps,这已经能够满足大多数串行设备的需要了。

摘要:全双工异步串行通信在TMS320C55xDSP上的通常实现方式是利用DSP的McBSP接口加外接芯片实现,这种设计方法增加了实现UART的硬件成本和电路设计复杂度。

提出了一种直接利用DSP的MCBSP接口和DMA通道实现UART的方法,给出了使用C语言和CSL的编程方法。

与传统实现方法相比,具有实现成本低,硬件电路简单,移植性强等特点,稍加修改可应用于C5000和C6000各系列芯片中。

关键词:DSP;全双工异步串行通信;多通道缓冲串口;DMA ;过采样1 引言:MS320C55x数字信号处理器通过多通道缓冲串口(McBSP)提供了与外设的多种同步串行通信方式。

然而,由于DSP 中串行通信由数据信号、帧同步信号和时钟3种信号配合实现,其中帧同步信号和数据信号由不同的数据线传输。

而异步串行通信则在一根传输线上实现数据发送或接收,且不需要专门的时钟信号线。

因此DSP与异步设备的接口,如UART通信实现相对复杂,需要对McBSP的相关寄存器进行正确初始化。

DSP中实现全双工异步通信的通常做法是使用专用的串行接口芯片,如TL16C550,这种设计方法编程相对简单,但增加了设计成本和电路复杂度。

本文介绍了一种TMS320C55x DSP芯片利用McBSP和DMA直接实现UART的方法,基于该方法实现的DSP异步串行通信模块已成功应用于控制偏振图像采集处理的DSP硬件设备中。

2 UART在DSP上的实现异步串行通信要求DSP能够模拟和检测到UART的帧信号。

由于DSP串口是同步串口,而且DSP时钟为高速时钟,经分频或倍频后无法保证与UART的异步串行时钟精确同步。

DSP的帧同步信号无法与UART的帧信号同步,造成串行通信信号中信号位的偏移。

最好的解决方法是减小偏移和对接收的数据流进行过采样,本文采用了对UART信号的16倍过采样。

/2.1 McBSP设置DSP的McBSP通过3种信号实现同步通信:数据、帧同步和时钟。

课程设计报告( 2014 -- 2015年度第二学期)课程名称:DSP课程设计题目:基于DSP实验系统的串口通信院系:电子与通信工程系班级:电子学号:学生姓名:指导教师:设计周数: 2成绩:日期:2015 年7月16日一、课程设计的目的与要求1.设计方案:通过TMS320C5509A的串口与电脑进行通信,利用串口调试助手发送数据,由DSP接收到,DSP读到收到数据进行下一步的让四位LED灯亮,实现数据的通信,并在lcd12864上显示发送的数据,还有显示拨码开关的数值。

2.设计指标:电脑只能发送0~15,因为读出数据的时候比较方便解码,比如发送4就可以直接给LED直接赋值,让第三个灯亮,也就是一般的二进制转换。

二、设计正文1.设计思路(系统组成介绍)串口模块:TL16C550 是一个标准的串口接口芯片,它的控制寄存器基地址为0x400200,寄存器占用TMS320VC5509 的8 个地址单元。

串口中断与TMS320VC5509 的INT0 连接。

用户可以使用TMS320VC5509 的中断0 响应串口中断。

TL16C550 有11 个寄存器,这11 个寄存器是通过TMS320VC5509 的3 个地址线(A3~A1)和线路控制寄存器中的DLAB 位对它们进行寻址的。

板上加上16C550、Max232 和驱动电路。

驱动电路主要完成将输出的0-3.3V 电平转换成异步串口的工作电平,转换电平的工作由MAX232 芯片完成,但由于它是5V 器件,所以它同DSP 间的信号线必须有电平转换,此板采用的是74LVC245。

实验箱上的液晶模块采用的型号是TJDM12864MTJDM12864M 是一款带中文字库的图形点阵模块,由动态驱动方式驱动128×64 点阵显示。

低功耗,供应电电压范围宽。

内含多功能的指令集,操作简易。

采用COB 工艺制作,结构稳固,使用寿命长。

特性:1.提供 8 位,4 位及串行接口可选2.64×16 位字符显示 RAM(DDRAM 最多 16 字符×4 行,LCD 显示范围 16×2 行)3.2M 位中文字型 ROM(CGROM),总共提供 8192 个中文字型(16×16 点阵)4.16K 位半宽字型 ROM(HCGROM),总共提供 126 个西文字型(16×8 点阵)5.64×16 位字符产生 RAM(CGRAM)6.15×16 位总共 240 点的 ICON RAM(ICONRAM)7.自动复位(RESET)功能8.绘图及文字画面混合显示功能9.提供多功能指令:——画面清除(display clear)——游标归位(return home)——显示开/关(display on/off)——游标显示/隐藏(cursor on/off)——字符闪烁(display character blink)——游标移位(cursor shift)——显示移位(display shift)——垂直画面旋转(vertical line scoll)——反白显示(By-line reverse display)——睡眠模式(sleep mode)DSP与LCD的连接:3.软件设计流程:4.在试验箱上模拟实现用随实验箱附带的串口线(两端均为9 孔“D”形插头)连接计算机com1 或com2 插座和ICETEK–VC5509-A 板上标准RS-232 插座,编译、下载、运行。

Rx3i PacSystem919-535-3180*******************GE Fanuc IC695CMM002/automation/ge-fanuc/rx3i-pacsystem/IC695CMM002RX3i serial communications module. Two isolated RS-232/485 port.IC695C IC695CM IC695CMMPACSystems™ RX3iIC695CMM002 and IC695CMM004 GFK-2461B Serial Communications Modules August 2007communications capabilities of the RX3i system.in the main PACSystems RX3i backplane.module can only be configured for DNP3 Master or Slave.Additional module features include:▪Port-to-port isolation and port-to-backplane isolation▪▪Hardware handshake: RTS/CTS for RS-232▪57.6K, 115.2K▪▪indicators▪▪Flash memory for future upgradesThese modules must be located in an RX3i Universal Backplane.RX3i Serial Communications can be hot-inserted and removedfollowing the instructions in the PACSystems RX3i System Manual,GFK-2314.2 RX3i Serial Communications Modules GFK-2461BRelease InformationThis release is an upgrade of previous version 1.10.Release HistoryRelease UpgradeKitCommentsIC695CMM002-AA IC695CMM004-AA N/A InitialReleaseIC695CMM002-AB IC695CMM004-AB 44A753277-G0244A753278-G02Supports CCM Slave ProtocolIC695CMM002-AC IC695CMM004-AC 44A753277-G0344A753278-G03Supports DNP3 Master and DNP3 Slave ProtocolNew for this ReleaseThis release of the RX3i Serial Module adds support for Distributed Network Protocol 3.0 Master and Slave to the other protocols: MODBUS Master/Slave, CCM, and Serial I/O. This module does not operate with COMMREQs but rather uses preconfigured mappings of the I/O reference memory.MODBUS Master and MODBUS Slave Protocols now support the configuration of 1 stop bit, for compatibility with some GE Fanuc Automation MODBUS Slaves.CompatibilityProgrammer: Proficy® Machine Edition Logic Developer 5.6 with Service Pack 2 SIM 10RX3i CPU: PACSystems RX3i CPU Version 5.00 or later is required to be able to use the timesynchronization feature on a DNP3 Master port.Problems Resolved for This ReleaseWhen parity is set to none in the port configuration for the Modbus Master or Modbus Slave protocols, the stop bits were forced to 2. This restriction has now been removed and the stop bits can be set to 1 or 2.RX3i Serial Communications Modules 3GFK-2461BRestrictions and Open Issues in this Release1. When multiple group objects (i.e. %I and %AI memory) are read in a single request, the DNP3 port willignore all but the first object. Operations of multiple group objects should be split into multiple successiveexchanges (i.e. exchange 1 - %I, exchange 2 - %AI).2. The DNP3 slave port has problems using the link layer to validate frame receipt. The DNP3 organizationencourages users not to do this.3. These modules do not support GE Fanuc special MODBUS commands for use with a Daniels FlowComputer.4. PLC Reference Address and Reference Length Parameters do not support bit length/start. Bit and Non-Byte Length operations must begin on a byte boundary.5. When a port is configured for CCM Slave protocol, and:▪ a new configuration is stored to the PLC using Machine Edition, or▪the system is power-cycled, or▪the module is hot-inserted,if the first query received from the CCM Master is a Read Scratchpad request, the module will reject thatrequest. All subsequent Read Scratchpad requests will be successful unless one of the above conditionsoccurs again.Operating NotesThe maximum resolution for the MODBUS drop delay is 420us, so the minimum time for a drop delay is 420us.Installation in Hazardous Locations•EQUIPMENT LABELED WITH REFERENCE TO CLASS I, GROUPS A, B, C & D, DIV. 2 HAZARDOUSLOCATIONS IS SUITABLE FOR USE IN CLASS I, DIVISION 2, GROUPS A, B, C, D OR NON-HAZARDOUSLOCATIONS ONLY•WARNING - EXPLOSION HAZARD - SUBSTITUTION OF COMPONENTS MAY IMPAIR SUITABILITY FOR CLASSI, DIVISION 2;•WARNING - EXPLOSION HAZARD - WHEN IN HAZARDOUS LOCATIONS, TURN OFF POWER BEFOREREPLACING OR WIRING MODULES; AND•WARNING - EXPLOSION HAZARD - DO NOT CONNECT OR DISCONNECT EQUIPMENT UNLESS POWER HASBEEN SWITCHED OFF OR THE AREA IS KNOWN TO BE NONHAZARDOUS.4 RX3i Serial Communications ModulesGFK-2461BSpecifications: IC695CMM002 and IC695CMM004Refer to the PACSystems RX3i System Manual , GFK-2314, for product standards and general specifications.Number of Serial PortsIC695CMM002: two independent serial ports IC695CMM004: four independent serial portsConnectors RJ-45 Number of Serial Communications Modules per CPU Six in the main CPU backplaneIC695CMM002 ********************************************Backplane power requirementsIC695CMM004********************************************LEDs Module OK, Port Fault, Port Status (2 or 4)Port TypeRS-232 or RS-485/22. 4-wire (full duplex) or 2-wire (half-duplex) operation for RS-485/422Flow Control for R-232 Selectable: Hardware (CTS/RTS) or noneBaud rates 1200, 2400, 4800, 9600, 19.2K, 38.4K, 57.6K, 115.2k Parity Even, odd, noneData bits 7, 8 Stop bits1, 2Operating Temperature 0°C to + 60°CInput Impedance Zin > 96 kOhm for RS-485/422 3 kOhm < Zin < 7 kOhm for RS-232 Max Overvoltage +/- 25VChannel-Channel Crosstalk –55dB minimumIsolationPort to Backplane and to frame ground: 250 VAC continuous; 1500 VAC for 1 minute, 2550VDC for one second. Port to port: 500VDC continuous, 710VDC for one minute.In order to meet emission and immunity requirements for the EMC directive (CE mark), shielded cable must be used with this module.RX3i Serial Communications Modules 5GFK-2461BLEDsSerial PortsEach port is a standard RJ-45 female connector with the following pin assignments. For MODBUS applications,note that these pin assignments are different than the standard MODBUS pin assignments. If the port isconfigured for MODBUS master or slave operation, custom cables are needed.6 RX3i Serial Communications Modules GFK-2461BIf the Serial Communications module is communicating with a Series 90-30 CPU363 or external PACSystemsRX3i CPU, the connections are:RX3i Serial Module CPU363/RX3iRD('B')T+ ToT- ToRD('A')SD('B')R+ ToSD('A')R- ToTerminationBy default, each port is set for no termination. Termination is needed if the module is the first or last device on an RS-485 network, even if there is only one other device on the network. Termination can be provided using either an external resistor as shown below or the port’s built-in 120-Ohm termination. If line termination other than 120 Ohms is required, an appropriate external resistor must be supplied.User-Supplied Termination for RS-485Termination using the built-in 120-Ohm resistor can be provided by either setting the appropriate RS-4851. Remove the module’s faceplate by pressing in on the side tabs and pulling the faceplate away from themodule.2. With the module oriented as shown, move either the upper or lower jumper:。

摘要:基于嵌入式系统发展的需要,提出TMS320VC5402 DSP与AT89C51单片机通信的三种设计方案。

利用TMS320VC5402的多通道缓冲串口MCBSP分别实现TM S320VC5402与AT89C51的SCI和SPI串行通信,以及通过TMS320VC5402的8位增强主机接口HPI一8实现TMS320VC5402与AT89C5l并行通信。

就硬件接口电路和软件编程进行详细的阐述。

关键词:单片机 DSP MCBSP HPI将DSP和单片机构成双CPU处理器平台,可以充分利用DSP对大容量数据和复杂算法的处理能力,以及单片机接口的控制能力。

而DSP与单片机之间快速正确的通信是构建双CPU处理器的关键问题。

下面就此问题分别设计串行SCI、SPI和并行HPI三种连接方式。

1 串行通信设计与实现1 1 SCI串行通信设计1.1.1 多通道缓冲串行口McBSP原理TMS320VC5402(简称VC5402)提供了2个支持高速、全双工、带缓冲、多种数据格式等优点的多通道缓冲串行口McBSP。

MCESP分为数据通路和控制通路。

①数据通路负责完成数据的收发。

CPU或DMAC能够向数据发送寄存器DXR写入数据,DXR中的数据通过发送移位寄存器XSR输出到DX引脚。

DR引脚接收数据到接收移位寄存器RSR,再复制到接收缓冲寄存器RBR,最后复制到数据接收寄存器DR R。

这两种数据多级缓冲方式使得数据搬移和片外数据通信能够同时进行。

②控制通路负责内部时钟产生,帧同步信号产生,信号控制和多通道选择。

另外.还具有向CPU发送中断信号和向DMAC发送同步事件的功能。

MCBSP时钟和帧同步信号通过CLKR、CLKX、FXR、FSX引脚进行控制,接收器和发送器可以相互独立地选择外部时钟和帧同步信号,也可以选择由内部采样率发生器产生时钟和帧同步信号。

帧同步脉冲有效表示传输的开始。

1.1.2 SC I串行接口设计设置VC5402的McRSP输出时钟和帧同步信号由内部采样率发生器产生,内部数据时钟CLKG和帧同步信号FSG驱动发送时钟CLKX和帧同步FSX(CLKXM=l,FSXM=l,FSGM=1),输入时钟也由内部采样率发生器产生,内部数据时钟CLKG 驱动接收时钟CLKR(CLKRM=1),同时由CPU时钟驱动采样率发生器(CLKSM=1)。

巧用电脑虚拟串口软件调试串口通信殷建彬朱前华笔者在试用Proteus这个软件的时候,在Labcenter Electronics\Proteus 6 Demonstration\SAMPLES\目录下看到COMPIM Demo这个例子,电路图如图1所示。

它用虚拟串口物理模型(左侧的P1)和一个虚拟终端(右侧的VT1)通信。

在使用这个例子的时候,笔者准备使用一个串口调试软件sscom32来检验一下,发现需要把电脑的两个串口连接起来,并且要串口2、3脚颠倒使用,当时手头没有这样的连线,也就没有进行这个试验。

后来有一天突然想到软驱、光驱、打印机甚至PC都能虚拟,串口也应该可以吧?功夫不负有心人,终于在一个外国的网站上找到一个虚拟串口软件――Virtual Serial Ports kit。

虚拟串口的使用Virtual Serial Ports kit在它的官方网站上下载到的最新版本是4.72,可惜只有15天的试用期。

下载解压后点击setup.exe进行安装,安装的时候,要求你同意它的协议才能继续安装。

然后一路“NEXT”,就可以安装成功了!安装完毕点击桌面上的图标,出现图2所示的界面。

点击工具栏的图标,出现了如图3所示的对话框,这是让我们设置虚拟串口的。

一般来说,电脑硬件上已经设置串口COM1和COM2,所以我们可以把虚拟串口设置成COM3和COM4,让这两个串口通讯,点击“OK”按钮,这个时候软件的界面变成了如图4所示的界面了。

如果发现工具栏上按钮是灰色,还需要点击一下,使它变成绿色,这意味着两个串口可以正常通信了。

笔者先试验了一下这个软件。

同时运行两个sscom32软件,既双击sscom32图标两次,软件的界面如图5所示。

点击左侧串口选择下拉箭头,如图6,把运行的两个sscom32的串口分别设置为COM3和COM4(要和虚拟串口软件的一致。

)点击“打开串口”按钮,打开两个串口,使“打开串口”前面的指示灯变为红色。

dSPACE实时仿真系统dSPACE系统选用的是适合仿真应用的POWER PC750FX处理器,在仿真中,不但要求处理器的运算速度足够高,还要对中断的响应足够快,在规定的仿真步长时间内保证算法计算完毕,dSPACE通过自己特别设计的实时内核,可以保证即使在最坏的情况下它也能在0.9—1.9个微秒切换来响应中断请求。

而这一点是其他一些系统所无法实现的,他们在最坏情况下(且对CPU的处理速度要求比较高)切换时间大多在7-9个微秒。

利用DS1005 POWER PC处理器板即使是最艰难的仿真应用也可以毫不费力地完成。

该板是专门为复杂的硬件在回路仿真而设计的。

例如:对一完整的汽车动态模型,5个并行C40 DSP需要720ms;而只有一个PPC处理器的DS1005板计算同一模型只需222ms。

不论是仿真汽车、导弹还是飞机,POWER PC的杰出性能及只用一个处理器就能仿真任何事物的能力将会使各种应用快速步入正轨。

利用DS1005 POWER PC处理器板可在各方面得到尽可能大的柔性。

通过板上的PHS(Peripheral high-speed)总线,DS1005可以管理dSPACE所有I/O板,并可根据用户的特定应用对I/O进行编程。

技术特性:处理器:IBM公司的PowerPC750FX(800MHz)32KWords的片内数据缓存及32KWords的片内指令缓存Superscalar(最多4路并行指令)12.6 SPECfp95,21.8 SPCEint95存储器:1MByte二级缓存16MByte闪存128M SRAM主存储器PHS总线接口:32位同步I/O总线20--30Mb/s传输速率,对新的I/O接口板提供30Mb/s传输速率多至64个PHS总线中断用于所有I/O板并行采样及更新的同步线并行处理:(选件)需DS910Gigallink模块高速光纤接口,传输速率>1.25Gbit/S最大可连20个处理器板光缆长度最大能达100m4条双向连接通道实时中断处理计时器及中断:两个通用定时器(多处理器系统)时间同步单元中断控制器DSPACE所采用的32位PHS总线(Peripheral high-speed bus)的特点正是实时控制系统所不可缺少的。

摘要:基于嵌入式系统发展的需要,提出TMS320VC5402 DSP与AT89C51单片机通信的三种设计方案。

利用TMS320VC5402的多通道缓冲串口MCBSP分别实现TM S320VC5402与AT89C51的SCI和SPI串行通信,以及通过TMS320VC5402的8位增强主机接口HPI一8实现TMS320VC5402与AT89C5l并行通信。

就硬件接口电路和软件编程进行详细的阐述。

关键词:单片机 DSP MCBSP HPI将DSP和单片机构成双CPU处理器平台,可以充分利用DSP对大容量数据和复杂算法的处理能力,以及单片机接口的控制能力。

而DSP与单片机之间快速正确的通信是构建双CPU处理器的关键问题。

下面就此问题分别设计串行SCI、SPI和并行HPI三种连接方式。

1 串行通信设计与实现1 1 SCI串行通信设计1.1.1 多通道缓冲串行口McBSP原理TMS320VC5402(简称VC5402)提供了2个支持高速、全双工、带缓冲、多种数据格式等优点的多通道缓冲串行口McBSP。

MCESP分为数据通路和控制通路。

①数据通路负责完成数据的收发。

CPU或DMAC能够向数据发送寄存器DXR写入数据,DXR中的数据通过发送移位寄存器XSR输出到DX引脚。

DR引脚接收数据到接收移位寄存器RSR,再复制到接收缓冲寄存器RBR,最后复制到数据接收寄存器DR R。

这两种数据多级缓冲方式使得数据搬移和片外数据通信能够同时进行。

②控制通路负责内部时钟产生,帧同步信号产生,信号控制和多通道选择。

另外.还具有向CPU发送中断信号和向DMAC发送同步事件的功能。

MCBSP时钟和帧同步信号通过CLKR、CLKX、FXR、FSX引脚进行控制,接收器和发送器可以相互独立地选择外部时钟和帧同步信号,也可以选择由内部采样率发生器产生时钟和帧同步信号。

帧同步脉冲有效表示传输的开始。

1.1.2 SC I串行接口设计设置VC5402的McRSP输出时钟和帧同步信号由内部采样率发生器产生,内部数据时钟CLKG和帧同步信号FSG驱动发送时钟CLKX和帧同步FSX(CLKXM=l,FSXM=l,FSGM=1),输入时钟也由内部采样率发生器产生,内部数据时钟CLKG 驱动接收时钟CLKR(CLKRM=1),同时由CPU时钟驱动采样率发生器(CLKSM=1)。

本科学生毕业设计基于dSPACE的CAN总线通讯程序开发系部名称:汽车与交通工程学院专业班级:车辆工程07-1班学生姓名:武中峰指导教师:王悦新职称:实验师黑龙江工程学院二○一一年六月The Graduation Design for Bachelor's Degree CAN Communication Program Development Based on dSPACECandidate:WU Zhong-fengSpecialty:Vehicle EngineeringClass:07-1Supervisor:Lecturer WANG Yue-xinHeilongjiang Institute of Technology2011-06·Harbin摘要随着现代汽车的日益发展,汽车电子设备不断增加,进而带来汽车综合控制系统中大量的控制信号需实时交换的问题,传统线束已远远不能满足这种要求,汽车局域网应运而生。

本文从研究汽车局域网入手,主要研究了国内外汽车控制器局域网的发展与现状,对当今国际汽车行业中应用最广的CAN总线原理和应用进行了深入研究与吸收。

并在研究中设计了采用CAN总线控制的门锁控制系统,制定了一套相应的可靠运行的协议。

通过试验验证,本研究门锁控制系统只需要两根信号线就可以实现数据的传输,使得传输线束大大简化,可靠性得到了提高,有效节约了线束安装空间和系统成本。

为提高汽车使用的便利性和行车的安全性,现代汽车越来越多地安装中控锁。

当驾驶员锁住其身边的车门时,其他车门也同时锁住。

驾驶员可通过门锁开关同时打开所有车门,也可单独打开某个车门。

当行车速度达到一定时,各个车门能自行锁上,防止乘员误操作车门把手而导致车门打开。

除在驾驶员身边车门以外,还在其他门设置单独的弹簧锁开关,可独立地控制一个车门的打开和锁住。

dSPACE是基于MATLAB/Simulink仿真系统开发的软硬件实时控制工作平台,利用它可缩短系统的开发时间,节约开发费用。