简易数字钟的设计

- 格式:doc

- 大小:809.00 KB

- 文档页数:24

数字时钟设计方案数字时钟是一种以数字形式显示时间的钟表。

它主要由时钟芯片、显示模块和控制电路等组成。

下面将介绍一种数字时钟的设计方案。

首先,时钟芯片是数字时钟的核心部件,其主要功能是实时计时,并提供时间信号给显示模块。

在设计中,可以选用一款精度较高的实时时钟芯片,如DS1302或DS3231,并通过SPI 或I2C等接口与其他器件进行通信。

其次,显示模块是数字时钟的输出设备,它将时钟芯片提供的时间信号转换成数字形式显示。

常见的数字时钟显示模块有七段数码管、液晶显示屏等。

在此方案中,我们选用四位共阳极的七段数码管。

然后,控制电路是数字时钟的逻辑控制部分,它通过控制模块将时钟芯片的时间信号经逻辑处理后发送给显示模块,并实现其他功能。

在此方案中,控制电路可以采用单片机或FPGA等器件实现。

以STM32单片机为例,通过编程控制GPIO口的电平改变,可以实现对七段数码管的动态显示。

具体实现方案如下:1. 硬件设计:选择合适的时钟芯片和显示模块,并完成其与控制电路的连接。

时钟芯片与控制电路的连接方式主要是通过SPI或I2C接口,而显示模块与控制电路的连接方式主要是通过GPIO口。

2. 软件设计:使用C语言或汇编语言编写控制电路的程序。

程序的主要任务是读取时钟芯片的时间信号,进行逻辑处理后控制七段数码管的显示。

3. 功能扩展:除了基本的时分秒显示外,还可以添加其他附加功能,如日期显示、闹钟设置、温度显示等。

这些功能可以通过增加相应的硬件模块和对应的软件控制实现。

4. 调试和测试:完成硬件和软件的设计后,需要进行调试和测试。

可以通过调试工具实时查看七段数码管的显示结果,并对代码进行正确性和稳定性测试。

5. PCB设计和制作:完成电路设计后,需要进行PCB的设计和制作。

在设计PCB时,要考虑电路的布局、信号线的走向和层间连接等因素,保证电路的稳定性和可靠性。

6. 组装和调试:完成PCB制作后,进行组装和调试。

将制作好的电路板和其他组件进行连接,进行最后的调试和测试。

设计制作简易数字钟一、设计要求1、设计一振荡源,用于产生1Hz的脉冲信号;2、能完成从00时00分00秒到23时59分59秒走时,并实时显示时、分、秒;3、具有手动校时、校分、校秒功能。

发挥部分:具有正点报时功能。

要求在59分58秒开始报时,持续5秒钟。

二、总体设计方案1、方案选择数字钟实际上是由一个对标准频率(1HZ)进行计数的计数电路为主要部分构成的。

由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ 时间信号必须做到准确稳定。

通常使用石英晶体振荡器电路来构成数字钟的标准时间基准信号。

数字钟的组成框图如下图所示。

数字钟计时周期是24,因此必须设置24 计数器,秒、分、时由七段数码管显示。

为使数字钟走时与标准时间一致,校时电路是必不可少的。

设计中采用状态机控制校时,通过切换开关用秒脉冲或手动按键产生脉冲先后对“时” “分” “秒”计数器进行校时操作。

2、数字钟的构成(1)数字钟的构成:振荡器、分频器、计数器、译码器、LED数码管显示器等几部分。

附加功能的实现还需采用T’触发器及与门和或门及蜂鸣器组成报时电路。

(2)数字钟的时、分、秒实际上就是由一个24 进制计数器(00-23),两个60 进制计数器(00-59)级联构成。

设计数字钟实际上就是计数器的级联。

(3)芯片选型:由于24进制、60进制计数器均由集成计数器级联构成,且都包含有基本的十进制计数器,从设计简便考虑,芯片选择十进制计数器74LS390。

3、元器件列表:型号74LS00、74LS04、74LS08、74LS21、74LS32、74LS47、74LS74、74LS86、74LS390、CD4068、CD4060、CD4511。

晶体管8050、510欧姆电阻、LED、轻触开关、自锁开关、蜂鸣器、10p电容、晶振32768、10M电阻。

三、系统工作原理1、主计数部分原理图图1主计数部分原理图如图所示,用两个十进制计数器74LS390组成60进制计数器和24进制计数器,分别用于对分、秒和时的计数。

目录一、课程设计任务及要求 (2)二、课程设计目的 (2)三、系统工作原理综述及原理框图 (2)四、各单元电路工作原理、电路图及仿真结果 (3)1.模24计数器 (3)2.模60计数器 (4)3.分频器 (7)4.校时控制器 (8)五、数字时钟原理图及仿真结果 (10)六、下载到实验箱、较时及测试结果 (12)七、课程设计小结 (12)附录:设备清单一、课程设计任务及要求1.课程设计任务:用CPLD设计简易数字时钟。

2.要求:(1)具有计时功能,用6位数码管分别显示时、分、秒信号。

(2)具有校时功能,进行时校时时不能对分计数器的状态有影响,进行分校时时不能对时计数器的状态有影响;校时结束后,秒计数器要清零。

二、课程设计目的1.通过完成课程设计,掌握实际问题的逻辑分析,学会对实际问题进行逻辑状态分配、化简。

2.掌握简单数字系统问题的控制电路设计要求及信号之间的配合。

3.掌握数字电路各单元电路与总体电路的设计、调试、模拟仿真方法。

4.掌握一个较复杂电路在实现时,出现问题时的分析思路与解决办法;学会模块化、层次化进行电路设计的方法。

三、系统工作原理综述及原理框图系统框图如下图所示:系统工作原理综述:由系统框图可知,此数字时钟由七部分组成:标准时钟源、分频器、秒计数器、分计数器、时计数器、分校时控制器、时校时控制器、译码显示器。

其中标准时钟源已经提供为1KHZ;分频器将其分为两种计时信号,一种为计数信号,为1HZ;一种为校时信号,为5HZ(可自行设定)。

系统正常工作时,所有计数器处于计数状态,结果经译码后由数码管显示出来;当清零键按下时,所有计数器均被清零,时钟显示00:00:00;当按下分校时键时,校时信号加到分计数器时钟端,使得分计数器快速计数,达到分较时的效果,同时秒计数器清零,且时计数器显示的数字不变;当按下时校时键时,校时信号加到时计数器时钟端,使得时计数器快速计数,达到时较时的效果,同时秒计数器清零,且分计数器显示的数字不变。

数字钟的设计

数字钟的设计可以包括以下要素:

1. 数字显示器:数字钟需要一个数字显示器来显示当前的

时间。

可以采用LED或LCD显示器,显示数字0-9等基本数字以及冒号等特殊符号。

2. 时间设置按钮:数字钟需要一个或多个按钮来设置时间。

用户可以通过按下按钮来调整小时、分钟和秒等时间设置。

3. 电路板:数字钟需要一个电路板来控制时间的计数和显示。

电路板上包含微控制器或集成电路芯片,负责处理输

入和输出信号,控制时间的计数和显示。

4. 电源:数字钟需要一个电源来供电。

可以使用电池或直

接接入电源插座。

5. 外壳:数字钟需要一个外壳来保护内部组件,同时也可以起到美观的作用。

外壳材料可以选择塑料、金属或木材等。

6. 时钟机芯:数字钟需要一个时钟机芯,用于稳定时间的计数和显示。

时钟机芯可以是石英机芯、机械机芯或电子机芯等。

7. 其他功能:数字钟还可以添加其他功能,如闹钟、温度显示、日历等。

这些功能可以通过额外的按钮和显示屏来实现。

需要根据实际需求和预算来选择设计数字钟的具体要素和组件。

同时,还需要考虑数字钟的易用性、耐用性和美观性等因素。

设计完成后,还需要进行测试和调整,确保数字钟的正常工作。

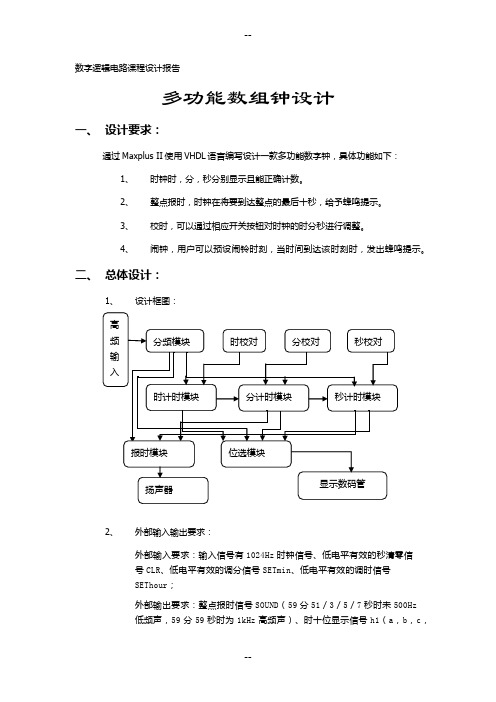

数字逻辑电路课程设计报告多功能数组钟设计一、设计要求:通过Maxplus II使用VHDL语言编写设计一款多功能数字钟,具体功能如下:1、时钟时,分,秒分别显示且能正确计数。

2、整点报时,时钟在将要到达整点的最后十秒,给予蜂鸣提示。

3、校时,可以通过相应开关按钮对时钟的时分秒进行调整。

4、闹钟,用户可以预设闹铃时刻,当时间到达该时刻时,发出蜂鸣提示。

二、总体设计:1、设计框图:2、外部输入输出要求:外部输入要求:输入信号有1024Hz时钟信号、低电平有效的秒清零信号CLR、低电平有效的调分信号SETmin、低电平有效的调时信号SEThour;外部输出要求:整点报时信号SOUND(59分51/3/5/7秒时未500Hz低频声,59分59秒时为1kHz高频声)、时十位显示信号h1(a,b,c,d,e,f,g)、时个位显示信号h0(a ,b,c,d,e,f,g)、分十位显示信号m1及分个位m0、秒十位s1及秒个位s0;数码管显示位选信号SEL0/1/2等三个信号。

3、各模块功能:1)FREQ分频模块:整点报时用的1024Hz与512Hz的脉冲信号,这里的输入信号是1024Hz信号,所以只要一个二分频即可;时间基准采用1Hz输入信号直接提供(当然也可以分频取得,这里先用的是分频取得的信号,后考虑到精度问题而采用硬件频率信号。

2)秒计数模块SECOND:60进制,带有进位和清零功能的,输入为1Hz脉冲和低电平有效的清零信号CLR,输出秒个位、时位及进位信号CO。

3)分计数模块MINUTE60进制,带有进位和置数功能的,输入为1Hz脉冲和高电平有效的使能信号EN,输出分个位、时位及进位信号CO。

4)时计数模块HOUR:24进制,输入为1Hz脉冲和高电平有效的使能信号EN,输出分个位、时位。

5)扫描模块SELTIME:输入为秒(含个/十位)、分、时、扫描时钟CLK1K,输出为D和显示控制信号SEL。

6)整点报时功能模块ALERT:输入为分/秒信号,输出为高频声控Q1K和Q500。

简易电子钟设计范文电子钟是一种通过电子技术实现时间显示的设备。

它通常由一个数字显示屏,一个控制电路和一个电源组成。

其主要功能是显示小时、分钟和秒钟等时间信息,可以准确地显示时间,并可以根据需要设置闹铃功能。

设计一款简易电子钟可以使用Arduino等开发板或单片机来实现。

首先,我们需要选择一块合适的数字显示屏。

常见的数字显示屏有数码管和液晶显示屏两种类型,它们的显示原理和控制方式有所不同。

如果选择数码管作为显示屏,可以考虑使用常见的7段数码管,它由八个LED灯组成,可以显示0-9的数字以及一些字母和特殊符号。

数码管的控制方式是通过控制每个LED灯的亮灭来实现显示,可以使用数字输出口来控制。

Arduino的数字输出口可以输出高电平(5V)和低电平(0V),通过控制输出口的电平,就能够控制数码管的亮灭。

如果选择液晶显示屏作为显示器,可以选择字符型液晶显示屏或者图形型液晶显示屏。

字符型液晶显示屏通常可以显示一些字符或者数字,它的控制方式是通过并行或者串行接口来控制,可以使用开发板的GPIO口来实现。

图形型液晶显示屏可以显示更多的信息,它的控制方式是通过SPI接口或者I2C接口来控制,这需要相应的驱动库或者芯片来实现。

无论选择数码管还是液晶显示屏,我们都需要编写程序来控制显示。

程序的核心是一个循环,其中使用时钟模块来获取当前的时间,并使用相应的控制方式将时间信息显示在显示屏上。

如果需要设置闹铃功能,可以在循环中判断当前时间和设置的时间是否相等,如果相等则触发闹铃。

设计一个简易电子钟的完整步骤如下:1. 选择适合的开发板或者单片机,例如Arduino。

2.选择合适的显示屏,例如7段数码管或者液晶显示屏。

3.连接显示屏到开发板,根据显示屏的类型选择合适的引脚连接方式。

4.编写代码来控制显示屏显示时间信息。

5.添加时钟模块,用来获取当前的时间信息。

6.根据需要添加闹铃功能。

7.测试电子钟的功能和性能,不断优化改进。

数字钟的设计引言数字钟是一种常见的时钟设计,它能够以数字形式显示时间,方便人们获取准确的时间信息。

本文将介绍数字钟的设计原理、硬件与软件实现,并提供一个示例设计的步骤指南。

设计原理数字钟的设计原理基于计数器和显示器。

计数器用于记录时间,而显示器用于将记录的时间以数字形式显示出来。

一般情况下,数字钟主要涉及到以下几个方面的设计:1.时钟电路:时钟电路是数字钟的核心组成部分,它通过稳定的振荡器产生一个稳定的时钟信号,以确保数字钟的准确性。

2.计数器电路:计数器电路用于记录时间。

它可以根据时钟信号来递增或递减计数值,并将计数值转换成小时、分钟和秒钟等形式。

3.显示器电路:显示器电路用于将计数器记录的时间以数字形式显示出来。

常见的显示器电路包括七段数码管、LCD显示屏等。

硬件设计在数字钟的硬件设计中,需要考虑以下几个方面:1.选取合适的时钟电路:选择合适的时钟电路非常重要,它直接影响到数字钟的准确性。

常用的时钟电路包括晶振电路和石英钟电路等。

2.选择合适的计数器芯片:选择合适的计数器芯片能够简化数字钟的设计。

常见的计数器芯片有74HC4017、CD4510等。

3.选择合适的显示器:根据设计需求选择合适的显示器。

七段数码管是常用的显示器,它能够以数字形式显示时间。

另外,LCD显示屏也是常见的选择之一。

软件设计数字钟的软件设计主要涉及到以下几个方面:1.程序框架设计:设计程序框架能够清晰地组织代码,使得代码具有良好的可读性和可维护性。

可以使用面向对象的思想设计程序框架,将时钟和显示器等抽象为对象,方便调用和管理。

2.时钟管理:设计一个时钟管理模块,用于控制时钟的计数和显示。

该模块需要根据计数器的计数值来更新显示器的显示。

3.用户交互设计:如果有需要,可以设计用户交互模块,允许用户设置时间等功能。

可以通过按键输入实现用户与数字钟的交互。

示例设计以下是一个简单的数字钟设计的示例步骤指南:1.选择合适的时钟电路,比如使用一个晶振电路作为时钟源。

毕业设计76简易数显电子钟设计一、引言电子钟是指使用数字显示的时钟,通过LED或LCD等显示器件显示时间。

本文将设计一款简易数显电子钟,采用数字管显示器件,实现准确显示时间的功能。

设计的电子钟具有简单、易操作、精确显示等特点,适合作为毕业设计的对象。

二、设计原理1.时钟芯片选取:选用高精度的时钟芯片,可以提供准确的时间信号。

2.数字显示器件选取:采用数字管显示时、分、秒的数据。

3.控制电路设计:根据时钟芯片提供的时间信号,通过控制电路将时、分、秒的数据传输到数字显示器件进行显示。

三、设计步骤1.选择时钟芯片:根据设计需求,选择适合的高精度时钟芯片,如DS13022.搭建电路原理图:根据选定的时钟芯片的电路原理图,搭建控制电路的原理图,包括时钟芯片、数字显示器件等。

3.PCB设计:根据电路原理图,进行PCB设计,制作电路板。

4.组件焊接:根据PCB设计制作的电路板,将所有的电子组件焊接到电路板上。

5.软件编程:根据时钟芯片的数据手册,编写软件程序,实现数据传输和显示功能。

6.系统调试:完成软硬件的搭建后,进行系统调试,检查时钟芯片和控制电路的正常工作情况。

7.最终制作:将电路板安装到外壳中,搭建简易数显电子钟的最终产品。

四、设计注意事项1.保证电路的稳定性和可靠性:在电路设计和焊接过程中,注意选择合适的电子元件,以确保电路的稳定性和可靠性。

2.时钟芯片的驱动:在软件编程过程中,需要熟悉时钟芯片的控制寄存器和通信协议,以确保准确的数据传输。

3.屏幕显示:在选择数字显示器件时,需考虑显示器件的亮度、清晰度等因素,以保证用户操作的便捷性。

五、设计成果展示通过厚一学期的努力,成功设计并制作了一款简易数显电子钟。

设计的电子钟具有准确的时间显示功能,通过数字管显示时、分、秒的数据。

用户可以方便地通过操作按钮调整时间。

电子钟外观简洁大方,适合放置在家居或办公场所使用。

六、结论本文以设计一款简易数显电子钟为目标,经过认真的设计与制作,成功实现了时、分、秒的准确显示功能。

数字时钟设计方案引言数字时钟是一种用于显示时间的设备。

它使用数字显示时间,并且通常具有精确的时间读数。

数字时钟由数字显示屏、时钟芯片和控制电路组成。

本文将介绍数字时钟的设计方案,包括硬件设计和软件设计。

硬件设计数字显示屏选择在数字时钟中,选择合适的数字显示屏非常重要。

目前市场上有很多不同类型的数字显示屏,常见的包括LED数码管、LCD液晶显示屏和OLED有机发光二极管等。

根据实际需求和预算,选择适合的数字显示屏。

LED数码管是一种常用的数字显示屏,它使用发光二极管来显示数字。

LED数码管的亮度高、视角宽,但功耗较高。

LCD液晶显示屏具有低功耗、高对比度和广视角优势,适合于室内使用。

OLED有机发光二极管具有自发光、亮度高和对比度好的特点,但相对来说价格较高。

时钟芯片选择时钟芯片是数字时钟中的核心部件,它用于提供精确的时间读数。

常见的时钟芯片包括DS1302、DS3231和DS1307等。

根据实际需求选择合适的时钟芯片。

DS1302是一款低成本的实时时钟芯片,具有较高的精度和稳定性。

DS3231是一款温度补偿实时时钟芯片,具有更高的精度和稳定性。

DS1307是一款低成本的实时时钟芯片,具有较低的精度和稳定性。

控制电路设计控制电路是数字时钟的关键组成部分,它用于驱动数字显示屏和时钟芯片。

控制电路由零件选择和电路布局两个方面考虑。

在零件选择方面,需要选择适当的晶体管、电阻器和电容等元件来实现数字显示和时钟控制功能。

其中,晶体管用于驱动数字显示屏,电阻器和电容用于实现时钟芯片的电路连接。

在电路布局方面,要注意数字显示屏和时钟芯片之间的布线,尽量减少干扰和串扰。

同时,考虑电源线的布局和接地方式,避免电源噪声对时钟电路的影响。

软件设计系统架构设计数字时钟的软件设计需要考虑系统架构。

常见的数字时钟系统架构包括单片机架构和嵌入式操作系统架构。

在单片机架构中,使用单片机作为主控制器,实现数字显示和时钟控制功能。

常见的单片机包括51单片机和AVR单片机等。

如何设计简单的数字时钟电路数字时钟电路是一种常见的电子电路,用于显示时间并具备时间计时功能。

设计一个简单的数字时钟电路可以通过以下步骤实现。

第一步:确定数字时钟的显示方式常见的数字时钟电路可以采用七段数码管进行显示,每个数码管由七个LED灯组成,用于显示数字0-9。

可以根据需要选择合适的数码管来完成数字时钟的显示。

第二步:确定时钟的计时器数字时钟电路需要一个计时器来跟踪时间。

常见的计时器可以使用555定时器或者基于微控制器的计时器模块。

选择适合自己的计时器并连接到电路中。

第三步:连接七段数码管将选定的七段数码管连接到电路中。

每个数码管的七个LED灯分别对应数码管的a、b、c、d、e、f、g引脚,根据数码管的型号和引脚布局进行正确连接。

例如,将数码管的a引脚连接到计时器的输出引脚,b引脚连接到计时器的另一个引脚,以此类推。

第四步:设计时钟功能根据需要设计时钟功能,包括显示当前时间、设置闹钟、调节亮度等。

可以通过增加按钮开关、旋转编码器或者完成基于微控制器的编程来实现这些功能。

第五步:连接电源和调试将数字时钟电路与合适的电源连接,并进行必要的调试。

确保电路中的元件连接正确并正常工作。

如果有需要,可以使用示波器或多用途测试仪来辅助调试。

总结:通过以上步骤,我们可以设计一个简单的数字时钟电路。

根据需求选择合适的数码管和计时器,连接七段数码管,设计时钟功能并连接电源进行调试。

这样就可以得到一个能够准确显示时间并具备计时功能的数字时钟电路。

需要注意的是,以上步骤只是设计一个简单的数字时钟电路的基本流程,具体的实现可能因项目需求和硬件平台的差异而有所不同。

在实际应用中,还需要考虑电路的稳定性、精度和可靠性等因素,并根据实际情况进行细节调整和优化。

中文摘要数字钟已经成为人们日常生活中不可缺少的必需品,广发应用于家庭及办公室等公共场所,给人们的生活、学习、工作及娱乐带来了极大的方便。

由于数字集成电路技术的发展和采用了先进的石英技术,使得数字钟具有走时准确、性能稳定、携带方便等优点,它还用于计时、自动报时及自动控制等各个领域。

尽管目前市场上已有现成的数字钟集成电路芯片出售,价格便宜、使用方便,但鉴于单片机的定时器功能也可以完成数字钟的设计,因此进行数字的设计是必要的。

在这里我们将已学过的比较零散的数字电路的知识有机的、系统的联系起来用于实际,来培养我们的综合分析和设计电路,写程序、调试电路的能力。

单片机具有体积小、功能强、可靠性高、价格低廉等一系列优点,不仅已成为工业测控领域普遍采用的智能化控制工具,而且已渗入到人们工作和生活的各个角落,有力地推动了各行各业的技术改造和产品的更新换代,应用前景广阔。

本次做的数字钟是以单片机(AT89C51)为核心,结合相关的元器件(共阴极LED 数码显示器等),再配以相应的软件,达到制作简易数字钟的目的。

硬件部分采用了单片机原理实验室的实验箱进行合理接线调试;软件部分通过keil进行了C程序的修改编译,protues软件仿真等。

最终在实验箱上实现了与仿真结果相同的实际效果。

关键词单片机定时功能、AT89C51、共阴LED、Keil、Protues软件。

AbstractMicroelectronics and computer technology along with the rapid development and progress, making the design of electronic systems and applications have entered a new era. The traditional manual design process is being advanced electronic design automation technology to replace. And is currently supporting modern technology has become the universal platform for electronic design, and step by step to support the development of system-level design. Only to hardware description language and logic synthesis-based top-down design methodology to meet the increasingly complex needs of digital system design. The progressive development of the taxi industry, the taxi meter is getting higher and higher requirements, the user requires not only the performance of the stability of billing, billing and accurate anti-cheat functions; and as a result of the instability in oil prices, billing system the need for regular adjustment of the meter so that users can request not to change the hardware to facilitate the billing system modifications.The system is the use of language, it can make use of digital circuits and system description, simulation and automatic design, and software as a development platform designed billing system procedures taxi and carried out a simulation program. To the achievement of pre-billing and simulation, as well as car to start, stop, pause and other functions, and dynamic scan shows the number of fares.Key Words Microcontroller\、AT89C51、7SEG-MPX6-CC-RED 、Keil、Proteus目录中文摘要 (I)Abstract (II)目录......................................................................................................................................... I II 1设计任务描述.. (4)1.1设计题目:简易数字钟的设计 (4)1.2 设计要求: (4)1.2.1 设计目的 (4)1.2.2 基本要求 (4)2设计思路 (5)3设计方框图 (6)3.1数字钟硬件部分示意图 (6)3.2数字钟软件部分组成框图 (6)3.2.1时间调整的程序流程 (6)3.2.2时钟显示程序流程 (7)4各部分模块介绍 (8)4.1单片机AT89C51芯片分析 (8)4.2晶振电路模块 (10)4.3复位电路模块 (10)4.4显示模块 (11)4.5时间校对按键模块 (11)5简易数字钟源程序 (12)5.1源程序 (12)6数字钟源程序的仿真 (17)6.1编译、连接 (17)6.2仿真 (18)6.2.1生成HEX文件 (18)6.2.2仿真结果 (19)7数字钟硬件原理图 (19)7.1总原理图 (19)8主要原器件清单 (20)小结 (21)致谢 (22)参考文献 (23)1 设计任务描述1.1 设计题目:简易数字钟的设计1.2 设计要求:1.2.1 设计目的熟练使用Keil开发环境,具备编写单片机程序(汇编语言或C语言)的初步能力,通过完成本课题的软硬件设计,使同学们了解单片机实例的整个开发流程。

第三单元简易数字钟的设计数字钟是一种用数字显示秒、分、时的计时装置,与传统的机械钟相比,它具有走时准确、显示直观、无需机械传动等优点。

因而得到了广泛的应用。

小到人们日常生活中的电子手表,大到车站、码头、机场等公共场所的大型数字电子钟,数字钟到处可见。

在数字电路的学习中,已经学习过用计数器芯片搭建数字钟。

51单片机内部集成了定时器/计数器,这为构建数字钟带来了方便。

在本单元中,学习如何用51单片机来构建一个功能数字钟。

【任务要求】在八个数码管上显示时、分、秒以及两个横杠。

通过单片机内部定时器控制走时,走时准确。

系统有四个按键,功能分别是调整,加,减,确定。

在按下调整键时候,显示“时”的两位数码管以1 Hz 频率闪烁。

如果再次按下调整键,则“分”开始闪烁,“时”恢复正常显示,依次循环,直到按下确定键,恢复正常的显示。

在数码管闪烁的时候,按下加或者减键可以调整相应的显示内容。

按键支持短按和长按,即短按时,修改的内容每次增加一或者减小一,长按时候以一定速率连续增加或者减少。

【学习知识点】数码管的原理,驱动程序的实现。

独立按键的原理及程序的实现。

51单片机内部定时器的原理及应用【内容安排】第一节:数码管显示原理及应用实现第二节:独立按键检测原理及应用实现第三节:计时的原理及实现第四节:数字钟的构建第一节数码管显示原理及应用实现1.1 数码管显示原理数字钟要把时间显示到数字显示的装置上,常用的数字显示装置有数码管、液晶、LED、CRT显示器等。

在单片机系统设计中,LED数码管是最基本的显示装置。

在数字钟的设计中我们用数码管对中的小时、分和表来进行显示。

LED数码管能显示各种数字或符号,由于它具有显示清晰、亮度高、寿命长、价格低廉的特点,因此使用非常广泛。

图1.1是几个数码管的图片,图a为单位数码管,图b为双位数码管,图c为四位数码管。

a 单位数码管b 双位数码管c 四位数码管图1.1数码管图片那么数码管是如何的工作呢?还记得我们小时候玩过的“火柴棒游戏”吗,几根火柴组合起来,可以拼成各种各样的图形,数码管实际上就是利用这个原理做成的。

简易数字钟的设计一.指标要求1.用中小规模集成电路设计一台能显示“时”,“分”,“秒”的简易数字钟;2.除按24小时计数外,还应具有手动调节小时,分钟,秒的校时功能;3.具有整点报时功能;二.设计计算1.整体方案设计1.1课题分析数字钟一般由6个部分组成,其中振荡器和分频器组成标准的秒信号发生器,由不同进制的计数器,译码器和显示器组成计时系统。

秒信号送入计数器进行计数,把累计的结果以“时”“分”“秒”的十进制数字显示出来。

“时”显示由二十四进制计数器,译码器和显示器构成,“分”“秒”显示分别由六十进制计数器,译码器和显示器构成。

1.2工作原理数字钟是一个将“ 时”,“分”,“秒”显示于人的视觉器官的计时装置。

它的计时周期为24小时,显示满刻度为23时59分59秒,另外应有校时功能。

因此,一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器、校时电路和振荡器组成。

干电路系统由秒信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路组成。

秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用石英晶体振荡器加分频器来实现。

将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发现胡一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计时器,可实现对一天24小时的累计。

译码显示电路将“时”、“分”、“秒”计数器的输出状态菁七段显示译码器译码,通过六位LED七段显示器显示出来。

整点报时电路时根据计时系统的输出状态产生一脉冲信号,然后触发一音频发生器实现报时。

校时电路是用来对“时”、“分”、“秒”显示数字进行校对调整的。

数字电子钟由振荡器、分频器、计数器、译码显示、报时等电路组成。

其中振荡器和分频器组成标准秒信号发生器,由不同进制的计数器、译码器和显示器组成计时系统。

一数字钟设计原理和基于QuartursⅡ的设计流程1.1 数字钟设计原理首先下载程序进行复位清零操作,电子钟从00:00:00计时开始。

sethour可以调整时钟的小时部分, setmin可以调整分钟,步进为1。

由于电子钟的最小计时单位是1s,因此提供给系统的内部的时钟频率应该大于1Hz,这里取100Hz。

CLK端连接外部10Hz的时钟输入信号clk。

对clk进行计数,当clk=10时,秒加1,当秒加到60时,分加1;当分加到60时,时加1;当时加到24时,全部清0,从新计时。

用6位数码管分别显示“时”、“分”、“秒”,通过OUTPUT( 6 DOWNTO 0 )上的信号来点亮指定的LED七段显示数码管。

该系统由振荡器、分频器、“时、分、秒”计数器、译码器及显示器、校时电路等组成。

石英晶体振荡器和分频器产生整个系统的时基信号,它直接决定计时系统的精度。

“秒计数器”采用六十进制计数器,每累计60秒向“分计数器”进位;“分计数器”采用六十进制计数器,每累计60分向“时计数器”进位;“时计数器”采用二十四进制计数器,按照“24翻1”规律计数。

“时、分、秒”计数器的输出经译码器送显示器显示。

校时电路用来当计时出现误差时对“时、分、秒”进行校对调整。

1.2 QuartursⅡ的设计流程图图1-1 设计流程图二系统框图及程序清单2.1 系统框图图2-1系统框图2.2 源程序2.2.1 小时计数器VHDL语言源程序LIBRARY IEEE;use IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY hour ISPORT(clk,reset:IN STD_LOGIC;daout:out STD_LOGIC_VECTOR(5 DOWNTO 0));END ENTITY hour;ARCHITECTURE fun OF hour ISSIGNAL count:STD_LOGIC_VECTOR(5 DOWNTO 0);BEGINdaout<=count;PROCESS(clk,reset)BEGINIF(reset='0')THEN count<="000000"; ——若reset=0,则异步清零ELSIF(clk'event and clk='1')THEN ——否则,若clk上升沿到IF(count(3 DOWNTO 0)="1001")THEN ——若个位计时恰好到“1001”即9IF(count<16#23#)THEN ——23进制count<=count+7; ——若到23D则elsecount<="000000"; ——复0END IF;ELSIF (count<16#23#)THEN ——若未到23D,则count进1count<=count+1;ELSE ——否则清零count<="000000";END IF; ——END IF(count(3 DOWNTO 0)=“1001”)END IF; ——END IF(reset=…0‟)END PROCESS;END fun;2.2.2 分钟计数器VHDL语言源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY minute ISPORT(clk,clk1,reset,sethour:IN STD_LOGIC;enhour:OUT STD_LOGIC;daout:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END ENTITY minute ;ARCHITECTURE fun OF minute ISSIGNAL count :STD_LOGIC_VECTOR (6 DOWNTO 0);SIGNAL enhour_1, enhour_2: STD_LOGIC; ——enmin_1为59分时的进位信号BEGIN ——enmin_2由clk调制后的手动调时脉冲信号串daout<=count;enhour_2<= (sethour and clk1); ——sethour为手动调时控制信号,高电平有效enhour<= (enhour_1 or enhour_2);PROCESS(clk,reset,sethour)BEGINIF(reset='0') THEN ——若reset为0,则异步清零count<="0000000";ELSIF(clk'event and clk='1')THEN ——否则,若clk上升沿到IF(count (3 DOWNTO 0) ="1001")THEN——若个位计时恰好到“1001”即9IF(count <16#60#) THEN ——又若count小于16#60#,即60IF(count="1011001") THEN——又若已到59Denhour_1<='1'; ——则置进位为1count<="0000000"; ——count复0ELSEcount<=count+7; ——若count未到59D,则加7,即作“加6校正”END IF; ——使前面的16#60#的个位转变为8421BCD的容量ELSEcount<="0000000";——count复0(有此句,则对无效状态电路可自启动)END IF; ——END IF(count<16#60#)ELSIF (count <16#60#) THENcount<=count+1; ——若count<16#60#则count加1enhour_1<='0' after 100 ns; ——没有发生进位ELSEcount<="0000000"; ——否则,若count不小于16#60# count复0END IF; ——END IF(count(3 DOWNTO 0)=“1001”)END IF; ——END IF(reset=…0‟)END process;END fun;2.2.3 秒钟计数器VHDL语言源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY second ISPORT( clk,reset,setmin:STD_LOGIC;enmin:OUT STD_LOGIC;daout:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END ENTITY second;ARCHITECTURE fun OF second ISSIGNAL count:STD_LOGIC_VECTOR(6 DOWNTO 0);SIGNAL enmin_1,enmin_2:STD_LOGIC; ——enmin_1为59秒时的进位信号BEGIN ——enmin_2由clk调制后的手动调分脉冲信号串daout<=count;enmin_2<=(setmin and clk); ——setmin为手动调分控制信号,高电平有效enmin<=(enmin_1 or enmin_2); ——enmin为向分进位信号PROCESS(clk,reset,setmin)BEGINIF(reset='0')THEN count<="0000000"; ——若reset为0,则异步清零ELSIF(clk 'event and clk='1')then ——否则,若clk上升沿到IF(count(3 downto 0)="1001")then ——若个位计时恰好到“1001”即9IF(count<16#60#)then ——又若count小于16#60#,即60HIF(count="1011001")then ——又若已到59Denmin_1<='1';count<="0000000";——则置进位为1及count复0 ELSE ——未到59Dcount<=count+7; ——则加7,而+7=+1+6,即作“加6校正”END IF;ELSE ——若count不小于16#60#(即count等于或大于16#60#)count<="0000000"; ——count复0END IF; ——END IF(count<16#60#)ELSIF(count<16#60#)then ——若个位计数未到“1001”则转此句再判count<=count+1; ——若count<16#60#则count加1enmin_1<='0'after 100 ns; ——没有发生进位ELSE ——否则,若count不小于16#60#count<="0000000"; ——则count复0END IF; ——END IF(count(3 DOWNTO 0)=“1001”)END IF; ——END IF(reset=…0‟)END PROCESS;END fun;2.2.4 顶层文件library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity DigitalClock isport(clk,en,rst : in std_logic;ADJEN : in std_logic;AlarmEn : in std_logic;alarmADJ : in std_logic;ADJ : in std_logic_vector(3 downto 0);sound : out std_logic;hour_unit : out std_logic_vector(3 downto 0);hour_decade : out std_logic_vector(3 downto 0);min_unit : out std_logic_vector(3 downto 0);min_decade : out std_logic_vector(3 downto 0);sec_unit : out std_logic_vector(3 downto 0);sec_decade : out std_logic_vector(3 downto 0);dote1 : out std_logic_vector(3 downto 0);dote2 : out std_logic_vector(3 downto 0));end ;architecture bhv of DigitalClock iscomponent hourport(rst,carry,en : in std_logic;ADJclk,ADJEN : in std_logic;ADJ : in std_logic_vector(3 downto 0);decade,unit : out std_logic_vector(3 downto 0));end component;component minport(rst,carry,en : in std_logic;ADJclk,ADJEN : in std_logic;ADJ : in std_logic_vector(3 downto 0);carryout : out std_logic;decade,unit : out std_logic_vector(3 downto 0));end component;component secport(rst,clk,en : in std_logic;ADJEN : in std_logic;carryout : out std_logic;decade,unit : out std_logic_vector(3 downto 0));end component;component alarmport(clk,en,ADJclk : in std_logic;alarmADJ : in std_logic;AlarmEn : in std_logic;ADJ : in std_logic_vector(3 downto 0);hour_unit : in std_logic_vector(3 downto 0);hour_decade : in std_logic_vector(3 downto 0);min_unit : in std_logic_vector(3 downto 0);min_decade : in std_logic_vector(3 downto 0);ADJhour_unit : out std_logic_vector(3 downto 0);ADJhour_decade : out std_logic_vector(3 downto 0);ADJmin_unit : out std_logic_vector(3 downto 0);ADJmin_decade : out std_logic_vector(3 downto 0);sound : out std_logic);end component;component PrescalClkport(clkin : in std_logic;clkout_1Hz : out std_logic;clkout_4Hz : out std_logic);end component;signal carry1,carry2,clk_1Hz,clk_4Hz : std_logic;signal hour1,hour2,min1,min2 ,ADJhour1,ADJhour2,ADJmin1,ADJmin2 : std_logic_vector(3 downto 0);beginU1 : hour port map(rst=>rst,ADJclk=>clk_4Hz,en=>en,carry=>carry1,ADJEN=>ADJEN,ADJ=>ADJ,decade=>hour1,unit=>ho ur2);U2 : min port map(rst=>rst,ADJclk=>clk_4Hz,en=>en,carry=>carry2,carryout=>carry1,ADJEN=>ADJEN,ADJ=>ADJ,decade= >min1,unit=>min2);U3 : sec port map(rst=>rst,clk=>clk_1Hz,en=>en,carryout=>carry2,decade=>sec_decade,unit=>sec_unit,ADJEN=>ADJEN);U4 : alarm port map(clk=>clk_1Hz,en=>en,ADJclk=>clk_4Hz,alarmADJ=>alarmADJ,AlarmEn=>AlarmEn,ADJ=>ADJ, hour_unit=>hour2,hour_decade=>hour1,min_unit=>min2,min_decade=>min1,ADJhour_decade=>ADJhour1,ADJhour_unit=>ADJhour2,ADJmin_decade=>ADJmin1,ADJmin_unit=>AD Jmin2 ,sound=>sound);U5 : PrescalClk port map(clkin=>clk,clkout_1Hz=>clk_1Hz,clkout_4Hz=>clk_4Hz);process(hour1,hour2,min1,min2,alarmADJ,ADJhour1,ADJhour2,ADJmin1,ADJmin2)beginif(alarmADJ='0') thenhour_decade<=hour1;hour_unit<=hour2;min_decade<=min1;min_unit<=min2;elsehour_decade<=ADJhour1;hour_unit<=ADJhour2;min_decade<=ADJmin1;min_unit<=ADJmin2;end if;dote1<="1010";dote2<="1010";end process;end;2.2.5 分频library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity PrescalClk isport(clkin : in std_logic;clkout_1Hz : out std_logic;clkout_4Hz : out std_logic);end ;Architecture bhv of PrescalClk isbeginprocess(clkin)variable count1 : integer range 0 to 32768;variable count2 : integer range 0 to 8192;beginif clkin 'event and clkin='1' then count1 := count1+1;count2:=count2+1;if(count1=32768) then clkout_1Hz<='1' ;else clkout_1Hz<='0';end if;if(count2=8192) then clkout_4Hz<='1';else clkout_4Hz<='0';end if;end if;end process;end;三各模块实现功能3.1秒计时器second1是由一个60进制的计数器构成的,具有清0、置数和计数功能。

数字电子技术课程设计报告要求:设计一个能显示时、分、秒的简易数字钟。

步骤:用verilog语言在记事本编写程序,再用QuartusⅡ仿真,定义针脚,在面板上模拟。

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的寿命,因此得到广泛的应用。

设计原理及框图数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路,具有时、分、秒计数显示功能,以24小时为计数循环。

这次实验主要是要实现时钟的计时功能,时间计数由秒个位和秒十位计数器,分个位和分十位计数器及时个位和时十位计数器,,其中秒个位和秒十位计数器,分个位和分十位计数器为60进制计数器,而根据设计要求,时个位和时十位计数器为24进制计数器.,然后需要把8位二进制数转变为译码管需要的8421码。

设计方案:这个实验总体分:秒、分、时三个模块,计时和较准两个模式标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲之一。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个时脉冲信号,该信号作为时计数器的时钟脉冲之一,时计数器采用24进制计时器,可实现对一天24小时的计时。

译码显示电路将“时”、“分”、“秒”计数器的输出状态通过译码管显示。

这们时钟的计时功能就实现了,秒模块是一个以1HZ的clock信号控制的60进制计数器,并同时产生分进位信号tun。

always @(posedge clock)beginif(sec==59) \\当秒等于59时,如果处于计时模式时产生begin \\一个进位脉冲tun, 否则tun信号暂停sec<=0;tun<=1;elsetun<=tun;endelse \\若秒不等于59,同样如果处于计时模式begin \\就使tun信号清0,否则tun信号暂停sec<=sec+1;if(at==0)tun<=0;elsetun<=tun;endend分模块也是一个60进制计数器,并产生小时的进位信号mod,但要受到两个控制信号的控制一个是进位信号tun,另一个是t_min的按建信号。

《数字电路》课程设计总结报告题目:数字钟设计2010 年 12 月 12 日数字钟设计 (3)一、设计任务 (3)1.1功能描述 (3)二、设计框图与整机概述 (3)2.1主题电路图 (3)2.2系统的工作原理 (3)三、各单元电路的设计方案及原理说明 (4)3.1设计思路 (4)3.2振荡器的设计 (4)3.3分频器的设计 (4)3.4分秒计数器的设计 (4)3.5校时电路的设计 (5)3.6显示电路的设计 (6)四、调试过程及结果分析 (6)4.1调试过程 (6)4.2结果分析 (6)五、设计、安装及调试中的体会 (6)六、对本次课程设计的意见和建议 (7)七、参考文献 (7)八、附录 (7)数字钟设计一、设计任务1.1功能描述设计一个多功能数字中电路,基本功能为:①准确计时,以数字形式显示分、秒的时间;②分和秒的计时要求为60进位;③校正时间。

二、设计框图与整机概述2.1主题电路图1s2.2系统的工作原理由振荡器产生高稳定的高频脉冲信号,作为数字钟的时间基准(系统时钟),再经分频器输出标准秒脉冲信号。

秒计数器计满60后向分计数器进位,分计数器计满60后重新开始计时。

计数器的输出经译码器送显示器。

计时出现误差时可以用校时电路进行校分。

分显示器 秒显示器时译码器 秒译码器分计数器 秒计数器 校时电路 分频器振荡器三、各单元电路的设计方案及原理说明3.1设计思路主体电路是由功能部件或单元电路组成的。

在设计这些电路或选择部件时,尽量用同类型的器件,如所有功能部件都采用TTL集成电路或都采用CMOS集成电路。

3.2振荡器的设计振荡器是数字钟的核心。

振荡器的稳定度及频率的精确度决定了数字钟计时的准确程度,通常选用石英晶体构成振荡器电路。

一般来说,振荡器的频率越高,计时精度越高。

在这里我们选用由集成电路定时器555与RC组成的多谐振荡器。

这里选用555构成的多谐振荡器,输出振荡频率v0=1KHz的脉冲,电路参数如下图所示。

中文摘要数字钟已经成为人们日常生活中不可缺少的必需品,广发应用于家庭及办公室等公共场所,给人们的生活、学习、工作及娱乐带来了极大的方便。

由于数字集成电路技术的发展和采用了先进的石英技术,使得数字钟具有走时准确、性能稳定、携带方便等优点,它还用于计时、自动报时及自动控制等各个领域。

尽管目前市场上已有现成的数字钟集成电路芯片出售,价格便宜、使用方便,但鉴于单片机的定时器功能也可以完成数字钟的设计,因此进行数字的设计是必要的。

在这里我们将已学过的比较零散的数字电路的知识有机的、系统的联系起来用于实际,来培养我们的综合分析和设计电路,写程序、调试电路的能力。

单片机具有体积小、功能强、可靠性高、价格低廉等一系列优点,不仅已成为工业测控领域普遍采用的智能化控制工具,而且已渗入到人们工作和生活的各个角落,有力地推动了各行各业的技术改造和产品的更新换代,应用前景广阔。

本次做的数字钟是以单片机(AT89C51)为核心,结合相关的元器件(共阴极LED 数码显示器等),再配以相应的软件,达到制作简易数字钟的目的。

硬件部分采用了单片机原理实验室的实验箱进行合理接线调试;软件部分通过keil进行了C程序的修改编译,protues软件仿真等。

最终在实验箱上实现了与仿真结果相同的实际效果。

关键词单片机定时功能、AT89C51、共阴LED、Keil、Protues软件。

AbstractMicroelectronics and computer technology along with the rapid development and progress, making the design of electronic systems and applications have entered a new era. The traditional manual design process is being advanced electronic design automation technology to replace. And is currently supporting modern technology has become the universal platform for electronic design, and step by step to support the development of system-level design. Only to hardware description language and logic synthesis-based top-down design methodology to meet the increasingly complex needs of digital system design. The progressive development of the taxi industry, the taxi meter is getting higher and higher requirements, the user requires not only the performance of the stability of billing, billing and accurate anti-cheat functions; and as a result of the instability in oil prices, billing system the need for regular adjustment of the meter so that users can request not to change the hardware to facilitate the billing system modifications.The system is the use of language, it can make use of digital circuits and system description, simulation and automatic design, and software as a development platform designed billing system procedures taxi and carried out a simulation program. To the achievement of pre-billing and simulation, as well as car to start, stop, pause and other functions, and dynamic scan shows the number of fares.Key Words Microcontroller\、AT89C51、7SEG-MPX6-CC-RED 、Keil、Proteus目录中文摘要 (I)Abstract (II)目录......................................................................................................................................... I II 1设计任务描述.. (1)1.1设计题目:简易数字钟的设计 (1)1.2 设计要求: (1)1.2.1 设计目的 (1)1.2.2 基本要求 (1)2设计思路 (2)3设计方框图 (3)3.1数字钟硬件部分示意图 (3)3.2数字钟软件部分组成框图 (4)3.2.1时间调整的程序流程 (4)3.2.2时钟显示程序流程 (5)4各部分模块介绍 (6)4.1单片机AT89C51芯片分析 (6)4.2晶振电路模块 (7)4.3复位电路模块 (7)4.4显示模块 (8)4.5时间校对按键模块 (9)5简易数字钟源程序 (10)5.1源程序 (10)6数字钟源程序的仿真 (15)6.1编译、连接 (15)6.2仿真 (16)6.2.1生成HEX文件 (16)6.2.2仿真结果 (16)7数字钟硬件原理图 (17)7.1总原理图 (17)8主要原器件清单 (18)小结 (19)致谢 (20)参考文献 (21)1 设计任务描述1.1 设计题目:简易数字钟的设计1.2 设计要求:1.2.1 设计目的熟练使用Keil开发环境,具备编写单片机程序(汇编语言或C语言)的初步能力,通过完成本课题的软硬件设计,使同学们了解单片机实例的整个开发流程。

1.2.2 基本要求⑴简要说明用单片机设计出一个数字钟。

此数字钟完成自动走时和时间调整的功能。

⑵任务和要求设计简易的数字钟,该数字钟满足以下要求:设计一个数字钟,该数字钟基本功能:使用单片机的定时/计数器实现数字中的定时计数功能,秒计60次成分,分计60次成小时,小时计24次则计满一天。

本设计LED显示部分采用动态显示,其中2个LED显示器显示秒,2个LED显示器显示分钟,2个LED 显示器显示小时。

同时为了使用方便,本题目还需要设计几个简单按键,可以通过按键实现时、分的调整,这样在主程序中需要加入键盘设置子程序。

2 设计思路基于单片机的简易数字钟设计主要可以分为以下几个模块来考虑:㈠对于单片机AT89C51的T0,T1定时中断部分。

本次设计中的单片机晶振频率采用了精准的11.0592MHZ。

故对T1初值设定为:DC00h,实现了10ms的定时,然后C 程序中通过定义一个变量i,对i进行i++的100次循环,如此即可达到最小1S的实现。

而后在这个1S程序段的基础之上,我们可以分别编写出对时,分的程序段。

对于定时器T0,我们可以将其用来作为数码管动态扫描的定时中断,本次设计设为50ms左右,初值为FC17h。

这个取值通过最后的仿真及实际效果看出合理,不会出现闪烁等情况。

㈡校时电路。

本次设计要求了该简易数字钟必须具备时、分的调整功能。

故必须接入2个简单的按键(本设计设置问p1.4调时、p1.5调分,按键为实验箱单次脉冲按键模块),并且在软件部分必须引入这2个独立按键的子程序。

㈢显示电路。

考虑采用动态显示部分,用P0口作为数码管数据(段选),P2口作为数码管控制(位选)。

动态显示通常都是采用动态扫描的方法进行显示,即循环点亮每一个数码管,这样虽然在任意时刻都只有一位数码管被点亮,但由于人眼存在视觉暂留效应,只要每位数码管间隔时间足够短,就可以给人以通俗显示的感觉。

上面第一部分已提到,我们采用了50ms左右的时间间隔,并且是合理的。

6位数码管,实验室的硬件是共阴极的,故我们的数码表采用{0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f, 0x00};㈣晶振电路。

在AT89C51芯片内部有一个高增益反相放大器,其输入端为芯片引脚XTAL1,输出端为引脚XTAL2。

而在芯片内部,XTAL1和XTAL2之间跨接晶体振荡器和微调电容,从而构成一个稳定的自激振荡器。

时钟电路产生的振荡脉冲经过触发器进行二分频之后,才成为单片机的时钟脉冲信号。

㈤复位电路。

这部分设计用来完成对单片机的复位。

以上是对本次设计课题的初步分析,以下将对各部分模块设计进行详细阐述。

3 设计方框图3.1 数字钟硬件部分示意图该简易数字钟硬件部分主要由晶振、手动复位、单片机AT89C51、数码管显示、时间调整按键模块组成。

框图如下:图3.1数字钟硬件系统示意图3.2 数字钟软件部分组成框图3.2.1 时间调整的程序流程图3.2时间调整程序流程框图3.2.2 时钟显示程序流程图3.3 24小时时钟4 各部分模块介绍4.1 单片机AT89C51芯片分析AT89C51单片机引脚图如下:图 4.1 AT89C51引脚图该单片机是标准的40引脚双列直插式集成电路芯片,其各个引脚功能如下:VCC:+5V电源。

VSS: 接地。

RST:复位信号。

当输入的复位信号延续两个周期以上的高电平时即为有效,用来完成单片机的初始化操作。

XTAL1和XTAL2:外接晶体引线端。

当使用芯片内部时钟时,此二引线端用于外接石英晶体和微调电容;当使用外部时钟时,用于接外部时钟脉冲信号。

PO口:P0口作为一个8位漏极开路双向I/O口,当作输出口使用时,必须接上拉电阻才有高电平输出;当作输入口使用时,必须先向电路中的锁存器写入“1”,使FET截止,以避免锁存器为“0”时对引脚输入的干扰。

本次设计采用P0口作为数码管段选输出使用。

P2口:内部有上拉电阻的8位I/O口,本次设计中作为数码管位选输出使用。