实验七 数模转换及计数器的应用

- 格式:ppt

- 大小:257.50 KB

- 文档页数:6

数电实验报告:计数器及其应用数字电子技术实验报告实验四:计数器及其应用一、实验目的:1、熟悉常用中规模计数器的逻辑功能。

2、掌握二进制计数器和十进制计数器的工作原理和使用方法。

二、实验设备:1、数字电路实验箱;2、74LS90。

三、实验原理:1、计数是一种最简单基本运算,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时具有分频功能。

计数器按计数进制分有:二进制计数器,十进制计数器和任意进制计数器;按计数单元中触发器所接收计数脉冲和翻转顺序分有:异步计数器,同步计数器;按计数功能分有:加法计数器,减法计数器,可逆(双向)计数器等。

2、74LS90是一块二-五-十进制异步计数器,外形为双列直插,NC表示空脚,不接线,它由四个主从JK触发器和一些附加门电路组成,其中一个触发器构成一位二进制计数器;另三个触发器构成异步五进制计数器。

在74LS90计数器电路中,设有专用置“0”端R0(1),R0(2)和置“9”端S9(1)S9(2)。

其中前两个为异步清0端,后两个为异步置9端。

CP1, CP2为两个时钟输入端;Q0 ~Q3为计数输出端。

当R1=R2=S1=S2=0时,时钟从CP1引入,Q0输出为二进制;从CP2引入,Q3输出为五进制。

时钟从CP1引入,二Q0接CP1,则Q3Q2Q1Q0输出为十进制(8421码);时钟从CP2引入,而Q3接CP1,则Q0Q3Q2Q1输出为十进制(5421码)。

四、实验原理图及实验结果:1、实现0~9十进制计数。

1)实验原理图如下:(函数信号发生器:5V 3Hz 偏移2.5V方波)2)实验结果:解码器上依次显示0~9十个数字。

2、实现六进制计数。

1)实验原理图如下:(函数信号发生器:5V 3Hz 偏移2.5V方波)2)实验结果:解码器上依次显示0~5六个数字。

3、实现0、2、4、6、8、1、3、5、7、9计数。

1)实验原理图如下:(函数信号发生器:5V 3Hz 偏移2.5V方波)2)实验结果:解码器上依次显示0、2、4、6、8、1、3、5、7、9十个数字。

模数、数模转换及其应用摘要:随着电子技术的迅速发展以及计算机在自动检测和自动控制系统中的广泛应用,利用电子系统处理模拟信号的情况变得更加普遍。

数字电子计算机所处理的都是不连续的数字信号,而实际遇到的大都是连续的模拟量,模拟量经过传感器转换成电信号的模拟量后,需经过模/数转换变成数字信号后才可输入到数字系统中进行处理和控制。

同时,往往还要求将处理后得到的数字信号再经过数/模转换成相应的模拟信号,作为最后的输出。

模数、数模转换建立在各种转换电路的基础上,并且不断改进模数、数模转换器的转换精度与转换速度。

模数、数模转换技术在工业中有着重要的应用。

关键字:电子系统模数转换器数模转换器转换技术的应用Digital to analog、digital to analog conversion and its application Abstract: With the rapid development of electronic technology and computer in the automatic detection and automatic control system in the broad application, the use of electronic system for processing analog signal conditions become more common. Digital electronic computer processing are not continuous digital signal, but actually encountered mostly continuous analog, analog quantity sensor is converted into electrical signals by analog, after A / D conversion into digital signal can be input to a digital system for processing and control. At the same time, also often seek treatment received digital signals through D / A conversion into a corresponding analog signal, as the final output. ADC, DAC based on conversion circuit based on continuous improvement, and module, digital to analog converter conversion precision and conversion rate. ADC,DAC technology in industry has important applications.Key words: electronic system;analog to digital converter;digital to analog converter;conversion technology application1引言作为把模拟电量转换成数字量或数字量转换成模拟电量输出的接口电路,转换器是现实世界中模拟信号通向数字信号的桥梁,是电子技术发展的关键和瓶颈所在。

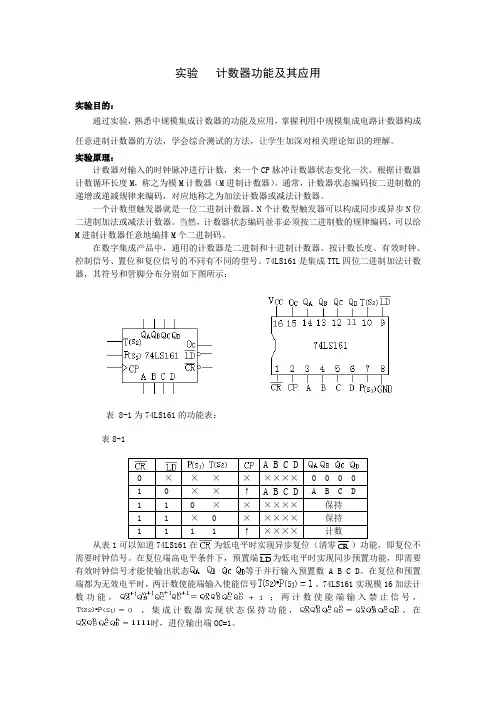

实验计数器功能及其应用实验目的:通过实验,熟悉中规模集成计数器的功能及应用,掌握利用中规模集成电路计数器构成任意进制计数器的方法,学会综合测试的方法,让学生加深对相关理论知识的理解。

实验原理:计数器对输入的时钟脉冲进行计数,来一个CP脉冲计数器状态变化一次。

根据计数器计数循环长度M,称之为模M计数器(M进制计数器)。

通常,计数器状态编码按二进制数的递增或递减规律来编码,对应地称之为加法计数器或减法计数器。

一个计数型触发器就是一位二进制计数器。

N个计数型触发器可以构成同步或异步N位二进制加法或减法计数器。

当然,计数器状态编码並非必须按二进制数的规律编码,可以给M进制计数器任意地编排M个二进制码。

在数字集成产品中,通用的计数器是二进制和十进制计数器。

按计数长度、有效时钟、控制信号、置位和复位信号的不同有不同的型号。

74LS161是集成TTL四位二进制加法计数器,其符号和管脚分布分别如下图所示:表 8-1为74LS161的功能表:表8-1A B C D从表1在为低电平时实现异步复位(清零需要时钟信号。

在复位端高电平条件下,预置端LD为低电平时实现同步预置功能,即需要有效时钟信号才能使输出状态等于并行输入预置数 A B C D。

在复位和预置端都为无效电平时,两计数使能端输入使能信号,74LS161实现模16加法计数功能,;两计数使能端输入禁止信号,,集成计数器实现状态保持功能,。

在时,进位输出端OC=1。

在数字集成电路中有许多型号的计数器产品,可以用这些数字集成电路来实现所需要的计数功能和时序逻辑功能。

用M进制集成计数器构成任意N进制计数器:1、M>N,需一片M进制计数器一种为反馈清零法,另一种为反馈置数法。

(1)反馈清零法反馈清零法是利用反馈电路产生一个给集成计数器的复位信号,使计数器各输出端为零(清零)。

反馈电路一般是组合逻辑电路,计数器输出部分或全部作为其输入,在计数器一定的输出状态下即时产生复位信号,使计数电路同步或异步地复位。

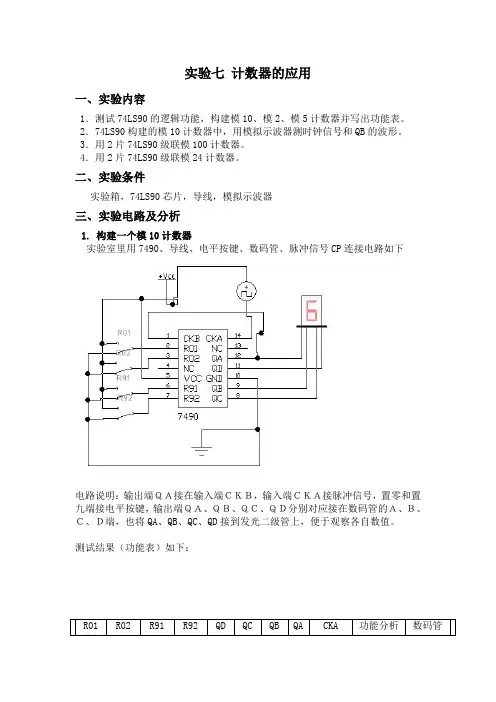

实验七计数器的应用一、实验内容1.测试74LS90的逻辑功能,构建模10、模2、模5计数器并写出功能表。

2.74LS90构建的模10计数器中,用模拟示波器测时钟信号和QB的波形。

3.用2片74LS90级联模100计数器。

4.用2片74LS90级联模24计数器。

二、实验条件实验箱,74LS90芯片,导线,模拟示波器三、实验电路及分析1.构建一个模10计数器实验室里用7490、导线、电平按键、数码管、脉冲信号CP连接电路如下电路说明:输出端QA接在输入端CKB,输入端CKA接脉冲信号,置零和置九端接电平按键,输出端QA、QB、QC、QD分别对应接在数码管的A、B、C、D端,也将QA、QB、QC、QD接到发光二级管上,便于观察各自数值。

测试结果(功能表)如下:结果分析及结论:1.置零端R01、R02必须同时有效才会有清零效果,同样置九端也必须同时有效,才会置为9;2.由上面可知,当置零端和置九端无效、时钟信号沿下降沿时,开始计数,由0~9依次循环,到9时此时QA为1,将QA接到输入B端便会有强制清零功能,故只会计到9,并重新开始计数,从而实现了模10计数器功能。

2.构建一个模5计数器实验室里用7490、导线、电平按键、数码管、脉冲信号CP连接电路如下电路说明:输入端CKB接脉冲信号,输入端CKA接输出端QD,置零和置九端接电平按键,输出端QA、QB、QC、QD分别对应接在数码管的A、B、C、D端,也将QA、QB、QC、QD接到发光二级管上,便于观察各自数值。

结果分析及结论:1.置零端和置九端同模10的功能一样,参考上面,功能表上不再显示;2.当置零端和置九端无效、时钟信号沿下降沿时,开始计数,显示0-2-4-6-8-0-2-4-6-8-………循环,从而实现了模5计数功能。

3.构建一个模2计数器实验室里用7490、导线、电平按键、数码管、脉冲信号CP连接电路如下电路说明:输入端CKA接脉冲信号,输入端CKB悬空,置零和置九端接电平按键,输出端QA、QB、QC、QD分别对应接在数码管的A、B、C、D端,也将QA、QB、QC、QD接到发光二级管上,便于观察各自数值。

实验2.10 计数器及其应用一、实验目的1、熟悉中规模集成计数器的功能及使用方法。

2、掌握时序逻辑部件功能的测试方法。

3、能熟练地用中规模集成计数器设计时序电路。

二、实验仪器及材料数字逻辑电路实验箱和扩展板、双踪示波器、芯片74LS00、74LS04、74LS10、双D触发器74LS74、同步十进制可逆计数器芯片74LS192(或CC40192)、可预置的4位同步二进制计数器74LS161等。

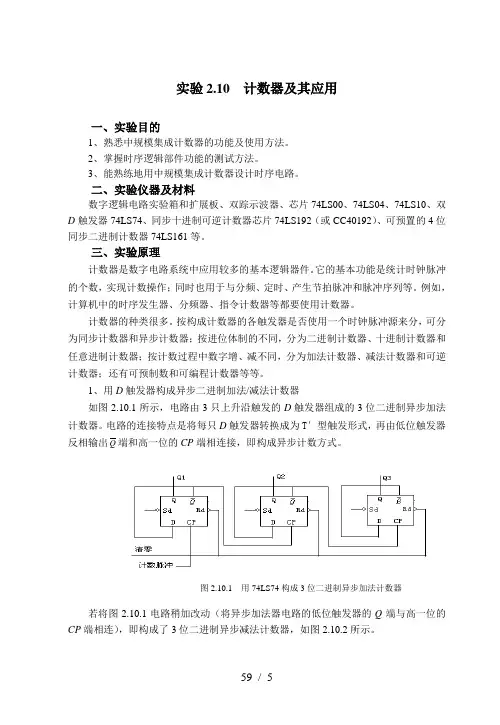

三、实验原理计数器是数字电路系统中应用较多的基本逻辑器件。

它的基本功能是统计时钟脉冲的个数,实现计数操作;同时也用于与分频、定时、产生节拍脉冲和脉冲序列等。

例如,计算机中的时序发生器、分频器、指令计数器等都要使用计数器。

计数器的种类很多。

按构成计数器的各触发器是否使用一个时钟脉冲源来分,可分为同步计数器和异步计数器;按进位体制的不同,分为二进制计数器、十进制计数器和任意进制计数器;按计数过程中数字增、减不同,分为加法计数器、减法计数器和可逆计数器;还有可预制数和可编程计数器等等。

1、用D触发器构成异步二进制加法/减法计数器如图2.10.1所示,电路由3只上升沿触发的D触发器组成的3位二进制异步加法计数器。

电路的连接特点是将每只D触发器转换成为T′型触发形式,再由低位触发器反相输出Q端和高一位的CP端相连接,即构成异步计数方式。

图2.10.1 用74LS74构成3位二进制异步加法计数器若将图2.10.1电路稍加改动(将异步加法器电路的低位触发器的Q端与高一位的CP端相连),即构成了3位二进制异步减法计数器,如图2.10.2所示。

59 / 52、中规模十进制计数器中规模集成计数器品种多,功能完善,通常具有预置、保持、计数等多种功能。

集成芯片74LS192是同步十进制可逆计数器。

它具有双时钟输入,可执行十进制加法和减法计数,并具有清零、置数等功能。

芯片引脚排列如图2.10.3所示。

其中LD 为置数端,CP U 为加计数脉冲输入端,CP d 为减计数脉冲输入端,u TC 为非同步进位输出端,d TC 为非同步借位输出端,P 0、P 1、P 2、P 3为数据输入端,MR 为清零端,Q 0、Q 1、Q 2、Q 3为计数器输出端。

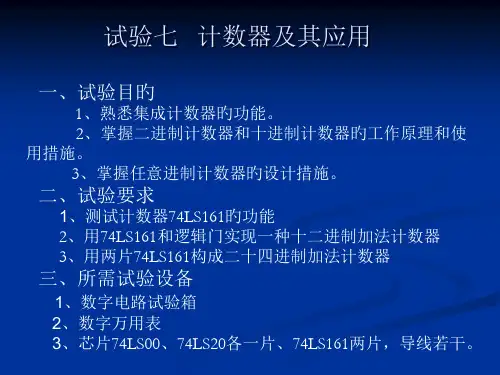

实验七 计数器及其应用一.实验目的1.熟悉计数器的工作原理,掌握MSI 计数器逻辑功能及其应用。

2.掌握计数器的级联方法,并会用MSI 计数器实现任意进制计数器。

3.会用MAX+PLUS Ⅱ系统软件进行任意进制计数器的设计。

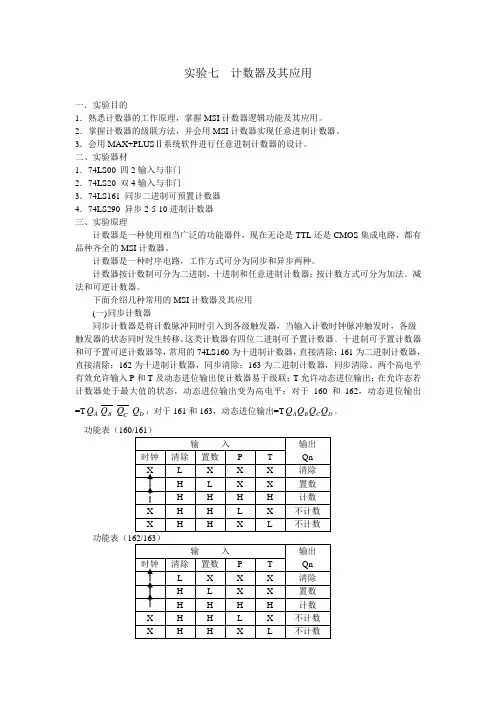

二、实验器材1.74LS00 四2输入与非门 2.74LS20 双4输入与非门3.74LS161 同步二进制可预置计数器 4.74LS290 异步2-5-10进制计数器三、实验原理计数器是一种使用相当广泛的功能器件,现在无论是TTL 还是CMOS 集成电路,都有品种齐全的MSI 计数器。

计数器是一种时序电路,工作方式可分为同步和异步两种。

计数器按计数制可分为二进制,十进制和任意进制计数器;按计数方式可分为加法﹑减法和可逆计数器。

下面介绍几种常用的MSI 计数器及其应用(一) 同步计数器同步计数器是将计数脉冲同时引入到各级触发器,当输入计数时钟脉冲触发时,各级 触发器的状态同时发生转移。

这类计数器有四位二进制可予置计数器﹑十进制可予置计数器和可予置可逆计数器等,常用的74LS160为十进制计数器,直接清除;161为二进制计数器,直接清除;162为十进制计数器,同步清除;163为二进制计数器,同步清除。

两个高电平有效允许输入P 和T 及动态进位输出使计数器易于级联;T 允许动态进位输出;在允许态若计数器处于最大值的状态,动态进位输出变为高电平;对于160和162,动态进位输出=T A Q B Q C Q D Q ;对于161和163,动态进位输出=T D C B A Q Q Q Q 。

功能表(160/161)输 入输出 Qn 时钟 清除 置数 P T X L X X X 清除 H L X X 置数 H H H H 计数 XH H L X 不计数 XHHXL不计数 功能表(162/163)输 入 输出 Qn 时钟 清除 置数 P T L X X X 清除 H L X X 置数 H H H H 计数 X H H L X 不计数 XHHXL不计数在可逆计数器中,74190﹑74LS190﹑74HC190为可予置BCD 十进制同步可逆计数器(带方式控制);74191﹑74LS191﹑74HC191为可予置四位二进制同步可逆计数器(带方式控制);74192﹑74LS192﹑74HC192﹑74C192为可予置BCD 十进制同步可逆计数器(双时钟带清除);74193﹑74L193﹑74LS193﹑74HC193﹑74C193为可予置四位二进制同步可逆计数器(双时钟带清除)。

数模转换器和模数转换器实验报告材料一、实验目的1.学习和掌握数模转换器和模数转换器的原理和工作方式;2.了解数模转换器和模数转换器在各种应用领域的具体应用;3.掌握数模转换器和模数转换器的实际测量方法和数据处理。

二、实验器材和原理1.数模转换器(DAC):将数字信号转换为模拟信号。

它可以将二进制数字信号转换为连续的模拟信号,并且可以根据控制信号的不同而输出不同的电压或电流;2.模数转换器(ADC):将模拟信号转换为数字信号。

它能够实时取样模拟信号,并将其转换为对应的数字信号;3.示波器:用于观测和显示信号波形;4.信号发生器:用于产生输入信号。

三、实验过程1.数模转换器实验:(1)将示波器的X轴连接到数模转换器的数字输入端,Y轴连接到模拟输出端;(2)通过示波器上的控制按钮,调整示波器显示的方式,使其能够显示数模转换器输出的模拟信号波形;(3)使用信号发生器产生不同频率的正弦信号,并通过数模转换器将其转换为模拟信号;(4)观察和记录示波器上显示的模拟信号波形,并进行分析和比较。

2.模数转换器实验:(1)将信号发生器的输出连接到模数转换器的模拟输入端;(2)调整信号发生器的频率和幅度,产生不同的模拟信号;(3)将模拟信号输入到模数转换器中,并观察和记录模数转换器输出的数字信号;(4)使用示波器观测和记录模数转换器输出的数字信号波形,并进行分析和比较。

四、实验结果和数据处理1.数模转换器实验结果:根据示波器显示的模拟信号波形,可以观察到数模转换器能够将输入的数字信号转换为连续的模拟信号,并且输出的模拟信号的波形与输入信号的波形一致。

2.模数转换器实验结果:根据示波器显示的数字信号波形,可以观察到模数转换器能够将输入的模拟信号实时取样并转换为对应的数字信号。

对于不同频率和幅度的输入信号,模数转换器能够正确地输出对应的数字信号。

五、实验结论数模转换器和模数转换器是将数字信号和模拟信号相互转换的重要器件。

实验七计数器及其应用一、实验目的1.学习用集成触发器构成计数器的方法2.掌握中规模集成计数器的使用方法及功能测试方法3.运用集成计数器构成1∕N分频器二、实验原理计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多。

按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。

根据计数器的不同,分为二进制计数器,十进制计数器和任意进制计数器。

根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等等。

目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数电路。

使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。

1、用D触发器构成异步二进制加∕减计数器图7-1是用四只D触发器构成的四位二进制异步加法计数器,它的连接特点是将每只D 触发器接成T′触发器,再由低位触发器的Q端和高一位的CP端相连接。

图7-1若将图7-1稍加改动,即将低位触发器的Q端与高一位的CP端相连接,即构成了一个4位二进制减法计数器3.中规模十进制计数器74LS90,其内部是由四个下降沿J-K触发器组成的两个独立CP为时钟脉冲输入端,Q0为输出端;另一个是异步五进计数器。

一个是二进制计数器,CP为时钟脉冲输入端,Q3Q2Q1为输出端。

R0A、R0B称异步复位(清零)端,制计数器,1S9A、S9B称异步置9端。

表7-1是该计数器功能表。

由该表可见:(1)复位端R0A= R0B=1以及置9端S9A或S9B之中有一个接“0”就实现计数器清零,即Q3Q2Q1Q0=0000。

(2)置9端S9A= S9B=1以及复位端R0A或R0B状态任意就实现计数器置“9”,即Q3Q2Q1Q0=1001。

(3)正常计数时,必须使R0A或R0B之中有一个接“0”,同时R9A或S9B之中有一个接“0”。

实验7 计数器及其应用一、实验目的:1. 熟悉计数器的逻辑功能。

2. 掌握集成计数器的使用方法。

3. 学习实现任意进制计数器的方法。

二、实验原理计数器是最常用的时序逻辑电路之一。

其功能就是对输入的脉冲进行计数。

计数器种类繁多,按计数制式可分为二进制计数器、十进制计数器、任意进制计数器;按构成计数器中的各触发器是否使用同一个时钟信号可将计数器分为同步计数器和异步计数器;按照计数方向,可分为加法计数器、减法计数器和可逆计数器等。

本实验选用同步二进制计数器74LS161。

图1为74LS61的逻辑符号及管脚分布。

图中,LD ——置数端;CP ——时钟脉冲输入端;CR ——清零端;S 1、S 2使能端;CO 溢出进位端;D 0~D 3预置数输入端;Q 0~Q 3数据输出端。

74LS161的功能表如表1所示。

从功能表可以看出,74LS161是异步清零、同步置数的模16加法计数器。

表 1 74LS161的功能表三、 实验内容图 1 74LS61 引脚排列及逻辑符号1.74LS61功能测试CR、LD、S1、S2、D0~D3接LED,CP接单脉冲。

在图2中画出实验接线图。

按自己画的接线图连接电路,将实验结果填入表2中。

图 2 实验内容1的接线图表 2 74LS161性能测试结果根据测试结果回答下列问题:(1) 74LS161进行清零操作与CP有关吗?()(有关,无关),因此74LS161是()(同步、异步)清零的。

(2) 74LS161进行置数操作与CP有关吗?()(有关,无关),74LS161进行置数操作是在CP脉冲的(上升沿、下降沿)实现的?因此74LS161是(同步、异步)置数的。

2.实验原理图如图3所示。

根据74LS161和74LS00的引脚分布在图中标出引脚号。

然后按图3连接电路。

其中CP接单脉冲,Q0~Q3、Z接LED。

将实验结果填入表3。

根据实验结果回答问题:(1) 该计数器是进制的计数器。

(2) 如果CR不接基本RS触发器,而按图中虚线所示连接,是否影响计数模数?图 3表 33. 原理图如图4所示。