数字电路精彩试题五套(含问题详解)

- 格式:doc

- 大小:2.36 MB

- 文档页数:23

数字电路试题及答案一、选择题(每题10分,共20分)1. 下列数字电路元件中,属于组合逻辑的是A. 集线器B. 隧道二极管C. 寄存器D. D触发器答案:A2. 十进制数 8 的二进制表示形式为A. 1010B. 1110C. 1000D. 1001答案:C3. 十六进制数 B 的二进制表示形式为A. 1010B. 1101C. 1111D. 1011答案:D4. 以下哪个逻辑门的输出是其他逻辑门输出的非A. 与门B. 或门C. 非门D. 异或门答案:C二、填空题(每题10分,共20分)1. 使用 2 输入 AND 门,将 A 和 B 两个开关输入,如果 A 和 B 均为高电平时,输出为________答案:高电平2. 使用 2 输入 OR 门,将 A 和 B 两个开关输入,如果 A 和 B 中有一个或两个为高电平时,输出为________答案:高电平3. 使用 2 输入 XOR 门,将 A 和 B 两个开关输入,如果 A 和 B 中只有一个为高电平时,输出为________答案:高电平4. 使用 2 输入 NAND 门时,输出为低电平的条件是________答案:A 和 B 均为高电平三、简答题(每题20分,共40分)1. 请简述组合逻辑和时序逻辑的区别。

答案:组合逻辑是指电路的输出仅由当前时刻的输入确定,与之前的输入无关。

组合逻辑电路的输出仅取决于输入信号的组合,对于相同的输入,始终保持相同的输出。

而时序逻辑是指电路的输出除了与当前输入有关外,还与之前的输入和输出有关。

时序逻辑电路的输出不仅取决于输入信号的组合,还受到电路之前状态的影响。

2. 请简述二进制和十六进制之间的转换原理。

答案:二进制是一种基于2的数制,只有两个数位 0 和 1。

而十六进制是一种基于16的数制,包含了 0 到 9 的数字和 A 到 F 的六个字母。

进行二进制到十六进制的转换时,将二进制数按照每四位分组,然后将每个四位二进制数转换为相应的十六进制数,最终得到的十六进制数就是对应的表示。

《数字电路》试卷及答案一、【单项选择题】 ( 本大题共20 小题,每题 2 分,共40 分) 在每题列出的四个选项中只有一个选项是切合题目要求的,请将正确选项前的字母填在答题卷相应题号处。

1、关于钟控 RS触发器,若要求其输出“ 0”状态不变,则输入的RS信号应为( A)。

[A] RS=X0[B] RS=0X[C] RS=X1[D] RS=1X2、以下各电路中,( B)能够产生脉冲准时。

[A]多谐振荡器[B]单稳态触发器[C]施密特触发器[D]石英晶体多谐振荡器3、以下逻辑电路中为时序逻辑电路的是(C)。

[A]变量译码器[B]加法器[C]数码存放器[D]数据选择器4、同步时序电路和异步时序电路比较,其差别在于后者(B)。

[A]没有触发器[B]没有一致的时钟脉冲控制[C]没有稳固状态[D]输出只与内部状态相关5、当用专用输出构造的PAL设计时序逻辑电路时,一定还要具备有(A)。

[A]触发器[B]晶体管[C] MOS 管[D]电容6、能将输出端直接相接达成线与的电路有(C)。

[A] TTL 与门[B]或门[C]三态门[D]三极管非门7、 TTL 与非门的剩余脚悬空等效于(A)。

[A] 1[B] 0[C] Vcc[D] Vee8、以下哪一条不是除去竟争冒险的举措(B)。

[A]接入滤波电路[B]利用触发器[C]加当选通脉冲[D]改正逻辑设计9、主从触发器的触发方式是(D)。

[A] CP=1[B] CP上涨沿[C] CP 降落沿[D]分两次办理10、组合型 PLA 是由( A)组成。

[A]与门阵列和或门阵列[B]一个计数器[C]一个或阵列[D]一个存放器11、以下四个数中,最大的数是(B)。

[A] (AF) 16[B] (001010000010)8421BCD[C] (10100000) 2[D] (198) 1012、触发器有两个稳态,储存8 位二进制信息要(B)个触发器。

[A] 2[B] 8[C] 16[D] 3213、以下门电路属于双极型的是(A)。

数电试题及答案一、选择题(每题5分,共20分)1. 在数字电路中,以下哪个不是基本的逻辑门?A. 与门B. 或门C. 非门D. 异或门答案:D2. 一个触发器可以存储的二进制数是:A. 1位B. 2位C. 3位D. 4位答案:A3. 以下哪个不是组合逻辑电路的特点?A. 无记忆功能B. 输出只依赖于当前输入C. 有记忆功能D. 输出与输入的逻辑关系固定答案:C4. 一个8位二进制计数器的计数范围是:A. 0-7B. 0-15C. 0-255D. 0-511答案:C二、填空题(每题5分,共20分)1. 在数字电路中,最小的可存储单元是______。

答案:触发器2. 一个D触发器的输出Q与输入D的关系是:当时钟脉冲上升沿到来时,Q变为D的______。

答案:值3. 在数字电路中,一个4位的二进制数可以表示的最大十进制数是______。

答案:154. 一个5进制计数器的计数范围是______。

答案:0-4三、简答题(每题10分,共30分)1. 请解释什么是同步电路和异步电路,并说明它们的主要区别。

答案:同步电路是指电路中的所有触发器都由同一个时钟信号控制,从而确保所有触发器在同一时刻更新其状态。

异步电路则没有统一的时钟信号,触发器的状态更新是独立进行的,可能会因为触发器的响应时间不同而导致时序问题。

2. 什么是摩尔斯电码,它在数字通信中有什么应用?答案:摩尔斯电码是一种早期的数字编码系统,通过不同的点(短脉冲)和划(长脉冲)的组合来表示字母、数字和标点符号。

在数字通信中,摩尔斯电码用于无线电通信,因为它可以有效地在嘈杂的信道中传输信息。

3. 解释什么是寄存器,并说明它在计算机系统中的作用。

答案:寄存器是一种高速的存储设备,用于存储指令、数据或地址。

在计算机系统中,寄存器用于快速访问和处理信息,它们是CPU内部的存储单元,用于执行算术和逻辑操作。

四、计算题(每题10分,共30分)1. 假设有一个4位的二进制计数器,起始计数值为0000,每次计数增加1。

数字电路试题及答案一、选择题1. 数字电路中最基本的逻辑门是以下哪一个?A. 与非门B. 或非门C. 与门D. 异或门答案:C2. 在二进制数系统中,用三个比特(bit)可以表示多少个不同的数值?A. 4B. 6C. 8D. 10答案:C3. 下列哪个触发器具有记忆功能?A. 组合逻辑B. 时序逻辑C. D型触发器D. T型触发器答案:C4. 在数字电路中,"0" 和 "1" 分别代表什么逻辑状态?A. 低电平 / 高电平B. 高电平 / 低电平C. 接地 / 供电D. 禁用 / 启用答案:A5. 以下哪种类型的逻辑门是使用晶体管实现开关功能的?A. 模拟门B. 数字门C. 模拟数字门D. 晶体管逻辑门答案:D二、填空题1. 在数字电路中,一个______门输出的高电平可以驱动多个输入端,而不会改变输出电平。

答案:或门2. _______是数字电路设计中的一种基本方法,它将复杂的电路分解为更简单的子电路。

答案:模块化设计3. 在数字电路中,一个______触发器在时钟信号的上升沿改变状态,而______触发器在下降沿改变状态。

答案:D型;JK型4. 一个4位二进制计数器的最大输出值是______。

答案:155. 在数字电路中,______是一种用于存储数据的电路,它可以在没有时钟信号的情况下保持信息。

答案:触发器三、简答题1. 请简述数字电路与模拟电路的主要区别。

答:数字电路处理的是离散的信号,通常只有两种状态(如高电平代表“1”,低电平代表“0”),而模拟电路处理的是连续变化的信号。

数字电路的主要优点是抗干扰能力强,易于实现逻辑运算和存储功能,而模拟电路则更擅长处理连续变化的信号,如音频和视频信号。

2. 什么是组合逻辑和时序逻辑?答:组合逻辑是指其输出仅依赖于当前输入信号的逻辑电路,不包含存储元件,如与门、或门和非门等。

时序逻辑则包含存储元件(如触发器),其输出不仅依赖于当前的输入信号,还依赖于历史状态,因此具有记忆功能。

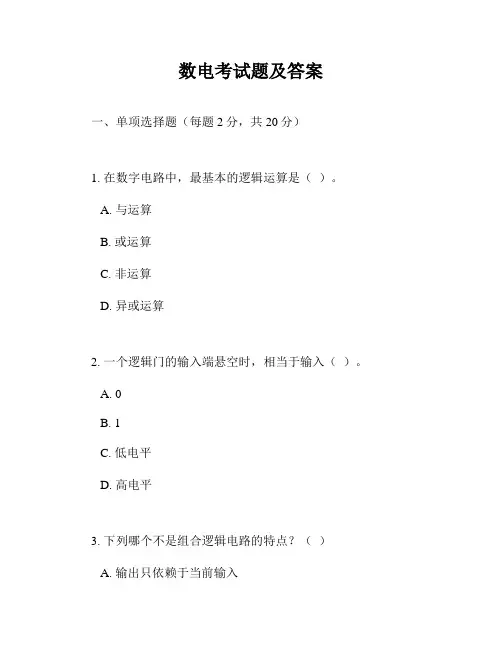

数电考试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑运算是()。

A. 与运算B. 或运算C. 非运算D. 异或运算2. 一个逻辑门的输入端悬空时,相当于输入()。

A. 0B. 1C. 低电平D. 高电平3. 下列哪个不是组合逻辑电路的特点?()A. 输出只依赖于当前输入B. 输出与输入之间存在时延C. 输出与输入之间没有记忆功能D. 输出与输入之间存在时延4. 在数字电路中,一个触发器可以存储()位二进制信息。

A. 1B. 2C. 4D. 85. 一个4位二进制计数器可以计数的最大值是()。

A. 7B. 15C. 16D. 2556. 下列哪个不是时序逻辑电路的特点?()A. 输出不仅依赖于当前输入,还依赖于电路状态B. 具有记忆功能C. 输出与输入之间存在时延D. 输出只依赖于当前输入7. 在数字电路中,一个D触发器的输出Q与输入D的关系是()。

A. Q=DB. Q=非DC. Q=D的非D. Q=非D的非8. 一个3线-8线译码器可以译码的输入信号有()种。

A. 2B. 4C. 8D. 169. 在数字电路中,一个JK触发器可以工作在()状态。

A. 稳定状态B. 振荡状态C. 稳定状态和振荡状态D. 以上都不是10. 一个8位A/D转换器的量化步长是()。

A. 1/8B. 1/16C. 1/256D. 1/512二、填空题(每题2分,共20分)1. 在数字电路中,逻辑“与”运算的符号是___________。

2. 一个2进制计数器的计数范围是___________。

3. 一个3位二进制数可以表示的最大十进制数是___________。

4. 在数字电路中,逻辑“或”运算的符号是___________。

5. 一个4位二进制数可以表示的最大十进制数是___________。

6. 在数字电路中,逻辑“非”运算的符号是___________。

7. 一个5位二进制数可以表示的最大十进制数是___________。

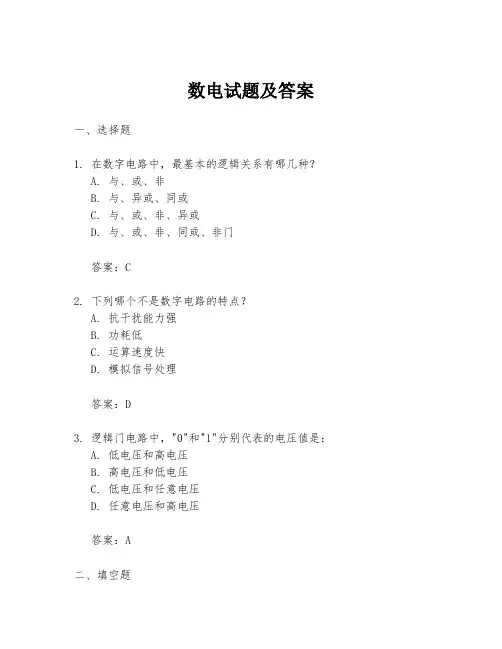

数电试题及答案一、选择题1. 在数字电路中,最基本的逻辑关系有哪几种?A. 与、或、非B. 与、异或、同或C. 与、或、非、异或D. 与、或、非、同或、非门答案:C2. 下列哪个不是数字电路的特点?A. 抗干扰能力强B. 功耗低C. 运算速度快D. 模拟信号处理答案:D3. 逻辑门电路中,"0"和"1"分别代表的电压值是:A. 低电压和高电压B. 高电压和低电压C. 低电压和任意电压D. 任意电压和高电压答案:A二、填空题1. 数字电路是由_______和_______构成的电路。

答案:逻辑门;组合逻辑2. 一个基本的逻辑门至少需要_______个输入端。

答案:13. 一个完整的数字系统通常包括_______、_______和_______。

答案:输入设备;处理单元;输出设备三、简答题1. 请简述数字电路与模拟电路的区别。

答案:数字电路主要处理离散的数字信号,使用二进制逻辑来表示和处理信息,具有抗干扰能力强、功耗低、运算速度快等特点。

而模拟电路处理连续变化的模拟信号,能够模拟自然界的物理量变化,但易受干扰,运算速度相对较慢。

2. 什么是组合逻辑电路?它有哪些特点?答案:组合逻辑电路是由逻辑门组成的电路,其输出只依赖于当前的输入状态,不包含存储元件。

其特点是输出对输入具有即时响应,没有记忆功能,且输出状态的确定性使得电路设计和分析相对简单。

四、计算题1. 给定一个逻辑表达式:Y = A'B + AB',其中A和B是输入变量,Y是输出。

如果A=1,B=0,求Y的值。

答案:将A=1,B=0代入表达式,得到Y = 1'0 + 10' = 0 + 0 = 0。

2. 计算以下逻辑电路的输出Z,当A=1,B=0,C=1时。

逻辑电路表达式:Z = (A + B')(A' + B + C)答案:将A=1,B=0,C=1代入表达式,得到Z = (1 + 0')(1' + 0 + 1) = (1)(1 + 1) = 2,但由于逻辑运算中只考虑0和1,因此Z的实际值为1。

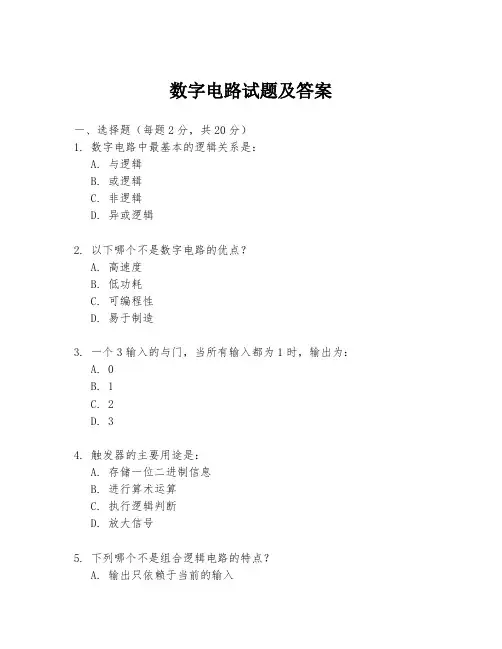

数字电路试题及答案一、选择题(每题2分,共20分)1. 数字电路中最基本的逻辑关系是:A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑2. 以下哪个不是数字电路的优点?A. 高速度B. 低功耗C. 可编程性D. 易于制造3. 一个3输入的与门,当所有输入都为1时,输出为:A. 0B. 1C. 2D. 34. 触发器的主要用途是:A. 存储一位二进制信息B. 进行算术运算C. 执行逻辑判断D. 放大信号5. 下列哪个不是组合逻辑电路的特点?A. 输出只依赖于当前的输入B. 输出可以延迟输入C. 没有记忆功能D. 可以进行复杂的逻辑运算二、填空题(每空2分,共20分)6. 一个典型的数字电路由________、________和输出三部分组成。

7. 一个4位二进制计数器可以计数的最大数值是________。

8. 一个D触发器的两个主要输入端是________和________。

9. 在数字电路中,________是一种常用的同步信号,用于协调电路的时序。

10. 一个3-8译码器可以将3位二进制信号转换为________种可能的输出状态。

三、简答题(每题15分,共30分)11. 简述数字电路与模拟电路的主要区别。

12. 解释什么是时钟信号,并说明它在数字电路中的作用。

四、计算题(每题15分,共30分)13. 给定一个逻辑表达式 Y = A'B + AB',使用卡诺图化简该表达式,并画出相应的逻辑电路图。

14. 设计一个2位二进制计数器,使用D触发器实现,并说明其工作原理。

答案一、选择题1. 答案:A(与逻辑)2. 答案:D(易于制造)3. 答案:B(1)4. 答案:A(存储一位二进制信息)5. 答案:B(输出可以延迟输入)二、填空题6. 答案:输入、处理7. 答案:15(2^4 - 1)8. 答案:数据输入(D)、时钟输入(CLK)9. 答案:时钟信号(Clock Signal)10. 答案:8三、简答题11. 数字电路与模拟电路的主要区别在于:数字电路处理的是离散的数字信号,而模拟电路处理的是连续的模拟信号。

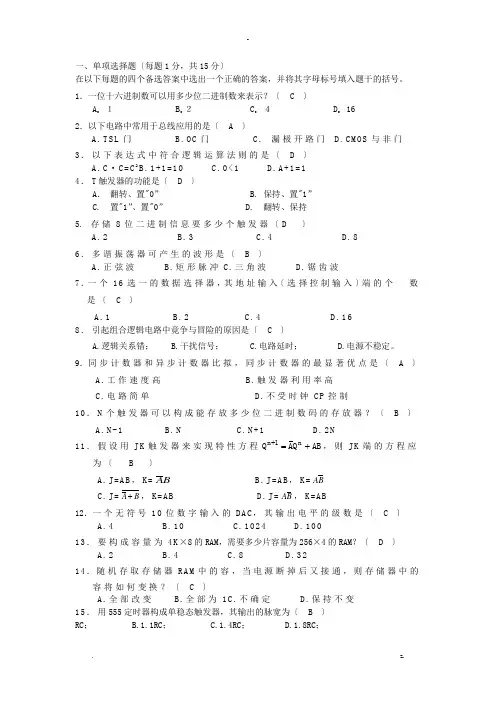

在以下每题的四个备选答案中选出一个正确的答案,并将其字母标号填入题干的括号。

1.一位十六进制数可以用多少位二进制数来表示?〔 C 〕A . 1B .2C . 4D . 162.以下电路中常用于总线应用的是〔 A 〕A.T S L 门B.O C 门C. 漏极开路门D.C M O S 与非门 3.以下表达式中符合逻辑运算法则的是〔 D 〕A.C ·C =C 2B.1+1=10C.0<1D.A +1=1 4.T 触发器的功能是〔 D 〕A . 翻转、置"0” B. 保持、置"1” C. 置"1”、置"0” D. 翻转、保持5. 存储8位二进制信息要多少个触发器〔D 〕A.2B.3C.4D.8 6.多谐振荡器可产生的波形是〔 B 〕A.正弦波B.矩形脉冲C.三角波D.锯齿波7.一个16选一的数据选择器,其地址输入〔选择控制输入〕端的个 数是〔 C 〕A.1B.2C.4D.16 8.引起组合逻辑电路中竟争与冒险的原因是〔 C 〕A.逻辑关系错;B.干扰信号;C.电路延时;D.电源不稳定。

9.同步计数器和异步计数器比拟,同步计数器的最显著优点是〔 A 〕 A.工作速度高 B.触发器利用率高C.电路简单D.不受时钟C P 控制10.N 个触发器可以构成能存放多少位二进制数码的存放器?〔 B 〕 A.N -1 B.N C.N +1 D.2N11.假设用J K 触发器来实现特性方程AB Q A Q n 1n +=+,则J K 端的方程应为〔 B 〕A.J =A B ,K =B AB.J =A B ,K =B AC.J =B A +,K =A BD.J =B A ,K =A B12.一个无符号10位数字输入的D A C ,其输出电平的级数是〔 C 〕A.4B.10C.1024D.100 13.要构成容量为4K ×8的RAM ,需要多少片容量为256×4的RAM ?〔 D 〕A.2B.4C.8D.32 14.随机存取存储器R A M 中的容,当电源断掉后又接通,则存储器中的容将如何变换?〔 C 〕A.全部改变B.全部为1C.不确定D.保持不变 15.用555定时器构成单稳态触发器,其输出的脉宽为〔 B 〕 RC ; B.1.1RC ; C.1.4RC ; D.1.8RC ;在以下每题的四个备选答案中有二至四个正确答案,请将正确答案全部选出并将其字母标号填入题干的括号;少选错选都不得分。

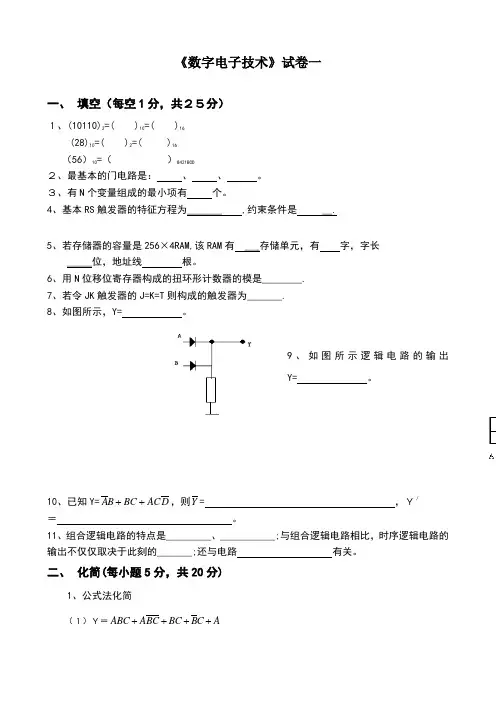

《数字电子技术》试卷一一、 填空(每空1分,共25分)1、(10110)2=( )10=( )16(28)10=( )2=( )16 (56)10=( )8421BCD2、最基本的门电路是: 、 、 。

3、有N 个变量组成的最小项有 个。

4、基本RS 触发器的特征方程为_______ ,约束条件是 __.5、若存储器的容量是256×4RAM,该RAM 有 ___存储单元,有 字,字长_____位,地址线 根。

6、用N 位移位寄存器构成的扭环形计数器的模是________.7、若令JK 触发器的J=K=T 则构成的触发器为_______.8、如图所示,Y= 。

9、如图所示逻辑电路的输出Y= 。

10、已知Y=D AC BC B A ++,则Y = ,Y/= 。

11、组合逻辑电路的特点是_________、___________;与组合逻辑电路相比,时序逻辑电路的输出不仅仅取决于此刻的_______;还与电路 有关。

二、 化简(每小题5分,共20分)1、公式法化简(1)Y=ABC ABC BC BC A ++++=+++(2)Y ABC A B C2、用卡诺图法化简下列逻辑函数=+++(1)Y BCD BC ACD ABDY=∑+∑(2)(1,3,4,9,11,12,14,15)(5,6,7,13)m d三、设下列各触发器初始状态为0,试画出在CP作用下触发器的输出波形(10分)四、用74LS161四位二进制计数器实现十进制计数器(15分)五、某汽车驾驶员培训班结业考试,有三名评判员,其中A 为主评判员,B 、C 为副评判员,评判时,按照少数服从多数原则,但若主评判员认为合格也可以通过。

试用74LS138和与非门实现此功能的逻辑电路。

(15分)P Q A Q B Q C Q D C T 74LS161 LD CPQ A 、Q B 、Q C 、Q D :数据输出端; A 、B 、C 、D :数据输入端; P 、T :计数选通端;r C :异步复位端;CP :时钟控制输入端;D L :同步并置数控制端;六、试分析如图电路的逻辑功能,设各触发器的初始状态为0(15分)《数字电子技术》试卷一参考答案一、填空(每空1分,共25分)1、10(22)、16(16);2(11100)、16(1)C ;8421(01010110)BCD 。

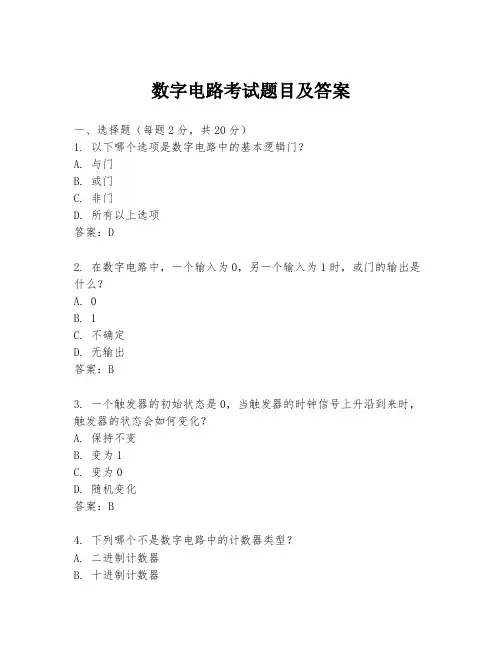

数字电路考试题目及答案一、选择题(每题2分,共20分)1. 以下哪个选项是数字电路中的基本逻辑门?A. 与门B. 或门C. 非门D. 所有以上选项答案:D2. 在数字电路中,一个输入为0,另一个输入为1时,或门的输出是什么?A. 0B. 1C. 不确定D. 无输出答案:B3. 一个触发器的初始状态是0,当触发器的时钟信号上升沿到来时,触发器的状态会如何变化?A. 保持不变B. 变为1C. 变为0D. 随机变化答案:B4. 下列哪个不是数字电路中的计数器类型?A. 二进制计数器B. 十进制计数器C. 十六进制计数器D. 模拟计数器答案:D5. 在数字电路中,一个D触发器的Q输出和Q'输出之间的关系是什么?A. 相同B. 相反C. 无关系D. 有时相同有时相反答案:B6. 一个4位二进制计数器能表示的最大数值是多少?A. 15B. 16C. 255D. 256答案:B7. 以下哪个不是数字电路中的编码方式?A. 二进制编码B. 格雷码编码C. 十进制编码D. 模拟编码答案:D8. 在数字电路中,一个异或门的输出为1的条件是什么?A. 输入相同B. 输入不同C. 至少一个输入为0D. 至少一个输入为1答案:B9. 一个3线到8线解码器有多少个输入线?A. 3B. 4C. 5D. 8答案:A10. 在数字电路中,一个锁存器和触发器的主要区别是什么?A. 锁存器可以保持一个稳定的状态,而触发器不能B. 触发器可以保持一个稳定的状态,而锁存器不能C. 两者没有区别D. 两者都是存储设备答案:B二、填空题(每题2分,共20分)1. 在数字电路中,一个3位二进制计数器可以表示的最大数值是__7__。

2. 如果一个触发器的J和K输入都是1,则触发器的状态将会__翻转__。

3. 在数字电路中,一个4位二进制计数器有__16__个不同的状态。

4. 一个D触发器的输出Q在时钟信号的__上升沿__时更新。

5. 一个3线到8线解码器可以产生__8__个输出。

数字电路试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是:A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑答案:A2. 一个3输入的与门,当所有输入都为高电平时,输出为:A. 低电平B. 高电平C. 浮空D. 不确定答案:B3. 触发器的两个稳定状态是:A. 0和1B. 正和负C. 高和低D. 真和假答案:A4. 下列哪个不是数字电路的优点?A. 高速度B. 高稳定性C. 低功耗D. 易于集成答案:C5. 以下哪个是组合逻辑电路的特点?A. 输出状态只与当前输入有关B. 具有记忆功能C. 输出状态与过去输入有关D. 以上都不是答案:A6. 一个D触发器的Q端在时钟信号上升沿触发时,其输出将:A. 保持不变B. 变为0C. 变为1D. 翻转答案:D7. 以下哪个逻辑门不是基本逻辑门?A. 与门B. 或门C. 非门D. 异或门答案:D8. 以下哪个是数字电路设计中的同步设计?A. 所有信号在同一个时钟信号下操作B. 信号在不同的时钟信号下操作C. 信号没有时钟信号D. 以上都不是答案:A9. 一个4位二进制计数器,其计数范围是:A. 0到3B. 0到7C. 0到15D. 1到4答案:C10. 在数字电路中,布尔代数的基本原理不包括:A. 幂等律B. 互补律C. 反演律D. 欧拉定律答案:D二、简答题(每题10分,共30分)1. 简述数字电路与模拟电路的主要区别。

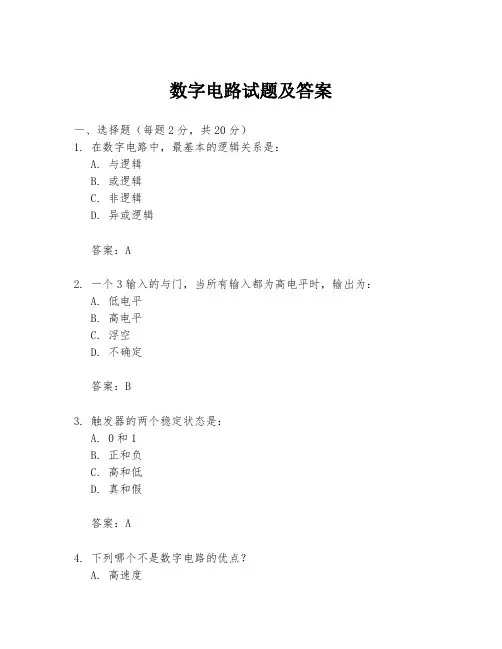

答:数字电路主要处理离散的数字信号,使用二进制数字表示信息,具有较高的抗干扰能力,易于实现大规模集成。

而模拟电路处理连续变化的模拟信号,使用电压或电流的连续变化来表示信息,通常需要较高的精度和稳定性。

2. 解释什么是时序逻辑电路,并给出一个例子。

答:时序逻辑电路是一种数字电路,其输出不仅依赖于当前的输入,还依赖于电路的历史状态。

这种电路通常包含存储元件,如触发器或寄存器。

一个常见的例子是计数器,它可以按照时钟信号的上升或下降沿进行计数。

数电考试题及答案一、选择题(每题1分,共10分)1. 数字电路中最基本的逻辑关系是()。

A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑2. 下列哪个不是数字电路的特点?()A. 抗干扰能力强B. 功耗低C. 体积小D. 工作速度慢3. 一个二进制数1011转换为十进制数是()。

A. 10B. 11C. 13D. 154. 在数字电路中,以下哪个不是基本的逻辑门?()A. 与门B. 或门C. 非门D. 放大门5. 触发器的主要用途是()。

A. 放大信号B. 存储信息C. 转换信号D. 滤波6. 一个完整的数字系统包括()。

A. 逻辑电路B. 电源C. 输入设备D. 所有选项7. 以下哪个不是数字电路的分类?()A. 组合逻辑电路B. 时序逻辑电路C. 模拟电路D. 存储电路8. 一个4位二进制计数器最多可以计数到()。

A. 8B. 16C. 32D. 649. 以下哪个是数字电路的优点?()A. 易受干扰B. 集成度高C. 功耗大D. 灵活性差10. 一个简单的数字钟至少需要多少个触发器?()A. 1B. 2C. 4D. 6二、填空题(每空1分,共10分)1. 数字电路中,最基本的逻辑运算包括________、________和________。

2. 一个二进制数1101转换为十进制数是________。

3. 触发器的两个稳定状态是________和________。

4. 一个数字电路系统由________、________和________组成。

5. 一个4位二进制计数器的计数范围是________到________。

三、简答题(每题5分,共20分)1. 简述数字电路与模拟电路的区别。

2. 解释什么是组合逻辑电路和时序逻辑电路。

3. 描述数字电路中的触发器是如何工作的。

4. 什么是数字电路的抗干扰能力?四、计算题(每题10分,共20分)1. 给定一个二进制数101101,转换为十进制数是多少?2. 如果一个数字钟使用4位二进制计数器,计算它的计数周期是多少秒?(假设时钟频率为1Hz)五、综合题(每题15分,共30分)1. 设计一个简单的数字电路,实现两个输入信号A和B的异或逻辑功能。

《数字电子技术基础》试卷一一填空题(22分每空2分)1、A 0 , A 1 ________ 。

2、JK触发器的特性方程为:。

3、单稳态触发器中,两个状态一个为态,另一个为态.多谐振荡器两个状态都为态,施密特触发器两个状态都为态.4、组合逻辑电路的输出仅仅只与该时刻的有关,而与无关。

5、某数/模转换器的输入为8位二进制数字信号(D7~D0),输出为0〜25.5V的模拟电压。

若数字信号的最低位是“1其余各位是“0”则输出的模拟电压为。

6、一个四选一数据选择器,其地址输入端有个。

二、化简题(15分每小题5分)用卡诺图化简逻辑函数,必须在卡诺图上画岀卡诺圈1) Y (A,B,C,D ) =Em (0,1,2,3,4,5,6,7,13,15)2) L(A, B,C,D) m(0,13,14,15) d(1,2,3,9,10,11)利用代数法化简逻辑函数,必须写岀化简过程3)F(A,B,C) AB ABC A(B AB)三、画图题(10分每题5分)据输入波形画输岀波形或状态端波形(触发器的初始状态为0)1、AJLBB丁L2、rLrmrLHT1 ~h 1< [i ~~i~■四、分析题(17分)1、分析下图,并写岀输岀逻辑关系表达式,要有分析过程(2、电路如图所示,分析该电路,画出完全的时序图,并说明电五、设计题(28分)1、用红、黄、绿三个指示灯表示三台设备的工作情况:绿灯亮表示全部正常;红灯亮表示有一台不正常;黄灯亮表示两台不正常;红、黄灯全亮表示三台都不正常。

列岀控制电路真值表,要求用74LS138和适当的与非门实现此电路(20分)2、中规模同步四位二进制计数器74LS161的功能表见附表所示;请用反馈预置回零法设计一个六进制加法计数器。

(8分)六、分析画图题(8分)画岀下图所示电路在V作用下,输岀电压的波形和电压传输特性74LS138功能表如下:2 / 26(勿74LS161功能表 清零 预置 使能 时钟 预置数据输入 输出 RD LDEP ETCPD C B AQ D Q C Q B Q A L XX X X XXXXL L L L H L X XT D C B AD C B A H H LXX XXXX 保 持 HH X LX XXXX 保 持 HHH HTXXXX计 数《数字电子技术基础》试卷一答案一、 填空题(22分每空2分)n 1nn1、A ,A2、Q JQ KQ3、稳态,暂稳态,暂稳态,稳态4、输入,电路原先状态5、0.1V6、两二、 化简题(15分 每小题5分)1) Y (A,B,C,D ) =Em (0,1,2,3,4,5,6,7,13,15) = A BDG1 G 2A G 2BC BAY 0Y 1Y 2Y 3Y 4Y 5Y 6Y 7 X H X X X XHHHHHHHHXX HX X XHHHHHHHHL XX XXXHHHHHHHHH L LL L L LHHHHHHHLL H HLHHHHHH H L LL H L HHLHHHHHLHHHHHLHHHHH L LH L L HHHHLHHH H L LH LH HHHHHLHH H L LH HLHHHHHHLHH L LH HHHHHHHHHLH L LH L L输 入输出2)L(A,B,C,D) m(0,13,14,15) d(1,2,3,9,10,11) AB AD AC3)F(A,B,C) AB ABC A(B AB) A B BC AB AB A B BC A 0 三、画图题(10分每题5分) 1、n2、 rA 1钉厂LTLrLTLRr 1 U1―r丁 H : ■ : um四、分析题(17分)1、(6 分) L A B2、(11 分) 五进制计数器12 34 5 67 8 9.JWWWWL五、设计题(28分) 1、(20 分) 1 )根据题意,列岀真值表 由题意可知,令输入为 A 、B 、C 表示三台设备的工作情况,A B C R Y G 0 0 01 1 0 00 10 1 0 0 1 0 0 1 0 0 1 1 1 0 0 1 0 0 0 1 0 1 0 1 1 0 0 11 0 1 0 0 11 10 0 1“1”表示正常,“0”表示不正常,令输岀为 R ,Y ,G 表示红、黄、绿二个批示灯的状态,“1”表示亮,“0”表示灭。

一、填空题:1.在计算机内部,只处理二进制数;二制数的数码为 1 、 0两个;写出从(000)2依次加1的所有3位二进制数: 000、001、010、011、100、101、110、111 。

2.13=(1101)2;(5A )16=(1011010)2;(10001100)2=(8C )16。

完成二进制加法(1011)2+1=(1100)2 3.写出下列公式:= 1 ;= B ;= A+B ;=B A +。

4.含用触发器的数字电路属于 时序逻辑电路 (组合逻辑电路、时序逻辑电路)。

TTL 、CMOS 电路中,工作电压为5V 的是 TTL ;要特别注意防静电的是 CMOS 。

5.要对256个存贮单元进行编址,则所需的地址线是 8 条。

6.输出端一定连接上拉电阻的是 OC 门;三态门的输出状态有 1 、 0 、 高阻态三种状态。

7.施密特触发器有 2 个稳定状态.,多谐振荡器有 0 个稳定状态。

8.下图是由触发器构成的时序逻辑电路。

试问此电路的功能是 移位寄存器 ,是 同步 时序电路(填同步还是异步),当R D =1时,Q 0Q 1Q 2Q 3= 0000 ,当R D =0,D I =1,当第二个CP 脉冲到来后,Q 0Q 1Q 2Q 3= 0100 。

(图一)1.和二进制数(111100111.001)等值的十六进制数是( B )A .(747.2)16B .(1E7.2) 16C .(3D7.1) 16D .(F31.2) 162.和逻辑式B A C B AC ++相等的式子是( A )R CPA.AC+B B. BC C.B D.BCA3.32位输入的二进制编码器,其输出端有( D )位。

A. 256B. 128C. 4D. 54.n位触发器构成的扭环形计数器,其无关状态数为个( B ) A.2n-n B.2n-2n C.2n D.2n-15.4个边沿JK触发器,可以存储( A )位二进制数A.4 B.8 C.166.三极管作为开关时工作区域是( D )A.饱和区+放大区B.击穿区+截止区C.放大区+击穿区D.饱和区+截止区7.下列各种电路结构的触发器中哪种能构成移位寄存器( C )A.基本RS触发器B.同步RS触发器C.主从结构触发器8.施密特触发器常用于对脉冲波形的( C )A.定时B.计数C.整形1.八进制数 (34.2 )8的等值二进制数为11100.01 ;十进制数 98 的8421BCD 码为10011000 。

数字电路试题及答案一、选择题1. 数字电路的基本组成单元是:A. 逻辑门B. 电源C. 电阻D. 电源线答案:A2. 下列哪种逻辑门的输出只有当所有输入都为高电平时才为高电平?A. 与门B. 或门C. 非门D. 异或门答案:A3. 使用逻辑门和触发器可以构建哪种类型的数字电路?A. 计数器B. 比较器C. 放大器D. 滤波器答案:A4. 下列哪种逻辑门的输出为输入信号的反相?A. 与门B. 或门C. 非门D. 异或门答案:C5. 在数字电路中,使用哪种逻辑门可以实现逻辑加法?A. 与门B. 或门C. 非门D. 异或门答案:D二、填空题1. 以下真值表表示的逻辑函数是______。

输入A | 输入B | 输出Y-----------------------------0 | 0 | 10 | 1 | 01 | 0 | 01 | 1 | 1答案:异或门2. 基本的二进制加法器是由______和______构成的。

答案:半加器和全加器3. 在数字电路中,时钟信号被用于控制______。

答案:触发器4. 使用______逻辑门,可以实现任意逻辑函数。

答案:与、或、非、与非5. ______________电路可以将电压信号进行放大。

答案:放大器三、解答题1. 简述半加器的功能和工作原理。

答案:半加器是一种能够实现二进制数相加的数字电路组件。

它接受两个输入信号A和B,并产生两个输出信号Sum和Carry。

Sum表示相加的结果,Carry表示进位的情况。

半加器的工作原理如下:- 将输入信号A和B分别输入两个异或门,得到的输出连接到一个与门,得到Sum。

- 将输入信号A和B分别输入一个与门和一个与非门,得到的输出连接到一个或门,得到Carry。

2. 请简要解释触发器的作用及其类型。

答案:触发器是一种能够存储和记忆输入信号状态的数字电路组件。

它可以在时钟信号的控制下,将输入的电平状态保持在输出上,实现状态的存储和延迟功能。

一、逻辑代数基础(逻辑函数化简、变换) (1小题) 1、解:(1)BD A D C B A Y +'=),,,((2)))(())((),,,(''•=''+'=BD A BD A D C B A Y(3)用反演定理得:D A B A D B A D C B A Y '+'='+'•=')(),,,( 或利用卡诺图得: D A B A D B A D C B A Y '+'='+'•=')(),,,(则))()(()(),,,(''+'+'+'=''+'=D A B A D A B A D C B A Y二、器件(门电路、触发器、存储器、ADC/DAC )(8小题)1、答:OC 门 )(1'=AB Y )(2'=CD Y )()()(21'+=''==CD AB CD AB Y Y Y2、答: 三态门EN=0时,)(1'=AB Y Y 2为高阻态 )('=AB Y EN=1时,Y 1为高阻态 )(2'=CD Y )('=CD Y 3、答:D = A ⊕Q CLK 上升沿触发 触发时Q * =D= A ⊕Q =AQ'+A'Q T 触发器 4、答:J = A 、K = A' CLK 的下降沿触发 Q * = JQ'+K'Q = A D 触发器 5、答:(1)RAM (2)地址线10根、数据线4根 (3)容量:210×4位 6、答:(1)4212⨯ (2)字扩展,因为数据线位数没变、增加了地址线位数。

7、答: D/A 转换器)2222(2001122334REF d d d d V v O +++−= 当4位数字量为0101时, v O =2.5V 8、答: A/D 转换器由mV 202V1.5≤n得8=n 分辨率8位 三、组合逻辑电路的设计(3小题)1、 解:(1(2)ABC +ABC C AB C B A BC A C O +'+'+'=(3)ABC C B A C B A C B A S +''+''+''=CA BC AB C O ++=(4)))()()()(('''''''''''=ABC C B A C B A C B A S))()()((''''=CA BC AB C O(5)逻辑图BC 101111011011 0 0 10 1000ABC 101111010001 01 10 100A2、解:(1(2)函数式)(765476543''•'•'•'=+++=m m m m m m m m Y )(763276322''•'•'•'=+++=m m m m m m m m Y )(753175311''•'•'•'=+++=m m m m m m m m Y)(176543210765432100''•'•'•'•'•'•'•'=+++++++=≡m m m m m m m m m m m m m m m m Y(3)电路图Y 32Y 13、解:(1)依题意得函数式如下:B S S A S S B A S S B S S A S S B A S S B A S S B S S A S S B A S S F '+'+'''+''+'''='+'+'''+''+'''=01010101010101010101)(),,,(与以下74LS152的函数式进行对比70126012501240123012************D A A A D A A A D A A A D A A A D A A A D A A A D A A A D A A A Y +'+'+''+'+''+''+'''=若令:12S A =、01S A =、A A =0,则160==D D 、B D D D D '====7432、051==D D 时,有F=Y 。

一.填空题(1分/空,共24分)1)十进制数(99.375)10=(1100011.011)2=(63.6)16。

2)数字电路按照其结构和工作原理分为两大类:组合逻辑电路和时序逻辑电路。

3)以下类型门电路多余的输入端应如何处理:TTL 与非门:接高电平或者悬空或者并联,CMOS 与非门:接高电平或者并联。

4)逻辑函数Y=AB+BC+CA 的与非-与非式为((AB)’(BC)’(CA)’)’。

5)三态输出门在普通门电路输出状态的基础上增加的状态为__高阻态___。

6)TTL 反相器的阈值电压为V TH =1.4V 。

若CMOS 反向器的V DD =10V 则其阈值电压为V TH =5V。

7)RS 触发器的特性方程为:Q*=S+R’Q ,(约束条件:SR=0),T 触发器的特性方程为:Q*=T’Q+TQ’。

8)16选1数据选择器的地址端有4位,n 个触发器构成计数器的最大计数长度为2n 。

9)如图(1-1)所示触发器电路中,当A=1时,输出状态为____Q=1___,如图(1-2)所示计数器电路为___6___进制计数器。

10)触发器三种触发方式分别为:电平触发,脉冲触发(主从触发),边沿触发,其中边沿触发的触发器抗干扰能力最强。

11)在多谐振荡器,单稳态触发器,施密特触发器中,施密特触发器中常用于波形的变换和整形,单稳态触发器常用于定时及延时,多谐振荡器常用于产生脉冲波形。

图(1-3)中555定时器接成的是施密特触发器。

√二.将下列逻辑函数化简为最简与-或形式(方法不限)(每小题5分,共15分,按步骤酌情给分)1)CDACD ABC AC Y +++=''2)求Y=BC AC C A B A +++))'')('((的反函数并化简=AC’+C(AB+AD’+D)Y’=[(A’B+AC’)’+(A’+C’)](B’+C’)=AC’+C(A+D)=[(A+B’)(A’+C)+A’+C’](B’+C’)=AC’+AC+CD =(AC+A’B’+B’C+A’+C’)(B’+C’)=A+CD=B’+C’3)356710(,,,)(,,,,)Y A B C D m m m m m =∑,给定约束条件:012480m m m m m ++++=。

《数字电子技术》试卷一一、 填空(每空1分,共25分)1、(10110)2=( )10=( )16(28)10=( )2=( )16(56)10=( )8421BCD2、最基本的门电路是: 、 、 。

3、有N 个变量组成的最小项有 个。

4、基本RS 触发器的特征方程为_______ ,约束条件是 __.5、若存储器的容量是256×4RAM,该RAM 有 ___存储单元,有 字,字长_____位,地址线 根。

6、用N 位移位寄存器构成的扭环形计数器的模是________.7、若令JK 触发器的J=K=T 则构成的触发器为_______.8、如图所示,Y= 。

9、如图所示逻辑电路的输出Y= 。

10、已知Y=D AC BC B A ++,则Y = ,Y/= 。

11、组合逻辑电路的特点是_________、___________;与组合逻辑电路相比,时序逻辑电路的输出不仅仅取决于此刻的_______;还与电路 有关。

二、化简(每小题5分,共20分)1、公式法化简++++(1)Y=ABC ABC BC BC A=+++(2)Y ABC A B C2、用卡诺图法化简下列逻辑函数=+++(1)Y BCD BC ACD ABDY=∑+∑(2)(1,3,4,9,11,12,14,15)(5,6,7,13)m d三、设下列各触发器初始状态为0,试画出在CP作用下触发器的输出波形(10分)四、用74LS161四位二进制计数器实现十进制计数器(15分)五、某汽车驾驶员培训班结业考试,有三名评判员,其中A 为主评判员,B 、C 为副评判员,评判时,按照少数服从多数原则,但若主评判员认为合格也可以通过。

试用74LS138和与非门实现此功能的逻辑电路。

(15分)P Q A Q B Q C Q D C T 74LS161 LD CPA B C D CrQ A 、Q B 、Q C 、Q D :数据输出端; A 、B 、C 、D :数据输入端; P 、T :计数选通端;r C :异步复位端;CP :时钟控制输入端;D L :同步并置数控制端;C :位输出端;六、试分析如图电路的逻辑功能,设各触发器的初始状态为0(15分)《数字电子技术》试卷一参考答案一、填空(每空1分,共25分)1、10(22)、16(16);2(11100)、16(1)C ;8421(01010110)BCD 。

2、与、或、非。

3、2N。

4、10n n Q S RQ RS +=+=5、1024、256、4位、8根。

6、2N 。

7、T 触发器。

8、Y=A+B 。

9、Y AB CD =+10、()()()Y A B B C A C D =++++;Y/=()()()A B B C A C D ++++11、即刻输入、即刻输出;输入信号、原来状态。

二、化简(每小题5分,共20分)1、公式法:Y A C =+;1Y =2、卡诺图法:Y BC BD =+;Y B D =+三、(本题10分)四、(本题15分)反馈置“0”法:五、(本题15分)解:根据设计要求,设输入变量为A (主评判员)、B 、C (副评判员)=1时,认为合格;A 、B 、C=0时认为不合格;输出变量为L=1通过,L=0不通过。

六、(本题15分)《数字电子技术》试卷二一、填空(每空1分,共20分)1、(1001101)2=( )10=( )8=( )16;(27)10=( )8421BCD 。

2、客观事物的最基本的逻辑关系有____ 逻辑____ 逻辑和_____逻辑三种。

3、函数1F A BB C 的反演式1F = ;函数2F ABC 的对偶式'2F = 。

4、51个“1”连续进行异或运算,其结果是 。

5、基本R-S 触发器的特征方程为_______ ;约束条件是 。

6、按照逻辑功能的不同特点,数字电路可分为______________、_____________两大类。

7、J-K 触发器,当J=K=0时,触发器处于_________状态;J=0、K=1时,触发器状态为________;K=0、J=1时,触发器状态为_________;J=K=1时,触发器状态__________。

8、某中规模寄存器有3个触发器,用它构成的扭环型计数器模长为 ;构成最长模计数器模长为 。

二、化简(每题5分,共20分) 1、用公式法化简下列逻辑函数。

1) AB B A AB B A F ++⊕=)(2)F A B AD BD BCE2、用卡诺图法化简下列逻辑函数。

1)∑=m F (0,2,3,4,8,10,11)2) ∑=m F (0,1,4,9,12,)+∑d (2,3,6,10,11,14)三、设计一个三变量判偶电路,当输入变量A,B,C中有偶数个1时,其输出为1;否则输出为0。

并用3/8线译码器(74LS138)和适当门电路实现。

(16分)四、如下图所示维持阻塞D触发器,设初态为0。

根据CP脉冲及A输入波形画出Q波形。

(8分)五、用74LS161构成六进制计数器,用两种方法实现,并画出状态图。

74LS161的功能表如下所示。

(16分)六、试分析下图的逻辑电路,写出电路的驱动方程、状态方程、列出状态转换真值表、画出状态转换图,说明电路的逻辑功能。

(20分)《数字电子技术》试卷二参考答案一、填空(每空1分,共20分) 1、77,115,4D ,00100111。

2、与、或、非。

3、()()A B B C ,()A B C 。

4、1。

5、1nn Q SR Q ,1RS(或RS=0)。

6、组合逻辑电路,时序逻辑电路。

7、保持,置“0”,置“1”,翻转(或计数)。

8、6,7。

二、化简(每题5分,共20分)1、1)F=A+B 2)F AD B2、1)F BD B CA CD 2)FABBDBD《数字电子技术》试卷三一、填空题(共19分,每空1分)1.按逻辑功能的不同特点,数字电路可分为 和 两大类。

2.在逻辑电路中,三极管通常工作在 和 状态。

3.(406)10=( )8421BCD4.一位数值比较器的逻辑功能是对输入的 数据进行比较,它有 、 、 三个输出端。

5.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接 电平。

6.单稳态触发器有两个工作状态 和 ,其中 是暂时的。

7.一般ADC 的转换过程由 、 、 和 4个步骤来完成。

8.存储器的存储容量是指 。

某一存储器的地址线为A 14~A 0 ,数据线为D 3~D 0 ,其存储容量是 。

一、 判断题(共16分,每题2分)1.TTL 或非门多余输入端可以接高电平。

( )2.寄存器属于组合逻辑电路。

( )3.555定时器可以构成多谐振荡器、单稳态触发器、施密特触发器。

( )4.石英晶体振荡器的振荡频率取决于石英晶体的固有频率。

( )5.PLA 的与阵列和或阵列均可编程。

( )6.八路数据分配器的地址输入(选择控制)端有8个。

( )7.关门电平U OFF 是允许的最大输入高电平。

( )8.最常见的单片集成DAC 属于倒T 型电阻网络DAC 。

( )三、选择题(共16分,每题2分)1.离散的,不连续的信号,称为( )。

A .模拟信号 B.数字信号2.组合逻辑电路通常由( )组合而成。

A .门电路 B.触发器 C.计数器3.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是( )。

A .111 B.010 C.000 D.1014.十六路数据选择器的地址输入(选择控制)端有( )个。

A .16 B.2 C.4 D.85.一位8421BCD 码译码器的数据输入线与译码输出线的组合是( )。

A .4:6 B.1:10 C.4:10 D.2:4A .逐次逼近型ADC B.双积分ADC C.并联比较型ADC7.ROM 属于( )。

A .组合逻辑电路 B.时序逻辑电路8.有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是( )。

A.1011--0110--1100--1000—0000B.1011--0101--0010--0001—0000四、综合题(32分)1、对下列Z 函数要求:(1)列出真值表;(2)用卡诺图化简;(3)画出化简后的逻辑图。

(9分)Z=C B A C B A B A ••+••+ BC=02、对下列门电路:(1)写出门电路的名称;(2)写出它们的输出。

(8分) 例:与门 Y=AB(a) (b) (c) (a)(b)(c) (d) (d) 3、分析下列电路是几进制的计数器。

(10分)=1 YBA & YBA &BAYEN C u O u I TG路,(3)画出相应的输出波形。

(5分)五、设计题(17分)1、试用3线—8线译码器74LS138和门电路实现下列函数。

(10分)Z (A 、B 、C )=AB+A C2、 74LS161是同步4位二进制加法计数器,其逻辑功能表如下,试分析下列电路是几进制计数器,并画出其状态图。

(7分)74LS161逻辑功能表Ou IV CC1 3 V23 Vu ou tt《数字电子技术》试卷三答案 一、填空题(共19分,每空1分) 组合逻辑电路、 时序逻辑电路 1. 饱和、 截止2. 0100 0000 01103. A 和B 两个、 Y A>B 、 Y A<B 、 Y A=B 4. 高5. 稳态、 暂稳态、暂稳态 6. 采样、 保持、 量化、 编码 7. 存储单元的总和、 215×4二、判断题(共16分,每题2分)1.× 2.× 3.√ 4.√ 5.√ 6.× 7.× 8.√三、选择题(共16分,每题2分)1.B 2.A 3.C 4.C 5.C 6.B 7.A 8.A四、综合题1、解(1)真值表 (2分) (2)卡诺图化简(3分) CP“1” “1” “1”(3)逻辑图 (表达式2分,逻辑图2分)Z=C B A B A ++=A⊕B+C BC=02、解(a) 异或门 Y=B A B A += A ⊕B (2分) (b) 集电极开路与非门 Y=B A •(2分)(c) 三态门 EN =0时, Y=B A •;EN =1时,Y=高阻抗 (2分) (d) CMOS 传输门 C=1、C=0时,u O = u I (2分)3、解: n n0010101,1,,J K J Q K Q ==== 10Z Q Q = (1分)nn+1n ()Q JQ KQ CP =+↓n+1n n n n n 00000000Q 11 ()J Q K Q Q Q Q CP =+=•+•=↓n+1n n n n n n 111110101Q ()J Q K Q Q Q Q Q CP =+=+↓ (2分)状态表 (3分)归纳上述分析结果可知,该时序电路为同步4进制加法计数器。