三人表决器的Multisim仿真

- 格式:doc

- 大小:79.50 KB

- 文档页数:4

三人表决器摘要本次设计的三人表决器,是投票系统中的客户端,是一种代表投票或举手表决的表决装置。

表决时,与会的有关人员只要按动各自表决器上“赞成”“反对”“弃权”的某一按钮,荧光屏上即显示出表决结果。

在三人表决器中三个人分别用手指拨动开关S W1、S W2、S W3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。

表决结果用L E D(高电平亮)显示,如果决议通过那么实验板上L2亮;如果不通过那么实验板上L1亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮。

一.任务设计三人表决器电路,并在仿真软件上验证电路的正确性。

二.目标掌握三人表决器电路的结构。

学会仿真软件数字部分的操作。

三.要求1复习三人表决器电路的设计步骤。

2熟悉用集成电路的引脚位置及各引脚用途。

3使用TTL门电路时,一定要正确连接电源端和接地端4按集成电路引脚图正确接线,芯片电源引脚不要接错,以免损坏芯片,影响实验正常进行。

四.实训工具及设备电脑一台;Mult isi m软件五.仿真电路图六.设计的主要内容:按照设计题目,根据所学的组合逻辑所学的知识及数字电路和嵌入式的知识完成三人表决器的设计,使之能够满足表决时少数服从多数的表决规则,根据逻辑真值表和逻辑表达式完成表决功能。

七.三人表决器概述:1.三人表决器的功能描述三个人分别用手指拨动开关S W1、S W2、S W3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。

表决结果用LE D (高电平亮)显示,如果决议通过那么实验板上L2亮;如果不通过那么实验板上L1亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮2.三人表决器”的逻辑功能表决结果与多数人意见相同。

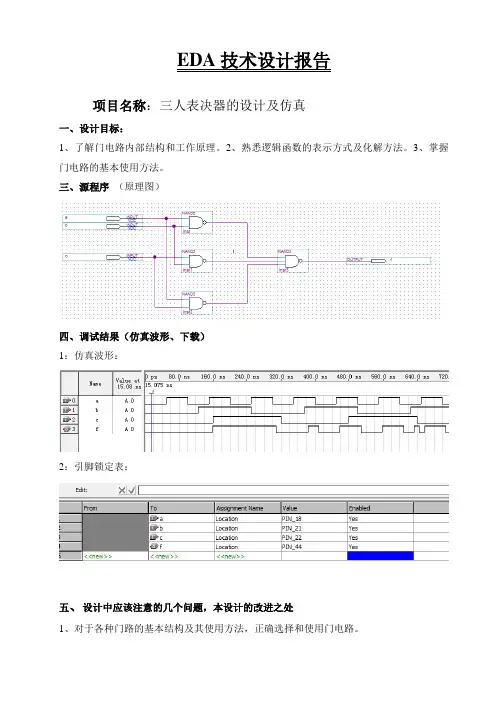

EDA技术设计报告

项目名称:三人表决器的设计及仿真

一、设计目标:

1、了解门电路内部结构和工作原理。

2、熟悉逻辑函数的表示方式及化解方法。

3、掌握门电路的基本使用方法。

三、源程序(原理图)

四、调试结果(仿真波形、下载)

1:仿真波形:

2:引脚锁定表:

五、设计中应该注意的几个问题,本设计的改进之处

1、对于各种门路的基本结构及其使用方法,正确选择和使用门电路。

2、设计时注意怎样才能实现三人表决,源程序的设计一定要有理有据。

3、引脚分配时注意分清设计的源程序中哪些是输入端,哪些是输出端,根据引脚对照表确定引脚分配。

参考文献:。

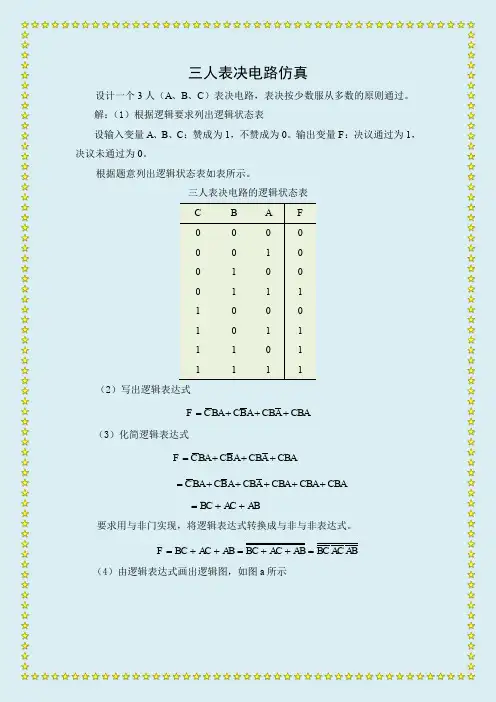

技能训练-仿真设计三人投票表决电路一.实训目的1.掌握简单应用电路的设计及测试方法2.掌握使用仿真软件Multisim 10进行电路的仿真调试3. 熟悉逻辑电路设计的流程二.实训器材1.设计题目试设计一个3人表决电路,多数人同意,提案通过,否则提案不通过。

2. 设计步骤用小规模集成电路设计组合逻辑电路的一般步骤如下:(1)分析设计任务,确定输入变量、输出变量,找到输出与输入之间的因果关系,列出真值表;(2)由真值表写出逻辑表达式;(3)化简变换逻辑表达式;(4)根据表达式画出逻辑图。

3. 根据逻辑图选择集成电路芯片,并进行仿真调试。

(1)设计流程可参照例(2)选择不同的逻辑图,就会有不同的仿真电路,同理,实现同一功能的实际电路也会不同。

4. 仿真电路示例,如图1-80所示。

图1-80 三人投票表决仿真电路5.自己设计实训表格,将仿真结果填入表格中。

四.注意事项1.熟悉Multisim 10仿真软件的基本操作,了解各个元件的位置。

2.仿真仅仅是对电路设计的验证、调试,电路设计的关键在原理图的设计。

3. 想一想:针对本任务的设计题目,试用不同的逻辑电路图及不同的集成电路芯片实现本题目的要求。

五.实训考核任务:仿真设计三人投票表决电路班级姓名组号扣分记录得分项目配分考核要求评分细则正确连接电路20分能使用仿真软件,并能正确连接电路1.不会使用仿真软件扣10分2.未能正确连接电路扣5分能用与非门实现本题目的要求30分能正确进行仿真,能满足本题目的要求1.连接方法不正确,每处扣5分2.不能正确进行仿真,扣5分3.结果不准确,每次扣5分能用或门30能正确进行仿真,1.连接方法不正确,每处。

电子设计自动化作业姓名:班级:院系:学号:三人表决器的ewb仿真EWB 软件,全称为ELECTRONICS WORKBENCH EDA ,是交互图像,技术有限公司在九十年代初推出的EDA软件,用于模拟电路和数字电路的混合仿真,利用它可以直接从屏幕上看到各种电路的输出波形。

EWB是一款小巧,但是仿真功能十分强大的软件。

EWB软件兼容性好,设计方便简洁,是可执行文件,无需安装。

并且软件仪器的控制面板外形和操作方式都与实物相似,可以实时显示测量结果,它带有丰富的电路元件库,提供多种电路的分析方法。

EWB还是一个优秀的电子技术训练工具,利用它提供的虚拟仪器可以用比实验室中更灵活的方式进行电路实验,仿真电路的实际运行情况,熟悉常用电子仪器测量方法。

下面就是我用软件制作的三人表决器的电路图的过程以及结果。

首先选择合适的译码器,这里我选择的是74138译码器,如图:■ [-»<*■« WMton二• B'H 亓X 乓El * L.J X % ':、3 - ?Id =F T V 茁特器&|ol «|rilD^kviK-i ET 1曲凸凸口已 1 ■亠亠亠・亠土J4HBIA VCC G2ft r Y2 石西 ¥3 G1 Y4 Y7 Y5 GND Y6J6a 15314 4 c 13 5 £ 1£6117 ID974138然后拉出两个电源+Vcc ,左右各一个,引脚分别连在 6和16两个引 脚处,如下图-=]”yD 阍P|q] t |g| “胡引 逅_f] 31 轲*" _7j E3肝」¥于阖引聲闊劄辛即I 刨叩I 期割匡亠丰1①⑥逾1 2 州斛啊刊逾| ©矽期嘲©心 引辎如闊国1F 面开始做甲乙丙三人的表决电路, 拉出一个单刀双掷开关,进 行旋转如图:JJWjL-WDltftPlal 闽鼻1割7辺團耳瓦和 曰?|hB 1-D山:,m. * 阿sma] gi P<K开关的一端连在1引脚处,另外的两处引脚分别连接+Vcc 和地线, 如图:鼻 H K &^HKI WorJUmchPh- EdH Circuit Aiulyvc '^AnicM 1-liUpD 两61唇就血i w i 占i因遽i 乖i j • H 丄 ■再豊也1织帶m 初创叩i .取毋同]刚UrtHrcUhl J 」lh斛斛眸1莎:|色画-》令搁锢日翩诩舉画©:电路做好了,但是缺少现实甲乙丙三人各自的表决结果, 现在就要在三路电路上分别连上三个灯作为指示,三个灯的lebal 值分别改成甲■T ==AS 也I Q I L UILi^Jl申炉Ti>wv 777+L35口科p4JEHD1rs①i 剧④i 砸肆平 囤逾1 <制©佥| “1|亠亠士土亠亠V匚:.•、、?21LmiHn■岸~r 如引罩闇罩I 喇钢剧叩州=?占站砒如EhIt Edl心临鸞」忖怛码WMfc- Hdp二JU 3 「底屯*. .1 月c_. Y :+、呎目古引引赛闔创辛坯母阳四引最后设计显示电路,需要用到一个与门,当两者以上同意时灯才会亮®:把12和10引脚连接到与门的上引脚,地线和9引脚连接到下引脚, 在另外一个引脚处连接一个灯作为显示如图:寺笛川订旱障障1 豆却1 四M E?il Logk^Hes r^0列[>£>|£>严i产1罗鬥門严]第[3l^uUl1 Lh——2-卡亠J*.n7433SiMvctNcs Wartibe«iichEJ-I Lircul Arul^ua WinH 口科HUp匸卜V押安D、徒 E 曲匚虹uii 白w 坐£知ddcw M(4p5-罰可点禹宅I 輻型皿|崙|心|园 翎 区|聊1"« 日_rj这样,一个三人表决器的模拟仿真电路图就完成了, 当甲乙丙三个灯 亮两个以上显示灯都会亮。

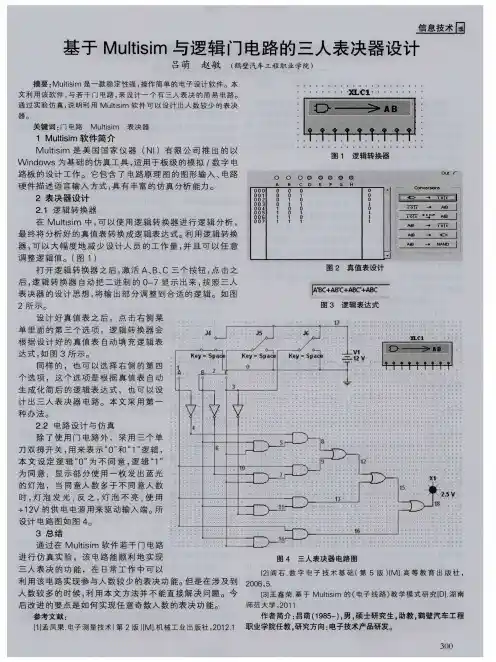

Multisim14多人表决器电路设计实验原理

一、实验原理:

电路由3个74L。

SO0N与非门电路和1个74LS10N与非门电路构成,当A,B。

C中任意两人按下按钮,工作电路向74LSO0N任意一个与非门电路输入2个高电平,输出1个低电平,输入到74LS10N与非门电路中,进而输出高电平,使得发光二极管发光,三人举手表决电路完成。

二、实验内容:

以少数服从多数的原则表决事件,输入A、B、C,同意为输入高电平(逻辑1 ),否则,不同意为输入低电平(逻辑0)。

输出L逻辑1表示赞成通过;输出逻辑0表示表示反对不通过。

验证实验结果:

用multisim字发生器实现高低电平输入,作为A、B、C的输入电平。

可将字发生器设置为单步调试,时钟频率1KHz,缓冲区大小(0008)H,上数序计数/下数序计数。

测试输出端L的输出高低电平,可以采用输出显示的发光二极管来测试。

将输出接至发光二极管的阳极,发光二极管的阴极接地;如果发光二极管发光,表示为高电平,否则为低电平。

为更直观观察输出现象,可在器件组中选择虚拟3D元件( 3D_VIRTUAL ) Led。

另一种测试方案即将输入A、B、C及输出L连接至逻辑分析仪观察波形图,看其是否满足逻辑函数表达式。

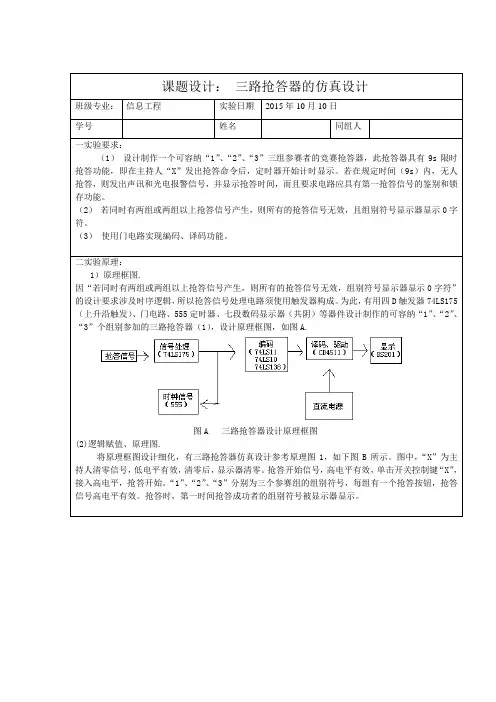

课题设计:三路抢答器的仿真设计班级专业:信息工程实验日期2015年10月10日学号姓名同组人一实验要求:(1)设计制作一个可容纳“1”、“2”、“3”三组参赛者的竞赛抢答器,此抢答器具有9s限时抢答功能,即在主持人“X”发出抢答命令后,定时器开始计时显示。

若在规定时间(9s)内,无人抢答,则发出声讯和光电报警信号,并显示抢答时间,而且要求电路应具有第一抢答信号的鉴别和锁存功能。

(2)若同时有两组或两组以上抢答信号产生,则所有的抢答信号无效,且组别符号显示器显示0字符。

(3)使用门电路实现编码、译码功能。

二实验原理:1)原理框图.因“若同时有两组或两组以上抢答信号产生,则所有的抢答信号无效,组别符号显示器显示0字符”的设计要求涉及时序逻辑,所以抢答信号处理电路须使用触发器构成。

为此,有用四D触发器74LS175(上升沿触发)、门电路、555定时器、七段数码显示器(共阴)等器件设计制作的可容纳“1”、“2”、“3”个组别参加的三路抢答器(1),设计原理框图,如图A.图A 三路抢答器设计原理框图(2)逻辑赋值、原理图.将原理框图设计细化,有三路抢答器仿真设计参考原理图1,如下图B所示。

图中,“X”为主持人清零信号,低电平有效,清零后,显示器清零。

抢答开始信号,高电平有效,单击开关控制键“X”,接入高电平,抢答开始。

“1”、“2”、“3”分别为三个参赛组的组别符号,每组有一个抢答按钮,抢答信号高电平有效。

抢答时,第一时间抢答成功者的组别符号被显示器显示。

图B 三路抢答器原理图(3)译码表.按设计要求,有七段数码显示器译码/驱动电路Ug(CD4511)对应的译码表,如下图C所示。

七段数码显示器的限流电阻R,取数码管的正向导通压降为2V,工作电流为6mA左右,有R=(5-2)/6kΩ=500Ω左右,取为E24系列值510Ω。

图C 七段译码显示电路的译码表四D触发器74LS175输出译码/驱动电路CD4511输入显示器对应显示Q3 Q2 Q1 D C B A0 0 0 0 0 0 0 00 0 1 0 0 0 1 10 1 0 0 0 1 0 20 1 1 0 0 0 0 01 0 0 0 0 1 1 31 0 1 0 0 0 0 01 1 0 0 0 0 0 01 1 1 0 0 0 0 0三、实验仪器和设备:四D触发器74LS175、门电路、555定时器、七段数码显示器、3线—8线译码器74LS138与非门74LS10、Multisium12.0软件四`、实验内容和步骤:(1)9秒定时抢答设计(如图D所示)当主持人没有发出抢答命令时,U2(74LS175)的CLR=0,清零信号有效,U2被清零;同时,使74LS190(U9)的LD=0,并行异步置数功能生效;U2的输出Q3Q2Q1Q0=d3d2d1d0=0000;计时数码管译码/驱动电路U3(CD4511)驱动计时数码管U4显示0字符。

数字电子技术仿真实验报告实验名称:组合逻辑电路设计学生姓名:刘佳璇学号:********指导教师:**院系:电气工程学院班级:201502D2017 年11 月29 日组合逻辑电路设计一、实验目的1、学会使用 MULTISIM 软件进行数字电子实验仿真。

2、能用指定的芯片完成组合逻辑电路的设计。

3、实验验证所设计的逻辑电路的逻辑功能。

4、熟悉各种集成门电路及争取使用集成门电路。

二、实验内容三人表决器三、实验原理设计组合逻辑电路的一般步骤如图所示。

逻辑表达式的化简过程是组合逻辑电路设计的关键,关系到电路组成是否最佳,以及使用的逻辑门的数量是否最少。

由于逻辑表达式不是唯一的,因此需要从实际出发,结合手中所有的逻辑门种类,将化简的表达式进行改写,以实现其逻辑功能。

要求电路最简(器件最少,器件间的连线最少)。

74LS20引脚排列图表决三人电路真值表见下表:Array写出逻辑函数表达式:+Y+=A+CCABCABBABC化简得:AB AC BC Y ++=AB AC BC Y ++=画出逻辑电路图:四、 实验设计与仿真构建仿真电路如图所示:验证:A=1,B=0,C=0时输出信号指示灯不亮,Y=0A=0,B=1,C=1时输出信号指示灯亮,Y=1测试波形连线路:字发生器设置如下:波形如下:仿真结果与实验结果一致。

五、实验小结这次的仿真实验是组合逻辑电路设计,我选择了三人表决器的设计,仿真结果与计算结果完全吻合。

实验六 三相电路仿真实验一、实验目的1、 熟练运用Multisim 正确连接电路,对不同联接情况进行仿真;2、 对称负载和非对称负载电压电流的测量,并能根据测量数据进行分析总结;3、 加深对三相四线制供电系统中性线作用的理解。

4、 掌握示波器的连接及仿真使用方法。

5、 进一步提高分析、判断和查找故障的能力。

二、实验仪器1.PC 机一台 2.Multisim 软件开发系统一套 三、实验要求1.绘制出三相交流电源的连接及波形观察 2.学习示波器的使用及设置。

3.仿真分析三相电路的相关内容。

4.掌握三瓦法测试及二瓦法测试方法 四、原理与说明1、负载应作星形联接时,三相负载的额定电压等于电源的相电压。

这种联接方式的特点是三相负载的末端连在一起,而始端分别接到电源的三根相线上。

2、负载应作三角形联接时,三相负载的额定电压等于电源的线电压。

这种联接方式的特点是三相负载的始端和末端依次联接,然后将三个联接点分别接至电源的三根相线上。

3、电流、电压的“线量”与“相量”关系测量电流与电压的线量与相量关系,是在对称负载的条件下进行的。

画仿真图时要注意。

负载对称星形联接时,线量与相量的关系为: 〔1〕P L U U 3= 〔2〕P L I I =负载对称三角形联接时,线量与相量的关系为:〔1〕P L U U = 〔2〕P LI I 3=4、星形联接时中性线的作用三相四线制负载对称时中性线上无电流,不对称时中性线上有电流。

中性线的作用是能将三相电源及负载变成三个独立回路,保证在负载不对称时仍能获得对称的相电压。

如果中性线断开,这时线电压仍然对称,但每相负载原先所承受的对称相电压被破坏,各相负载承受的相电压高低不一,有的可能会造成欠压,有的可能会过载。

五、实验内容及参考实验步骤 〔一〕、建立三相测试电路如下:V1220 V50 Hz 0Deg V2220 V 50 Hz 120Deg V3220 V 50 Hz 240DegX3220 V X4220 VJ2Key = BJ1Key = A43X1220 VX2220 V26NN'UVWJ3Key = C15图1 三相负载星形联接实验电路图1.接入示波器:测量ABC 三相电压波形。

实验六 三相电路仿真实验一、实验目的1、 熟练运用Multisim 正确连接电路,对不同联接情况进行仿真;2、 对称负载和非对称负载电压电流的测量,并能根据测量数据进行分析总结;3、 加深对三相四线制供电系统中性线作用的理解。

4、 掌握示波器的连接及仿真使用方法。

5、 进一步提高分析、判断和查找故障的能力。

二、实验仪器1.PC 机一台 2.Multisim 软件开发系统一套 三、实验要求1.绘制出三相交流电源的连接及波形观察 2.学习示波器的使用及设置。

3.仿真分析三相电路的相关内容。

4.掌握三瓦法测试及二瓦法测试方法 四、原理与说明1、负载应作星形联接时,三相负载的额定电压等于电源的相电压。

这种联接方式的特点是三相负载的末端连在一起,而始端分别接到电源的三根相线上。

2、负载应作三角形联接时,三相负载的额定电压等于电源的线电压。

这种联接方式的特点是三相负载的始端和末端依次联接,然后将三个联接点分别接至电源的三根相线上。

3、电流、电压的“线量〞与“相量〞关系测量电流与电压的线量与相量关系,是在对称负载的条件下进行的。

画仿真图时要注意。

负载对称星形联接时,线量与相量的关系为: 〔1〕P L U U 3= 〔2〕P L I I =负载对称三角形联接时,线量与相量的关系为:〔1〕P L U U = 〔2〕P LI I 3=4、星形联接时中性线的作用三相四线制负载对称时中性线上无电流,不对称时中性线上有电流。

中性线的作用是能将三相电源及负载变成三个独立回路,保证在负载不对称时仍能获得对称的相电压。

如果中性线断开,这时线电压仍然对称,但每相负载原先所承受的对称相电压被破坏,各相负载承受的相电压上下不一,有的可能会造成欠压,有的可能会过载。

五、实验内容及参考实验步骤 〔一〕、建立三相测试电路如下:V1220 V50 Hz 0Deg V2220 V 50 Hz 120Deg V3220 V 50 Hz 240DegX3220 V X4220 VJ2Key = BJ1Key = A43X1220 VX2220 V26NN'UVWJ3Key = C15图1 三相负载星形联接实验电路图1.接入示波器:测量ABC 三相电压波形。

数字电子技术仿真实验报告

实验名称:组合逻辑电路设计

学生姓名:刘佳璇学号:

指导教师:金丹

院系:电气工程学院班级: 201502D

2017 年 11 月 29 日

组合逻辑电路设计

一、实验目的

1、学会使用 MULTISIM 软件进行数字电子实验仿真。

2、能用指定的芯片完成组合逻辑电路的设计。

3、实验验证所设计的逻辑电路的逻辑功能。

4、熟悉各种集成门电路及争取使用集成门电路。

二、实验内容

三人表决器

三、实验原理

设计组合逻辑电路的一般步骤如图所示。

逻辑表达式的化简过程是组合逻辑电路设计的关键,关系到电路组成是否最佳,以及使用的逻辑门的数量是否最少。

由于逻辑表达式不是唯一的,因此需要从实际出发,结合手中所有的逻辑门种类,将化简的表达式进行改写,以实现其逻辑功能。

要求电路最简(器件最少,器件间的连线最少)。

表决三人电路真值表见下表:

写出逻辑函数表达式:

Y+

+

=

A

+

BC

C

ABC

C

AB

B

A

化简得:

+

Y+

=

AC

BC

AB

+

Y+

=

AB

AC

BC

画出逻辑电路图:

四、实验设计与仿真

构建仿真电路如图所示:

验证:

A=1,B=0,C=0时输出信号指示灯不亮,Y=0 A=0,B=1,C=1时输出信号指示灯亮,Y=1测试波形连线路:

字发生器设置如下:

波形如下:

仿真结果与实验结果一致。

五、实验小结

这次的仿真实验是组合逻辑电路设计,我选择了三人表决器的设计,仿真结果与计算结果完全吻合。