编程说明

- 格式:doc

- 大小:13.00 KB

- 文档页数:1

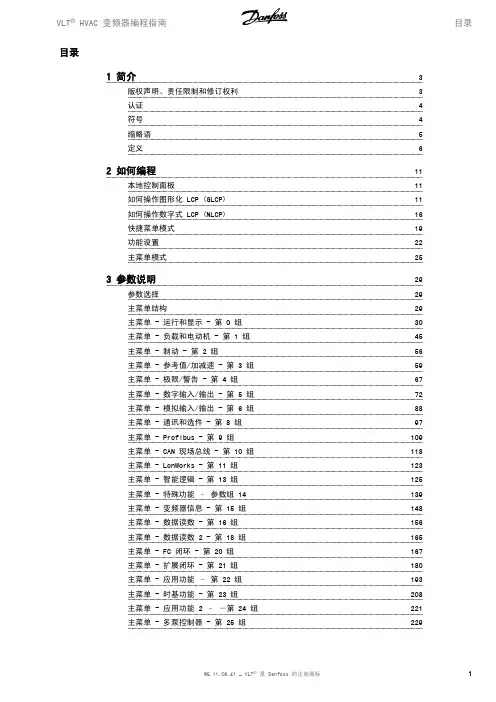

目录1 简介3版权声明、责任限制和修订权利3认证4符号4缩略语5定义62 如何编程11本地控制面板11如何操作图形化 LCP (GLCP)11如何操作数字式 LCP (NLCP)16快捷菜单模式19功能设置22主菜单模式253 参数说明29参数选择29主菜单结构29主菜单 - 运行和显示 - 第 0 组30主菜单 - 负载和电动机 - 第 1 组45主菜单 - 制动 - 第 2 组56主菜单 - 参考值/加减速 - 第 3 组59主菜单 - 极限/警告 - 第 4 组67主菜单 - 数字输入/输出 - 第 5 组72主菜单 - 模拟输入/输出 - 第 6 组88主菜单 - 通讯和选件 - 第 8 组97主菜单 - Profibus - 第 9 组109主菜单 - CAN 现场总线 - 第 10 组118主菜单 - LonWorks - 第 11 组123主菜单 - 智能逻辑 - 第 13 组125主菜单 - 特殊功能 – 参数组 14139主菜单 - 变频器信息 - 第 15 组148主菜单 - 数据读数 - 第 16 组156主菜单 - 数据读数 2 - 第 18 组165主菜单 - FC 闭环 - 第 20 组167主菜单 - 扩展闭环 - 第 21 组180主菜单 - 应用功能 – 第 22 组193主菜单 - 时基功能 - 第 23 组208主菜单 - 应用功能 2 – -第 24 组221主菜单 - 多泵控制器 - 第 25 组229主菜单 - 模拟 I/O 选件 MCB 109 - 第 26 组2414 疑难解答251报警字255警告字256扩展状态字257故障消息2585 参数列表263参数选项263默认设置263 0-** 操作/显示264 1-** 负载/电动机265 2-** 制动265 3-** 参考值/加减速266 4-** 极限/警告266 5-** 数字输入/输出267 6-** 模拟输入/输出268 8-** 通讯和选件269 9-** Profibus270 10-** CAN 现场总线270 11-** LonWorks271 13-** 智能逻辑控制器271 14-** 特殊功能272 15-** 变频器信息273 16-** 数据读数274 18-** 信息和读数275 20-** FC 闭环276 21-** 扩展 闭环277 22-** 应用功能278 23-** 基于时间的功能279 24-** 应用功能 2279 25-** 多泵控制器280 26-** 模拟输入输出选件 MCB 109281索引28211本指南适用于软件版本为 3.3.x 的所有 VLT HVAC Drive 变频器。

库卡机器人编程语法-概述说明以及解释1.引言1.1 概述概述库卡机器人编程语法是指在库卡机器人系统中使用的编程语言规则和规范。

库卡机器人是一种广泛应用于工业生产领域的工业机器人,它能够执行各种任务,并协助人类完成繁重、危险或重复性高的工作。

在库卡机器人编程语法中,我们需要了解语法结构、关键字、表达式和指令等方面的知识。

掌握这些知识有助于我们编写出高效、准确、安全的机器人程序,实现对机器人的精确控制。

库卡机器人编程语法具有以下几个特点:首先,它是一种结构化的编程语言,具有清晰的程序组织结构,便于代码的编写和维护;其次,它支持多种类型的数据和变量,如整数、浮点数、字符串等,以及各种运算符和逻辑操作符,使得程序设计更加灵活;再次,它提供了丰富的控制结构和函数库,能够满足不同的编程需求;最后,它还具备错误处理和调试机制,方便我们定位和修复程序中的错误。

库卡机器人编程语法的学习和掌握对于使用和开发库卡机器人系统至关重要。

正确地使用编程语法可以提高机器人系统的工作效率和准确性,减少人为错误的发生。

同时,熟练地掌握库卡机器人编程语法可以为后续的高级功能开发和应用打下基础,为机器人系统的进一步发展提供支持。

本篇文章将系统地介绍库卡机器人编程语法的要点和基本知识,并结合实际例子进行解读和应用。

通过对概述的研究和学习,读者可以对库卡机器人编程语法有一个全面而深入的了解,为后续的学习和应用打好基础。

1.2 文章结构文章结构部分的内容:在本文中,我们将以库卡机器人编程语法为主题,对其进行深入探讨和分析。

文章主要分为引言、正文和结论三部分。

引言部分首先概述了文章的主题,即库卡机器人编程语法,并简要介绍了本文的结构和目的。

正文部分将着重介绍库卡机器人编程语法的要点。

其中,2.1节将详细阐述库卡机器人编程语法的第一个要点,包括语法的基本概念、常用指令和编程规范等内容。

2.2节则将对库卡机器人编程语法的第二个要点进行探讨,探讨其在实际应用中的具体用法和注意事项。

PM0271编程手册STM32WB BLE协议栈编程指南引言本文档的主要目的是为开发人员提供有关如何使用STM32WB BLE协议栈API和相关事件回调开发低功耗蓝牙(BLE)应用的一些参考编程指南。

本文档介绍了允许访问STM32WB片上系统所提供的低功耗蓝牙功能的STM32WB低功耗蓝牙协议栈库框架、API接口和事件回调。

本编程手册还提供一些与低功耗蓝牙(BLE)技术有关的基本概念,以便将STM32WB BLE协议栈API、参数及相关事件回调与BLE协议栈特性联系起来。

用户必须具备有关BLE技术及其主要功能的基本知识。

有关STM32WB系列和低功耗蓝牙规范的更多信息,请参考本文档结尾处的第6节“参考文档”。

STM32WB是一种功率极低的低功耗蓝牙(BLE)单模网络处理器,符合蓝牙规范v5.3并支持主设备或从设备角色。

手册结构如下:• 低功耗蓝牙(BLE)技术的基本原理• STM32WB BLE协议栈库API和事件回调概述• 如何利用STM32WB库API和事件回调设计应用(使用“switch case”事件处理程序提供一些示例,而不使用事件回调框架)PM0271概述1 概述本文档适用于STM32WB系列基于双核Arm®的微控制器。

注意:Arm是Arm Limited(或其子公司)在美国和/或其他地区的注册商标。

2 低功耗蓝牙技术低功耗蓝牙(BLE)无线技术由蓝牙技术联盟(SIG)开发,目的是使设备能够以极低功耗标准使用纽扣电池工作数年。

传统蓝牙作为一种无线技术标准,可以取代连接便携式和/或固定式电子设备的线缆,但是由于采取了快速跳频、以连接为导向的行为方式和相对复杂的连接流程,无法采用电池供电的方式。

低功耗蓝牙设备的功耗仅为标准蓝牙产品的一小部分,让使用纽扣电池的设备能够无线连接到启用了标准蓝牙的设备。

图1. 支持低功耗蓝牙技术的以钮扣电池供电的设备低功耗蓝牙技术广泛应用于传输少量数据的传感器应用中:• 汽车• 运动与健身• 医疗• 娱乐• 家庭自动化• 安全和接近感测2.1BLE协议栈架构低功耗蓝牙技术已被蓝牙核心规范4.0正式采纳(参见第6节参考文件)。

sin x泰勒级数展开的python编程-概述说明以及解释1.引言1.1 概述概述:sin x是一种基本的三角函数,常用于描述周期性现象或波动振动问题。

在数学中,sin x可以通过泰勒级数来近似表示。

泰勒级数展开是将一个函数在某个点的附近进行多项式逼近的方法,可以将复杂的函数转化为简单的多项式来进行计算和分析。

本文旨在通过使用Python编程语言实现sin x的泰勒级数展开,来探讨其原理和应用。

文章将从sin x的定义与特性入手,介绍泰勒级数展开的原理,并详细解释如何使用Python编写程序来实现这一展开过程。

通过编程实例,读者将能够理解泰勒级数展开的计算方法和在Python中的具体实现步骤,同时也能加深对sin x函数的理解。

文章将以以下内容逐步展开:首先,在引言部分给出了本文的目的和整体结构;接下来,就sin x的定义和特性进行介绍,包括正弦函数的图像特点和基本性质;然后,将详细解释泰勒级数展开的原理,包括级数的推导和收敛条件;最后,通过使用Python编程语言来实现sin x的泰勒级数展开,并给出具体的代码实例和运行结果。

文章的结论部分将对实现结果进行总结和分析,探讨编程应用展望,并对整篇文章进行总结,并展望未来可能的扩展方向。

通过阅读本文,读者将能够深入了解sin x的泰勒级数展开,掌握使用Python编程来实现该展开的方法,同时也能够在实际应用中运用所学知识解决相关问题。

1.2文章结构文章结构部分的内容通常包括对整篇文章的组织和内容安排的介绍。

在这个部分,你可以描述每个章节的主要内容和目的,以及这些章节之间的逻辑关系。

下面是一个可能的编写方式:1.2 文章结构本文将主要围绕sin x的泰勒级数展开展开,通过Python编程实现该展开式的计算。

文章分为引言、正文和结论三个主要部分。

在引言部分,我们将给出这篇文章的概述,简要介绍sin x的定义和特性,以及本文的目的。

正文部分将具体讨论sin x的定义与特性(2.1小节),以及泰勒级数展开的原理(2.2小节)。

汇编多文件编程-概述说明以及解释1.引言1.1 概述汇编多文件编程是一种在汇编语言中使用多个文件来编写程序的技术。

在传统的汇编程序中,所有的代码都是写在一个文件中的,当程序变得庞大时,这会导致代码的可读性和可维护性变得非常困难。

汇编多文件编程通过将不同功能的代码分开存放在不同的文件中,使得程序结构更清晰,代码逻辑更容易理解。

通过合理地划分文件,我们可以将不同的功能模块独立编写,便于单独测试和调试,提高了代码的复用性和可扩展性。

在汇编多文件编程中,我们通常将主程序和不同的功能模块分别写在不同的文件中。

这些文件可以包含代码、数据和常量等信息。

通过在主程序中调用其他文件中的函数和变量,我们可以实现不同文件之间的交互和数据共享。

汇编多文件编程还可以提高代码的模块化程度,降低了编写和维护程序的难度。

它使得团队合作开发更加便捷,每个成员可以独立地编写和测试自己负责的部分,最后再进行整合。

总之,汇编多文件编程是一种有效的编程技术,它能够提高程序的可读性、可维护性和可扩展性。

通过合理地划分和组织代码,我们可以更好地编写和管理复杂的汇编程序。

在本文中,我们将介绍汇编语言的基础知识,以及如何使用多文件进行汇编编程的概念和方法。

1.2 文章结构文章结构部分的内容可以包括以下内容:文章结构部分旨在介绍本文的整体组织架构,用以引导读者了解本篇长文的内容安排和逻辑结构。

本文主要分为引言、正文和结论三个部分。

引言部分对本文的主题进行概述,并介绍文章的背景和意义。

通过简要介绍汇编多文件编程的概念和应用领域,引发读者对该主题的兴趣,并提出本文的目的和研究问题。

正文部分是本文的核心内容,主要分为两个小节:汇编语言基础和多文件编程概念。

在汇编语言基础部分,将介绍汇编语言的定义、特点和基本语法,为读者建立起对汇编语言的基本认识。

在多文件编程概念部分,将详细探讨多文件编程的原理和应用,包括多文件编程的优势、实现方法和注意事项,以及多文件编程在实际项目开发中的应用案例。

Intel® 64 and IA-32 ArchitecturesSoftware Developer’s ManualVolume 3 (3A, 3B, 3C & 3D):System Programming GuideNOTE: The Intel 64 and IA-32 Architectures Software Developer's Manual consists of four volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A-Z, Order Number 325383; System Programming Guide, Order Number 325384; Model-Specific Registers, Order Number 335592. Refer to all four volumes when evaluating your design needs.Order Number: 325384-065USDecember 2017Intel technologies features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at , or from the OEM or retailer.No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifica-tions. Current characterized errata are available on request.This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmapsCopies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting /design/literature.htm.Intel, the Intel logo, Intel Atom, Intel Core, Intel SpeedStep, MMX, Pentium, VTune, and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.*Other names and brands may be claimed as the property of others.Copyright © 1997-2017, Intel Corporation. All Rights Reserved.CONTENTSPAGECHAPTER 1ABOUT THIS MANUAL1.1INTEL® 64 AND IA-32 PROCESSORS COVERED IN THIS MANUAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1 1.2OVERVIEW OF THE SYSTEM PROGRAMMING GUIDE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4 1.3NOTATIONAL CONVENTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6 1.3.1Bit and Byte Order. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6 1.3.2Reserved Bits and Software Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7 1.3.3Instruction Operands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8 1.3.4Hexadecimal and Binary Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8 1.3.5Segmented Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8 1.3.6Syntax for CPUID, CR, and MSR Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9 1.3.7Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9 1.4RELATED LITERATURE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10CHAPTER 2SYSTEM ARCHITECTURE OVERVIEW2.1OVERVIEW OF THE SYSTEM-LEVEL ARCHITECTURE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1 2.1.1Global and Local Descriptor Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3 2.1.1.1Global and Local Descriptor Tables in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.1.2System Segments, Segment Descriptors, and Gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.1.2.1Gates in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.1.3Task-State Segments and Task Gates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.3.1Task-State Segments in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.4Interrupt and Exception Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.4.1Interrupt and Exception Handling IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.5Memory Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.1.5.1Memory Management in IA-32e Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.1.6System Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.1.6.1System Registers in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.1.7Other System Resources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.2MODES OF OPERATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.2.1Extended Feature Enable Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9 2.3SYSTEM FLAGS AND FIELDS IN THE EFLAGS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9 2.3.1System Flags and Fields in IA-32e Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11 2.4MEMORY-MANAGEMENT REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11 2.4.1Global Descriptor Table Register (GDTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12 2.4.2Local Descriptor Table Register (LDTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12 2.4.3IDTR Interrupt Descriptor Table Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12 2.4.4Task Register (TR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13 2.5CONTROL REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13 2.5.1CPUID Qualification of Control Register Flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-19 2.6EXTENDED CONTROL REGISTERS (INCLUDING XCR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19 2.7PROTECTION KEY RIGHTS REGISTER (PKRU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21 2.8SYSTEM INSTRUCTION SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21 2.8.1Loading and Storing System Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-23 2.8.2Verifying of Access Privileges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-23 2.8.3Loading and Storing Debug Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-24 2.8.4Invalidating Caches and TLBs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-24 2.8.5Controlling the Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-25 2.8.6Reading Performance-Monitoring and Time-Stamp Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-25 2.8.6.1Reading Counters in 64-Bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26 2.8.7Reading and Writing Model-Specific Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26 2.8.7.1Reading and Writing Model-Specific Registers in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26 2.8.8Enabling Processor Extended States. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26Vol. 3A iiiCONTENTSiv Vol. 3A PAGECHAPTER 3PROTECTED-MODE MEMORY MANAGEMENT3.1MEMORY MANAGEMENT OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1 3.2USING SEGMENTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2 3.2.1Basic Flat Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3 3.2.2Protected Flat Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3 3.2.3Multi-Segment Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4 3.2.4Segmentation in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5 3.2.5Paging and Segmentation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5 3.3PHYSICAL ADDRESS SPACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6 3.3.1Intel® 64 Processors and Physical Address Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6 3.4LOGICAL AND LINEAR ADDRESSES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6 3.4.1Logical Address Translation in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7 3.4.2Segment Selectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7 3.4.3Segment Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8 3.4.4Segment Loading Instructions in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9 3.4.5Segment Descriptors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9 3.4.5.1Code- and Data-Segment Descriptor Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12 3.5SYSTEM DESCRIPTOR TYPES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13 3.5.1Segment Descriptor Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-14 3.5.2Segment Descriptor Tables in IA-32e Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-16CHAPTER 4PAGING4.1PAGING MODES AND CONTROL BITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1 4.1.1Three Paging Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1 4.1.2Paging-Mode Enabling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3 4.1.3Paging-Mode Modifiers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4 4.1.4Enumeration of Paging Features by CPUID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5 4.2HIERARCHICAL PAGING STRUCTURES: AN OVERVIEW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6 4.332-BIT PAGING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7 4.4PAE PAGING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13 4.4.1PDPTE Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-13 4.4.2Linear-Address Translation with PAE Paging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-14 4.54-LEVEL PAGING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19 4.6ACCESS RIGHTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28 4.6.1Determination of Access Rights . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-29 4.6.2Protection Keys . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-31 4.7PAGE-FAULT EXCEPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-31 4.8ACCESSED AND DIRTY FLAGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-33 4.9PAGING AND MEMORY TYPING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-34 4.9.1Paging and Memory Typing When the PAT is Not Supported (Pentium Pro and Pentium II Processors). . . . . . . . . . . . . .4-34 4.9.2Paging and Memory Typing When the PAT is Supported (Pentium III and More Recent Processor Families). . . . . . . . . .4-34 4.9.3Caching Paging-Related Information about Memory Typing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-35 4.10CACHING TRANSLATION INFORMATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-35 4.10.1Process-Context Identifiers (PCIDs). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-35 4.10.2Translation Lookaside Buffers (TLBs). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-36 4.10.2.1Page Numbers, Page Frames, and Page Offsets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-36 4.10.2.2Caching Translations in TLBs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-37 4.10.2.3Details of TLB Use. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-37 4.10.2.4Global Pages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-38 4.10.3Paging-Structure Caches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-38 4.10.3.1Caches for Paging Structures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-38 4.10.3.2Using the Paging-Structure Caches to Translate Linear Addresses. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-40 4.10.3.3Multiple Cached Entries for a Single Paging-Structure Entry. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41 4.10.4Invalidation of TLBs and Paging-Structure Caches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41 4.10.4.1Operations that Invalidate TLBs and Paging-Structure Caches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41 4.10.4.2Recommended Invalidation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-43 4.10.4.3Optional Invalidation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-44 4.10.4.4Delayed Invalidation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-45 4.10.5Propagation of Paging-Structure Changes to Multiple Processors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-46 4.11INTERACTIONS WITH VIRTUAL-MACHINE EXTENSIONS (VMX). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-47 4.11.1VMX Transitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-47CONTENTSPAGE 4.11.2VMX Support for Address Translation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-474.12USING PAGING FOR VIRTUAL MEMORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-47 4.13MAPPING SEGMENTS TO PAGES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-48CHAPTER 5PROTECTION5.1ENABLING AND DISABLING SEGMENT AND PAGE PROTECTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1 5.2FIELDS AND FLAGS USED FOR SEGMENT-LEVEL ANDPAGE-LEVEL PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2 5.2.1Code-Segment Descriptor in 64-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3 5.3LIMIT CHECKING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4 5.3.1Limit Checking in 64-bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5 5.4TYPE CHECKING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5 5.4.1Null Segment Selector Checking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6 5.4.1.1NULL Segment Checking in 64-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6 5.5PRIVILEGE LEVELS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6 5.6PRIVILEGE LEVEL CHECKING WHEN ACCESSING DATA SEGMENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8 5.6.1Accessing Data in Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9 5.7PRIVILEGE LEVEL CHECKING WHEN LOADING THE SS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10 5.8PRIVILEGE LEVEL CHECKING WHEN TRANSFERRING PROGRAM CONTROL BETWEEN CODE SEGMENTS . . . . . . . . . . . . . . . . 5-10 5.8.1Direct Calls or Jumps to Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10 5.8.1.1Accessing Nonconforming Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11 5.8.1.2Accessing Conforming Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12 5.8.2Gate Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13 5.8.3Call Gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13 5.8.3.1IA-32e Mode Call Gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14 5.8.4Accessing a Code Segment Through a Call Gate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15 5.8.5Stack Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17 5.8.5.1Stack Switching in 64-bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19 5.8.6Returning from a Called Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20 5.8.7Performing Fast Calls to System Procedures with theSYSENTER and SYSEXIT Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20 5.8.7.1SYSENTER and SYSEXIT Instructions in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21 5.8.8Fast System Calls in 64-Bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22 5.9PRIVILEGED INSTRUCTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23 5.10POINTER VALIDATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24 5.10.1Checking Access Rights (LAR Instruction) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24 5.10.2Checking Read/Write Rights (VERR and VERW Instructions). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25 5.10.3Checking That the Pointer Offset Is Within Limits (LSL Instruction). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25 5.10.4Checking Caller Access Privileges (ARPL Instruction). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26 5.10.5Checking Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27 5.11PAGE-LEVEL PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27 5.11.1Page-Protection Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.2Restricting Addressable Domain. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.3Page Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.4Combining Protection of Both Levels of Page Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.5Overrides to Page Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29 5.12COMBINING PAGE AND SEGMENT PROTECTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29 5.13PAGE-LEVEL PROTECTION AND EXECUTE-DISABLE BIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30 5.13.1Detecting and Enabling the Execute-Disable Capability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30 5.13.2Execute-Disable Page Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30 5.13.3Reserved Bit Checking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31 5.13.4Exception Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32CHAPTER 6INTERRUPT AND EXCEPTION HANDLING6.1INTERRUPT AND EXCEPTION OVERVIEW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1 6.2EXCEPTION AND INTERRUPT VECTORS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1 6.3SOURCES OF INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2 6.3.1External Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2 6.3.2Maskable Hardware Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3 6.3.3Software-Generated Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4Vol. 3A v。

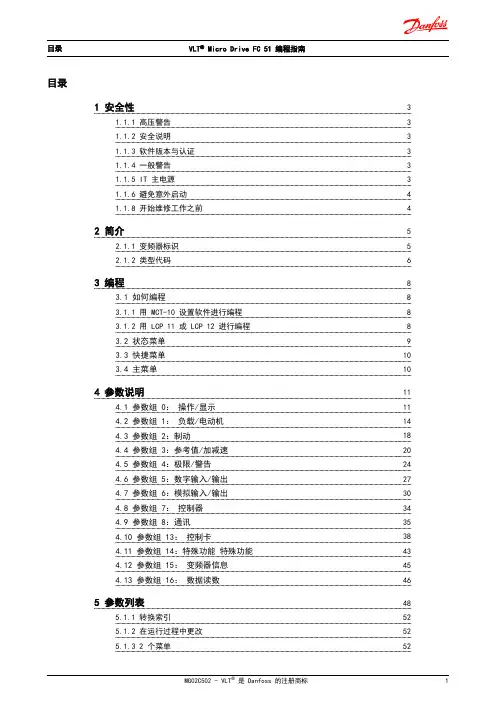

目录1 安全性31.1.1 高压警告31.1.2 安全说明31.1.3 软件版本与认证31.1.4 一般警告31.1.5 IT 主电源31.1.6 避免意外启动41.1.8 开始维修工作之前42 简介52.1.1 变频器标识52.1.2 类型代码63 编程83.1 如何编程83.1.1 用 MCT-10 设置软件进行编程83.1.2 用 LCP 11 或 LCP 12 进行编程83.2 状态菜单93.3 快捷菜单103.4 主菜单104 参数说明114.1 参数组 0: 操作/显示114.2 参数组 1: 负载/电动机144.3 参数组 2:制动184.4 参数组 3:参考值/加减速204.5 参数组 4:极限/警告244.6 参数组 5:数字输入/输出274.7 参数组 6:模拟输入/输出304.8 参数组 7: 控制器344.9 参数组 8:通讯354.10 参数组 13: 控制卡384.11 参数组 14:特殊功能 特殊功能434.12 参数组 15: 变频器信息454.13 参数组 16: 数据读数465 参数列表485.1.1 转换索引525.1.2 在运行过程中更改525.1.3 2 个菜单525.1.4 类型525.1.5 0-** 操作/显示535.1.6 1-** 负载/电动机535.1.7 2-** 制动535.1.8 3-** 参考值/加减速545.1.9 4-** 极限/警告545.1.10 5-** 数字输入/输出545.1.11 6-** 模拟输入/输出555.1.12 7-** 控制器555.1.13 8-** 通讯和选件555.1.14 13-** Smart Logic565.1.15 14-** 特殊功能565.1.16 15-** 变频器信息565.1.17 16-** 数据读数576 故障排查586.1.1 报警字、警告字和扩展状态字60索引631安全性1.1.1高压警告只要变频器 与主电源相连,它便带有危险电压。

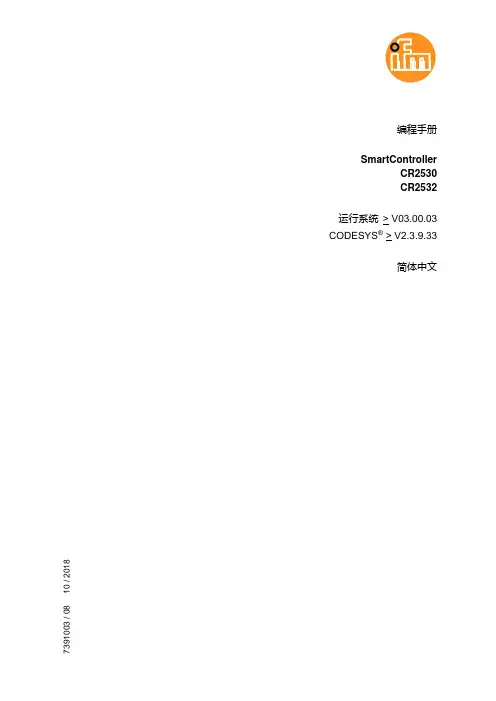

7391003 / 08 10 / 2018内容1关于本手册51.1版权 (5)1.2概述:ecomatmobile 装置文档模块 (6)1.3符号和格式是什么意思? (7)1.4本文档的结构是怎样的? (8)1.5说明沿革(CR253n) (10)2安全说明112.1请注意! (11)2.2需要预先具备哪些知识? (12)2.3控制器的启动运行状况 (12)2.4注意事项:序列号 (12)3系统描述133.1关于装置的信息 (13)3.2硬件说明 (14)3.2.1硬件结构 (14)3.2.2输入端(技术) (17)3.2.3输出端(技术) (23)3.2.4关于配线的注意事项 (30)3.2.5关于簧片继电器的安全说明 (30)3.2.6状态LED (31)3.3接口说明 (32)3.3.1CAN 接口 (33)3.4软件说明 (34)3.4.1装置的软件模块 (35)3.4.2CODESYS 项目的编程说明 (37)3.4.3工作状态 (41)3.4.4装置的性能极限 (44)4配置474.1设定运行时系统 (48)4.1.1重新安装运行时系统 (48)4.1.2更新运行时系统 (50)4.1.3检验安装 (50)24.2设定编程系统 (51)4.2.1手动设定编程系统 (51)4.2.2通过模板设定编程系统 (55)4.3一般功能配置 (55)4.3.1系统变量 (55)4.4输入端和输出端功能配置 (56)4.4.1配置输入端和输出端(默认设定) (56)4.4.2配置输入端 (57)4.4.3配置输出端 (62)4.5变量 (67)4.5.1保留变量 (67)4.5.2网络变量 (68)5IFM 功能元件695.1针对装置CR2530 的IFM 库 (69)5.1.1库ifm_CR2530_V03yyzz.LIB (70)5.1.2库ifm_RAWCan_NT_Vxxyyzz.LIB (71)5.1.3库ifm_CANopen_NT_Vxxyyzz.LIB (72)5.1.4库ifm_J1939_NT_Vxxyyzz.LIB (73)5.2针对装置CR2530 的IFM 功能元件 (75)5.2.1输出端功能元件 (75)5.2.2功能元件:RAW-CAN(第2 层) (77)5.2.3功能元件:CANopen (115)5.2.4功能元件:SAE J1939 (172)5.2.5功能元件:处理输入值 (216)5.2.6功能元件:输出端功能 (229)5.2.7功能元件:系统 (238)6诊断和错误处理2656.1诊断 (265)6.2故障 (265)6.3响应系统错误 (266)6.3.1响应错误消息的进程示例 (266)6.4CAN / CANopen: 错误和错误处理 (266)7附录2677.1系统标志 (268)7.2地址分配和I/O 工作模式 (269)7.2.1I/O 地址/变量 (269)7.2.2可能的输入端/输出端工作模式 (272)37.3集成I/O 模块:说明 (276)7.3.1系统说明I/O 模块ExB01 (276)7.3.2I/O 模块的配置 (291)7.3.3集成I/O 模块的对象目录 (305)7.3.4I/O 模块的运行 (346)7.3.5针对集成ExB01 I/O 模块的系统标志 (349)7.3.6I/O 模块错误消息 (350)7.4错误表 (353)7.4.1错误标志 (353)7.4.2错误:CAN / CANopen (353)8专业术语355 9指数37241 关于本手册内容版权 (5)概述:ecomatmobile 装置文档模块 (6)符号和格式是什么意思? (7)本文档的结构是怎样的? (8)说明沿革(CR253n) (10)2021.1 版权46224 © ifm electronic gmbh保留所有权利。

UIS8910DM Programming Guide声明Statement本文件所含数据和信息都属于紫光展锐所有的机密信息,紫光展锐保留所有相关权利。

本文件仅为信息参考之目的提供,不包含任何明示或默示的知识产权许可,也不表示有任何明示或默示的保证,包括但不限于满足任何特殊目的、不侵权或性能。

当您接受这份文件时,即表示您同意本文件中内容和信息属于紫光展锐机密信息,且同意在未获得紫光展锐书面同意前,不使用或复制本文件的整体或部分,也不向任何其他方披露本文件内容。

紫光展锐有权在未经事先通知的情况下,在任何时候对本文件做任何修改。

紫光展锐对本文件所含数据和信息不做任何保证,在任何情况下,紫光展锐均不负责任何与本文件相关的直接或间接的、任何伤害或损失。

All data and information contained in or disclosed by this document is confidential and proprietary information of UNISOC and all rights therein are expressly reserved. This document is provided for reference purpose, no license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document, and no express and implied warranties, including butwithout limitation, the implied warranties of fitness for any particular purpose, and non-infringement, as well as any performance. By accepting thismaterial, the recipient agrees that the material and the information contained therein is to be held in confidence and in trust and will not be used, copied, reproduced in whole or in part, nor its contents revealed in any manner to others without the express written permission of UNISOC. UNISOC may make any changes at any time without prior notice. Although every reasonable effort is made to present current and accurate information, UNISOC makes no guarantees of any kind with respect to the matters addressed in this document. In no event shall UNISOC be responsible or liable, directly or indirectly, for any damage or loss caused or alleged to be caused by or in connection with the use of or reliance on any such content.CONTENTS: 1Getting Start11.1Overview (1)1.2Linux Build (2)1.3Windows Build (3)1.4Kconfig (4)1.5menuconfig (4)1.6guiconfig (5)2Architecture72.1Overview (7)2.2Bootloader (10)2.3HAL(Hardware Abstract Layer) (11)2.4OSI(OS Interface) (11)2.5libc (11)2.6Driver (11)2.7File System (12)2.8IPC/RPC (12)2.9CFW(Communication FrameWork) (12)2.10PS Interface (12)2.11TCP/IP (12)2.12COAP/LWM2M/ (12)2.13AT Receiver (12)2.14Open CPU (13)3Flash Layout153.1Overview (15)3.2Bootloader (16)3.3Application (16)3.4System FS (17)3.5Modem FS (17)3.6Factory FS (17)3.7Configurations (17)3.8Frequently Overwrite Small File (18)4Kernel(OS Interface)19i4.1Overview (20)4.2Thread (20)4.3osiEvent_t (20)4.4Thread Callback (21)4.5Thread Notify (22)4.6Semaphore (22)4.7Mutex (22)4.8Work and Work Queue (22)4.9Interrupt Latency (23)4.10ISR Programming (23)4.11Timer (24)4.12Elapsed Timer (26)4.13Power management (26)4.14Cache (28)4.15atomic (28)4.16Floating Point (28)4.17FreeRTOS Integration (29)4.18API Reference (30)5OSI Libraries735.1Overview (73)5.2Event Hub and Event Dispatch (73)5.3FIFO (74)5.4Value String Map (74)5.5Memory Recycler (74)5.6Generic List (76)5.7Event Hub and Dispatch API Reference (76)5.8FIFO API Reference (80)5.9Value String Map API Reference (83)5.10Memory Recycler API Reference (89)5.11Generic List API Reference (91)6C++Language936.1Compiling Options (93)6.2Global Object (93)6.3Static Object (94)7Clock Management957.1clk_sys Callback (96)7.2Fix clk_sys Constrain (96)7.3Hardware Minimal Clock Constrain (96)7.4Software Minimal Clock Constrain (96)7.5Hardware External RAM Access Constrain (97)7.6Hardware Clock Constrain and PM Source (97)7.7Reapply Constrains (97)7.8Thread Safe (98)7.9API Reference (98)8Memory Management103 ii8.1Overview (103)8.2Pool Type (104)8.3Reference Count (104)8.4Pattern Check (104)8.5Alignment (104)8.6Thread Safe and ISR (105)8.7Limitation (105)8.8API Reference (105)9Trace1139.1Overview (113)9.2Format String (113)9.3Trace Level (114)9.4Trace Tag (114)9.5Trace ID (115)9.6Basic and Extended (115)9.7API Reference (116)10SFFS(Small Flash File System)11910.1Overview (119)10.2Flash Block Device (120)10.3SFFS Blocks (121)10.4Power Failure Safe (121)10.5vfs_sfile_write (121)10.6Quick Format (122)10.7Memory Usage (122)10.8EBUSY (122)10.9Flash Block Device API Reference (123)10.10SFFS VFS API Reference (125)10.11SFFS API Reference (126)11CFW Event Dispatch13711.1Overview (137)11.2UTI Management (140)11.3Thread Safe (140)11.4API Reference (140)12IPC(Inter-Processor Communication)14312.1Overview (143)12.2Shared Registers (144)12.3Shared Memory Layout (144)12.4Thread Safe (145)12.5API Reference (145)13PS IPC Interface15313.1Overview (153)13.2Thread Safe (153)13.3API Reference (153)iii14RPC(Remote Procedure Call)15714.1Overview (158)14.2Function Call (160)14.3Event (160)14.4Code Generation (161)14.5XML by Example (162)14.6Event Router (166)14.7Dead Lock (166)14.8Command Queue (166)14.9API Reference (166)15AT Receiver Engine17315.1Overview (173)15.2AT Engine Process Flow (174)15.3AT Settings (176)15.4AT Command Line Parsing (176)15.5AT Command Parameter (177)15.6AT Response (177)15.7Add an AT command (178)15.8AT Command Asynchronous Context (179)15.9AT and SIM (179)15.10Speech Call (179)15.11Memory Free Later (180)15.12AT Engine API Reference (180)15.13AT Parameter API Reference (200)15.14AT Response API Reference (212)16Firmware Update21916.1Firmware Update in Application (219)16.2Firmware Update in Bootloader (220)16.3FUPDATE_RESULT_CANNT_START (220)16.4Files for Firmware Update (220)16.5API Reference (221)17IOMUX22717.1Overview (227)17.2API Reference (228)18Hardware Spinlock22918.1Overview (229)18.2API Reference (229)19GPIO23119.1Overview (231)19.2API Reference (231)20ADI bus for PMIC23520.1Overview (235)20.2API Reference (235)iv21PMIC Interrupt23721.1Overview (237)21.2API Reference (237)22SPI Flash24122.1Overview (241)22.2API Reference (241)23RTC and Alarm24723.1Overview (247)23.2API Reference (247)24Uart Driver25324.1Overview (253)24.2API Reference (253)25Axidma Driver26125.1Overview (261)25.2API Reference (261)26PMIC ADC26526.1Overview (265)26.2API Reference (265)27I2c Driver26927.1Overview (269)27.2API Reference (269)28IFC27328.1Overview (273)28.2Auto Mode (274)28.3Interrupt (274)28.4Channels (274)28.5Cache Coherence (275)28.6Thread Safe (275)28.7API Reference (275)29PPP Guides27929.1Linux (279)29.2Windows (281)30Coding Style Guide28330.1Copyright Header (284)30.2Indent (284)30.3Line Length (284)30.4File Name Convention (284)30.5Function Name Convention (284)30.6Static Functions (285)30.7Local Variable Name Convention (285)30.8Global Variable Name Convention (285)v30.9Struct Name Convention (285)30.10enum (286)30.11C++Class,Method and Member Name (286)30.12stdint,stdbool (287)30.13const,void* (287)30.14Object Oriented (287)30.15extern (287)30.16Global Variables (288)30.17Public Header (288)30.18extern“C” (288)30.19Parameter Checking (288)30.20Return bool or int (289)30.21Warning (289)31Indices and tables291 Index293viCHAPTERONEGETTING STARTContents•Overview•Linux Build–System Requirement–Build–CMake Options–Directory Convention•Windows Build–System Requirement–Build Under cmd.exe–Build Under msys2/MINGW/Cygwin/Cygwin64•Kconfig•menuconfig•guiconfig1.1OverviewThis SDK can be built on Windows and Linux.Most of the tools used during building the SDK are included in the SDK,including both Linux version and Windows ly:•GCC•cmake•ninja•nanopb1Programming Guide Documentation•Python3(Linux build will use the system version)•gperf1.2Linux Build1.2.1System RequirementOnly Ubuntu16.04is supported.The following packages are needed:$sudo apt install build-essential python3python3-tk qtbase5-dev1.2.2Build$.tools/launch.sh#select target by numerical index$cout$cmake../..-G Ninja$ninja.tools/launch.sh It will set PATH and several environment variables.Also,it can be called as.tools/ launch.sh<target_name><debug|release>for non-interactive mode.Non-interactive mode is useful in building script.cmake../..-G Ninja This SDK uses CMake as the building system.This step will generate ninja build file.Though CMake can support various generators.Only ninja is support in this SDK.It is only needed to run this step once.Afterward,when there are changes in source codes,CMakeLists.txt, Kconfig or target.config,ninja will invoke re-configuration automatically.ninja This command will build the selected target.In multi-processor system,Ninja will use available CPUs for parallel build.It is not needed to specify parallel job count.ninja clean CMake and ninja can handle dependency very well.In most cases,incremental build is enough.In case to clean build results for a clean build,ninja clean can be called.ninja unittests This SDK supports unit test framework.By default,unit tests are not built.If needed, ninja unittests can be called to build all unit testscout A function defined at.tools/launch.It will create target output directory,if not existed,and change directory to it.croot A function defined at.tools/launch.It will change directory to the root of project.2Chapter1.Getting StartProgramming Guide Documentation 1.2.3CMake OptionsThe supported CMake command line options:-DWITH_WERROR=on Waning is bad.However,-Werror makes development inconvenient.So,-Werror compile option isn’t added at build.When-DWITH_WERROR=on is added in the cmake command line, -Werror compile option will be added.It is recommended to add this option is CI,to make sure all warnings are solved.-DBUILR_REVISION=<revision_name>It defines a string of revision ually,it will be defined as the tag name.When not specified,the name is DEVEL.1.2.4Directory Convention<project_root>/out/<target_name>-<debug|release>Output directory of target.Out-of-source build is followed.That is,during build,there are no any build result will be generated in the source tree.All build result including intermediate build result will be created under the output directory. <project_root>/out/<target_name>-<debug|release>/lib Directory for libraries.<project_root>/out/<target_name>-<debug|release>/hex Directory for elf,map,bin and imagefiles.<project_root>/out/<target_name>-<debug|release>/include Directory for generated headerfiles.<project_root>/out/<target_name>-<debug|release>/rpcgen Sourcefiles generated by rpcgen.py.1.3Windows Build1.3.1System RequirementSupported Windows versions:•Windows7SP1,x64•Windows10,x64•Visual C++Redistributable for Visual Studio2015x86•Visual C++Redistributable for Visual Studio2015x641.3.2Build Under cmd.exe>call tools\l aunch.bat<target_name><debug|release>>cd out\t arget_name>>cmake..\..-G Ninja>ninja1.3.Windows Build3Programming Guide DocumentationIt is very similar to Linux build.tools\launch.bat doesn’t support interactive mode.The<target_name> is necessary,and<debug|release>is optional.When not specified,debug will be used.cmd.exe doesn’t support function as bash.So,cout and croot can’t be used.1.3.3Build Under msys2/MINGW/Cygwin/Cygwin64mintty and bash coming with msys2/MINGW/Cygwin/Cygwin64is more convenient than cmd.exe for inter-active.However,nothing from msys2/MINGW/Cygwin/Cygwin64will be used for building.$.tools/launch.sh#select target by numerical index$cout$cmake../..-G Ninja$ninjaIt is very similar to Linux build.After.tools/launch.sh is called,prebuilts/win32/python3will be added to the beginning of PATH.This python3is Windows native Python3.It it possible that it will affect msys2/Cygwin/Cygwin64 system.1.4KconfigKconfig is used as configuration system.For each target,target/<target_name>/target.config keeps the target configuration.At build,out/ <target_name>-<debug|release>/target.cmake will be generated,and the configurations will be used by CMake.Contrary to Linux build,there are no config.h will be generated.Rather,each module should use CMake configuration_file command to generate headerfile from a template.1.5menuconfigmconf under Linux source tree is great,but can’t run on Windows.Kconfiglib is used.Python script menuconfig can work well on Linux,and Windows cmd.exe.However,it can’t work well under mintty of msys2/Cygwin/Cygwin64.On Linux:$cd<project_root>#assume".tools/launch.sh"is already executed.$menuconfig.pyOn Windows msys2/Cygwin/Cygwin64:$cd<project_root>#assume".tools/launch.sh"is already executed.$tools/menuconfig.bat4Chapter1.Getting StartProgramming Guide DocumentationOn Windows cmd.exe:>cd<project_root>#assume"call tools\launch.bat<target_name>"is already˓→executed.>tools\m enuconfig.batDuring.tools/launch.sh or call tools\launch.bat,KCONFIG_CONFIG will be set to target/<target_name>/target.config.minconfig.py will strip down all default configurations,and only contain configuration value not equal to default value.The strip down version is suitable to keep in revision control.1.6guiconfigguiconfig is a Python script from Kconfiglib.On Linux/msys2/Cygwin/Cygwin64:$cd<project_root>#assume".tools/launch.sh"is already executed.$guiconfig.pyOn Windows cmd.exe:>cd<project_root>#assume"call tools\launch.bat<target_name>"is already˓→executed.>python3tools\g uiconfig.py1.6.guiconfig5Programming Guide Documentation6Chapter1.Getting StartCHAPTERTWOARCHITECTUREContents•Overview•Bootloader•HAL(Hardware Abstract Layer)•OSI(OS Interface)•libc•Driver•File System•IPC/RPC•CFW(Communication FrameWork)•PS Interface•TCP/IP•COAP/LWM2M/...•AT Receiver•Open CPU2.1OverviewThis SDK architecture can support various UNISOC IoT platforms.Currently,the followings are supported:•8955:2G•8908:NB IoT•8909:NB IoT/2G7Programming Guide Documentation•8915:LTE Cat1/2G,eMTC/2GThere are separated AP and CP in8915,and the architecture of the SDK for8915is:There is only one CPU for both application can stack in8955/8908/8909,and the architecture of the SDK for 8955/8908/8909is:8Chapter2.ArchitectureProgramming Guide DocumentationThough FreeRTOS is used in this SDK,there is OSI(OS Interface)layer to isolate RTOS and application.So,3rd party RTOS can be easily port to the SDK,and replace FreeRTOS.Also,3rd cloud SDK based on3rd party RTOS can run natively without porting.2.1.Overview9Programming Guide Documentation2.2BootloaderBootloader is the software entrance after system jump out of ROM.The main features of bootloader: Differential UpgradeThis SDK is target to platforms using NORflash,and most of the code are running on NORflash directly(XIP, eXecute In Place).And there is only one copy of codes on NORflash.So,at upgrade,it is needed to be done in bootloader.File system will be used for upgrade,for storing upgrade package.So,bootloader shall supportfile system.And thefile system layout in bootloader should be exactly the same with thefile system layout in application.UART/USB UpgradeIf enabled,bootloader will monitor UART/USB input for upgrade.The use case is an upgrade tool will running on PC.When the communication between PC upgrade tool and platform is established,PC upgrade tool can upgrade 10Chapter2.ArchitectureProgramming Guide Documentation thefirmware.Note:Not all platforms support USB upgrade.Application Signature VerificationWhen secure boot is enabled,ROM will verify the signature of bootloader.And bootloader shall verify the application signature.Note:Not all platforms support secure boot.Bootloader doesn’t support upgrade itself safely.Application doesn’t rely on any setting in bootloader,so in the life cycles,it doesn’t needed to upgrade bootloader.2.3HAL(Hardware Abstract Layer)HAL is platform deeply coupled layer.Examples:•System clock setting;•Memory setting;•Basic power setting;This layer can be shared with both bootloader and application.So,it can’t use RTOS features.Note:osiEnterCritical and osiExitCritical can be used in HAL.2.4OSI(OS Interface)Besides RTOS abstraction,OSI will provide other common system features.It is closer to programming environ-ment.2.5libcnewlib is used in this SDK.2.6DriverDrivers are various peripheral drivers.It is built on top of HAL and OSI.Full RTOS features can be used in drivers,including thread,semaphore,mutex,timer,work queue and etc.2.3.HAL(Hardware Abstract Layer)11Programming Guide Documentation2.7File SystemSFFS is afile system optimized for NORflash.All persistent information storage are usingfile system.Also,POSIXfile system APIs(such as open,read,write,and etc)are provided with prefix vfs_.2.8IPC/RPCFor platforms with separated AP and CP,IPC is the mechanism of AP/CP communication.RPC is a mechanism built on top of IPC.With RPC,any CPU can call APIs implemented in other CPUs.Though peer CPU API call is a serial of IPC communication,application can’t feel any differences with local API call. 2.9CFW(Communication FrameWork)CFW is a layer above protocol stack(2G,NB IoT,LTE Cat1,eMTC).On some platforms,CFW implementation may be located on other CPU.However,with the help of RPC,appli-cation is the same.Note:It is not supported to call CFW directly in customer development.2.10PS InterfacePS interface is a layer for PS data with protocol stack.The APIs is the same for platforms with protocol stack in the same CPU,and platforms with protocol stack in other CPU.2.11TCP/IPlwIP is used in this SDK to provide TCP/IP stack.2.12COAP/LWM2M/...There are many IoT IP based protocols in this SDK.Most of them are ported from open source projects.2.13AT ReceiverThis SDK provides AT receiver.AT commands can be received from UART,USB(CDC/ACM).12Chapter2.ArchitectureProgramming Guide Documentation 2.14Open CPUThis SDK provides open CPU features.Open CPU is an friendly development environment based on the base SDK.OSI,drivers and TCP/IP are well documented,and they can be used in development on top of the base SDK.Also, it supports:Dynamic LoaderAn easy-to-use dynamic loader mechanism is implemented in this SDK.The basic features:•Application can call exposed APIs in base SDK.•Base SDK and application can be upgraded independently.•Application can be loaded fromfiles onfile system,and can be loaded from NORflash directly.When loading from NORflash directly,application can run on NORflash directly.Some limitations:•Application can’t access global variables in base SDK directly.•Flash and RAM reserved for application shall be planned beforehand.AT Command by APIThere is a virtual AT channel in this SDK.With the virtual AT command channel,legacy application based on sending AT commands can be ported easily.RILDue to it is not supported to call CFW directly in customer development,RIL is provided.It is a bunch of simplified communication API.2.14.Open CPU13Programming Guide Documentation14Chapter2.ArchitectureCHAPTERTHREEFLASH LAYOUTContents•Overview•Bootloader•Application•System FS•Modem FS•Factory FS•Configurations•Frequently Overwrite Small File3.1OverviewThis IoT SDK is based on NORflash,and SFFS is thefile system for NVRAM,modem image and etc.Typicalflash layout for8MBflash:Partition Range Size Mount Pointbootloader0..0x1000064KBapplication0x10000..0x340000 3.2MBsystem FS0x340000..0x4a0000 1.4MB/modem FS0x4a0000..0x7e0000 3.2MB/modemfactory FS0x7e0000..0x800000128KB/factoryTypicalflash layout for16MBflash:15Programming Guide DocumentationPartition Range Size Mount Pointbootloader0..0x1000064KBapplication0x10000..0x9800009.6MBsystem FS0x980000..0xca0000 3.1MB/modem FS0xca0000..0xfe0000 3.2MB/modemfactory FS0xfe0000..0x1000000128KB/factoryThe size of each partition can be configured.However,it is not recommended to change the number and order of the partitions.The default layout leaves very large rooms for application,and the systemfile system is tight.When there are many customized data shall be stored,it can be considered to decrease application partition,and increase system file system partition.Whenfile system configurations(includingflash offset,size,erase block size and logic block size)are changed, the originalfiles onfile system will be destroyed.Though overhead offile system is highly optimized on SFFS,it should be considered atflash layout plan.3.2BootloaderAt boot,ROM will load bootloader to internal SRAM and execute on internal SRAM.ROM will only load size of0xbf40fromflash.When secure boot is enabled,the last0x260is used for signature.So,for one stage bootloader,the maximum code size is0xbce0.When0xbce0is not enough,two stage bootloader is needed.Also,when secure boot is needed,thefirst stage bootloader should verify the signature of second stage of bootloader.Currently,one stage bootloader is used. Feature list of bootloader:•Check application image,and jump to application;•When secure boot is enabled,verify application signature;•FOTA upgrade;Note:Due to ROM can support UART download,it is not needed to support download and/or upgrade in bootloader.3.3ApplicationApplication partition is not managed byfile system.It is for application,including SDK and customized applica-tion.And most of the application shall run onflash directly(XIP).16Chapter3.Flash LayoutProgramming Guide Documentation 3.4System FSThis is the partition for run time data,such as NVRAM,and managed byfile system.By default,it is mounted as read-write.Two directories are used by SDK:•/modemnvm(CONFIG_FS_MODEM_NVM_DIR)•/nvm(CONFIG_FS_AP_NVM_DIR)•/fota(CONFIG_FS_FOTA_DATA_DIR)FOTA upgrade data will be stored in this partition.So,it should ensure there are enough rooms for FOTA upgrade data.Also,this partition will be written frequently.For NORflashfile system,performance will downgrade whenfile system is close to full:•write will be much slower;•erase count will increase rapidly;Note:In case there are data will be stored frequently,flash life-cycle should be considered.Due to SFFS can handle wear-leveling well,the larger spare rooms infile system,the life-cycle offlash can be longer.FOTA data size is hard to estimate.Though FOTA data size can be very small when the code change is small, 10%of the original size is the minimum requirement.3.5Modem FSThis is the partition for modem image,and managed byfile system.By default,it is mounted as read-only to avoid overwrite accidentally.3.6Factory FSThis is the partition for factory data,such calibration data,IMEI,serial number and etc.,and managed byfile system.By default,it is mounted as read-only to avoid overwrite accidentally.3.7Configurations•CONFIG_BOOT_FLASH_OFFSET•CONFIG_BOOT_FLASH_SIZE•CONFIG_APP_FLASH_OFFSET3.4.System FS17Programming Guide Documentation•CONFIG_APP_FLASH_SIZE•CONFIG_FS_MODEM_MOUNT_POINT•CONFIG_FS_MODEM_FLASH_OFFSET•CONFIG_FS_MODEM_FLASH_SIZE•CONFIG_FS_MODEM_EB_SIZE•CONFIG_FS_MODEM_PB_SIZE•CONFIG_FS_SYS_MOUNT_POINT•CONFIG_FS_SYS_FLASH_OFFSET•CONFIG_FS_SYS_FLASH_SIZE•CONFIG_FS_SYS_EB_SIZE•CONFIG_FS_SYS_PB_SIZE•CONFIG_FS_FACTORY_MOUNT_POINT•CONFIG_FS_FACTORY_FLASH_OFFSET•CONFIG_FS_FACTORY_EB_SIZE•CONFIG_FS_FACTORY_PB_SIZE3.8Frequently Overwrite Small FileHere is an example of writing smallfile frequently.File system configuration:•flash size:1MB•erase block size:32KB•logical block size:512B•file size:200B•write every5minute,overwrite thefileAt worse case,thefile system is very close to full,each write will causeflash erase.And then there are105,120flash erase every year.At best case,thefile system is empty.Then,1950times offile write will cause oneflash erase of everyflash sectors.So,there are only54flash write every year.18Chapter3.Flash LayoutCHAPTERFOURKERNEL(OS INTERFACE)Contents•Overview•Thread•osiEvent_t•Thread Callback•Thread Notify•Semaphore•Mutex•Work and Work Queue•Interrupt Latency•ISR Programming•Timer–Timer and Sleep–Timer Stop Corner Case–Timer API inside Callback–Timer Pool•Elapsed Timer•Power management–PM Source–Wake Lock–Resume Order–Auto Sleep19Programming Guide Documentation–Callback Restriction•Cache•atomic•Floating Point•FreeRTOS Integration•API Reference4.1OverviewThis IoT SDK is based on RTOS.By design,SDK won’t access the used RTOS directly.Rather,OSI(OS Interface) layer is designed.SDK can only access OSI API.OSI can be implemented by various RTOS.Even the underlay RTOS is changed,the SDK itself can keep unchanged.OSI based on FreeRTOS is provided in the SDK.And it is possible and not hard to implement OSI based on other RTOS.4.2ThreadThread is the basic RTOS scheduling unit.Threads have independent stack.OSI thread has a bundled event queue.There are APIs to send event to thread.The basic model of OSI thread is event processing.An typical OSI thread is:void entry(void*argument){osiThread_t*thread=osiThreadCurrent();while(running){osiEvent_t event={};osiEventWait(thread,&event);_processEvent(&event);}osiThreadExit();}There no API to delete another thread.Rather,thread should be terminated by themselves,through some kinds of pre-defined inter-thread communication method.At the end of thread entry function,osiThreadExit() should be called.4.3osiEvent_tosiEvent_t is the data structure of OSI event:20Chapter4.Kernel(OS Interface)Programming Guide Documentation typedef struct osiEvent{uint32_t id;///<event identifieruint32_t param1;///<1st parameteruint32_t param2;///<2nd parameteruint32_t param3;///<3rd parameter}osiEvent_t;The message queue for OSI event is named as event queue.The most important inter-thread communication is to send and wait event.At send and wait event,the event body is copied.Three words are enough to carry event information in most cases.Then this design can reduce malloc and free function calls.The details of the event parameters are defined by each event.In case that three words are not enough,dynamic pointer can be carried as event parameter.The memory management convention is defined by each event.When dynamic memory is used,usually event sender allocate memory,event receiver free memory after process.4.4Thread CallbackThread callback is a callback to be executed inside specified thread.The implementation is based on OSI event. However,the codes will be more readable with osiThreadCallback,rather than huge switch/case of event IDs.With event ID,the codes will look like://senderosiEvent_t event={EVENT_ID,param1};osiEventSend(thread,&event);//receiverfor(;;){osiEvent_t event={};osiEventWait(thread,&event);switch(event.id){case EVENT_ID:function_call(event.param1);break;}}With thread call,the codes will look like:osiThreadCallback(thread,function_call,param1);4.4.Thread Callback21。

没问题!主题:gsk980tc3编程及操作说明一、gsk980tc3编程1.1 基本概念gsk980tc3编程是指利用gsk980tc3数控系统对机床进行指令控制和程序设计的过程。

在进行编程前,需要了解一些基本概念:- gsk980tc3数控系统:是一种用于机床自动化控制的系统,能够实现对机床运动轴、进给轴和其他辅助轴的控制。

- gsk980tc3编程语言:是一种专门用于gsk980tc3数控系统的编程语言,用于描述工件的加工轨迹和加工参数。

1.2 编程步骤进行gsk980tc3编程时,一般可以按照以下步骤进行:- 确定加工图形和加工工艺要求。

- 选用适当的编程方式和编程方法。

- 输入相关的几何参数和工艺参数。

- 进行程序编辑和调试。

- 运行程序,检验程序的正确性。

1.3 编程规范在进行gsk980tc3编程时,还需要遵守一些编程规范,以确保编写出高质量的程序:- 程序清晰、简洁、易懂。

- 避免出现语法错误和逻辑错误。

- 严格按照加工工艺要求和机床的运动特性进行编程。

二、gsk980tc3操作2.1 界面介绍gsk980tc3数控系统的操作界面通常包括以下几个部分:- 程序编辑区:用于显示当前的程序代码。

- 参数设置区:用于设置与机床加工相关的各项参数。

- 运动控制区:用于手动控制机床的各个轴进行运动。

2.2 操作方式进行gsk980tc3操作时,一般需要按照以下操作方式进行:- 打开系统电源,启动gsk980tc3数控系统。

- 进行程序选择或新建程序。

- 对加工参数进行设置。

- 进行手动操作或自动操作。

2.3 操作注意事项在操作gsk980tc3数控系统时,还需要注意以下几点:- 严格按照操作手册的要求进行操作。

- 注意机床运动轴和进给轴的安全范围。

- 对机床进行定期的维护和保养。

以上是关于gsk980tc3编程及操作的一些基本说明,希望能够对您有所帮助。

如果您在使用过程中遇到问题,可以随时通联我们的掌柜人员进行交流和解答。

gsoap编程-概述说明以及解释1.引言1.1 概述在编程领域中,gSOAP是一个常用的开源工具包,用于构建基于标准协议的Web服务。

通过gSOAP编程,开发人员可以轻松地创建和部署跨平台的Web服务,实现不同系统之间的通信和数据交换。

本文将深入探讨gSOAP编程的概念、优势以及基本原理,帮助读者了解如何利用这一强大工具进行Web服务开发。

无论是初学者还是有经验的开发人员,都可以通过学习gSOAP编程,提升自己在Web服务领域的技术水平,并加速项目的开发进程。

1.2 文章结构文章结构部分:本文主要分为引言、正文和结论三个部分。

在引言部分,将对gSOAP 编程进行概述,介绍文章的结构和目的。

正文部分将详细讨论什么是gSOAP编程、gSOAP编程的优势以及gSOAP编程的基本原理。

在结论部分,将对整篇文章进行总结,展望gSOAP编程的应用前景,并给出结束语。

通过这样的结构,读者可以系统地了解gSOAP编程的相关知识,从而更好地理解和应用该技术。

1.3 目的本文的目的在于介绍和探讨gSOAP编程的基本概念、优势以及基本原理。

通过深入了解gSOAP编程,读者可以更好地理解如何利用gSOAP 提高代码重用性、简化开发流程并实现跨平台的Web服务通信。

此外,本文也将展望gSOAP编程的未来发展趋势,为读者提供对这一技术领域的更深入了解和应用前景。

希望读者通过本文的阅读,能够更加全面地认识和理解gSOAP编程,并在实际项目中有效地运用这一技术,从而提高软件开发效率和质量。

2.正文2.1 什么是gSOAP编程gSOAP编程是一种用于开发网络通信和Web服务的工具集。

gSOAP 是一个开源的跨平台工具,可以帮助开发人员轻松地创建和部署基于SOAP和WSDL标准的Web服务。

它提供了一组工具和库,使开发人员能够在C和C++中快速地创建SOAP和RESTful风格的Web服务。

通过gSOAP编程,开发人员可以很容易地将现有的C和C++代码转换为Web服务,从而使其能够与其他系统进行通信。

SCPI协议N3410系列编程手册 (1)1.前言 (3)2.安全说明 (4)2.1.安全须知 (4)2.2.安全标识 (4)3.语法 (5)3.1.INST:NSEL (5)3.2.OUTP (5)3.3.VOLT (5)3.4.CURR (5)3.5.MEAS:VOLT (5)3.6.MEAS:CURR (5)3.7.VOLT?MAX (6)3.8.CURR?MAX (6)3.9.OUTP:PARA (6)3.10.OUTP:SERI (6)3.11.OUTP:TRAC (6)3.12.MEAS:VOLT:ALL (6)3.13.MEAS:CURR:ALL (7)4.编程实例 (7)4.1.将通道1开启恒压限流测试 (7)4.2.将通道1和通道2设置成并联模式并开启恒压限流测试 (7)4.3.回读所有通道电压或电流 (8)5.配置寄存器列表 (8)1.前言尊敬的用户:非常感谢您选择恩智(上海)测控技术有限公司(以下简称NGI)N3410系列三通道可编程直流电源(以下简称N3410)。

以下为您做相关介绍:关于公司本公司主要从事仪器仪表、电子产品、机械设备、自动测试系统、计算机软件、自动控制设备、自动监控报警系统的设计、安装、销售、维修,软件测试,从事货物及技术的进出口业务等。

恩智测控(NGI)为智能设备与测控仪器的专业制造商,始终秉持“以客户为中心,以奋斗者为本”的企业宗旨,致力于信息化制造、科学实验、教育科研等相关领域测控解决方案的研究与探索。

通过不断深入接触并了解各相关行业的测控与电子电路技术需求,持续投入研发并向各行业合作伙伴提供具有竞争力的解决方案,NGI已经拥有了广泛的测控和电子技术类产品线,合作伙伴遍布多个行业领域。

NGI持续的研发投入和对产业发展的追踪,寄望于为客户提供贴心的技术服务和应用体验,为智能制造业的发展做出应有的贡献。

十年来,NGI始终发扬“团结协作,勇攀高峰”的团队精神,不断推出尖端测控技术和产品,在多个领域保持技术领先地位。

GX_Developer_编程软件使用说明GX_Developer 编程软件使用说明GX_Developer 是三菱电机公司开发的一款用于三菱可编程控制器(PLC)编程的软件工具。

它具有强大的功能和友好的用户界面,能够帮助工程师高效地完成 PLC 程序的编写、调试和维护工作。

接下来,让我们详细了解一下这款软件的使用方法。

一、软件安装与启动1、安装首先,需要从官方渠道获取 GX_Developer 软件的安装包。

运行安装程序后,按照提示逐步进行操作。

在安装过程中,需要选择安装路径、语言等选项。

安装完成后,桌面上会出现软件的快捷方式图标。

2、启动双击桌面上的快捷方式图标,或者在开始菜单中找到GX_Developer 并点击打开。

启动软件后,会出现一个欢迎界面,随后进入主程序窗口。

二、界面介绍1、菜单栏菜单栏包含了软件的各种功能选项,如文件、编辑、视图、工程、在线、诊断等。

通过点击这些菜单,可以执行相应的操作。

2、工具栏工具栏提供了一些常用操作的快捷按钮,例如新建工程、打开工程、保存工程、编译、下载等,方便用户快速执行操作。

3、工程数据列表区在这个区域,可以查看和管理工程中的各种数据,如程序、参数、软元件注释等。

4、编程区这是编写 PLC 程序的主要区域,可以使用梯形图、指令表等编程语言进行编程。

5、状态栏状态栏显示当前软件的一些状态信息,如当前打开的工程名称、编程模式、在线状态等。

三、新建工程1、点击菜单栏中的“工程”,选择“新建工程”。

2、在弹出的新建工程对话框中,选择 PLC 系列和型号。

3、设置工程的名称、保存路径等信息。

4、选择编程语言,如梯形图或指令表。

5、点击“确定”按钮,完成新建工程。

四、编写程序1、在编程区,可以使用鼠标和键盘输入指令和软元件。

2、梯形图编程时,通过拖拽和连接图形符号来构建程序逻辑。

3、指令表编程时,直接输入指令和操作数。

4、可以使用软件提供的注释功能,为程序中的软元件和指令添加注释,提高程序的可读性。

CVM索引器编程手册-适用AP系列驱动器配置的MCK软件©techservo 2014深圳市泰科智能智能伺服技术有限公司版权说明本手册的版权为深圳市泰科智能智能伺服技术有限公司所有。

未经泰科智能智能许可,不得以任何方式复制和抄袭本手册的内容。

本文档仅供用户参考,文档中的内容力图精确和可靠,但错误和疏忽之处在所难免,如果您发现错误,请不吝赐教。

泰科智能智能保留随时修改和完善本文档的权利,有疑问请咨询我们,谢谢。

目录1.关于该手册 (6)2.泰科智能索引器程序 (6)2.1. 程序特性 (6)3.描述和操作 (7)3.1. 程序特性 (7)3.2. 序列选择 (7)3.2.1. 使用寄存器选择序列 (7)3.2.2. 使用数字输入选择序列 (8)3.3. Go命令 (9)3.3.1. 使用寄存器初始化Go (9)3.3.2. 使用数字输入初始化Go (9)3.3.3. 启动或复位时使用立即执行单个Go(Immediate Single Go)命令 (9)3.4. 优先输入命令 (10)3.5. 索引器程序寄存器 (10)3.6. 典型连接框图 (10)4.编程 (11)4.1. 步骤概述 (11)4.2. 驱动器基本设置 (12)4.2.1. 典型的驱动器基本设置 (12)4.2.2. 使用索引器程序配置为其他模式和命令源 (12)4.3. 打开索引器程序 (13)4.4. 索引器程序界面概述 (13)4.5. 菜单 (14)4.6. 工具栏功能 (14)4.7. 设置序列选择和Go命令 (15)4.7.1. 序列选择 (15)4.7.2. Go命令 (16)4.7.3. 优先输入命令 (17)4.8. 创建和修改序列 (18)4.9. 使用单步/调试模式 (19)4.9.1. 总述 (19)4.9.2. 进入单步/调试模式 (19)4.9.3. 退出单步/调试模式 (19)5.函数 (19)5.1. 使用寄存器向函数传值 (19)5.2. 多轴驱动器支持 (20)5.3. 等待运动完成(Wait Move Done) (20)5.4. 等待一个延时时间(Wait for Delay Time) (21)5.5. 等待事件(Wait for Event) (21)5.6. 等待输入掩码(Wait for Input Mask) (22)5.7. 位置等待(Wait for Position) (22)5.8. 输入等待(Wait for Input) (23)5.9. 参数等待(Wait for Parameter) (24)5.10. 设置电流上限(Set Current Limits) (25)5.11. 设置跟踪窗口(Set Tracking Windows) (25)5.12. 设置增益(Set Gain) (26)5.13. 位置模式下速度运动(Velocity Move Position Mode) (27)5.14. 运动(Move) (28)5.15. 回零点(Home) (29)5.16. 电流运动(Current Move) (30)5.17. 速度模式下的速度运动(Velocity Move Velocity Mode) (30)5.18. 模拟量速度模型(Analog Velocity Mode) (31)5.19. 模拟量位置模式(Analog Position Mode) (32)5.20. 停止驱动器工作(Disable Amplifier) (33)5.21. 凸轮内部主轴(Camming Internal Master) (33)5.22. 电子凸轮(Camming) (33)5.23. 外部数字量输入控制位置模式(Digital Position Mode) (34)5.24. 速度环单级点输出滤波(Velocity Loop Single Pole Output Filer) (35)5.25. 设置输出(Set Output) (36)5.26. 位置触发输出(Position Triggered Output) (36)5.27. 数学运算(Math) (37)5.28. 条件寄存器设置(If Register Set) (38)5.29. 获取设置参数(Get Set Parameter) (39)5.30. 条件跳转(Conditional Jump) (40)5.31. 扩展的数学运算(Extended Math) (40)5.32. 逻辑运算(Logic) (41)附录A:串口发送ASCII命令 (42)A.1. 连接 (42)A.1.1. 单轴连接 (42)A.1.2. 多点网络连接 (42)A.2. 通讯协议 (43)A.3. 读写寄存器 (43)附录B:回零点方法描述 (44)B.1. 回零点方法总述 (44)B.2. 回零点方法图例说明 (44)B.3. 回零点方法描述 (44)B.3.1. 设置当前位置为零点(Set current position as home) (44)B.3.2. 下一个索引脉冲(Next Index) (44)B.3.3. 限位开关(Limit Switch) (45)B.3.4. 碰到限位开关后反向第一个索引脉冲点(Limit Switch Out to Index) (45)B.3.5. 硬停止(Hardstop) (46)B.3.6. 硬停止后反向第一个索引脉冲(Hardstop Out to Index) (46)B.3.7. 零点开关(Home Switch) (47)B.3.8. 零点开关输出到第一个索引脉冲(Home Switch Out to Index) (48)B.3.9. 零点开关输入到第一个索引脉冲(Home Switch In to Index) (48)B.3.10. 零点开关下降沿(Lower Home) (49)B.3.11. 零点开关上升沿(Upper Home) (49)B.3.12. 零点开关下降沿外第一个索引脉冲(Lower Home Outside to Index) (50)B.3.13. 零点开关下降沿内第一个索引脉冲(Lower Home Inside to Index) (51)B.3.14. 零点开关上升沿外的第一个索引脉冲(Upper Home Outside to Index) (52)B.3.15. 零点开关上升沿内的第一个索引脉冲(Upper Home Inside to Index) (52)1.关于该手册本手册描述了泰科智能虚拟机(CVM)中的索引器程序(英文名字的直译,即Indexer 2 Program)使用说明。

图形化编程创作说明范文在本次创作说明中,我们将介绍图形化编程的基本概念、使用工具和步骤,并且展示一个简单的图形化编程创作案例。

希望通过本次创作说明,读者能够初步了解图形化编程的魅力,尝试使用图形化编程工具进行创作,并且得到一定的启发和帮助。

一、图形化编程的基本概念1. 图形化编程工具:图形化编程工具是一种特殊的软件开发工具,它以图形界面的形式呈现程序的逻辑结构、工作流程和数据流动。

用户通过拖拽、连接和配置各种图形化模块来创建程序,并且可以直观地查看程序的运行流程和结果。

2. 模块化编程:图形化编程是一种模块化的编程方式,程序由各种功能模块组成,每个模块代表一种功能或逻辑。

用户可以根据需要选择、拖拽和连接不同的模块,来组合出所需的程序。

3. 可视化编程:图形化编程是一种可视化的编程方式,用户无需理解复杂的代码语法和逻辑,只需要在图形化界面上进行操作,就能够创建程序。

这种编程方式适合初学者和非专业程序员使用。

二、图形化编程的使用工具和步骤1. 使用工具:目前市面上有很多图形化编程工具,比较常用的有Scratch、Blockly、App Inventor等。

这些工具都提供了丰富的图形化模块库,用户可以根据需要选择、拖拽和连接这些模块,来创建程序。

2. 创作步骤:(1)选择工具:首先需要选择一款适合自己需求的图形化编程工具。

(2)创建项目:打开选定的图形化编程工具,并创建一个新的项目。

(3)选择模块:根据项目需求,在工具提供的模块库中选择适合的模块。

(4)拖拽模块:将选择的模块拖拽到工作区,安排它们的位置和连接关系。

(5)配置模块:根据程序需求对各个模块进行配置,设置参数和逻辑。

(6)调试程序:在完成程序的拼接和配置后,进行程序的调试和测试,确保程序能够正确运行。

(7)保存和分享:如果程序创作完成,可以保存程序并且分享给其他人。

三、图形化编程创作案例下面我们将展示一个简单的图形化编程创作案例,以Scratch为例。

LD-D型MP3音乐打铃扩音机补充说明

手动播放

1、自动播放,直接按下数字键,大于5的曲目按5+后再按数字键。

2、手动播放可进行单曲和连续连续播放。

在校时状态下,按下“星期”键5秒,显示“CE--NO”,此时为单曲播放(播放完一首歌后自动停止播放),再按“星期”键5秒,显示“CE--ER”,此时为连续播放(播放完一首后自动播放下一首),每按“星期”键5秒,显示状态在二者之间转换。

手动编程

1、调整“功能”键至编程状态(编程灯亮),此时星期灯闪动。

2、调整“星期”键,选择打铃方式——七天编程、六天编程、五天编程或单天独立编程等,如调整星期一至星期日灯全亮,为七天编程。

3、选择好打铃方式后,按“存储”键。

特别注意:用户初次使用,在进行完本步骤时就进行总清。

按“清除/停止”键2秒,总清灯亮,屏显示“——”,约一分钟后,总清完毕。

重复第1、第2再进行后面的操作。

总清时,清除掉的程序与选择的打铃方式有关,若七天编程时,总清七天的内容。

在初次总清时,要在七天编程状态下进行。

4、调整“时间”至打铃点,调整“曲目”,选择相应曲目,然后按“存储”键,存储灯亮起,表示该次打铃点已存入。

5、重复第4步操作,直至将所有打铃点存储完毕。

特别注意:存储过程中若有错误,可利用“清除/停止”键,进行单点清除。

在已存入的打铃点上(此时存储灯亮),按一下“清除/停止”键,存储灯灭,表示此打铃点已清除,然后存入正确的打铃点。

6、所有打铃点存储完毕后,可按下“时间”,检查一遍所有的打铃点是否正确。

7、确认打铃点正确无误后,调整“功能”至自动状态,便可正常工作。

说明:若用户时间表上要求某一天的程序与其它不同,可进行以下操作。

将程序编完后,调整“星期”键,使这一天灯亮,按下“存储”键。

此时可进行两种操作。

一是按下“总清”,将这一天的程序全部清除掉,然后按照第3、4、5、6步骤,将这一天的程序输入进去。

二是若这一天与其它六天只有几个打铃点不同,可将这一天未存入的打铃点存进去,将多存入的清除掉。