IA调试手册中文版2017

- 格式:pdf

- 大小:7.74 MB

- 文档页数:16

300MW机组DEH、MEH系统说明书(ia)13-7-25 300MW机组DEH系统说明书1/25汽轮机数字电调控制系统说明书图号:71.K156.35-01上海汽轮机有限公司2021.613-7-25 300MW机组DEH系统说明书2/25300MW机组DEH、MEH系统? DEH控制系统的组成DEH控制系统由下列几部分组成: 1.1 DEH系统DEH控制器采用上海FOXBORO公司的I/A系统硬件,其组成及硬件配置详见传递图及有关硬件资料。

1.2 EH系统EH系统包括控制阀门的油动机及其向油动机提供高压抗燃油的EH供油系统,除此之外还包括控制油动机紧急关闭的危急遮断控制块(电磁阀)和隔膜阀等部件。

EH系统的功能是接受DEH输出指令,控制汽轮机进汽阀门开度,改变进入汽轮机的蒸汽流量,满足汽轮机转速及负荷调节的要求。

同时通过危急遮断控制块(电磁阀)接受危急遮断系统输出指令,通过隔膜阀接受保安系统信号,控制油动机的紧急关闭。

因此EH 系统实际上是DEH控制器及危急遮断系统或保安系统的执行机构。

控制阀门的油动机共有:主汽门油动机2个,调节汽阀油动机4个,再热调节汽阀油动机2个,再热主汽门油动机2个。

其中再热主汽门油动机为二位式结构,主汽门、调节汽阀及再热调节汽阀油动机为连续控制式结构。

1.3 保安系统包括机械超速危急遮断器,危急遮断油门,手拍危急遮断装置以及危急遮断复位装置等保安部套。

保安系统以隔膜阀为媒体将停机信号传递到EH系统,控制油动机的紧急关闭。

一、 DEH系统功能汽轮机组采用由纯电调和液压伺服系统组成的数字式电液控制系统(DEH),提供了以下几种运行方式:? 操作员自动控制13-7-25 300MW机组DEH系统说明书3/25? 汽轮机自启动 ? 自同期运行 ? DCS远控运行 ? 手动控制通过这几种运行方式,可以实现汽轮机控制的基本功能如转速控制、功率控制、工程师站和操作员站的画面是主机控制接口,它是用来传递指令给汽轮机和获得运行所需的资料。

管线阀门API规范6D第22版2002年1月ISO14313 : 1999,石油和天然气工业——管线输送系统—— 管线阀门生效日期:2002年7月1日国家推荐采用国石油学会第22版6D ISO14313:1999 API前言本标准归口于API阀门和井口设备标准分委员会(API C1/SC6)管辖。

本API标准与ISO14313:1999的英文版等同。

ISO14313由石油、天然气工业SC2管线输送系统的材料、设备和海上结构的ISO/TC67技术委员会编制。

本标准已对下列版本进行了修改:a) 取消了来自于国际标准的ISO前言代之的API特殊的注解和前言;b) 包括了国标指导性附录(附录E—API会标)给使用者提供指南。

本标准在封面上打印生效日期,但可以从发布之日起使用。

API出版物可以被任何想要引用的人使用,学会已尽了最大努力保证出版的资料准确并可靠。

但是学会对这些出版物并不表明或者作出保证,并且特别说明不对由于使用本标准而造成损失或损坏承担任何责任,也不因出版物有矛盾而违背联邦、州或地方的法规承担任何责任。

邀请建议的修改宜送交给Upstream Segment, API, 1200 L Street, NW Washington, D. C. 20005。

翻译:朱翌总校对:王国平ISO14313:1999 API第22版6D特别注解API出版物有必要提出一个共性的问题,有关特殊的情况,宜审查地方、州和联邦的法律和法规。

API没有要求雇主、制造厂或供货商承担预先告知和适当培训及装备其雇员和涉及健康和安全危害有关人员的责任,也没有要求他们承担地方、州和联邦法律的责任。

涉及安全和健康危害的资料和有关特殊材料和条件的适当的预防措施宜从雇主、制造厂或该材料的供货商获得,或者从材料的安全参数资料中获得。

API出版物中所含有的内容对于制造、销售任何方法的使用、专利证书范围内的设备或产品并不意味着授与了任何权利,也不保证任何人在使用出版物所包含的内容中不侵犯有关专利证书而违反法律规定。

Intel® 64 and IA-32 ArchitecturesSoftware Developer’s ManualVolume 3 (3A, 3B, 3C & 3D):System Programming GuideNOTE: The Intel 64 and IA-32 Architectures Software Developer's Manual consists of four volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A-Z, Order Number 325383; System Programming Guide, Order Number 325384; Model-Specific Registers, Order Number 335592. Refer to all four volumes when evaluating your design needs.Order Number: 325384-065USDecember 2017Intel technologies features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at , or from the OEM or retailer.No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifica-tions. Current characterized errata are available on request.This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmapsCopies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting /design/literature.htm.Intel, the Intel logo, Intel Atom, Intel Core, Intel SpeedStep, MMX, Pentium, VTune, and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.*Other names and brands may be claimed as the property of others.Copyright © 1997-2017, Intel Corporation. All Rights Reserved.CONTENTSPAGECHAPTER 1ABOUT THIS MANUAL1.1INTEL® 64 AND IA-32 PROCESSORS COVERED IN THIS MANUAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1 1.2OVERVIEW OF THE SYSTEM PROGRAMMING GUIDE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4 1.3NOTATIONAL CONVENTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6 1.3.1Bit and Byte Order. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6 1.3.2Reserved Bits and Software Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7 1.3.3Instruction Operands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8 1.3.4Hexadecimal and Binary Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8 1.3.5Segmented Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8 1.3.6Syntax for CPUID, CR, and MSR Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9 1.3.7Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9 1.4RELATED LITERATURE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10CHAPTER 2SYSTEM ARCHITECTURE OVERVIEW2.1OVERVIEW OF THE SYSTEM-LEVEL ARCHITECTURE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1 2.1.1Global and Local Descriptor Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3 2.1.1.1Global and Local Descriptor Tables in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.1.2System Segments, Segment Descriptors, and Gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.1.2.1Gates in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.1.3Task-State Segments and Task Gates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.3.1Task-State Segments in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.4Interrupt and Exception Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.4.1Interrupt and Exception Handling IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 2.1.5Memory Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.1.5.1Memory Management in IA-32e Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.1.6System Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.1.6.1System Registers in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.1.7Other System Resources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.2MODES OF OPERATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.2.1Extended Feature Enable Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9 2.3SYSTEM FLAGS AND FIELDS IN THE EFLAGS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9 2.3.1System Flags and Fields in IA-32e Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11 2.4MEMORY-MANAGEMENT REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11 2.4.1Global Descriptor Table Register (GDTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12 2.4.2Local Descriptor Table Register (LDTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12 2.4.3IDTR Interrupt Descriptor Table Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12 2.4.4Task Register (TR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13 2.5CONTROL REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13 2.5.1CPUID Qualification of Control Register Flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-19 2.6EXTENDED CONTROL REGISTERS (INCLUDING XCR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19 2.7PROTECTION KEY RIGHTS REGISTER (PKRU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21 2.8SYSTEM INSTRUCTION SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21 2.8.1Loading and Storing System Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-23 2.8.2Verifying of Access Privileges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-23 2.8.3Loading and Storing Debug Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-24 2.8.4Invalidating Caches and TLBs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-24 2.8.5Controlling the Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-25 2.8.6Reading Performance-Monitoring and Time-Stamp Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-25 2.8.6.1Reading Counters in 64-Bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26 2.8.7Reading and Writing Model-Specific Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26 2.8.7.1Reading and Writing Model-Specific Registers in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26 2.8.8Enabling Processor Extended States. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26Vol. 3A iiiCONTENTSiv Vol. 3A PAGECHAPTER 3PROTECTED-MODE MEMORY MANAGEMENT3.1MEMORY MANAGEMENT OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1 3.2USING SEGMENTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2 3.2.1Basic Flat Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3 3.2.2Protected Flat Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3 3.2.3Multi-Segment Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4 3.2.4Segmentation in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5 3.2.5Paging and Segmentation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5 3.3PHYSICAL ADDRESS SPACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6 3.3.1Intel® 64 Processors and Physical Address Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6 3.4LOGICAL AND LINEAR ADDRESSES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6 3.4.1Logical Address Translation in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7 3.4.2Segment Selectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7 3.4.3Segment Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8 3.4.4Segment Loading Instructions in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9 3.4.5Segment Descriptors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9 3.4.5.1Code- and Data-Segment Descriptor Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12 3.5SYSTEM DESCRIPTOR TYPES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13 3.5.1Segment Descriptor Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-14 3.5.2Segment Descriptor Tables in IA-32e Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-16CHAPTER 4PAGING4.1PAGING MODES AND CONTROL BITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1 4.1.1Three Paging Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1 4.1.2Paging-Mode Enabling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3 4.1.3Paging-Mode Modifiers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4 4.1.4Enumeration of Paging Features by CPUID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5 4.2HIERARCHICAL PAGING STRUCTURES: AN OVERVIEW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6 4.332-BIT PAGING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7 4.4PAE PAGING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13 4.4.1PDPTE Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-13 4.4.2Linear-Address Translation with PAE Paging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-14 4.54-LEVEL PAGING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19 4.6ACCESS RIGHTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28 4.6.1Determination of Access Rights . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-29 4.6.2Protection Keys . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-31 4.7PAGE-FAULT EXCEPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-31 4.8ACCESSED AND DIRTY FLAGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-33 4.9PAGING AND MEMORY TYPING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-34 4.9.1Paging and Memory Typing When the PAT is Not Supported (Pentium Pro and Pentium II Processors). . . . . . . . . . . . . .4-34 4.9.2Paging and Memory Typing When the PAT is Supported (Pentium III and More Recent Processor Families). . . . . . . . . .4-34 4.9.3Caching Paging-Related Information about Memory Typing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-35 4.10CACHING TRANSLATION INFORMATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-35 4.10.1Process-Context Identifiers (PCIDs). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-35 4.10.2Translation Lookaside Buffers (TLBs). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-36 4.10.2.1Page Numbers, Page Frames, and Page Offsets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-36 4.10.2.2Caching Translations in TLBs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-37 4.10.2.3Details of TLB Use. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-37 4.10.2.4Global Pages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-38 4.10.3Paging-Structure Caches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-38 4.10.3.1Caches for Paging Structures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-38 4.10.3.2Using the Paging-Structure Caches to Translate Linear Addresses. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-40 4.10.3.3Multiple Cached Entries for a Single Paging-Structure Entry. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41 4.10.4Invalidation of TLBs and Paging-Structure Caches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41 4.10.4.1Operations that Invalidate TLBs and Paging-Structure Caches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41 4.10.4.2Recommended Invalidation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-43 4.10.4.3Optional Invalidation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-44 4.10.4.4Delayed Invalidation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-45 4.10.5Propagation of Paging-Structure Changes to Multiple Processors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-46 4.11INTERACTIONS WITH VIRTUAL-MACHINE EXTENSIONS (VMX). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-47 4.11.1VMX Transitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-47CONTENTSPAGE 4.11.2VMX Support for Address Translation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-474.12USING PAGING FOR VIRTUAL MEMORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-47 4.13MAPPING SEGMENTS TO PAGES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-48CHAPTER 5PROTECTION5.1ENABLING AND DISABLING SEGMENT AND PAGE PROTECTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1 5.2FIELDS AND FLAGS USED FOR SEGMENT-LEVEL ANDPAGE-LEVEL PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2 5.2.1Code-Segment Descriptor in 64-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3 5.3LIMIT CHECKING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4 5.3.1Limit Checking in 64-bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5 5.4TYPE CHECKING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5 5.4.1Null Segment Selector Checking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6 5.4.1.1NULL Segment Checking in 64-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6 5.5PRIVILEGE LEVELS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6 5.6PRIVILEGE LEVEL CHECKING WHEN ACCESSING DATA SEGMENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8 5.6.1Accessing Data in Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9 5.7PRIVILEGE LEVEL CHECKING WHEN LOADING THE SS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10 5.8PRIVILEGE LEVEL CHECKING WHEN TRANSFERRING PROGRAM CONTROL BETWEEN CODE SEGMENTS . . . . . . . . . . . . . . . . 5-10 5.8.1Direct Calls or Jumps to Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10 5.8.1.1Accessing Nonconforming Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11 5.8.1.2Accessing Conforming Code Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12 5.8.2Gate Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13 5.8.3Call Gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13 5.8.3.1IA-32e Mode Call Gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14 5.8.4Accessing a Code Segment Through a Call Gate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15 5.8.5Stack Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17 5.8.5.1Stack Switching in 64-bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19 5.8.6Returning from a Called Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20 5.8.7Performing Fast Calls to System Procedures with theSYSENTER and SYSEXIT Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20 5.8.7.1SYSENTER and SYSEXIT Instructions in IA-32e Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21 5.8.8Fast System Calls in 64-Bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22 5.9PRIVILEGED INSTRUCTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23 5.10POINTER VALIDATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24 5.10.1Checking Access Rights (LAR Instruction) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24 5.10.2Checking Read/Write Rights (VERR and VERW Instructions). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25 5.10.3Checking That the Pointer Offset Is Within Limits (LSL Instruction). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25 5.10.4Checking Caller Access Privileges (ARPL Instruction). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26 5.10.5Checking Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27 5.11PAGE-LEVEL PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27 5.11.1Page-Protection Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.2Restricting Addressable Domain. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.3Page Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.4Combining Protection of Both Levels of Page Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 5.11.5Overrides to Page Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29 5.12COMBINING PAGE AND SEGMENT PROTECTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29 5.13PAGE-LEVEL PROTECTION AND EXECUTE-DISABLE BIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30 5.13.1Detecting and Enabling the Execute-Disable Capability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30 5.13.2Execute-Disable Page Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30 5.13.3Reserved Bit Checking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31 5.13.4Exception Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32CHAPTER 6INTERRUPT AND EXCEPTION HANDLING6.1INTERRUPT AND EXCEPTION OVERVIEW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1 6.2EXCEPTION AND INTERRUPT VECTORS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1 6.3SOURCES OF INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2 6.3.1External Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2 6.3.2Maskable Hardware Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3 6.3.3Software-Generated Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4Vol. 3A v。

电子产品中限用物质的测定第8 部分:气相色谱-质谱法测定聚合物中的邻苯二甲酸酯(GC-MS),(PY/TD-GC-MS)这个标准基于以下文件:CDV Report on voting111/416/CDV 111/430/RVC1 范围1.1 IEC 62321 的这一部分给出了两个标准和两个信息型技术来测定电子产品中聚合物的DIBP、DBP、BBP、DEHP、DNOP、DINP、DIDP 含量;1.2 GC-MS 和PY/TD-GC-MS 技术在本文的标准中作了详细说明;1.3 GC-MS 测试DIBP、DBP、BBP、DEHP、DNOP、DINP、DIDP 的定量限值范围为50mg/kg-2000mg/kg;1.4 TD-GC-MS 测试DIBP、DBP、BBP、DEHP、DNOP、DINP、DIDP 的筛选和半定量限值范围为100mg/kg-2000mg/kg;1.5 IAMS 适用于DIBP、DBP、BBP、DEHP、DNOP、DINP、DIDP 的筛选和半定量,但由于峰值和分辨率的限制,DBP、DIBP、DEHP、DNOP 还没能建立IAMS 的方法;1.6 LC-MS 技术仅限于测定BBP、DEHP、DNOP、DINP 和DIDP,由于峰值和分辨率的限制,DBP、DIBP 还没有合适的LC-MS 方法;1.7 本文档提供了一个标准的PY/TD-GC-MS 和GC-MS、可参考的直接进样的IAMS 和LC-MS的流程图;1.8 本文档的标准已经用含有个别浓度在450mg/kg~30000mg/kg 邻苯二甲酸盐的PE 和PVC材料评估了这4 种测试方法,本文档对上述的其他聚合物,其他邻苯二甲酸化合物以及其他浓度范围未做具体研究。

2 引用标准下列的整个或部分文件对这个文档的参考不可或缺,它表明了标准的日期,引用的版本,对未标明的标准,标准文件的最终版本(包括修订版)可用。

IEC62321-1:2013 电子产品的限用物质的测定第一部分3 术语、定义和缩写词3.1 术语和定义对于这个文档,使用下列术语和定义,ISO 和IEC 官网有维护。

电子产品中限用物质的测定第8 部分:气相色谱-质谱法测定聚合物中的邻苯二甲酸酯(GC-MS),(PY/TD-GC-MS)这个标准基于以下文件:CDV Report on voting111/416/CDV 111/430/RVC1 范围1.1 IEC 62321 的这一部分给出了两个标准和两个信息型技术来测定电子产品中聚合物的DIBP、DBP、BBP、DEHP、DNOP、DINP、DIDP 含量;1.2 GC-MS 和PY/TD-GC-MS 技术在本文的标准中作了详细说明;1.3 GC-MS 测试DIBP、DBP、BBP、DEHP、DNOP、DINP、DIDP 的定量限值范围为50mg/kg-2000mg/kg;1.4 TD-GC-MS 测试DIBP、DBP、BBP、DEHP、DNOP、DINP、DIDP 的筛选和半定量限值范围为100mg/kg-2000mg/kg;1.5 IAMS 适用于DIBP、DBP、BBP、DEHP、DNOP、DINP、DIDP 的筛选和半定量,但由于峰值和分辨率的限制,DBP、DIBP、DEHP、DNOP 还没能建立IAMS 的方法;1.6 LC-MS 技术仅限于测定BBP、DEHP、DNOP、DINP 和DIDP,由于峰值和分辨率的限制,DBP、DIBP 还没有合适的LC-MS 方法;1.7 本文档提供了一个标准的PY/TD-GC-MS 和GC-MS、可参考的直接进样的IAMS 和LC-MS的流程图;1.8 本文档的标准已经用含有个别浓度在450mg/kg~30000mg/kg 邻苯二甲酸盐的PE 和PVC材料评估了这4 种测试方法,本文档对上述的其他聚合物,其他邻苯二甲酸化合物以及其他浓度范围未做具体研究。

2 引用标准下列的整个或部分文件对这个文档的参考不可或缺,它表明了标准的日期,引用的版本,对未标明的标准,标准文件的最终版本(包括修订版)可用。

IEC62321-1:2013 电子产品的限用物质的测定第一部分3 术语、定义和缩写词3.1 术语和定义对于这个文档,使用下列术语和定义,ISO 和IEC 官网有维护。

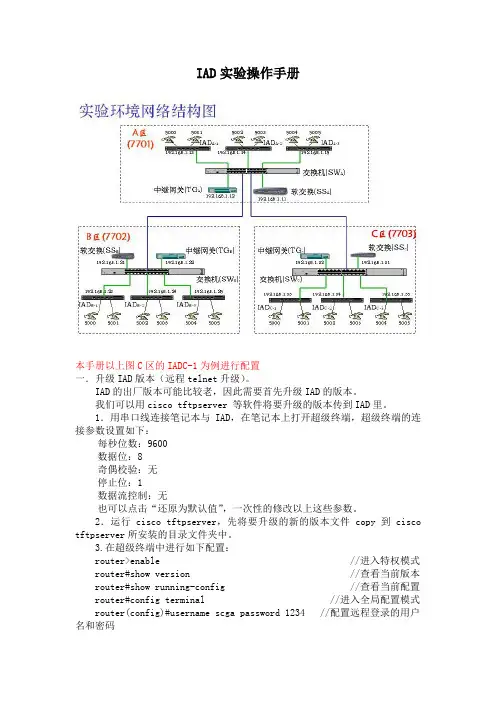

IAD实验操作手册本手册以上图C区的IADC-1为例进行配置一.升级IAD版本(远程telnet升级)。

IAD的出厂版本可能比较老,因此需要首先升级IAD的版本。

我们可以用cisco tftpserver 等软件将要升级的版本传到IAD里。

1.用串口线连接笔记本与IAD,在笔记本上打开超级终端,超级终端的连接参数设置如下:每秒位数:9600数据位:8奇偶校验:无停止位:1数据流控制:无也可以点击“还原为默认值”,一次性的修改以上这些参数。

2.运行cisco tftpserver,先将要升级的新的版本文件copy到cisco tftpserver所安装的目录文件夹中。

3.在超级终端中进行如下配置:router>enable //进入特权模式router#show version //查看当前版本router#show running-config //查看当前配置router#config terminal //进入全局配置模式router(config)#username scga password 1234 //配置远程登录的用户名和密码router(config)#enablepassword 1234 //配置enable密码router(config)#interface fastethernet 0/0 //进入端口配置模式router(config-fastethernet0/0)#ip add 192.168.1.33 255.255.255.0//配置IAD的百兆口IP地址router(config-fastethernet0/0)#exit //退出端口配置模式router(config)#ip route 0.0.0.0 0.0.0.0 192.168.1.254//配置缺省路由router(config)#line vty 0 4 //进入line配置模式router(config-line)#login local //允许远程登录router(config-line)#exitrouter(config)#exitrouter#wr //保存配置4.进入“cmd”命令行模式,输入以下命令:telnet 192.168.1.33 //远程登录到IAD上username:scga //输入用户名password: //输入密码router>enable //进入特权模式password: //输入enable密码router#copy tftp flash //拷贝新版本到IAD中IP Address of remote host [0.0.0.0] :192.168.1.36 //输入存放新版本文件的笔记本IP地址Source file name [VLRT.DLZ] :gw1000.dlz //输入新版本的文件名Download Flash from host 192.168.1.36 file "gw1000.dlz" [Y/n]? y//输入“y”确认升级############################################Overwrite Flash [Y/n] :y //输入“y”确认写入新版本!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!router#reboot //重启IAD Proceed with reload? (yes/no):y //输入“y”确认重启二.配置IAD配置IAD可以通过超级终端,远程telnet等方式,这两种方式到IAD的连接如前所述。

PSL 641数字式线路保护装置使用说明书目录注意事项............................................................................................................................................................... 错误!未定义书签。

1.装置介绍. (1)1.1.面板布置 (1)1.2.键盘简介 (2)1.3.信号灯简介 (3)1.4.串行接口 (4)1.5.操作区简介 (4)1.6.出厂铭牌 (5)1.7.背板及端子简介 (6)2.菜单操作 (14)2.1功能简介 (14)2.2操作说明 (15)3.用户调试大纲 (31)3.1.装置通电前检查 (31)3.2.绝缘检查 (31)3.3.上电检查 (31)3.4.采样精度检查 (31)3.5.接点输出校验 (31)3.6.定值校验 (32)3.7.跳合闸电流保持试验 (32)3.8.相序检查 (32)3.9.校准时钟 (32)4.事件信息一览表 (33)4.1.PSL640系列保护事件信息一览表 (33)4.2.PSL640系列保护告警事件信息一览表(告警、呼唤为相同的灯光信号) (33)4.3.PSL640保护压板信息一览表 (34)4.4.PSL640保护遥测量信息一览表 (34)4.5.PSL640保护遥信量信息一览表 (35)5.附图 (36)1.装置介绍1.1.面板布置1.2.键盘简介PS 640系列保护装置键盘示意图1.3.信号灯简介。

--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--I Q调试手册中文版(总77页)电动执行机构IQ系列安装和维护手册请确保完整阅读和理解本手册出版物编号 E170C2Rotork设定器可按现场要求对执行器的控制、指示、保护功能进行设定。

所有的执行器在投入使用前,有必要检查其与过程控制系统要求的兼容性。

请阅读本手册。

当Rotork工作人员或指定代理商按照合同规定进行现场调试和验收时,执行器组态的相关文件应让客户留档备查。

3本手册提供如下介绍:* 手动和电动(就地和远程)操作。

* 执行器的准备和安装。

* 根据有关阀门正确操作的要求,对执行器进行初级设定。

* 根据现场具体控制和指示的要求,对执行器进行二级设定。

* 维护 - 故障排除。

* 销售和服务。

RotorkIQ系列执行器 - 全世界首家推出无需打开电气端盖即可进行调试和查询的阀门执行器。

使用所提供的红外线设定器进入执行器的设定程序,即使在危险区域,也可安全、快捷地对力矩值、限位以及其它所有控制和指示功能进行设定。

IQ的设定和调整在执行器主电源接通和断开时均可完成。

标准诊断功能可对控制系统、阀门和执行器的状态进行诊断,并通过执行器的显示屏上的图标和帮助屏幕来显示。

按一下设定器的按键即可在显示屏上对相应阀位的瞬时力矩进行监视。

内置的数据记录器可获取操作和阀门力矩数据,可提醒用户根据需要对阀门进行维护。

运行于PC 机的IQ Insight软件和/或Rotork本安型通讯器可4访问数据记录器,可对执行器的所有功能进行组态和记录。

执行器是否带有设定器,可根据接线端子箱盖上的黄色标签来识别。

有关Rotork IQ和其它系列执行器的资料,可浏览我们的网站。

56目录页码1 健康与安全22 保存3 3 IQ系列执行器的操作3手动操作3电动操作3执行器的显示 -4阀位指示执行器的显示 -5报警指示4 准备驱动轴套74.1IQ7至IQ357A和Z型推力底座4.2IQ7至IQ357B型非推力底座4.3IQ40至IQ958A和Z型推力底座4.4IQ40至IQ959B型非推力底座5 执行器的安装10提升杆式阀门 -11顶部安装带齿轮箱的阀门-11侧面安装非提升杆式阀门-11顶部安装手轮密封11IQM调节型执行器12IQML线性推力装置12IQML线性行程的调整126 接线14地线的连接14端子箱盖的拆卸14电缆入口14端子的接线15端子箱盖的复位157 设定16设定程序16设定器17进入设定程序18设定方式-口令18新口令18检查方式18程序路径分支-19分支点 (Cr)7.8 执行器的显示19设定 / 检查方式返回阀位指示198 设定-初级设定功能20初级设定功能目录 219 设定 -二级设定功能30二级设定功能目录 3010 维护和故障排除61帮助显示63IrDA诊断和组态6811 重量和尺寸70二进制、十六进制、十进制71换算表123本手册是为让用户能够胜任对Rotork IQ 系列执行器的安装、操作、调试及检查而出版的。

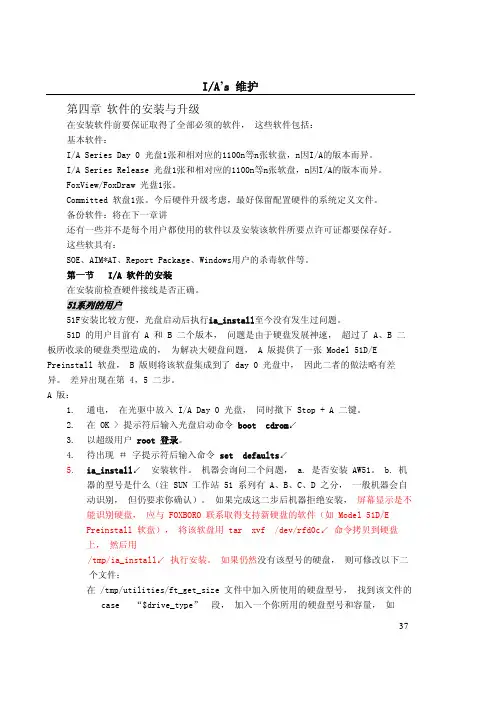

I/A’s 维护第四章 软件的安装与升级在安装软件前要保证取得了全部必须的软件, 这些软件包括:基本软件:I/A Series Day 0 光盘1张和相对应的1100n等n张软盘,n因I/A的版本而异。

I/A Series Release 光盘1张和相对应的1100n等n张软盘,n因I/A的版本而异。

FoxView/FoxDraw 光盘1张。

Committed 软盘1张。

今后硬件升级考虑,最好保留配置硬件的系统定义文件。

备份软件:将在下一章讲还有一些并不是每个用户都使用的软件以及安装该软件所要点许可证都要保存好。

这些软具有:SOE、AIM*AT、Report Package、Windows用户的杀毒软件等。

第一节 I/A 软件的安装在安装前检查硬件接线是否正确。

51系列的用户51F安装比较方便,光盘启动后执行ia_install至今没有发生过问题。

51D 的用户目前有 A 和 B 二个版本, 问题是由于硬盘发展神速, 超过了 A、B 二板所收录的硬盘类型造成的, 为解决大硬盘问题, A 版提供了一张 Model 51D/E Preinstall 软盘, B 版则将该软盘集成到了 day 0 光盘中, 因此二者的做法略有差异。

差异出现在第 4,5 二步。

A 版:1.通电, 在光驱中放入 I/A Day 0 光盘, 同时揿下 Stop + A 二键。

2.在 OK > 提示符后输入光盘启动命令 boot cdrom↙3.以超级用户 root 登录。

4.待出现 # 字提示符后输入命令 set defaults↙5.ia_install↙ 安装软件。

机器会询问二个问题, a. 是否安装 AW51。

b. 机器的型号是什么(注 SUN 工作站 51 系列有 A、B、C、D 之分, 一般机器会自动识别, 但仍要求你确认)。

如果完成这二步后机器拒绝安装, 屏幕显示是不能识别硬盘, 应与 FOXBORO 联系取得支持新硬盘的软件(如 Model 51D/EPreinstall 软盘), 将该软盘用 tar xvf /dev/rfd0c↙ 命令拷贝到硬盘上, 然后用/tmp/ia_install↙ 执行安装。

IALA VTS手册-2002这部第三版的IALA VTS手册着眼于更新原有版本中的指南和帮助,以便行政管理部门和主管机关考虑实施一个新的VTS,或更新一个己有的VTS 。

自1955年第一次讨论把岸基雷达装置和甚高频(VHF)无线电话通信的使用作为提高海运便利的一种方法起,IALA就与VTS的发展联系在一起。

IALA关注着VTS的发展并认识到国与国之间存在不协调与不一致,认为需要有一个论坛供类似问题的讨论和经验共享。

为此,IALA在1980年成立了一个VTS委员会以担当此项工作。

自那时起,VTS委员会己稳步成长并发展成为全球最重要的船舶交管系统(VTS)论坛。

委员会已有大约60个成员代表航标当局、IALA产业实体成员和国际组织,如IAPH和IMPA,它既关注VTS的规则,也关注VTS的运行。

IALA在VTS事务中与I MO密切合作,本手册就是建立在IMO关于VTS的A.857号决议基础上,并应与其一同考虑。

IALA当前在VTS事务中的活动将远远不只是手册的发行,还包括IALA/IAPH/IMPA的VTS事务中VTS各项细节的准备。

本手册中涉及的IALA建议案、指南和示范课程可从IALA总部获取。

第一章绪论 (6)1.1 VTS发展的背景 (6)1.2 手册中使用的术语的定义和词汇表 (7)第二章规划VTS (10)2.1 规划VTS时应考虑的因素 (10)2.1.1 总则 (10)2.1.2 开发和实现 (10)2.1.3 初始阶段 (13)2.1.4 可行性和设计研究阶段 (14)2.1.4.1 总则 (15)2.1.4.2 VTS覆盖水域概况 (15)2.1.4.3 环境方面 (16)2.1.4.4 系统用户和用户要求 (16)2.1.4.5 技术规格分阶段 (18)2.1.5 风险评估阶段 (18)2.1.6 费/效阶段 (19)2.1.7 实施阶段 (19)2.1.8 评价阶段 (20)2.2 服务和运行项目 (20)2.2.1 服务项目 (20)2.2.2 信息服务 (20)2.2.3 助航服务 (20)2.2.4 交通组织服务 (21)2.2.5 运行制度和规则 (22)2.2.6 同联合服务、港口运营、应急服务和相邻VTS的协作 (23)2.3 技术项目 (23)2.3.1 数据收集 (24)2.3.2 数据评价 (25)2.3.3 数据发布 (25)2.4 法律因素 (26)2.4.1 总则 (26)2.4.2 职权 (26)2.4.3 VTS与船舶间的关系 (28)2.4.4 责任 (28)2.5 内陆水域VTS (28)第三章构建VTS (30)3.1 运行原则和方法 (30)3.1.1 原则 (30)3.1.2 方法 (31)3.1.2.1地域分隔 (31)3.1.2.2 时间分隔 (31)3.1.2.3 距离分隔 (31)3.2 设施提供 (32)3.2.1 支持VTS的基础设施 (32)3.2.2 基础设施的运行方面 (32)3.2.3 基础设施的技术方面 (33)3.2.4 基础设施的管理方面 (34)3.3 设备提供 (34)3.3.1 总则 (34)3.3.2 VTS分部或分区的划分 (35)3.3.3 VTS覆盖水域的监控要求 (36)3.3.3.1 监控区域范围 (36)3.3.3.2 运行条件 (37)3.3.3.3 探测性能 (37)3.3.3.4雷达精度 (38)3.3.3.5距离分辨率和精度 (38)3.3.3.6 方位分辨率和精度 (38)3.3.3.7 跟踪 (38)3.3.3.8 显示 (41)3.3.4 通信要求 (41)3.3.4.1与VTS覆盖水域内航行船舶的通信 (42)3.3.4.2 其他通信 (42)3.3.4.3通信录音设备 (43)3.3.5 附属设备 (43)3.3.5.1 VTS操作员工作站 (43)3.3.5.2附加控制台 (44)3.3.6 设备的有效性和稳定性 (44)3.3.7 设备选择 (45)3.3.8 文件 (45)第四章 AIS---VTS工具 (46)4.1 总则 (46)4.2 AIS作用 (46)4.2.1 自动船舶识别 (46)4.2.2 VHF通信 (47)4.2.3 改进船舶跟踪 (47)4.2.3.1 较宽的地理覆盖范围。

315项目命令行界面(CLI)基本操作手册一:登录系统 (3)二:查看配置 (3)2.1 网络配置(公网)查看 (3)2.2 协议配置查看 (4)2.3 DSP参数配置查看 (5)2.4 私网状态查看 (6)2.5 端点状态查看 (7)2.6 版本信息查看 (7)三:基本调试命令 (7)3.1 ping 的使用 (7)3.2 路由及内存的查看 (8)3.3配置的生效 (8)3.4 VLAN的设置 (9)3.5 公网ip、子网掩码和网关的配置 (10)3.6 DNS设置命令 (11)3.7 MG MGC的设置 (11)3.8 手动注册/注销 (11)3.9 退出命令 (12)3.10 退出CLI界面命令 (13)四:测试时常用命令 (13)4.1修改进程音配置 (13)4.2 静音压缩、回声抑制、舒适噪声本地开关 (14)4.3 RTP名称的配置 (14)4.4 编码方式的本地配置 (14)4.5 MGC模式配置配置 (15)4.6 fax本地配置 (15)4.7 区别振铃的配置 (16)4.8 来电显示的模式配置 (16)4.9 增益的配置 (16)4.10 DTMF(2833 )本地配置 (17)一:登录系统一级用户名和密码都是“gepon”输入“enable”按回车,进入二级密码输入,二级密码为“gepon”如下:********** Level-1 login **********Username: geponPassword: *****# enable********** Level-2 login **********Password: *****Level-2 login success. Configuring is availible.#在进入Level-1后,只具有查看部分参数的权限;进入Level-2,具有查看所有参数和修改参数权限。

二:查看配置2.1 网络配置(公网)查看在根路径下输入network 回车就可以查看相关的网络配置,如下:# networkCurrent network configurations:( "*" means the Running Config V alue)Net Mode: StaticPublic IP: 192.168.1.110Net mask: 255.255.0.0Gateway: 0.0.0.0DNS1: 0.0.0.0DNS2: 0.0.0.0MAC: 00:0a:c2:10:01:10Hostname:VLAN: disabledVLAN TAG: 4088NTP: enabledNtphostname: 在network路径下,也可以通过输入show all 查看当前路径下的所有配置,如下:network> show all( "*" means the Running Config V alue)Net Mode: Static (网络模式)Public IP: 192.168.1.110 (公网IP)Net mask: 255.255.0.0 (子网掩码)Gateway: 0.0.0.0 (网关)DNS1: 0.0.0.0 (DNS 1)DNS2: 0.0.0.0 (DNS 2)MAC: 00:0a:c2:10:01:10 (IAD MAC地址)Hostname:VLAN: disabled (VLAN 使能)VLAN TAG: 4088 (VLAN tag)NTP: enabled (NTP使能)Ntphostname: (NTP服务器)其中第一项Net Mode为网络模式,分为静态(Static),DHCP模式和PPPOE模式。

User Manual ESI-AM 2017 MODULESDocument Version 2017-08-271.Contents1.CONTENTS (2)2.INTRODUCTION (3)3.NUMERICAL WORK FLOW (3)4.MODULES (4)5.ADDITIONAL FEATURES (7)2.IntroductionESI-AM integrates tools and solvers that resolve powder scale as well as component scale phenomenon. ESI-AM is this the first commercial integrated material engineering platform dedicated to metallic additive manufacturing. V2017 of ESI-AM focusses on Powder Bed Fusion (PBF) processes.ESI-AM graphical user interface implicitly suggests a work flow supporting rapid low cost qualification of additive manufacturing processes and products.ESI-AM nevertheless retains the flexibility that each tool can be used separately. It is not necessary to use the solvers in a certain sequence. Each tool can be run operated based on the data bases, experimental data or experience. This document describes ESI-AM numerical work flow and the modules utilized. The theory, assumptions and user manuals are available in separate documents.3.Numerical Work FlowThe numerical work flow depicted below ensures the transfer of process relevant information across multiple length and time scales to assess different aspects of the additive manufacturing processes. The overall procedure is the foundation for simulation based qualification of the powder, process parameters and the work piece.Prescan optimizes process parameters to achieve high material density and maximum build rate. Eligible process parameter combinations (pareto front) can be confirmed in subsequent steps. First spreading the powder of choice on the processing table is simulated to obtain the packing density as a function of table displacement. The packing density defines the maximum allowable vertical distortion during build. Should the distortion module indicate a higher distortion for a certain layer, interaction of the coater arm with the build can be expected. The user can then either exclude this set of parameters and choose the next combination from the pareto front, decide to use soft coater arm or optimize the support structure.The work piece thermal history can be computed using the 3D printer control file. The outcome can be either used in a more accurate distortion and residual stress models or to assess the metallurgical evolution of the work piece. These options are currently in research mode and have not been fully integrated in ESI-AM.The Distortion and Residual Stress module is used to confirm manufacturability, work piece orientation, support structure and to quantify final distortion and as-built residual stresses. The user can fine tune the outcome by choosing different processing parameters, changing orientation, deposition strategy or adapting the support structure utilized to stabilize the build.Figure 1: ESI-AM Integrated Computational Material Engineering for Additive ManufacturingOnce manufacturability and final distortion are confirmed to be acceptable, the material quality and the probability of build defects as well as surface finish can be assessed in melting module. The heat source powder interaction is resolved to simulation material melting, solidification and evaporation. The model is a three phase model resolving solid, liquid and gaseous phases allowing quantitative determination of porosity and surface roughness.4.Modules4.1.Data BaseESI-AM modules require a lot of details about material behavior including data about phase changes (melting, evaporation), surface tension, optical behavior and material strength. Setting up models is much quicker when referencing the data base.The data base, a repository of material properties, manages thermos-physical as well thermos-mechanical properties of metallic alloys. It includes template materials such as stainless steel 316L, Inconel 718 as Ti6Al4V. The contents can be used directly, they can be edited based on user experience or measurements and can be freely extended to include more materials.Figure 2: ESI-AM data baseIt is important to note that material properties play a central role in prediction quality. It is therefore recommended to continuously revise and update the content based on supplier data sheets, new literature and new measurements.The upcoming version of ESI-AM is to include additional information pertaining to powder, 3D printers and combinations of material – powder – printer and processing parameters. This solution will enable users to manage their printing knowledge and use it as a foundation for ESI-AM.4.2.PrescanThe prescan module considers four process parameters: Power, scan speed, hatch spacing and table displacement when identifying a process window that enables printing of dense material at the highest possible build rate.The model input include material properties, powder size distribution, bounds of printer performance (e.g. heat source powder ranges from 10 to 400 W). The multi-objective optimization problem delivers a pareto front of possible process parameter combinations that fulfil the optimization objectives.The user can choose one of the points on the pareto front and proceed to qualifying the work piece and material quality achieved using more detailed analysis.4.3.Powder SpreadingThe powder size distribution and the table displacement are used to simulate the powder spreading process. The prototype assumes a rigid coater arm by default, but other geometries such as a roller can be defined in advanced mode.Results are analyzed statistically to provide powder bed characteristics across the modelling processing table. Typical results include the powder packing density, change in powder size distribution and the geometric distribution of powder particles in the powder bed.Using the packing density material consolidation and the space available above the processed material can be estimated. This information is used in the distortion module to assess manufacturability. Assessing the powder size distribution on the processing table enables assessment of powder recyclability as a function of the process parameters investigated. The powder bed geometry is utilized in melting models to resolve the heat source interaction with the powder and quantify as-built material quality.4.4.Distortion & Residual StressThe Distortion and Residual Stress module operates at work piece length scale. It automatically creates a computational grid, set suitable clamping conditions for the base plate and supports component analysis during build, at the end of the build process, release of the build plate from the machine and cutting the work piece from the base plate.Input includes the CAD model, the support structure if defined and deposition strategy.Both simplified and detailed modelling are supported allowing the use the flexibility of running quick trend analysis as well as quantitative analysis resolving deposition strategy. The elastoplastic material behavior is considered.During the build process manufacturability is assessed by comparing the maximum vertical distortion of each layer with the space between build surface and coater arm predicted by the Spreading module.If the support structure is not provided, the tool will create supports based on part orientation.The final work piece shape and as-built residual stresses are calculated for different stages: End of build, release or base plate and cut off of work piece from base plate.Figure 3: Example Distortion and Residual Stress Model - Courtesy Bomabrdier Aerostructures & Engineering Services (AMAZE Project) 4.5.MeltingThe Melting module resolves the heat source powder interaction to resolve powder melting, evaporation and solidification. The solidified material can be analyzed to determine the expect porosity and surface finish.Figure 4: Example of processing material showing splatter, porosity cloud and crack.The utilization of melting models is expected to be required during the printer / powder qualification stage. Once the qualification is concluded, the process window and corresponding porosity and surface finish data will be available in the data base for referencing during future analysis of new work pieces and homogenization algorithms assessing part performance.5.Additional FeaturesESI-AM is foreseen to have several automated post processing tools that provide quantitative results. These tools are supported with interactive tools that allow the user to analyze the data separately.The current prototype does not have its own graphical environment. Other tools from the ESI portfolio are used accordingly.5.1.PreprocessingTwo automated grid generators are used to create computational grids for the Distortion and Residual Stress (CFD-VisCART) and Melting modules (CFD-GEOM). The grid generation is automatic and should not require the user to interact directly with the grid generator. If this should be needed, it is recommended to contact ESI-AM support team.5.2.Post ProcessingESI Visual environment is used to analyze Distortion and Residual Stress results. The user is able to visualized the build process and the evolution of distortion and stresses. Other variable can be calculated including plastic strain, tresca stresses and strains.CFD-VIEW is used to visualize Spreading and Melting results. Automated video creation tools are available as well as quantitative analysis tools based on CFD-VIEW>。

IA系统FCP270说明书B0700ARREV C I/ASeries ? SystemField Control Processor 270 (FCP270)User’s GuideMay 31, 2007Invensys, Foxboro, FoxCom, Spec 200, SPECTRUM and I/A Series are trademarks of Invensys plc, its subsidiaries, and affiliates. All other brand names may be trademarks of their respective owners.Copyright 2004-2007 Invensys Systems,Inc.All rights reservedContentsFigures (vii)Tables (ix)Preface (xi)Who This Book Is For (xi)What You Should Know (xi)Revision Information (xi)Reference Documents (xi)Glossary of Terms (xiii)1. Introduction (1)Overview (1)Features (2)Fault-Tolerance (3)Traditional Redundant Systems (3)FCP270 Fault-tolerant Operation (3)On-Line Image Update (4)FCP270 Network Configuration (4)Network Path Switching (4)Splitter/Combiner (4)Fieldbus Expansion Module 100 (FEM100) (6)I/O Communications (6)Communication to 200 Series Fieldbus Modules (7)Communication to Y-Module Fieldbus Modules (7)Time Synchronization (7)Overview (7)Internal Source Time Synchronization (7)External Source Time Synchronization (8)FCP270 Sizing Constraints (8)FCP270 Supported Block Processing Cycles (8)2. Installing the Field Control Processor 270 (9)Overview (9)System Definition (9)Installing a Single or Primary FCP270 Module (10)Installing a Shadow FCP270 Module (13)iiiB0700AR – Rev C ContentsCabling a Single (Non-Fault-Tolerant) FCP270 Module (14)Cabling a Fault-Tolerant FCP270 Module Pair (14)Boot-Up Sequence (18)Case 1 – Rebooting a Commissioned FCP270 (18)Case 2 – Connecting an FCP270 with the Same Letterbug (19)Case 3 – Connecting an FCP270 with a New Letterbug (19)Case 4 – Connecting a Shadow Module with Same Software Image (19) Case 5 – Connecting a Shadow Module with Different Software Image (19) Cabling Y-Module FBMs to an FCP270 Baseplate (20)Remote Fieldbus Extension, Cable Connections (20)3. Configuration Information (27)System Definition (27)System Definition Procedure (27)Integrated Control Configuration (28)Off-Line Control Configuration (29)On-Line Control Configuration (30)Available I/A Series System Control Blocks (30)4. System Management (31)Overview (31)Operating Status (31)System Management Displays for the FCP270 (31)Equipment Information Display for FCP270 (31)Configuration Information Display for FCP270 (36)Equipment Change Display for FCP270 (37)Reboot Station Procedure (39)Image Update Procedure for a Non-Fault-Tolerant FCP270 (39) Image Update Procedure for a Fault-Tolerant FCP270 (40)On-line Image Update Procedure for a Fault-Tolerant FCP270 (41) System Management Displays – Primary ECB (FBM0) (42) Equipment Information Display for Primary ECB (FBM0) (43) Equipment Change Display for Primary ECB (FBM0) (46) Overview of Fieldbus Switching Mode (48)Using the Fieldbus Switching Options (49)Overview of the General Download (49)Downloading all FBM Images (49)On-Line Diagnostics (PIO) Display for Primary ECB (FBM0) (50) 5. Troubleshooting (53)Overview (53)LED Indicators, Reset Button, and Infrared Ports (53) Operational Status LED Indicators (55)FCP270 Troubleshooting (55)ivContents B0700AR – Rev C Using the Operational Status LEDs (56) Red off, Green off (56)Red on, Green off (56)Red on, Green on (57)Cycling Red, Red/Green (57)Red off, Green on (57)Using the Ethernet Tx and Rx/Link Status LEDs (58)Using the Fieldbus Tx and RX Status LEDs (58)Fault-Tolerant FCP270 Troubleshooting Addenda (58) Replacing a Failed Module (59)Memory Dumps and Last Gasp Messages (59)Last Gasp Messages (59)Memory Dumps (60)Diagnostics (61)Start-Up Diagnostics (61)Error Recovery Local Diagnostics (62)Error Recovery Cooperative Diagnostics (62)Appendix A. Upgrade Diagrams (63)Index (73)vB0700AR – Rev C Contents viFigures1-1.Typical FCP270 Network Configuration (Simplified) (5)2-1.FCP270 Module Installation (Typical) (10)2-2.Cabling the FCP270 Fault-tolerant Controllers (Two-Position Baseplate Example) (15) 2-3.Cabling the FCP270 Fault-tolerant Controllers (Four-Position Baseplate Example) (16) 2-4.Cabling Y-Module FBMs to an FCP270 Baseplate (21)2-5.TCA Cable Connection to 268 Kbps Fieldbus Splitter/Terminator (22)2-6.TCA Termination Block Assembly Mounting (22)2-7.TCA Termination Block Removal (23)2-8.Remote Redundant Fieldbus Cabling (FCP270 End) (24)2-9.Example of Extending Fieldbus in Two Directions from FCP270 (25)3-1.Typical Control Scheme Using an FCP270 and 200 Series FBMs (29)4-1.Equipment Information Display for FCP270 – Typical (1 of 2) (32)4-2.Equipment Information Display for FCP270 – Typical (2 of 2) (32)4-3.Configuration Information Display for FCP270 (36)4-4.Equipment Change Display for FCP270 (37)4-5.REBOOT STATION Dialogue Box – Fault-Tolerant FCP270 (39)4-6.IMAGE UPDATE Dialogue Box – Non-Fault-Tolerant FCP270 (40)4-7.IMAGE UPDATE Dialogue Box – Fault-Tolerant FCP270 (41)4-8.ON-LINE IMAGE UPDATE Dialogue Box – Fault-Tolerant FCP270 (41)4-9.REBOOT STATION Dialogue Box – Fault-Tolerant FCP270 (42)4-10.Equipment Information Display for Primary ECB (FBM0) – Typical (1 of 2) (43)4-11.Equipment Information Display for Primary ECB (FBM0) – Typical (2 of 2) (44)4-12.Equipment Change Display for Primary ECB (FBM0) (47)4-13.On-line Diagnostics Display for Primary ECB (FBM0) (50)5-1.FCP270 LED Indicators, Reset Button, and Infrared Port (54)A-1.Equipment Replacement Order for CP60-to-FCP270 Conversions (64)A-2.Converting CP10/30/40 with Local I/O to FCP270s (65)A-3.Converting CP60 with DCM10E to FCP270 (66)A-4.Converting CP60 with DCM10Ef to FCP270 (67)A-5.Converting CP60 with DCM10Ef with Fiber Optic Hub to FCP270 (68)A-6.Converting CP60 with FBI10E and 100Series FBMs to FCP270s (69)A-7.Converting CP60 with 200Series DIN Rail Mounted Equipment to FCP270 (70)A-8.Converting Micro-I/A Station to FCP270 (71)A-9.Converting AW51/AW70 to FCP270s (72)viiB0700AR – Rev C Figures viiiTables2-1.Cables for Connecting the FCP270 or Splitter/Combiners to the Ethernet Switches ..14 2-2.Cables for Connecting the Splitter/Combiners to theFCP270 (18)4-1.Equipment Information Display Fields for FCP270 (33)4-2.Configuration Information Display Fields for FCP270 (36)4-3.Equipment Change Display Fields for FCP270 (37)4-4.Equipment Information Display Fields for Primary ECB (FBM0) (44)4-5.Equipment Change Display Fields for Primary ECB (FBM0) (47)4-6.Equipment Change Display Fields for Primary ECB (FBM0) (50)5-1.FCP270 LED Indicators, Reset Button, and Infrared Communication Ports (54)5-2.FCP270 Operational Status LEDs (55)ixB0700AR – Rev C Tables xPrefaceThis document describes how to configure and install the Field Control Processor 270 (FCP270) in an I/A Series? system with The MESH control network. It also describes how the FCP270 functions in The MESH control network. Finally, it describes how to troubleshoot system prob-lems.Who This Book Is ForThis book is intended for the use of process control engineers and operators, instrument and maintenance engineers, and other qualified and authorized personnel involved in installing, configuring and maintaining the FCP270 for operation in the I/A Series MESH control network. What You Should KnowPrior to using this book, you should be generally familiar with the I/A Series system, and with DIN Rail Mounted FBM Subsystem User’s Guide (B0400FA). Detailed information relating to the various I/A Series software and hardware elements is found in the reference documents listed below.Revision InformationFor Revision C of this document, the following changes were made to this document:Chapter1 “Introduction”Added the Fieldbus Expansion Module 100 (FEM100) to the introduction and “Fieldbus Expansion Module 100 (FEM100)” on page6.Added “FCP270 Supported Block Processing Cycles” on page8.Chapter5 “T roubleshooting”Added “Memory Dumps” on page60.Appendix A “Upgrade Diagrams”Added the Appendix.Reference DocumentsThe following documents provide additional and related information.For information about defining control blocks and compounds, refer to:Integrated Control Block Descriptions (B0193AX)Integrated Control Software Concepts (B0700AG)For information about configuring and managing the FCP270, refer to:CP 270 On-Line Upgrade (B0700BY)System Definition: A Step-by-Step Procedure (B0193WQ)xiB0700AR – Rev C PrefacexiiLetterbug Configurator User’s Guide (B0700AY)Integrated Control Configurator (B0193AV)I/A Series Configuration Component (IACC) User’s Guide (B0400BP)Process Operations and Displays (B0700BN)System Management Displays (B0193JC)Field Control Processor 270 (FCP270) Sizing Guidelines and Excel Workbook (B0700AV).For information about associated DIN Fieldbus Modules and the Fieldbus Expansion Module 100, refer to:DIN Rail Mounted FBM Subsystem User’s Guide (B0400FA).For information about Y-module Fieldbus Modules, refer to:I/A Series System Equipment Installation (B0193AC).For information about system power and earthing (grounding), refer to:Power, Earthing (Grounding), EMC and CE Compliance (B0700AU)For information about supported migration products, refer to:SPECTRUM Migration Integrator User's Guide (B0193RC)SPEC 200 Control Integrator User's Guide (B0193RD)SPEC 200 MICRO Control Integrator User's Guide (B0193RR)SPEC 200 CCM Control Integrator User's Guide (B0193VU)DCS Fieldbus Modules for Westinghouse WDPF Systems User's Guide (B0400BA).DCS Fieldbus Modules for APACS+ Automation Systems User’s Guide (B0700BK)DCS Fieldbus Modules for Honeywell TDC 2000 Systems User’s Guide (B0193VL)DCS Fieldbus Modules for Honeywell TDC 3000 Systems User’s Guide (B0193YW)DCS Fieldbus Modules for Bailey NET90 and INFI90 Systems User’s Guide (B0193XG)DCS Fieldbus Modules for Fisher PROVOX Series 10 Systems User’s Guide (B0193WV)DCS Fieldbus Modules for Fisher PROVOX Series 20 Systems User’s Guide (B0193YV)DCS Fieldbus Modules for Fisher PROVOX Controller Series Systems User’s Guide (B0400AR)For information about The MESH control network, refer to:The MESH Control Network Architecture Guide (B0700AZ)Most of these documents are available on the I/A Series Electronic Documentation CD-ROM (K0173TQ or K0173WT). The latest revisions of each document are also available through our Global Product Support at /doc/0f6c5e5a6edb6f1aff001fa3.html .Preface B0700AR – Rev C Glossary of TermsThe following terminology, used throughout this user’s guide, relates to the FCP270 controller and associated equipment.Name MeaningAI Analog inputAPACS+?Siemens? Process Automation SystemAW Application WorkstationBPC Block Processing CycleCP60Control Processor 60CSD Control Strategy DiagramDIN DIN is a non-governmental organization established to promote thedevelopment of standardization and related activities in Germany.ECB Equipment Control BlockEEPROM Electrically erasable programmable read-only memoryFBM I/A Series system Fieldbus ModuleFCM Fieldbus Communication ModuleFCP270Field Control Processor 270FDSI Foreign Device Systems IntegratorFEM Fieldbus Expansion ModuleGMT Greenwich Meridian Time (GMT) is an international time standard GPS Global positioning systemHART HART Field Communications Protocol is a standard for digitallyenhanced 4 to 20 mA smart instrument communication.HDLC High-level Data Link Control protocol - Master/Slave Protocol used ontop of several physical layers for FBM communicationI/A Series?Intelligent Automation SeriesIACC I/A Series Configuration ComponentICC Integrated Control ConfiguratorIR InfraredLC Connector for fiber optic cable connection to the ZCP270 orsplitter/combinerLED Light-emitting diodeLetterbug Alphanumeric string that the user defines to identify a station in anI/A Series control system.Letterbug Configurator Handheld device for setting, modifying and reading the controllerletterbug and reading controller status informationMMF Multimode fiber cableMTK Master TimekeeperMT-RJ Connector for fiber optic cable connection to Ethernet switchesxiiiB0700AR – Rev C PrefaceName MeaningROM Read only memoryRx ReceiveSMDH System Management Display Handler, the user interface for equipmentstatus and change actionsSOE Sequence of EventsSTK Slave TimekeeperSysDEF System DefinitionTDA T ransient Data AnalyzerTDR T ransient Data RecorderThe MESH The MESH Control NetworkTx T ransmitUTC Universal Coordinated Timexiv1. IntroductionThis chapter describes the main features, fault-tolerant operation, network configuration, and time synchronization of the Field Control Processor 270. OverviewThe Field Control Processor 270 (FCP270) is an optionally fault-tolerant station that performs regulatory, logic, timing, and sequential control together with connected Fieldbus Modules (FBMs) and other process interface devices. It also performs data acquisition (via the FBMs and/or other devices) and alarm detection and notification.The FCP270 supports process control via the standard 2 Mbps HDLC fieldbus for the following products:All DIN rail mounted 200 Series FBMs (FBM201, FBM202, and so forth). The FCP270 supports up to 32modules itself, and supports up to 128 modules whenused with a Fieldbus Expansion Module 100 (FEM100); based on the loading ofFCP270. Refer to Field Control Processor 270 (FCP270) Sizing Guidelines and ExcelWorkbook (B0700AV).Field Device Systems Integrator (FDSI) modules (FBM230/231/232/233)DCS Fieldbus Modules for APACS+ Automation SystemsDCS Fieldbus Modules for Westinghouse WPDF SystemsThe FCP270 also supports process control via the optional 268 Kbps HDLC fieldbus for the fol-lowing products:All Y-module FBMs, also known as 100 Series FBMs (FBM01, FBM02, and so forth) – up to 64 modules, via an extended fieldbusFieldbus Cluster I/O via FBP10 fieldbus processor moduleFoxboro Hydrostatic Interface Unit (HIU)Foxboro Mass FlowmeterFoxboro Panel Display StationsSPECTRUM Migration IntegratorsSPEC 200 Control IntegratorsSPEC 200 MICRO Control IntegratorsSPEC 200 CCM Control IntegratorsDCS Fieldbus Modules for Honeywell TDC 2000 and TDC 300 SystemsDCS Fieldbus Modules for Bailey Net90 and Infi90 SystemsDCS Fieldbus Modules for Fisher’s PROVOX Series 10, Series 20, and Controller Series Systems.1B0700AR – Rev C 1. Introduction2NOTEThe FCP270 supports either the 2 Mbps or the 268 Kbps HDLC fieldbus, but not both at the same time. For the maximum number of devices supported by each fieldbus, refer to the device specific Product Specification Sheets.FeaturesThe FCP270 provides the following new features and improvements.A direct 100 Mbps Ethernet fiber connection to the The MESH control network for high speed data communication that is immune to electromagnetic interference overthe distance of the fiber cable.A fault-tolerant option that delivers improved availability and safety using unique, dual controller comparison on all outgoing messages.On-line image update replaces the executable image (operating system) of a running, fault-tolerant FCP270 controller with a newer image without having to shut downthe equipment being controlled by the FCP270.Hardened, field-mounted control (100 Mbps Ethernet fiber controller, 2Mbps fieldbus, Series200 DIN rail mounted FBMs, Termination Assemblies, and FPS400-24 power supply). The new configuration eliminates the need for a rackroom (you only need a control room and a field enclosure).Supports up to 128 Series200 DIN rail mounted FBMs, or equivalent modules (depending on the sizing guidelines), when connected to an optional Fieldbus Expan-sion Module 100 (FEM100).Connection to Ethernet or serial devices via FDSIs which allows for new device interfaces. The FDSIs include FBM230, FBM231, FBM232, andFBM233.Optional global positioning system allows external time synchronization.Sequence of Events (SOE) are optionally time stamped at the FBM (200 Series FBMs only) to 1 ms1 accuracy throughout the system for later analysis of events.Optional T ransient Data Recorder (TDR) allows 10 ms sampling of analog data for later analysis of events using T ransient Data Analyzer (TDA). TDR data is optionallytime stamped (200 Series FBMs only) to 1 ms1 accuracy.Infrared interface to the I/A Series system Letterbug Configurator allows setting and reading the controller letterbug.Memory resident image for fast station reboot. Reboot time is less than 10 seconds.Improved controller performance. Block executions/second is 10,000 for the FCP270 compared to 3400 for the CP60.Up to 4000 blocks can be configured for the FCP270 (or fault-tolerant FCP270 pair) A scalable license lets you start small with a full-featured control system. You can grow your system over time.Alarm enhancements to the function blocks: re-alarming on changes to alarm priority, re-alarming based on time, alarm suppression based on time.1. Time stamping has 1 ms accuracy only when using the optional GPS external time synchronization.1. Introduction B0700AR – Rev C3Foundation Fieldbus, FoxCom?, HART, Profibus, and Modbus FBMs are supported.Y-module FBMs and DCS migration FBMs are supported.For enhanced reliability during maintenance operations, a recessed reset button, located at the front of the module, allows you to manually reset the module withoutremoving it from the baseplate.Fault-ToleranceFault-tolerant operation is unique with Foxboro control processors and uses patented technology. Fault-tolerance is superior to redundancy because outgoing messages from the fault-tolerant controller must be identical in both modules for a message to transmit successfully.The following sections describe the difference between redundancy and fault-tolerance from an applications standpoint and how fault-tolerance is implemented using the FCP270.Traditional Redundant SystemsT raditionally, the goal of improved availability through redundancy has been achieved using a second, or “backup” controller. Redundant systems that use a secondary controller may have the following shortcomings:Problems with the primary controller are not detected or are only detected after a number of potentially bad messages have been transmitted to the field. Secondary controllers may not use the latest “good” data when they take over from the primary controller. Configuring the secondary controller correctly can result insubstantial system downtime.Secondary controllers may have health problems that are hard to determine after they have been idle for a long period of time.T o remove these shortcomings from critical systems, the FCP270 uses a patented method of fault-tolerance. FCP270 Fault-tolerant OperationThe fault-tolerant version of the FCP270 consists of two modules operating in parallel, with two separate connections to the The MESH control network. The two control processor modules, married together as a fault-tolerant pair, provide continuous operation of the unit in the event of virtually any hardware failure occurring within one module of the pair.Both modules receive and process information simultaneously, and faults are detected by the modules themselves. One of the significant methods of fault detection is comparison ofcommunication messages at the module’s external interface. Upon detection of a fault, thecommunication message is aborted, and self-diagnostics are run by both modules to determine which module is defective. The non-defective module then assumes control without affecting normal system operations. An aborted control network communication message is then sent by the non-defective module via the retry mechanisms of the communications protocol. An aborted fieldbus communication message is retried on the next BPC. For more information, see “Diagnos-tics” on page 61.B0700AR – Rev C 1. Introduction On-Line Image UpdateFor a fault-tolerant FCP270 controller, on-line image update replaces the executable image (oper-ating system) of a running FCP270 with a newer image without having to shut down the equip-ment being controlled by the FCP270. This feature allows you to take advantage of product enhancements while interrupting process control for only 1.5 seconds, approximately.Because the FCP270 contains its executable image in internal flash memory, and has sufficient RAM to hold a new executable image at the same time, on-line image updates are now much easier to perform.FCP270 Network ConfigurationThe MESH control network uses redundant communication paths to enhance control reliability.Figure1-1 shows a simplified FCP270 network configuration using redundant Ethernet fiber switches, 100Mbps fiber cables, splitter/combiners, FCP270 controllers (fault-tolerant), and redundant 2 Mbps fieldbus and redundant 268 Kbps fieldbus. Multiple FCP270s can share the same redundant switch. The FCP270 uses 100 Mbps Ethernet fiber connections to communicate with I/A Seriesworkstations connected to Ethernet switches in The MESH. For information about general guidelines and specific requirements for designing The MESH above the FCP270 level, including site planning and network installation guidelines, see The MESH Control Network Architecture Guide (B0700AZ).For instructions on installing and cabling the FCP270 in the non-fault-tolerant and fault-tolerant configurations, see Chapter2 “Installing the Field ControlProcessor 270”.Network Path SwitchingThe MESH control network provides redundant communications paths. The MESH architecture and the software in the controller allow it to switch paths when a communications path fails or when replacing modules.Each FCP270 has two station MAC addresses and two IP addresses, which are not embedded in hardware. When you replace the controller, the new controller acquires its station MAC and IP addresses from the system configuration file based on its assigned letterbug. Software on the FCP270 then selects the network path that is used to transmit outbound communication. Splitter/CombinerFault-tolerant FCP270s require a pair of splitter/combiners, one to connect to each of The MESH control network paths (see Figure1-1). Non-fault-tolerant FCP270s can optionally use splitter/combiners to provide for a future upgrade to fault-tolerant operation. The splitter/combiner has three 100 Mbps connections: one to the primary module of a fault-tolerant pair, one to the shadow module, and one to The MESH. One splitter/combiner in the pair is con-nected to one Ethernet switch, the other is connected to another Ethernet switch.The splitter/combiner is connected via fiber optic cables. Inbound traffic from The MESH is split and sent to each FCP270 controller. Output traffic is sent from the primary module, which can be either physical module, to The MESH.41. Introduction B0700AR – Rev C5Figure 1-1. Typical FCP270 Network Configuration (Simplified)* Splitter/Combiner.Note: For additional sizing information, refer to Field Control Processor 270 (FCP270) SizingThe MESH Control NetworkGuidelines (B0700AV).Up to 64 Y -module FBMs per FCP270 or FCP270 Pair (See Note below and “Overview” on page 1)。