Verilog24小时计数器

- 格式:docx

- 大小:305.23 KB

- 文档页数:7

课程设计任务书学生姓名:罗序森专业班级:通信gj1101______ 指导教师:胡辑伟工作单位:____信息工程学院_____ 题目: 通信工程应用技术课设——FPGA一、设计任务与要求设计一个具有系统时间设置和带闹钟功能的24小时计时器中的应用。

电子钟要求如下:(1)计时功能:4位LED数字时钟对当前时间的小时和分钟进行显示,显示的最长时间为23小时59分。

(2)设置并显示新的闹钟时间:用户先按“set”键,再用数字键“0”~“9”输入时间,然后按“alarm”键确认。

在正常计时显示状态下,用户直接按下“alarm”键,则已设置的闹钟时间显示在显示屏上。

(3)设置新的计时器时间:用户先按“set”键,再用数字键“0”-“9”输入新的时间,然后按“time”键确认。

在输入过程中;输入的数字在显示屏上从右到左依次显示。

例如,用户要设置新的时间12:00,则按顺序输入“l”,“2”,“0”,“0”键,与之对应,显示屏上依次显示的信息为:“1”,“12”;“120”,“1200”。

如果用户在输入任意几个数字后较长时间内,例如5秒,没有按任何键,则计时器恢复到正常的计时显示状态。

(4)闹钟功能:如果当前时间与设置的闹钟时间相同,则扬声器发出蜂鸣声;三.时间安排:指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (2)Abstract ................................................... 错误!未定义书签。

1 绪言 ..................................................... 错误!未定义书签。

1.1 课题的研究背景及意义................................ 错误!未定义书签。

1.2 闹钟系统的.......................................... 错误!未定义书签。

verilog实现简易24⼩时计数器1.顶层数码管显⽰模块`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company:// Engineer://// Create Date: 18:57:45 08/18/2019// Design Name:// Module Name: dynamic_seg_top// Project Name:// Target Devices:// Tool versions:// Description: //实现简易时钟计数功能//// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://module dynamc_seg_top//---------------------<端⼝声明>---------------------------------------(input clk_50MHZ , //时钟,50Mhzinput rst_n , //复位,低电平有效output reg [ 7:0] seg_sel , //数码管位选output reg [ 7:0] seg_data //数码管段选,即内容显⽰);//---------------------<信号定义>---------------------------------------wire clk_1KHZ ;reg [3:0] data_tmp ;reg [7:0] cnt ;wire [23:0] data ;//----------------------------------------------------------------------// 1k分频例化,扫描⼀个数码管时间为1ms//----------------------------------------------------------------------CLK_DIV #(.width(16),.cnt(50_000))uut(.clk_50MHZ(clk_50MHZ),.rst_n(rst_n),.clk_out(clk_1KHZ));//======================================================================////时,分,秒计数例化////======================================================================clock_cntclk_cnt_uut(.clk_50MHZ(clk_50MHZ),.rst_n(rst_n),.data(data));//----------------------------------------------------------------------// 数码管扫描,8位循环扫描,频率为1k//----------------------------------------------------------------------always @(posedge clk_1KHZ or negedge rst_n)beginif(!rst_n)seg_sel <= 8'b0111_1111;else if(seg_sel==8'b1111_1110)seg_sel <= 8'b0111_1111;elseseg_sel <= ~(~seg_sel>>1);end//----------------------------------------------------------------------// 位选,不同计数对应不同位选编码,也对应分割的不同数据//----------------------------------------------------------------------always @(*)begincase(seg_sel)8'b0111_1111: data_tmp = data[ 3: 0] ; // 位18'b1011_1111: data_tmp = data[ 7: 4] ; // 位28'b1101_1111: data_tmp = 4'ha ; // 位38'b1110_1111: data_tmp = data[11:8] ; // 位48'b1111_0111: data_tmp = data[15:12] ; // 位58'b1111_1011: data_tmp = 4'hb ; // 位68'b1111_1101: data_tmp = data[19:16] ; // 位78'b1111_1110: data_tmp = data[23:20] ; // 位8default: data_tmp = 4'b0000 ;endcaseend//----------------------------------------------------------------------// 段选,将不同分割数据进⾏段选编码,实验平台为2个4位⼀体共阳数码管//----------------------------------------------------------------------always @(*)begincase(data_tmp)4'h0: seg_data = 9'hc0;4'h1: seg_data = 9'hf9;4'h2: seg_data = 9'ha4;4'h3: seg_data = 9'hb0;4'h4: seg_data = 9'h99;4'h5: seg_data = 9'h92;4'h6: seg_data = 9'h82;4'h7: seg_data = 9'hf8;4'h8: seg_data = 9'h80;4'h9: seg_data = 9'h90;4'ha: seg_data = 9'hbf;//4'hb: seg_data = 9'hbf;//第三位和第六位显⽰时钟的分隔线default:seg_data = 9'hc0;endcaseendendmodule2.时分秒计数模块`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company:// Engineer://// Create Date: 19:51:36 02/25/2020// Design Name:// Module Name: clock_cnt// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments:////////////////////////////////////////////////////////////////////////////////////module clock_cnt(input clk_50MHZ,input rst_n,output [23:0]data);reg [7:0] second ;//时钟“秒”reg [7:0] minute ;//时钟“分”reg [7:0] hour ;//时钟“⼩时”wire clk_1HZ ;//----------------------------------------------------------------------//-- 例化计数分频产⽣1HZ时钟//----------------------------------------------------------------------CLK_DIV #(.width(28),.cnt(50_000_000))uut(.clk_50MHZ(clk_50MHZ),.rst_n(rst_n),.clk_out(clk_1HZ));//----------------------------------------------------------------------//-- 秒计数,从0-59计数,1秒加⼀,到59清零//----------------------------------------------------------------------always @(posedge clk_1HZ or negedge rst_n)beginif(!rst_n)second<=8'd0;else if (second[3:0]==4'd9)beginsecond[3:0]<=8'd0;if(second[7:4]==4'd5)second[7:4]<=4'd0;elsesecond[7:4]<=second[7:4]+4'd1;endelsesecond[3:0]<=second[3:0]+4'd1;end//----------------------------------------------------------------------//-- 分计数,从0-59计数,1分钟加⼀,到59清零//----------------------------------------------------------------------always @(posedge clk_1HZ or negedge rst_n)beginif(!rst_n)minute<=8'd0;else if ((second[3:0]==4'd9)&(second[7:4]==4'd5))beginif(minute[3:0]==4'd9)beginminute[3:0] <=4'd0;if(minute[7:4]==4'd5)minute[7:4] <=4'd0;elseminute[7:4] <=minute[7:4]+4'd1;endelsebeginminute[3:0]<=minute[3:0]+4'd1;endendelseminute<=minute;end//----------------------------------------------------------------------//-- ⼩时计数,从0-23计数,1⼩时加⼀,到23清零//----------------------------------------------------------------------always @(posedge clk_1HZ or negedge rst_n)beginif(!rst_n)hour<=8'd0;else if ((second[3:0]==4'd9)&(second[7:4]==4'd5)&(minute[3:0]==4'd9)&(minute[7:4]==4'd5)) beginif(hour[7:4]==4'd2)beginif(hour[3:0]==4'd3)beginhour[3:0] <=4'd0;hour[7:4]<=4'd0;endelsebeginhour[7:4]<=hour[7:4];hour[3:0] <=hour[3:0]+4'd1;endendelsebeginif(hour[3:0]==4'd9)beginhour[3:0] <=4'd0;hour[7:4] <=hour[7:4]+4'd1;endelsebeginhour[3:0] <=hour[3:0]+4'd1;hour[7:4] <=hour[7:4];endendendelsehour<=hour;endassign data[3:0] =second [3:0];//将“秒”的个位数送到数码管第⼀位assign data[7:4] =second [7:4];//将“秒”的⼗位数送到数码管第⼆位assign data[11:8] =minute [3:0];//将“分“的个位数送到数码管第四位assign data[15:12] =minute [7:4];//将”分”的⼗位数送到数码管第五位assign data[19:16] =hour [3:0];//将“时“的个位数送到数码管第七位assign data[23:20] =hour [7:4];//将”时”的个位数送到数码管第⼋位endmodule3.任意时钟分频模块`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company:// Engineer://// Create Date: 18:54:40 02/25/2020// Design Name:// Module Name: CLK_DIV// Project Name:// Target Devices:// Tool versions:// Description: //任意时钟分频模块//// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments:////////////////////////////////////////////////////////////////////////////////////module CLK_DIV #(parameter width = 28,parameter cnt = 50_000_000)(input clk_50MHZ,input rst_n ,output clk_out);reg [width-1:0] cnt_p;reg cnt_n;reg clk_p;reg clk_n;//上升沿计数器,实现0-49_999_999计数always@(posedge clk_50MHZ or negedge rst_n)beginif(!rst_n)cnt_p <= 1'b0;else if(cnt_p == (cnt-1))cnt_p <= 1'b0;elsecnt_p <= cnt_p + 1'b1;end//上升沿触发时钟分频,实现1HZ时钟输出always@(posedge clk_50MHZ or negedge rst_n)beginif(!rst_n)clk_p<=1'b0;else if(cnt_p<(cnt>>1))clk_p<=1'b0;elseclk_p<=1'b1;endalways@(negedge clk_50MHZ or negedge rst_n)beginif(!rst_n)cnt_n <= 1'b0;else if(cnt_n == (cnt-1))cnt_n <= 1'b0;elsecnt_n <= cnt_n + 1'b1;endalways@(negedge clk_50MHZ or negedge rst_n)beginif(!rst_n)clk_n<=1'b0;else if(cnt_n<(cnt>>1))clk_n<=1'b0;elseclk_n<=1'b1;endwire clk1=clk_50MHZ; //当分频系数为1时,输出时钟wire clk2=clk_p; //当分频系数为偶数时,输出等于clk_pwire clk3=clk_p&clk_n;//当分频系数为奇数时,输出等于clk_p&clk_n assign clk_out=(cnt==1)?clk1:(cnt[0]? clk2:clk3);endmodule4.时分秒仿真testbench⽂件`timescale 100ps / 1ps////////////////////////////////////////////////////////////////////////////////// Company:// Engineer://// Create Date: 22:18:22 02/25/2020// Design Name: clock_cnt// Module Name: C:/mydesign/dybamic_seg1/clk_tb.v// Project Name: dybamic_seg// Target Device:// Tool versions:// Description://// Verilog Test Fixture created by ISE for module: clock_cnt//// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://////////////////////////////////////////////////////////////////////////////////module clk_tb;// Inputsreg clk_50MHZ;reg rst_n;// Outputswire [23:0] data;// Instantiate the Unit Under Test (UUT)clock_cnt uut (.clk_50MHZ(clk_50MHZ),.rst_n(rst_n),.data(data));initial begin// Initialize Inputsclk_50MHZ = 0;rst_n = 0;// Wait 100 ns for global reset to finish#10;rst_n = 1;#10;// Add stimulus hereendalways #1 clk_50MHZ=~clk_50MHZ;endmodule5.显⽰模块仿真testbench⽂件`timescale 1ns / 1ps////////////////////////////////////////////////////////////////////////////////// Company:// Engineer://// Create Date: 15:11:16 02/26/2020// Design Name: dynamc_seg_top// Module Name: C:/mydesign/dybamic_seg1/dy_segtb.v// Project Name: dybamic_seg// Target Device:// Tool versions:// Description://// Verilog Test Fixture created by ISE for module: dynamc_seg_top //// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://////////////////////////////////////////////////////////////////////////////////module dy_segtb;// Inputsreg clk_50MHZ;reg rst_n;// Outputswire [7:0] seg_sel;wire [7:0] seg_data;// Instantiate the Unit Under Test (UUT)dynamc_seg_top uut (.clk_50MHZ(clk_50MHZ),.rst_n(rst_n),.seg_sel(seg_sel),.seg_data(seg_data));initial begin// Initialize Inputsclk_50MHZ = 0;rst_n = 0;// Wait 100 ns for global reset to finish#10;rst_n = 1;#10;// Add stimulus hereendalways #1 clk_50MHZ=~clk_50MHZ;endmodule。

Verilog计数器设计原理1. 介绍计数器是一种常见的数字电路,用于计算和记录事件的数量。

在数字系统中,计数器通常用于生成时钟信号、控制状态机、实现频率分频等应用。

Verilog是一种硬件描述语言,可以用于设计和仿真数字电路。

本文将详细介绍与Verilog计数器设计相关的基本原理。

2. 计数器的基本概念计数器是一种能够在输入脉冲信号的作用下进行累加或递减操作的数字电路。

它通常由触发器和逻辑门组成,触发器用于存储和传递数据,逻辑门用于控制触发器的工作状态。

2.1 同步计数器同步计数器是通过时钟信号来同步各个触发器的状态转换,以实现数据的累加或递减操作。

它包含一个时钟输入端(CLK)和一个复位输入端(RST)。

2.1.1 同步正向计数器同步正向计数器是最简单的同步计数器之一,它能够在每个上升沿时钟信号到达时进行累加操作。

2.1.1.1 原理同步正向计数器由多个触发器和逻辑门组成,其中每个触发器都有一个时钟输入端和一个复位输入端。

当时钟信号的上升沿到达时,触发器的状态将根据输入信号进行更新。

具体的原理如下:1.初始化:将计数器的初始值设置为0。

2.时钟边沿检测:当时钟信号的上升沿到达时,进入下一步操作。

3.累加操作:根据触发器的当前状态进行累加操作。

如果触发器为0,则变为1;如果触发器为1,则变为0。

4.检测溢出:如果最高位触发器由1变为0,则表示计数溢出,需要将其他低位触发器进行进位操作。

2.1.1.2 Verilog代码示例以下是一个4位同步正向计数器的Verilog代码示例:module synchronous_counter(input wire clk,input wire rst,output wire [3:0] count);reg [3:0] count;always @(posedge clk or posedge rst)beginif (rst)count <= 4'b0000;elsecount <= count + 1;endendmodule2.1.2 同步递减计数器同步递减计数器是同步正向计数器的一种扩展,它能够在每个上升沿时钟信号到达时进行递减操作。

设计一个具有时、分、秒计时的电子钟,按24 小时计时。

要求: (1)数字钟的时间用六位数码管分别显示时、分、秒; (2)用两个控制键,对数字钟分别进行分、时校正;( 3)用Verilog HDL 语言设计,用Modelsim 软件做功能仿真,用Quartus II 综合。

(4)将设计代码和仿真代码写在作业本上。

module countersmh(out,sel,dp,clock_128,clear,corr_min,corr_hour);input clock_128,clear,corr_min,corr_hour;output [6:0] out;output [2:0] sel;output dp;reg [6:0] out;reg [2:0] sel;reg [3:0] cnt_sl,cnt_sh,cnt_ml,cnt_mh,cnt_hl,cnt_hh,count;reg [15:0] fenping;wire clock_1=fenping[1];always @(posedge clock_128 or negedge clear)beginif (!clear)fenping <= 16'b0;elsefenping <= fenping + 1;end//cnt_slalways@(posedge clock_1 or negedge clear)beginif(!clear)cnt_sl<=4'b0;else if (cnt_sl == 9) cnt_sl<=4'b0;elsecnt_sl<=cnt_sl+1;end//cnt_shalways@(posedge clock_1 or negedge clear)beginif(!clear)cnt_sh<=4'b0;else if (cnt_sh == 5 && cnt_sl == 9)cnt_sh<=4'b0;else if (cnt_sl == 9)cnt_sh<=cnt_sh+1; elsecnt_sh <= cnt_sh; end //cnt_ml always@(posedge clock_1 or negedge clear) begin if(!clear) cnt_ml<=4'b0;else if (cnt_sh == 5 && cnt_sl == 9 && cnt_ml == 9) cnt_ml<=4'b0;else if (corr_min == 0)begin if(cnt_ml == 9)cnt_ml<=4'b0;else cnt_ml<=cnt_ml+1;endelse if (cnt_sh == 5 && cnt_sl == 9) cnt_ml<=cnt_ml+1;elsecnt_ml <= cnt_ml; end//cnt_mhalways@(posedge clock_1 or negedge clear) begin if(!clear)cnt_mh<=4'b0;else if (cnt_sh == 5 && cnt_sl == 9 && cnt_ml == 9 && cnt_mh == 5) cnt_mh<=4'b0;else if (corr_min == 0)beginif(cnt_mh == 5 && cnt_ml == 9) cnt_mh<=4'b0;else if(cnt_ml == 9) cnt_mh<=cnt_mh+1;else cnt_mh <= cnt_mh;endelse if (cnt_sh == 5 && cnt_sl == 9 && cnt_ml == 9) cnt_mh<=cnt_mh+1;elsecnt_mh <= cnt_mh;end//cnt_hlalways@(posedge clock_1 or negedge clear)beginif(!clear) cnt_hl<=4'b0;else if ( cnt_hh == 2 && cnt_hl == 3 && cnt_mh == 5 && cnt_ml == 9 && cnt_sh == 5 && cnt_sl == 9 )cnt_hl<=4'b0;else if ( cnt_hl == 9 && cnt_mh == 5 && cnt_ml == 9 && cnt_sh == 5 && cnt_sl == 9 ) cnt_hl<=4'b0;else if (corr_hour == 0)beginif(cnt_hh == 2 && cnt_hl == 3)cnt_hl<=4'b0;else if(cnt_hl == 9)cnt_hl<=4'b0;endelse if (cnt_mh == 5 && cnt_ml == 9 && cnt_sh == 5 && cnt_sl == 9) cnt_hl<=cnt_hl+1;elsecnt_hl <= cnt_hl;end//cnt_hhalways@(posedge clock_1 or negedge clear)beginif(!clear)cnt_hh<=4'b0;else if ( cnt_hh == 2 && cnt_hl == 3 && cnt_mh == 5 && cnt_ml == 9 && cnt_sh == 5 && cnt_sl == 9 ) cnt_hh<=4'b0;else if (corr_hour == 0)beginif(cnt_hh == 2 && cnt_hl == 3) cnt_hh<=4'b0;else if (cnt_hl == 9)cnt_hh <= cnt_hh+1;else cnt_hh <= cnt_hh;endelse if (cnt_hl == 9 && cnt_mh == 5 && cnt_ml == 9 && cnt_sh == 5 && cnt_sl == 9) cnt_hh<=cnt_hh+1;elsecnt_hh <= cnt_hh;end //selalways@(posedge clock_128 or negedge clear ) beginif(!clear)sel<=0;else if(sel==3'b101)sel <= 3'b000;elsesel <= sel+1;endalways @(sel)begincase(sel)3'b000: count=cnt_hh;3'b001: count=cnt_hl;3'b010: count=cnt_mh;3'b011: count=cnt_ml;3'b100: count=cnt_sh;default: count=0;endcaseend//decoderwire dp;assign dp = (sel == 3'b011 || sel == 3'b001)?1'b1:1'b0;always @(count)begincase(count)4'd0: out=7'b011_1111;4'd1: out=7'b000_0110;4'd2: out=7'b101_1011;4'd3: out=7'b100_1111;4'd4: out=7'b110_0110;4'd5: out=7'b110_1101;4'd6: out=7'b111_1101;4'd7: out=7'b000_0111;4'd8: out=7'b111_1111;4'd9: out=7'b110_1111;default: out=7'b000_0000;endcaseendendmodule'timescale 1ns/1ns'in clude"./co un tersmh.v"module test;reg Clock_128,Clear,Corr_min,Corr_hour;wire [6:0] Out;wire [2:0] Sel;wire Dp;initialbeginClock_128=0;Clear=1;Corr_min=1;Corr_hour=1;#50 Clear=0;#50 Clear=1;#1000 Corr_min=0;#1000 Corr_min=1;#100 Corr_hour=0;#1000 Corr_hour=1;endalways #2 Clock_128=~Clock_128;countersmhm(.out(Out),.sel(Sel),.dp(Dp),.clock_128(Clock_128),.clear(Clear),.corr_min(Corr_min),.corr_ho ur(Corr_hour));endmodule。

实验报告2019 -2020 学年第2学期开课单位电子信息学院适用年级、专业2017级电子信息科学与技术Z 课程名称FPGA技术及应用-课内实验主讲教师课程序号BS6222003X3-03课程代码BS6222003X3实验名称计时器和倒计时的系统设计实验学时2学时学号姓名实验五计时器和倒计时的系统设计①掌握用Verilog HDL文本输入法设计计时电路的方法,并通过电路仿真和硬件验证,进一步了解计时器的功能和特性。

②掌握用Verilog HDL文本输入法设计倒计时电路的方法,并通过电路仿真和硬件验证,进一步了解倒计时电路的功能和特性。

二、实验原理1.计时器24小时计时器的电路框图如图8.1所示。

图8.1 24小时计时器的电路框图24小时计时器由2个60进制加计数器和1个24进制加计数器构成,输入CLK为1HZ(秒)的时钟,经过60进制加计数后产生1分钟的进位时钟信号,再经过60进制加计数后产生1小时的进位时钟信号送给24进制加计数器进行加计数,当加计数到达23:59:59后,再来-一个秒脉冲,产生时的进位输出。

将两个60进制加计数器和一个24进制加计数器的输出送数码管显示,得到计时器的显示结果。

其中,秒脉冲由EDA实调仪上的20MHz晶振分频得到。

2.倒计时器24小时倒计时器的电路框图如图8.2所示。

图8.2 24 小时倒计时器的电路框图24小时倒计时器由2个60进制减计故器和1个24进制减计数器构成,输入CLK为1Hz(秒)的时钟,经过60进制减计数后产生1分钟的借位时钟信号,再经过60进制减计数后产生I小时的借位时钟信号送给24进制减计数器进行减计数,当减计数到达00:00:00后,产生时的借位输出,同时24小时倒计时器停止倒计时,并发出提醒信号。

将两个60进制减计数器和一个24进制减计数器的输出送数码管显示,得到倒计时的显示结果。

其中,秒脉冲由EDA实训仪上的20MHz晶振分频得到。

三、实验设备①EDA实调仪1台。

数码管计时(verilog)学习笔记代码分析:`timescale 1ns / 1ps///////////////////////////////////////////////////////////////////// ///////////module seg7(clk,rst_n,ds_stcp,ds_shcp,ds_data);input clk; //25M输入时钟信号input rst_n; //复位信号输入,低有效output ds_stcp; //74HC595的并行时钟输入,上升沿将当前串行输入数据并行输出output ds_shcp; //74HC595的串行时钟输入,上升沿锁存当前串行输入数据output ds_data; //74HC595的串行数据输入//数码管显示 0~F 对应段选输出parameter SEG_NUM0 = 8'h3f,//c0,SEG_NUM1 = 8'h06,//f9,SEG_NUM2 = 8'h5b,//a4,SEG_NUM3 = 8'h4f,//b0,SEG_NUM4 = 8'h66,//99,SEG_NUM5 = 8'h6d,//92,SEG_NUM6 = 8'h7d,//82,SEG_NUM7 = 8'h07,//F8,SEG_NUM8 = 8'h7f,//80,SEG_NUM9 = 8'h6f,//90,SEG_NUMA = 8'h77,//88,SEG_NUMB = 8'h7c,//83,SEG_NUMC = 8'h39,//c6,SEG_NUMD = 8'h5e,//a1,SEG_NUME = 8'h79,//86,SEG_NUMF = 8'h71;//8e;//数码管位选 0~3 对应输出parameter SEG_WE0 = 4'b1110,SEG_WE1 = 4'b1101,SEG_WE2 = 4'b1011,SEG_WE3 = 4'b0111;//递增数据产生单元reg[24:0] cnt_1s; //1s计数器,0-24999999(时钟频率25MHz)reg[15:0] dis_data; //数码管显示数据,16位//1s定时计数always @(posedge clk or negedge rst_n)if(!rst_n) cnt_1s <= 25'd0;else if(cnt_1s == 25'd24_999_999) cnt_1s <= 25'd0;else cnt_1s <= cnt_1s+1'b1;wire done_1s = (cnt_1s == 25'd24_999_999); //1s定时到标志位,高有效一个时钟周期//显示数据每秒递增always @(posedge clk or negedge rst_n)if(!rst_n) dis_data <= 16'd0;else if(done_1s) dis_data <= dis_data+1'b1;//-------------------------------------------------//分时显示数据控制单元reg[7:0] seg_num; //当前显示数据reg[7:0] seg_duan; //7段数码管段选信号(包括小数点为8段)reg[3:0] seg_wei; //7段数码管位选信号reg[7:0] cnt_4; //分时计数器,每个clk自加“1”always @(posedge clk or negedge rst_n)if(!rst_n) cnt_4 <= 8'd0;else cnt_4 <= cnt_4+1'b1;//显示数据,1s内seg_num不变,直到dis_data变化此信号才发生变化always @(posedge clk or negedge rst_n)if(!rst_n) seg_num <= 8'h00;elsecase(cnt_4[7:6])2'b00: seg_num <= dis_data[3:0]; //00h~3fh2'b01: seg_num <= dis_data[7:4]; //40h~7fh2'b10: seg_num <= dis_data[11:8]; //80h~bfh2'b11: seg_num <= dis_data[15:12]; //c0h~ffhdefault: seg_num <= 8'h00;endcase//段选数据译码,由于seg_num在1s内保持不变,故此信号1s内保持不变always @(posedge clk or negedge rst_n)if(!rst_n) seg_duan <= 8'h00;elsecase(seg_num)4'h0: seg_duan <= SEG_NUM0;4'h1: seg_duan <= SEG_NUM1;4'h2: seg_duan <= SEG_NUM2;4'h3: seg_duan <= SEG_NUM3;4'h4: seg_duan <= SEG_NUM4;4'h5: seg_duan <= SEG_NUM5;4'h6: seg_duan <= SEG_NUM6;4'h7: seg_duan <= SEG_NUM7;4'h8: seg_duan <= SEG_NUM8;4'h9: seg_duan <= SEG_NUM9;4'ha: seg_duan <= SEG_NUMA;4'hb: seg_duan <= SEG_NUMB;4'hc: seg_duan <= SEG_NUMC;4'hd: seg_duan <= SEG_NUMD;4'he: seg_duan <= SEG_NUME;4'hf: seg_duan <= SEG_NUMF;default: ;endcase//位选译码,2的8次方时间分成4段,每段时间内选通一个7段led管always @ (cnt_4[7:6])case(cnt_4[7:6])2'b00: seg_wei <= SEG_WE0;2'b01: seg_wei <= SEG_WE1;2'b10: seg_wei <= SEG_WE2;2'b11: seg_wei <= SEG_WE3;default: seg_wei <= 4'b1111;endcase//-------------------------------------------------//74HC95驱动译码reg ds_stcpr; //74HC595的并行时钟输入,上升沿将当前串行输入数据并行输出reg ds_shcpr; //74HC595的串行时钟输入,上升沿锁存当前串行输入数据reg ds_datar; //74HC595的串行数据输入//串行移位时钟产生,在cnt_4所处区间上时,即每隔20H个clk周期,ds_shcpr 每个clk都会翻转一次,而剩下20H个周期保持之前的状态不变,在cnt_4的计时大周期内发生4次always @(posedge clk or negedge rst_n)if(!rst_n) ds_shcpr <= 1'b0;else if((cnt_4 > 8'h02 && cnt_4 <= 8'h22) || (cnt_4 > 8'h42 && cnt_4 <= 8'h62)|| (cnt_4 > 8'h82 && cnt_4 <= 8'ha2) || (cnt_4 > 8'hc2 && cnt_4 <= 8'he2))ds_shcpr <= ~ds_shcpr;//串行移位数据产生,在cnt_4的02—22期间,每个clk都将seg_duan,seg_wei 的1位送给ds_datar,在一个cnt_4计时大周期内总共送4次always @(posedge clk or negedge rst_n)if(!rst_n) ds_datar <= 1'b0;elsecase(cnt_4)8'h02,8'h42,8'h82,8'hc2: ds_datar <= seg_duan[7];8'h04,8'h44,8'h84,8'hc4: ds_datar <= seg_duan[6];8'h06,8'h46,8'h86,8'hc6: ds_datar <= seg_duan[5];8'h08,8'h48,8'h88,8'hc8: ds_datar <= seg_duan[4];8'h0a,8'h4a,8'h8a,8'hca: ds_datar <= seg_duan[3];8'h0c,8'h4c,8'h8c,8'hcc: ds_datar <= seg_duan[2];8'h0e,8'h4e,8'h8e,8'hce: ds_datar <= seg_duan[1];8'h10,8'h50,8'h90,8'hd0: ds_datar <= seg_duan[0];8'h1a,8'h5a,8'h9a,8'hda: ds_datar <= seg_wei[0];8'h1c,8'h5c,8'h9c,8'hdc: ds_datar <= seg_wei[1];8'h1e,8'h5e,8'h9e,8'hde: ds_datar <= seg_wei[2];8'h20,8'h60,8'ha0,8'he0: ds_datar <= seg_wei[3];default: ;endcase//并行移位时钟产生,即在23,63,a3,e3时刻置“1”,而在02,42,82,c2时刻置“0”always @(posedge clk or negedge rst_n)if(!rst_n) ds_stcpr <= 1'b0;else if((cnt_4 == 8'h02) || (cnt_4 == 8'h42) || (cnt_4 == 8'h82) || (cnt_4 == 8'hc2)) ds_stcpr <= 1'b0;else if((cnt_4 == 8'h23) || (cnt_4 == 8'h63) || (cnt_4 == 8'ha3) || (cnt_4 == 8'he3)) ds_stcpr <= 1'b1;wire ds_stcp = ds_stcpr;wire ds_shcp = ds_shcpr;wire ds_data = ds_datar;endmodule-------------------------------------------------------------------------------------------------------------------1.74HC595相关2.模块相关信号定义:2.程序设计相关①最开始参数化定义了SEG_NUM0—SEG_NUMF,对应7段数码管的显示,再定义了SEG_WE0—SEG_WE3,对应数码管的位选②时钟为25MHz,用cnt_1s完成1s计时,1s计时到了,使done_1s信号有效,并使dis_data每秒“+1”③之后的代码参考下面这张图来说明Cnt_4每个clk周期计数,其总的计数周期可以分为4段时间,分时扫描显示数据和位选信号。

24小时数字时钟的VHDL程序2012-4-20 23:24阅读(37)先编辑一个74LS161十进制计数器:Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity court161 isport( clk,CTT,CTP,LD,CR:in std_logic;D3,D2,D1,D0: in std_logic;Q:out std_logic_VECTOR(3 DOWNTO 0);Co: out std_logic);end court161;architecture court of court161 issignal a,b,c: std_logic ;signal D,CQI:std_logic_vector(3 downto 0);beginD<=D3&D2&D1&D0;a<=CTT and CTP;b<=(not (CQI(3) and CQI(0)))and LD; process(clk,CTT,CTP,LD,CR,D3,D2,D1,D0) beginif a='1' thenif clk'event and clk='1' thenif b='0' then CQI<=D;else CQI<=CQI+1;end if;end if;if CQI=9 then c<='1';else c<='0';end if;end if;if clk'event and clk='1' then Co<=c;end if;if CR='0' then CQI<="0000";end if;Q<=CQI ;end process; end ;再编辑一个7段数码管(共阴极)显示驱动程序:Library ieee;Use ieee.std_logic_1164.all;Entity QDLED7 isPORT(DATA:IN STD_LOGIC_VECTOR(3 DOWNTO 0);a,b,c,d,e,f,g:out std_logic);end QDLED7;Architecture LED of QDLED7 issignal y: STD_LOGIC_VECTOR(6 DOWNTO 0); beginprocess(DATA)begincase DATA iswhen "0000"=>y<="1111110" ;when "0001"=>y<="0110000" ;when "0010"=>y<="1101101" ;when "0011"=>y<="1111001" ;when "0100"=>y<="0110011" ;when "0101"=>y<="1011011" ;when "0110"=>y<="1011111" ;when "0111"=>y<="1110000" ;when "1000"=>y<="1111111" ;when "1001"=>y<="1111011" ;when others=>null;end case;a<=y(6);b<=y(5);c<=y(4);d<=y(3);e<=y(2);f<=y(1);g<=y(0);end process;end;然后在编写时钟描述语言Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity timer24 isport(CP,CR:IN STD_LOGIC;AS0,BS0,CS0,DS0,ES0,FS0,GS0,AS1,BS1,CS1,DS1,ES1,FS1 ,GS1:OUT STD_LOGIC;AM0,BM0,CM0,DM0,EM0,FM0,GM0,AM1,BM1,CM1,DM1,EM1,FM1 ,GM1:OUT STD_LOGIC;AH0,BH0,CH0,DH0,EH0,FH0,GH0,AH1,BH1,CH1,DH1,EH1,FH1 ,GH1:OUT STD_LOGIC);END TIMER24;architecture TIMER of TIMER24 issignal H1,H0,M1,M0,S1,S0:std_logic_vector(3 downto 0); SIGNAL C0,C1,C2,C3,C4,C5: std_logic ;COMPONENT court161 IS port( clk,CTT,CTP,LD,CR:in std_logic;D3,D2,D1,D0:in std_logic;Q:out std_logic_VECTOR(3 DOWNTO 0);Co: out std_logic);end COMPONENT;COMPONENT QDLED7 ISPORT(DATA:IN STD_LOGIC_VECTOR(3 DOWNTO 0);a,b,c,d,e,f,g:out std_logic);end COMPONENT;beginU0:court161 PORTMAP(CP,'1','1','1',CR,'0','0','0','0',S0,C0);U1:court161 PORT MAP(C0,'1','1',(NOT(S1(2)ANDS1(0))),CR,'0','0','0','0',S1,C1);U2:court161 PORT MAP((NOT(S1(2)ANDS1(0))),'1','1','1',CR,'0','0','0','0',M0,C2);U3:court161 PORT MAP(C2,'1','1',(NOT(M1(2)ANDM1(0))),CR,'0','0','0','0',M1,C3);U4:court161 PORT MAP(C3,'1','1','1',(CR AND(NOT(H1(1) AND H0(2)))),'0','0','0','0',H0,C4);U5:court161 PORT MAP(C4,'1','1',(NOT H1(1)),(CRAND(NOT(H1(1) AND H0(2)))),'0','0','0','0',H1,C5);U6:QDLED7 PORT MAP(S0,AS0,BS0,CS0,DS0,ES0,FS0,GS0);U7:QDLED7 PORT MAP(S1,AS1,BS1,CS1,DS1,ES1,FS1,GS1);U8:QDLED7 PORT MAP(M0,AM0,BM0,CM0,DM0,EM0,FM0,GM0);U9:QDLED7 PORT MAP(M1,AM1,BM1,CM1,DM1,EM1,FM1,GM1);U10:QDLED7 PORT MAP(H0,AH0,BH0,CH0,DH0,EH0,FH0,GH0);U11:QDLED7 PORT MAP(H1,AH1,BH1,CH1,DH1,EH1,FH1,GH1);END;接上数码管,和脉冲信号发生器,必要时要分频,分成脉冲周期为1秒的脉冲周期方可。

24小时计时器设计摘要:使用硬件描述语言VHDL进行编程,设计六十进制和二十四进制计数器,利用原理图输入设计方法,使用两片六十进制计数器和一片二十四进制计数器,设计出了一个24小时计时器系统。

使用QuartusII软件进行编译,时序仿真,来验证该系统的正确性。

整个系统设计简单,使用方便,具有24小时计时显示功能,可以分别对时,分,秒进行校正。

关键词:VHDL 计数器24小时计时器目录1.设计背景 (1)2.设计方案 (1)2.1.六十进制计数器设计 (2)2.2.二十四进制计数器设计 (3)3.方案实施 (5)4.仿真结果 (6)5.参考文献 (7)1.设计背景随着EDA技术的发展和应用领域的扩大,EDA技术在电子信息、通信、自动控制及计算机应用等领域的重要性日益突出。

基于EDA技术的数字系统设计,一般可以再单片PLD实现,具有功能强、功耗低,体积小、可靠性高等特点,成为当今数字系统设计的主流。

此次EDA课程大作业,我的设计课题是24小时计时器系统设计,根据要求使用平时所学VHDL语言进行编程和原理图输入设计方法来完成。

报告书主要包括设计背景、设计方案、方案实施、仿真波形。

设计方案主要介绍了我对于设计课题的大致设计思路,之后各个部分将会详细介绍设计组成及程序。

2.设计方案24小时计时器的原理图如图2.1所示。

它由两片六十进制计时器和一片二十四进制计数器构成,输入CLK为1Hz的时钟,经过60分频后产生1分钟时钟信号,再经过60分频后,产生1小时的时钟信号,最后进行24分频,得到1天的脉冲送COUT输出。

将两个60分频和一个24分频的输出送7段数码管,得到24小时的计时显示结果。

图2.1 24小时计时器的原理图图2.1中的CLK是1Hz时钟输入端;RST是复位输入端,高电平有效;JM、JF和JS分别是校秒、校分和校时的输入端,下将沿有效;QM[7..0]、QF[7..0]和QS[7..0]分别是秒、分、时的计时输出端;COUT是“天”脉冲输出端。

use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fenpin isport(clk40M: in std_logic;clk1hz,clk1000hz: out std_logic);end fenpin;architecture one of fenpin issignal a: integer range 0 to 19999 :=0;signal clk1000,clk1: std_logic;beginprocess(clk40M)beginif rising_edge(clk40M) thenif a=19999 thenclk1000<=not clk1000; a<=0;else a<=a+1;end if ; end if;end process;clk1000hz<=clk1000;process(clk1000)variable a1: integer range 0 to 499 :=0;beginif rising_edge(clk1000) thenif a1=499 then clk1<=not clk1;a1:=0;else a1:=a1+1;end if;end if;end process;clk1hz<=clk1;end one;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport(clk1hz: in std_logic;mg,ms: buffer std_logic_vector(3 downto 0));architecture two of cnt10 issignal jw: std_logic;signal mg1,ms1,mg2,ms2: std_logic_vector(3 downto 0);signal q1,q2,q3,q4,q5,q6: std_logic_vector(3 downto 0):="0000";beginprocess(clk1hz)beginq5<=q3;if q5="0000" then q5<="0001" ;q1<="0000";elsif rising_edge(clk1hz) thenif q1="1001" then jw<='1';q1<="0000";else q1<=q1+1;jw<='0';end if;end if;end process;mg1<=q1;process(jw)beginq6<=q4;if q6="0000" then q6<="0001" ;q2<="0000";elsif rising_edge(jw)then q2<=q2+1;end if;end process;ms1<=q2;process(mg1,ms1)beginmg2<=mg1;ms2<=ms1;if mg2="0100" and ms2="0010" thenmg2<="0000";ms2<="0000";q3<="0000";q4<="0000";elsemg2<=mg1;ms2<=ms1;q3<="0001";q4<="0001";end if;end process;mg<=mg2;ms<=ms2;end two;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity decode isport(clk1000hz: in std_logic;mg,ms: in std_logic_vector(3 downto 0);atog: out std_logic_vector(6 downto 0);sel: out std_logic_vector(1 downto 0));end decode;architecture four of decode issignal q: std_logic_vector(0 to 3) ;signal count : integer range 0 to 1:=0;beginprocess(clk1000hz)beginif rising_edge(clk1000hz) thencount<=count+1;end if;end process;process(count,mg,ms)beginif count=0 then q<=mg;sel<="01";elsif count=1 then q<=ms;sel<="10";end if;end process;process(q)begincase q iswhen "0000" => atog<="0111111";when "0001" => atog<="0000110";when "0010" => atog<="1011011";when "0011" => atog<="1001111";when "0100" => atog<="1100110";when "0101" => atog<="1101101";when "0110" => atog<="1111101";when "0111" => atog<="0000111";when "1000" => atog<="1111111";when "1001" => atog<="1101111";when others => atog<=null;end case;end process;end four;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity aa isport(clk40M: in std_logic;atog: out std_logic_vector(6 downto 0);sel: out std_logic_vector(1 downto 0));end aa;architecture one of aa iscomponent fenpin isport(clk40M: in std_logic;clk1000hz,clk1hz: out std_logic);end component;component cnt10 isport(clk1hz: in std_logic;mg,ms: out std_logic_vector(3 downto 0));end component;component decode isport(clk1000hz: in std_logic;mg,ms: in std_logic_vector(3 downto 0);atog: out std_logic_vector(6 downto 0);sel: out std_logic_vector(1 downto 0));end component;signal clk1000,clk1:std_logic;signal mg1,ms1:std_logic_vector(3 downto 0); signal cc: integer;beginU1: fenpin port map(clk40M,clk1000,clk1);U2: cnt10 port map(clk1,mg1,ms1);U3: decode port map(clk1000,mg1,ms1,atog,sel);end one;。

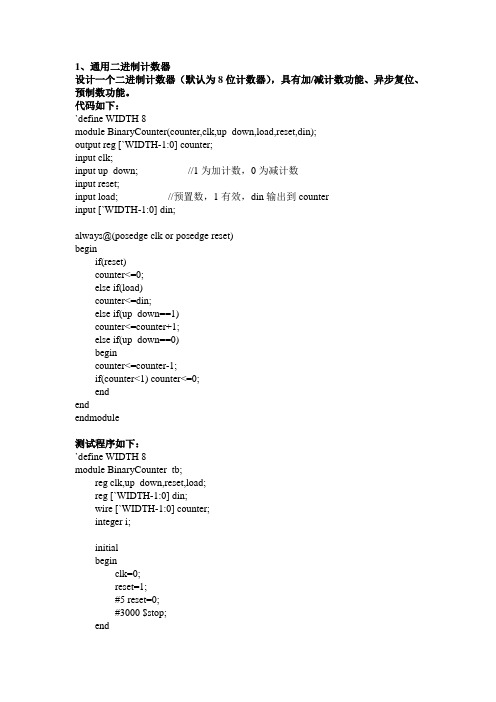

1、通用二进制计数器设计一个二进制计数器(默认为8位计数器),具有加/减计数功能、异步复位、预制数功能。

代码如下:`define WIDTH 8module BinaryCounter(counter,clk,up_down,load,reset,din);output reg [`WIDTH-1:0] counter;input clk;input up_down; //1为加计数,0为减计数input reset;input load; //预置数,1有效,din输出到counterinput [`WIDTH-1:0] din;always@(posedge clk or posedge reset)beginif(reset)counter<=0;else if(load)counter<=din;else if(up_down==1)counter<=counter+1;else if(up_down==0)begincounter<=counter-1;if(counter<1) counter<=0;endendendmodule测试程序如下:`define WIDTH 8module BinaryCounter_tb;reg clk,up_down,reset,load;reg [`WIDTH-1:0] din;wire [`WIDTH-1:0] counter;integer i;initialbeginclk=0;reset=1;#5 reset=0;#3000 $stop;endalways #5 clk=~clk;/*always@(posedge clk)beginup_down={$random}%2;load={$random}%2;din={$random}%256;end*/initialbegin#5;for(i=0;i<256;i=i+3)begindin=i;#10;endendinitialbeginup_down=1;load=1;#20 load=0;#30 load=1;#30 load=0;endalways #200 up_down=~up_down;BinaryCounter bcounter(.counter(counter),.clk(clk),.up_down(up_down),.load(load),.reset(reset),.din(din));endmodule波形图如下:图1 二进制计数器波形图图2 二进制计数器波形图从图像可看出,20s-50s为加计数,50s-80s时load=1,执行置数功能,80s-200s 时up_down=1,为加计数,200s-280s时up_down=0,为减计数。

二十四小时计时器目录1.项目任务描述 (1)2.24小时计时器流程图 (1)3.24小时计时器源程序 (2)3.1六十进制计数器 (2)3.2二十四进制计数器 (2)4.24小时计时器波形仿真 (3)4.1六十进制计数器波形图 (3)4.2二十四进制计数器波形图 (3)24小时计时器的设计1.项目任务描述:二十四小时计时器是利用特定原理来测定时间的装置,本设计运用Quartus ii 9.0软件以编程的方式实现计时器,计时器由两片六十进制计数器和一片二十四进制计数器构成,输入CLK为1HZ(秒)的时钟,经过60分频后产生1分钟时钟信号,再经过60分频后,产生1小时的时钟信号,最后进行24分频,得到1天的脉冲送COUT输出。

将两个60分频和一个24分频的输出,得到24小时的计时结果,并用数码管显示,所以利用软件分别对二十四进制计数器和六十进制计数器分别编程,编程顺利通过后再通过Quartus ii 9.0软件的波形仿真对二十四进制计数器和六十进制计数器分别仿真,仿真编译通过通过调试得到正确结果,进而验证计数器的正确性,其中60计数器运用ModelSim仿真。

2.24小时计时器流程图:3.24小时计时器源程序:本项目是通过两块六十进制的计数器,和一个二十四进制计数器构成的,所以在这里我们将单独给出二十四进制计数器和六十进制计数器。

运用Quartus ii 9.0软件分别对六十进制计数器和二十四进制计数器编程,调试直到程序编译成功。

3.1六十进制计数器源程序:module cnt60(clk,clrn,j,q,cout);input clk,clrn,j;output reg[7:0]q;output reg cout;always@(posedge clk^j or negedge clrn)beginif(~clrn) q=0;else beginif(q==’h59) q=0;else q=q+1;if(q[3:0]==’h a) beginq[3:0]=0;q[7:4]=q[7:4]+1;endif(q==’h59) cout=1;else cout=0;endendendmodule3.2二十四进制计数器源程序:module cnt24(clk,clrn,j,q,cout);input clk,clrn,j;output reg[7:0]q;output reg cout;always@(posedge clk^j or negedge clrn)beginif(~clrn) q=0;else beginif(q==’h23) q=0;else q=q+1;if(q[3:0]==’ha) beginq[3:0]=0;q[7:4]=q[7:4]+1;endif(q==’h23) cout=1;else cout=0;endendendmodule4.24小时计时器波形仿真运用Quartus ii 9.0软件仿真出二十四进制计数器和六十进制计数器的波形,通过波形的仿真可以看到波形的具体变化,实现六十进制计数器(如图4.1)和二十四进制计数器(如图4.2)的计数功能。

目录1 设计任务及要求 (1)2 总体设计分析 (1)3 各模块设计 (2)3.1 数字钟主体部分 (2)3.1.1小时计数器 (2)3.1.2 分、秒计数器 (3)3.2 分频部分 (4)3.3 秒表模块 (5)3.4 闹钟模块 (5)3.5 时间设置模块 (7)3.6 报时模块 (7)3.7 控制显示模块 (8)3.8 顶层模块 (11)4 总结 (11)4.1 本次作业遇到的问题 (11)4.2 建议和总结 (12)附件 (13)1 设计任务及要求本次大作业的要求为设计一个多功能数字钟,其具体要求如下:1.有基础的实时数字钟显示功能,即时、分、秒的正常显示模式,并且在此基础上增加上,下午显示。

2.手动校准。

按动方式键,将电路置于校时状态,则计时电路可用手动方式校准,每按一下校时键,时计数器加1;按动方式键,将电路置于校分状态,以同样方式手动校分。

3.整点报时,仿中央人民广播电台整点报时信号,从59分50秒起每隔2秒发出一次低音“嘟”信号(信号鸣叫持续时间1S,间隙时间1S)连续5次,到达整点(00分00秒时),发一次高音“哒”信号(信号持续时间1S)。

4.闹时功能,按动方式键,使电路工作于预置状态,此时显示器与时钟脱开,而与预置计数器相连,利用前面手动校时,校分方式进行预置,预置后回到正常模式。

当计时计至预置的时间时,扬声器发出闹铃信号,时间为半分钟,闹铃信号可以用开关“止闹”,按下此开关后,闹铃声立刻中止,正常情况下应将此开关释放,否则无闹时作用。

5.秒表功能。

按start键开始计秒,按stop键停止计秒并保持显示数不变,直到复位信号加入。

2 总体设计分析设计的总体部分按照要求可以分为基本的数字时钟显示、手动校准、整点报时、闹钟功能和秒表功能5大部分。

其总体设计框图如下:图1 总体设计框图其中整点报时跟闹钟部分要求不同频率的声响,所以需要加入分频器模块将输入的1kHZ的分频产生500HZ及1HZ的方波信号,其中1HZ的信号对应1S 的周期,可以用作时钟秒的显示及秒表部分。

学生实验报告实验课名称:VHDL硬件描述语言实验项目名称:同步计数器专业名称:电子科学与技术班级:32050801学号:3205080127学生姓名:柯斌教师姓名:程鸿亮2010年_11月 13日组别_____________________同组同学李福来实验日期2011年11月13日实验室名称成绩_____一、实验名称:同步计数器二、实验目的与要求:设计一个同步二十四进制计数器,理解触发器同步计数工作机制,掌握同步触发控制的VHDL描述方法以及异步清零的描述方法。

三、实验内容:通过VHDL编程,实现一个同步二十四进制计数器,要求有1个异步清零端、1个时钟脉冲输入、驱动7段数码管显示的个位和十位信号端四、实验条件:1. WindowsXP操作系统2. QuartusII EDA开发系统3. 杭州康芯SOPC硬件开发平台五、实验原理:clk:计数时钟脉冲输入;clr:异步清零信号,高电平有效,此时输出显示为“00”ten[6..0]:十位数的7段数码管显示输出;one[6..0]:个位数的7段数码管显示输出;六、源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;-------------------------------entity cnt24 isport(clk,clr:in std_logic;ten,one:out std_logic_vector(6 downto 0);co:out std_logic);end entity cnt24;---------------------------architecture str of cnt24 issignal ten_temp,one_temp:std_logic_vector(3 downto 0); begin--------------------------process(clr,clk) isbeginif (clr='1') thenten_temp<="0000";one_temp<="0000";co<='0';elsif (clk'event and clk='1') thenif(one_temp="0011" and ten_temp="0010") then one_temp<="0000";ten_temp<="0000";co<='1';elsif(one_temp="1001") thenten_temp<=ten_temp+1;one_temp<="0000";elseone_temp<=one_temp+1;end if;end if;end process;----------------------------process(one_temp) isbegincase one_temp iswhen"0000"=>one<="1111110";when"0001"=>one<="0110000";when"0010"=>one<="1101101";when"0011"=>one<="1111001";when"0100"=>one<="0110011";when"0101"=>one<="1011011";when"0110"=>one<="1011111";when"0111"=>one<="1110000";when"1000"=>one<="1111111";when"1001"=>one<="1111011";when others=>one<="1111110"; end case;end process;---------------------------------- process(ten_temp)isbegincase ten_temp iswhen"0000"=>ten<="0000000";when"0001"=>ten<="0110000";when"0010"=>ten<="1101101";when others=>ten<="1111110"; end case;end process;-----------------------------------end str;七、实验结果与分析:1,RTL仿真如下:2,时序仿真结果:3,代码下载后的部分实例:计数到23时,无进位。

数字钟的设计一、任务要求:(1)设计一个数字钟。

(2)具有时,分,秒计数显示功能,以24小时循环计时。

(3)具有清零,调节小时、分钟功能。

(4)具有整点报时功能,整LED灯花样显示。

二、系统框图:三、模块说明(含程序代码)1. 秒模块程序清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity SECOND isport(clk,clr:in std_logic;----时钟/清零信号sec1,sec0:out std_logic_vector(3 downto 0);----秒高位/低位co:out std_logic);-------输出/进位信号end SECOND;architecture SEC of SECOND isbeginprocess(clk,clr)variable cnt1,cnt0:std_logic_vector(3 downto 0);---计数beginif clr='1' then----当ckr为1时,高低位均为0cnt1:="0000";cnt0:="0000";elsif clk'event and clk='1' thenif cnt1="0101" and cnt0="1000" then----当记数为58(实际是经过59个记时脉冲)co<='1';----进位cnt0:="1001";----低位为9elsif cnt0<"1001" then----小于9时cnt0:=cnt0+1;----计数elsecnt0:="0000";if cnt1<"0101" then----高位小于5时cnt1:=cnt1+1;elsecnt1:="0000";co<='0';end if;end if;end if;sec1<=cnt1;sec0<=cnt0;end process;end SEC;秒模块仿真波形秒模块原理图当clr=1时,秒的高低位清零;当clr=0时,来一个时钟信号sec0加1,当sec0加到九时清零,co=1,sec1加1。

VERILOG24小时多功能数字钟的设计班级:自动化学生:XXXXX 学号:XXXXXX1 设计目标掌握可编程逻辑器件的应用开发技术——设计输入、编译、仿真和器件编程;熟悉一种EDA软件使用与实验系统介绍;掌握Verilog HDL设计方法,设计一个多功能数字钟,满足以下要求:①能显示小时、分钟、秒钟(小时以24进制,时、分用显示器,秒用LED);②能调整小时、分钟的时间;③复位;2 实验装置586计算机,MAX+plusⅡ 10.2软件,专用编程电缆,EDA Pro2K数字实验装置等。

3 设计步骤和要求①在MAX+plusⅡ 10.2软件中,输入设计的原理图,采用Verilog HDL输入方式,采用分层模块的设计方法设计电路②对电路进行仿真分析;③选择器件,分配引脚,重新对设计项目进行编译和逻辑综合;④对EDA Pro2K数字实验装置中的FPGA器件进行在系统编程,并实际测试电路的逻辑功能(用实验板上的译码显示电路显示结果);4 具体步骤4.1 建立 Quartus 工程;1.打开 Quartus II 工作环境2.点击菜单项 File->New Project Wizard 帮助新建工程3.输入工程工作路径、工程文件名以及顶层实体名4.添加设计文件5.选择设计所用器件6.设置EDA工具7.查看新建工程总结在完成新建后,Quartus II 界面中Project Navigator 的Hierarchy 标签栏中会出现用户正在设计的工程名以及所选用的器件型号4.2 使用 Verilog HDL 完成设计输入代码如下:(1)数字钟顶层模块://*****************timeclock top block(top_clock.v)***************module clock_24(CLK,CP,nCR,EN,Adj_Min,Adj_Hour,SEG7_1,SEG7_2,SEG7_3,SEG7_4);input CLK,nCR,EN,Adj_Min,Adj_Hour; //定义输入端口变量output[7:0]SEG7_1,SEG7_2,SEG7_3,SEG7_4;output CP;wire CP;wire[7:0]Hour,Minute,Second; //说明变量的类型supply1 Vdd;wire MinL_EN,MinH_EN,Hour_EN; //定义中间变量freqDiv UO(CLK,CP);counter10 U1(Second[3:0],nCR,EN,CP); //秒计数器个位counter6 U2(Second[7:4],nCR,(Second[3:0]==4'h9),CP); //秒计数器十位assign MinL_EN=Adj_Min?Vdd:(Second==8'h59);assignMinH_EN=(Adj_Min&&(Minute[3:0]==4'h9))||(Minute[3:0]==4'h9)&&(Second==8' h59);counter10 U3(Minute[3:0],nCR,MinL_EN,CP); //分计数器个位counter6 U4(Minute[7:4],nCR,MinH_EN,CP); //分计数器十位//产生小时计数器使能信号。

Adj_Hour=1,校正小时;Adj_Hour=0,小时正常计时assign Hour_EN=Adj_Hour?Vdd:((Minute==8'h59)&&(Second==8'h59));//24进制小时计数器:调用24进制底层模块构成counter24 U5(Hour[7:4],Hour[3:0],nCR,Hour_EN,CP); //小时计数器SEG7_LUT U6(SEG7_1,Hour[7:4]);SEG7_LUT U7(SEG7_2,Hour[3:0]);SEG7_LUT U8(SEG7_3,Minute[7:4]);SEG7_LUT U9(SEG7_4,Minute[3:0]);endmodule(2)十进制计数器模块://***********counter10.v(BCD:0~5)********************************module counter10(Q,nCR,EN,CP);input CP,nCR,EN;output[3:0]Q;reg [3:0] Q;always@(posedge CP or negedge nCR)beginif(~nCR)Q<=4'b0000; //nCR=0,计数器被异步清零else if(~EN)Q<=Q; //EN=0,暂停计数else if(Q==4'b1001)Q<=4'b0000;else Q<=Q+1'b1; //计数器增1计数endmodule(3)六进制计数器模块://***********counter6.v(BCD:0~5)**********************************module counter6(Q,nCR,EN,CP);input CP,nCR,EN;output[3:0]Q;reg [3:0] Q;always@(posedge CP or negedge nCR)beginif(~nCR)Q<=4'b0000; //nCR=0,计数器被异步清零else if(~EN)Q<=Q; //EN=0,暂停计数else if(Q==4'b0101)Q<=4'b0000;else Q<=Q+1'b1; //计数器增1计数endendmodule(4)24进制计数器模块://***********counter24.v(BCD:0~23)*********************************module counter24(CntH,CntL,nCR,EN,CP);input CP,nCR,EN;output[3:0]CntH,CntL;reg [3:0] CntH,CntL;always@(posedge CP or negedge nCR)beginif(~nCR){CntH,CntL}<=8'h00;else if(~EN){CntH,CntL}<={CntH,CntL};else if((CntH>2)||(CntL>9)||((CntH==2)&&(CntL>=3))){CntH,CntL}<=8'h00;else if((CntH==2)&&(CntL<3))begin CntH<=CntH; CntL<=CntL+1'b1;endelse if(CntL==9)begin CntH<=CntH+1'b1; CntL<=4'b0000;endelsebegin CntH<=CntH; CntL<=CntL+1'b1;endend(5)分频模块://***********freqDiv.v********************************* module freqDiv(in_50MHz,out_1Hz);input in_50MHz;output out_1Hz;reg out_1Hz;reg [25:0]cnt;always@(posedge in_50MHz)begincnt <= cnt + 1'B1;if(cnt < 26'd2*******)out_1Hz <=0;elsebeginif(cnt >= 26'd5*******)cnt <= 26'b0;else out_1Hz <=1;endendendmodule(6)显示模块://***********SEG7_LUT.v********************************* module SEG7_LUT(oSEG1,iDIG);input [3:0] i DIG;output [7:0] o SEG1;reg [7:0] o SEG;wire [7:0] oSEG1;always @(iDIG)begincase(iDIG)4'h0: oSEG = 8'b00111111;4'h1: oSEG = 8'b00000110;4'h2: oSEG = 8'b01011011;4'h3: oSEG = 8'b01001111;4'h4: oSEG = 8'b01100110;4'h5: oSEG = 8'b01101101;4'h6: oSEG = 8'b01111101;4'h7: oSEG = 8'b00000111;4'h8: oSEG = 8'b01111111;4'h9: oSEG = 8'b01101111;4'ha: oSEG = 8'b01110111;4'hb: oSEG = 8'b01111100;4'hc: oSEG = 8'b00111001;4'hd: oSEG = 8'b01011110;4'he: oSEG = 8'b01111001;4'hf: oSEG = 8'b01110001;endcaseendassign oSEG1=~oSEG;endmodule4.3 电路编译4.4 电路仿真选择仿真参数保存波形文件Q_DECODE_38.vwf点击菜单项Processing->Generate Functional Simulation Netlist,产生功能仿真网表点击菜单项Processing->Start Simulation 启动功能仿真4.5 器件的编程下载下载程序:在Programmer界面中,将.sof 文件列表中Program/Configure 属性勾上再点击Start 按钮,开始下载程序。

完成后,下载程序显示100%最终调试,在DE0 实验板上,扳动SW2,SW1 和SW0 开关,可以看到译码之后的LEDR7-LEDR0 红色LED 发光输出。