单精度浮点乘法器的FPGA实现

- 格式:doc

- 大小:130.50 KB

- 文档页数:4

基于FPGA的流水线单精度浮点数乘法器设计彭章国;张征宇;王学渊;赖瀚轩;茆骥【摘要】针对现有的采用Booth算法与华莱士(Wallace)树结构设计的浮点乘法器运算速度慢、布局布线复杂等问题,设计了基于FPGA的流水线精度浮点数乘法器.该乘法器采用规则的Vedic算法结构,解决了布局布线复杂的问题;使用超前进位加法器(Carry Look-ahead Adder,CLA)将部分积并行相加,以减少路径延迟;并通过优化的4级流水线结构处理,在Xilinx(R)ISE 14.7软件开发平台上通过了编译、综合及仿真验证.结果证明,在相同的硬件条件下,本文所设计的浮点乘法器与基4-Booth算法浮点乘法器消耗时钟数的比值约为两者消耗硬件资源比值的1.56倍.【期刊名称】《微型机与应用》【年(卷),期】2017(036)004【总页数】5页(P74-77,83)【关键词】浮点乘法器;超前进位加法器;华莱士树;流水线结构;Vedic算法;Booth 算法【作者】彭章国;张征宇;王学渊;赖瀚轩;茆骥【作者单位】西南科技大学信息工程学院,四川绵阳621010;西南科技大学信息工程学院,四川绵阳621010;中国空气动力研究与发展中心,四川绵阳621000;西南科技大学信息工程学院,四川绵阳621010;西南科技大学信息工程学院,四川绵阳621010;西南科技大学信息工程学院,四川绵阳621010【正文语种】中文【中图分类】TP331.2浮点乘法器(eFloating Point Multiplier,FPM)是数字信号处理(eDigital Signal Processing,DSP)、视频图像处理以及信号识别等应用邻域重要的运算单元。

尤其是在视频图像处理领域,随着对高速海量图像数据处理的实时性要求逐渐提高,设计一种具有更高速率、低功耗、布局规律、占用面积小和集成度高的浮点乘法器极其重要。

阵列乘法器是采用移位与求和的算法而设计的一种乘法器[1]。

基于FPGA的全流水浮点乘累加器的设计及实现作者:李世平陈铠来源:《电子技术与软件工程》2016年第02期摘要为提升浮点乘累加的流水性能,本文提出了一种基于FPGA全流水浮点乘累加器的设计和实现方法。

通过无阻赛流水累加和串形全加等技术,实现了任意长度单精度浮点复向量的乘累加计算,且相邻两个向量之间无流水间隙。

该累加器在Xilinx的XC7VX690T FPGA上实现,乘法器和逻辑资源消耗不到1%,最高运行频率可达279MHz。

【关键词】FPGA 浮点乘累加全流水1 引言随着半导体技术的不断发展,FPGA的功能和性能显著提升,正逐渐成为雷达、通信等诸多领域数字系统设计的重点,通常被用做复杂信号处理算法的硬件加速。

浮点乘累加作为信号处理算法中的常用基本单元,在矩阵乘、矩阵协方差、FIR等计算过程中都有着广泛应用。

传统累加器是通过将加法器的输出反馈到输入端来实现,对于浮点运算而言,由于浮点加法计算较复杂,需要经历对阶、尾数运算、结果规格化、舍入处理和溢出判断五个步骤,一般会有7~14级的流水延迟,进而会导致流水线阻塞,因此需要研究采用合理的累加结构来提高流水性能。

Ling Zhuo等人提出了一种面向矩阵运算的流水累加结构,提高了流水性能,但该结构控制机制复杂,且缓存资源消耗大,正比于流水延迟量的平方;袁松等人采用了分级流水线方法,缓存消耗较小,但在中小规模矩阵累加时会出现流水线暂停,而且输出时延较大,与矩阵总数据个数成正比。

本文提出了一种基于FPGA的全流水浮点乘累加器结构,能够实时完成任意长度单精度浮点复向量的乘累加计算,且相邻两个向量之间无流水间隙,该累加器在Xilinx的XC7VX690T FPGA上实现,乘法器和逻辑资源消耗不到1%,最高运行频率可达279MHz,目前已成功在矩阵协方差、求逆等算法实现过程中推广应用。

2 方案设计基于FPGA的全流水乘累加器结构如图1所示。

A和B为两个等长度的浮点向量,valid 表示输入数据有效,last表示当前处理向量的最后一个数据;Q为输出累加结果,Qvalid为累加结果的有效标志。

Electronic Technology •电子技术Electronic Technology & Software Engineering 电子技术与软件工程• 113●基金项目:广西自然科学基金项目(2014GXNSFAA118392);广西教育厅科研项目(YB2014209)。

【关键词】FPGA 单精度浮点运算 模块化 系统FPGA 近年来在体系结构、技术水平和持续改进的设计方面进行了提高和完善,弥补了专用处理器灵活性不足之处,FPGA 的容量、速度和资源已经有了更好的提高。

在微处理器的指令系统中,浮点数加/减和乘/除法指令都是实现2个单精度浮点数的运算,浮点数算术运算系统的设计通常采用流水线和自顶向下方式,但对于所执行的浮点数算术运算指令需要应用上一条运算指令的运算结果作为操作数的指令,则浮点数算术运算的流水线操作失去作用,影响了浮点数算术运算指令执行的速度。

本设计利用Verilog 语言,采用基于FPGA 自主设计的浮点数算术运算系统,进行浮点加减乘除运算验证和仿真,提高了运算的操作速度,具有较强的通用性和可操作性。

1 单精度浮点加减乘除运算1.1 单精度浮点数表示IEEE754标准中,一个规格化32位的浮点数表示为:X=(-1)S ×(1.M)×2e e=E-127其中用1位表示数字的符号S ,S 为0表示正数,S 为1表示负数。

IEEE754标准中规定的规格化浮点数的阶码是用移码表示,用8位来表示阶码E ,E 是带有偏移量的阶码,偏基于FPGA 单精度浮点数算术运算系统的设计与仿真文/谢四雄 李克俭 蔡启仲 潘绍明移量是127,e 是实际阶码,在计算实际阶码e 时,对阶码E 的计算采用源码的计算方式,32位浮点数的8位的阶码E 的取值范围是0到255,用23位来表示尾数M ,尾数用原码表示,其中尾数域值是1.M 。

单精度浮点数的存储格式如表1所示,因为规格化的浮点数的尾数域最左位总是1,故这一位不予存储,而认为隐藏在小数点的左边,使用的时候再恢复出来。

原创性声明郑重声明:此篇题为《基于FPGA的单精度浮点数乘法器设计》的论文,是作者在导师的指导下,于武汉大学攻读硕士学位期间,进行研究工作所取得的成果。

根据作者所知,论文中除了参考文献列举的地方外,不包含其他人已经发表或撰写过的研究成果。

本声明的一切法律结果由本文作者承担。

作者签名:旷捷毛雪莹彭俊淇导师签名:黄启俊常胜撰写日期:二零一零年三月十八日基于FPGA的单精度浮点数乘法器设计作者:旷捷毛雪莹彭俊淇导师:黄启俊常胜(武汉大学物理科学与技术学院,武汉,430072)摘要:本文设计了一个基于FPGA的单精度浮点数乘法器。

乘法器为五级流水线结构。

设计中采用了改进的带偏移量的冗余Booth3算法和跳跃式Wallace树型结构,减少了部分积的数目,缩短了部分积累加的耗时;提出了对尾数定点乘法运算中Wallace树产生的2个伪和采用部分相加的处理方式,有效地提高了的运算速度;并且加入了对特殊值的处理模块,完善了乘法器的功能。

单精度浮点数乘法器在Altera DE2开发板上进行了验证,其在Cyclone II EP2C35F672C6器件上的最高工作频率达到212.13 MHz。

关键词:改进的带偏移量的冗余Booth3算法;跳跃式Wallace树;单精度浮点数乘法器;FPGAAn FPGA Implementation of Single Precision Floating-point MultiplierAuthor: KUANG Jie, MAO Xueying, PENG JunqiTutor: HUANG Qijun, CHANG Sheng(Department of Physics Science and Technology, Wuhan University, Wuhan, 430072)Abstract:An FPGA implementation of single precision floating-point multiplier is introduced in this thesis. With the usage of modified redundant Booth3 with bias and leapfrog Wallace tree, and the application of partial addition in fixed-point multiplication, the efficiency of the 5-stage multiplier is promoted. Moreover, a module dealing with special values is introduced to perfect the function of the multiplier. The verification of the multiplier is accomplished on Altera DE2, and the Fmax on Cyclone II EP2C35F672C6 reaches 212.13 MHz.Key words: modified redundant Booth3 with bias; leapfrog Wallace tree; single precision floating-point multiplier; FPGA随着数字信号处理技术的不断发展,人们对数据的精确性和处理的实时性的要求日益提高,浮点数逐渐取代定点数,成为应用最广的数据格式。

基于FPGA的浮点运算器IP核的设计与实现摘要浮点运算作为数字信号处理的最基本的运算,具备动态范围大的特点,不仅成为衡量微处理器性能的主要指标之一,而且广泛适用于复杂的数学计算、科学应用和工程设计中,随着多媒体技术的蓬勃发展,浮点运算单元的应用范围越来越广泛,它已经走入了千家万户,用来解决复杂的数字图像处理,移动物体模型的建立,三维动画设计与演示等等。

随着FPGA的出现以及EDA技术的成熟,采用FPGA实现数字信号处理的方法已经显示出巨大的潜力,利用FPGA技术设计浮点乘法器可以缩短产品的开发周期。

本设计提出了一种基于VHDL语言的浮点乘法器的硬件实现方法,就是用VHDL 语言描述设计文件和原理图方式设计,以Altera公司的Cyclone系列产品为硬件平台,以Quartus为软件工具进行模拟仿真,实现了任意以IEEE754标准表示的23位单精度浮点数的乘法运算。

设计中对阶码的溢出进行了研究并进行了处理,同时对结果进行了规格化处理,通过利用FPGA在线可编程的技术,设计出的浮点乘法器更加方便灵活,克服了专用乘法器的不足,更能广泛的应用到各个领域。

关键词:IEEE754,单精度浮点数,乘法器,硬件描述语言,FPGA,QuartusTHE DESIGN AND IMPLEMENTATION OF FLOATING-POINT UNIT IP CORE BASED ON FPGAABSTRACTAs the most basic operation of digital signal processing, floating-point calculation is equipped with the characteristic of dynamic range, it is not only the main measure of microprocessor performance indexes, but also is widely used in complex mathematical calculation, science applications and engineering design. with the vigorous development of multimedia technology, floating point arithmetic unit has been widely used, and it has come home, been used to solve complex problems, such as digital image processing, the establishment of the moving object model, 3-d animation design and demonstrate, etc. With the maturity of FPGA presence and EDA technology, it has shown great potential to realize digital signal processing by the method of using FPGA, it can cut short the development cycle by using the FPGA technology design floating-point on time-multiplier. The design is proposed based on VHDL language of floating on time-multiplier, the hardware realization method is described with VHDL language schematic design documents and Altera design, by the way the Cyclone series products for hardware platform, with Quartus for software tools for simulation,it realized any twenty-three single precision floating-point multiplication which is in the IEEE754 standard. Design of order yards was studied and spill the processing, and the results are the normalized processing, by using the on-line programmable FPGA technology, design the floating-point greater flexibility on time-multiplier, overcome the deficiency of special on time-multiplier, more can widely used in various fields.KEY WORDS:IEEE754,float,multiplier unit,VHDL,FPGA,Quartus目录前言 (1)第1章绪论 (3)§1.1 引言 (3)§1.2 浮点数的格式 (3)§1.2.1 一般浮点数表示方法 (3)§1.2.2 IEEE754标准表示的浮点数 (4)§1.2.3 浮点数的规格化 (5)§1.2.4 特殊浮点数 (5)§1.3 浮点乘法器的原理 (6)第2章EDA工具介绍 (8)§2.1 EDA技术及其发展 (8)§2.2 EDA设计流程及其工具 (8)§2.2.1 设计流程 (8)§2.2.2 HDL简介 (10)§2.2.3 Quartus II简介 (10)第3章整体框架设计及功能模块介绍 (11)§3.1 设计思路 (11)§3.2 预处理模块 (11)§3.3 定点乘法器 (12)§3.3.1 IEEE754舍入模式 (12)§3.3.2 定点乘法器原理 (13)§3.3.3 定点乘法器模块 (13)§3.4 计算尾数模块 (15)§3.5 计算阶码及溢出处理 (16)§3.5.1 定点加减法原理 (16)§3.5.2 溢出概念与检测方法 (17)§3.5.3 阶码运算原理 (18)§3.5.4 补码模块 (18)§3.5.5 阶码相加模块 (19)§3.5.6 溢出模块 (20)§3.6 数据显示模块 (21)§3.6.1 数据模块 (21)§3.6.2 显示模块 (22)第4章仿真结果及实验验证 (24)§4.1 顶层原理图 (24)§4.2 顶层仿真 (25)§4.2.1 一般情况 (25)§4.2.2 特殊情况 (25)§4.2.3 显示情况 (26)§4.3 引脚锁定 (26)§4.4 硬件平台 (27)§4.4.1 FPGA简介 (27)§4.4.2 芯片选择 (28)§4.5 下载验证 (28)结论 (30)参考文献 (31)致谢 (33)附录 (34)前言21世纪是信息化的时代,信息产业已经成为衡量一个国家经济科技实力的重要标志,集成电路则是信息技术与信息产业的基础,是电子信息产业的命脉。

(完整)单精度浮点乘法器编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望((完整)单精度浮点乘法器)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为(完整)单精度浮点乘法器的全部内容。

EDA/SOPC课程设计报告题目: 单精度浮点乘法器姓名: 张恺学号:120260230同组人:刘龙指导教师:王晨旭成绩:目录第1章课程设计的要求1.1 课程设计的目的●通过课堂所讲授的内容以及私下查阅资料,自主完成课程设计的题目,提高编程能力,培养用计算机解决实际问题的能力,积累调试程序的经验,更好的消化老师课堂所讲授的内容,对Verilog这种语言也有了更深的了解;●掌握较大工程的基本开发技能;●培养综合运用Modelsim,ISE,Debussy工具进行硬件开发的能力;●培养数字系统设计的基本能力;●通过课设积累起的编程以及硬件的能力对于今后的考研抑或是找工作都有非常实际性的效果;1.2 课程设计的条件●设计条件1:gVim编辑器以及Mentor公司开发的FPGA仿真软件Modelsim;●设计条件2:Xilinx公司开发的硬件设计工具ISE以及Xilinx公司的开发板;●设计条件3:虚拟机环境下的Linux系统具有的Design Compiler工具;●设计条件4:虚拟机环境下的Linux系统具有的SDF工具以及Debussy工具;1.3 课程设计的要求●设计要求1:能够在Modelsim工具下正确的完成程序的编译以及成功的实现波形的仿真;●设计要求2:能够在ISE工具下正确的完成程序的综合以及合理的绑定管脚并成功的将程序下载到开发板里,在开发板中实现程序的功能;●设计要求3:能够在虚拟机的Linux系统下采用Design Compiler完成逻辑综合,并且评估其时序面积;●设计要求4:能够在虚拟机的Linux系统下完成SDF反标仿真;第2章课程设计的内容2.1 设计思路对于单精度浮点乘法器这一课程题目,重点在于正确理解IEEE-754标准,设计出符合IEEE-754标准的单精度浮点乘法器。

单精度浮点运算单元的FPGA设计与实现张素萍;李红刚;张慧坚;董定超【摘要】This paper analyzes the principle and operation process of the floating-point unit; studies the architecture of Floating-Point Unit. To solve the deficiency which FPU design depended on software. We propose a project of the FPU design which is suitable for FPGA.This approach enhances the portability and improvement of the system and higher calculating speed. The design unit is simulated, meeting the requirements of design and realizing logic synthesis in FPGA w ith the model Cyclone Ⅱ EP2C35F672C6. The result shows that the operating frequency is 47. 4MHZ to meet all requirements of the design.%针对以前浮点运算依靠软件实现的弊端,提出采用自顶向下的设计方法,模块化的设计思想来实现FPU整个设计,这种设计方法增强了系统的可移植性及可改进性;系统在CycloneⅡ EP2C35FC684C6的FPGA上综合实现,验证结果表明,在满足各项功能要求的前提下,其系统最高时钟频率可达到47.4MHZ,提高了浮点运算单元的处理速度.【期刊名称】《计算机测量与控制》【年(卷),期】2011(019)005【总页数】4页(P1178-1180,1183)【关键词】浮点;FPU;IEEE754;FPGA【作者】张素萍;李红刚;张慧坚;董定超【作者单位】天津中德职业技术学院电气工程系,天津,300191;天津市光学精密机械研究所,天津,300384;中国热带农业科学院科技信息研究所,海南,儋州,571737;中国热带农业科学院科技信息研究所,海南,儋州,571737【正文语种】中文【中图分类】TP3320 引言随着信息应用领域对数据运算精度要求的不断提高和数值运算范围的不断扩大,使得在当今嵌入式微处理器的设计中,浮点运算单元(Floating-point Unit,FPU)的研究显得越来越重要。

快速浮点运算在FPGA中的实现王强【摘要】Floating point calculation is one of important calculations on computers, which is very complex and has certain speed shortcomings for ordinary software. We design the calculation mode by arithmetic of float-point number with single precision under IEEE754 to improve its calculation speed, shorten the period of product development and implement float-point number with single precision in FPGA and making full use of the features of FPGA production line.%浮点计算是计算机计算中的一种重要计算方式,计算过程比较复杂,一般的软件在计算时有一定的速度缺陷。

在IEEE754标准下通过FPGA器件对单精度浮点数的四则运算进行运算模块设计,利用FPGA的流水线工作特点,提高浮点计算速度,缩短产品开发周期,在浮点运算的规则下实现了FPGA器件上的单精度浮点数运算。

【期刊名称】《铜仁学院学报》【年(卷),期】2014(000)004【总页数】3页(P104-106)【关键词】浮点运算;IEEE754;FPGA【作者】王强【作者单位】铜仁学院物理与电子工程学院,贵州铜仁 554300【正文语种】中文【中图分类】TP3321.引言EDA 技术和FPGA 的产生与发展提供了用硬件直接实现浮点数运算的可能。

用硬件实现的浮点数运算,能够以并行方式工作,速度快,抗干扰性强,可以作为IP核被调用,所以在性能和灵活性上都有很大的优势[1]。

FPGA中的浮点四则运算由于定点的四则运算比较简单,如加减法只要注意符号扩展,小数点对齐等问题即可。

在本文中,运用在前一节中描述的自定义浮点格式FPGA中数的表示方法(下),完成浮点四则运算的实现过程1.自定义浮点格式加(减)法运算基于FPGA 实现的浮点加法运算包括了一系列对尾数和指数部分的操作:移位、交换、格式化、舍入和格式化等。

如下图所示,自定义浮点流水加法器实现结构主要分为两部分:基本加法器部分和格式化操作部分。

在图(a)中的基本加法器,首先比较两个操作数的指数部分,较大的指数加上1之后,寄存输出(保证流水输出)作为加法和的指数部分;另一方面根据指数部分的比较结果,交换尾数的位置,即需要对较小的尾数进行右移对齐;之后尾数部分相加,得到的结果高位截取后输出作为加法和的尾数部分。

由于操作数A 和B 的尾数部分首先需要符号位拓展之后进行才进行下一步操作,而最后的和是直接高位截取输出的,故导致加法结果比实际值小一倍,这就是前面指数需要加上1输出的原因。

对于(b)中的格式化操作,首先对来自基本加法器的尾数和指数进行预处理,然后计算尾数部分的符号位个数。

最后根据计算得到的符号位个数,左移尾数后输出尾数部分,而指数则减去符号位数作为指数部分输出。

如果是一次而输入加法则以这样的结构即可,但如果涉及多次加法,以流水形式完成,则在结构上可以作更好的优化。

如下是四输入和八输入加法器的结构:如上所示的情况,可知,这样的方法可以减少格式化操作,而格式化操作在整个运算过程中消耗相对比较多的资源,因此这样的实现结构可以有效的减少硬件资源的消耗。

3. 乘加运算浮点乘法运算较为简单,对应的尾数部分进行相乘,指数部分进行相加。

尾数相乘部分采用XILINX 乘法器IP即可。

需要注意的是,乘法结果输出的位宽指定,在乘法器IP中,按一般流程下来,乘完之后的结果是保留两位符号位(假设乘数都是一个符号的情况),即多出一个符号位,按小数乘法分析的话,值的情况是比实际结果小一倍,在截位输出的时候需要做一定的取舍(是从最高位开始截位输出,还是次高位开始截位输出;如果从最高位截位输出,则结果比实际值小一倍,如果从次高位截位输出只有一种情况会溢出,即两个乘数都为-1的情况,这种情况如果从次高位截位输出则会错误,其余情况都是正确的)。

32位单精度浮点乘法器的FPGA实现

摘要: 采用Verilog HDL语言, 在FPGA上实现了32位单精度浮点乘法器的设计, 通过采用改进型Booth编码,和Wallace 树结构, 提高了乘法器的速度。

本文使用Altera Quartus II 4.1仿真软件, 采用的器件是EPF10K100EQ 240 -1, 对乘法器进行了波形仿真, 并采用0.5CMOS工艺进行逻辑综...

摘要: 采用Verilog HDL语言, 在FPGA上实现了32位单精度浮点乘法器的设计, 通过采用改进型Booth编码,和Wallace 树结构, 提高了乘法器的速度。

本文使用Altera Quartus II 4.1仿真软件, 采用的器件是EPF10K100EQ 240 -1, 对乘法器进行了波形仿真, 并采用0.5CMOS工艺进行逻辑综合。

关键词: 浮点乘法器; Boo th 算法; W allace 树; 波形仿真

随着计算机和信息技术的快速发展, 人们对微处理器的性能要求越来越高。

乘法器完成一次乘法操作的周期基本上决定了微处理器的主频, 因此高性能的乘法器是现代微处理器中的重要部件。

本文介绍了32 位浮点阵列乘法器的设计, 采用了改进的Booth 编码, 和Wallace树结构, 在减少部分积的同时, 使系统具有高速度, 低功耗的特点, 并且结构规则, 易于VLSI的实现。

1 乘法计算公式

32 位乘法器的逻辑设计可分为: Booth编码与部分积的产生, 保留进位加法器的逻辑, 乘法阵列的结构。

1.1 Booth编码与部分积的逻辑设计

尾数的乘法部分,本文采用的是基4 Booth编码方式, 如表1。

首先规定A m和B m 表示数据A和B的实际尾数,P 表示尾数的乘积, PP n表示尾数的部分积。

浮点32 位数, 尾数是带隐含位1 的规格化数, 即: A m=1×a22a21….a0和B m = 1

×b22b21.…b0, 由于尾数全由原码表示,相当于无符号数相乘, 24 × 24 位尾数乘积P 的公式为:

1.2 乘法器的阵列结构

本文采用的是3 -2 加法器, 输入3 个1 位数据: a, b,ci; 输出2 个1 位数据: s, Co。

运算式如下:

其逻辑表达式如下:

当每个部分积PP n产生之后, 将他们相加便得到每个乘法操作的结果。

相加的步骤有很多, 可采用的结构和加法器的种类也很多。

比如串行累加:

而Wallace 树的乘法阵列如下:

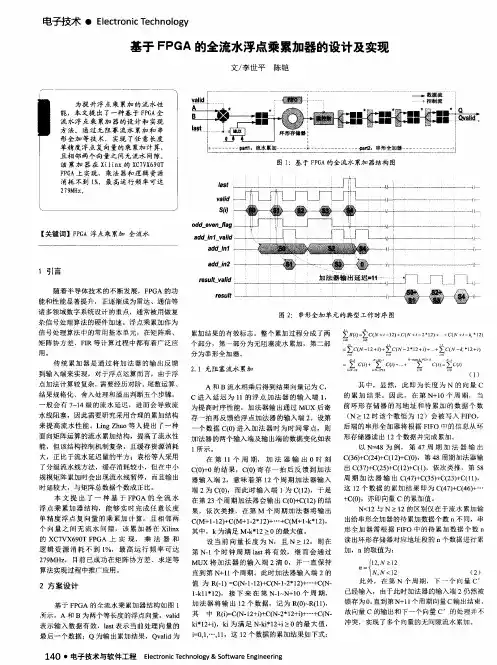

加法器之间的连接关系如图1, 图2 所示, 或者从公式(7) 与(8) 中可以看出, 图1中串行累加的方法延迟为11个3-2 加法器的延迟, 而图2中, Wallace树延迟为5个3 -2加法器的延迟。

图1的延迟比图2的延迟大。

图1 串行累

加图2 Wallace 树

2 32 位浮点乘法器的设计

本文是针对IEEE754 单精度浮点数据格式进行的浮点乘法器设计。

IEEE754 单精度浮点格为32位, 如图3 所示。

设A ,B均为单精度IEEE754格式, 他们的符号位, 有效数的偏移码和尾数部分分别用S , E 和M来表示。

双精度和单精度采用的运算规则是一致的, 只是双精度的位长增加了一倍, 双精度是64位, 其中尾数52位, 指数11位, 1位符号位。

所以提高了精度范围。

图3 32 位浮点数据格式

32 位浮点数据格式: A = (- 1) S×M ×2E-127。

其中乘法器运算操作分4步进行。

(1) 确定结果的符号, 对A 和B 的符号位做异或操作。

(2) 计算阶码, 两数相乘, 结果的阶码是两数的阶码相加, 由于A 和B 都是偏移码, 因此需要从中减去偏移码值127,得到A 和B 的实际阶码, 然后相加, 得到的是结果的阶码, 再把他加上127, 变成偏移码。

(3) 尾数相乘,A 和B 的实际尾数分别为24位数, 即1×M a 和1×M b, 最高位1是隐藏位, 浮点数据格式只显示后23位, 所以尾数相乘结果应为一个48位的数据。

(4) 尾数规格化, 需要把尾数相乘的48位结果数据变成24 位的数据, 分3步进行:

① 如果乘积的整数位为01, 则尾数已经是规格化了;如果乘积的整数位为10, 11, 则需要把尾数右移1位, 同时把结果阶码加1。

② 对尾数进行舍入操作, 使尾数为24位, 包括整数的隐藏位。

③ 把结果数据处理为32位符合IEEE浮点数标准的结果。

包括1位符号位, 8位结果阶码位, 结果23尾数位。

3 32 位浮点乘法器的实现与仿真

图4 列出本设计的FPGA 仿真结果。

图中data1是被乘数, data2是乘数, reset 是清零信号, 高有效。

start 是开始信号, 也是高有效。

dataout10是两个浮点32 位数相乘, 进行规格化以后的结果, 是一个32 位数。

Product 是24位尾数相乘的结果, 是一个48位数。

图4 32 位浮点乘法器的仿真结果

整个设计采用了VHDL和Verilog HDL语言进行结构描述, 如果采用的是上华0.5 的标准单元库, 并用Synopsys DC 进行逻辑综合, 其结果是完成一次32位浮点乘法的时间为30ns, 如果采用全定制进行后端版图布局布线, 乘法器性能将更加优越。

4 结语

本文给出了32 位浮点乘法器的设计, 浮点算法具有高精度性以及较宽的运算

范围, 使得乘法的设计更能够满足工程和科学计算的要求, 电路的设计、模拟和实现均采用Altera Quartus II 4.1开发工具。

采用的器件EPF10K100EQ 240-1, 逻辑单元是1914个, PIN的数量是147,本设计采用了一系列的算法和结构, 如采用Booth编码的方法和Wallace树的结构, 使得系统具有高速度特点, 并且易于ASIC的后端版图实现。