nj单片机原理及应用(C语言版)第5章

- 格式:pdf

- 大小:930.20 KB

- 文档页数:85

第5章汇编语言程序设计及仿真调试5.1 汇编语言程序设计基础知识5.2 汇编语言程序设计举例5.3 利用Keil uVision2调试程序5.1.1 伪指令一般来说,在汇编语言源程序中用MSC-51指令助记符编写的程序,都可以一一对应的产生目标程序。

但还有一些指令,例如指定目标程序或数据存放的起始地址,给一些指定的标号赋值,在内存中预留工作单元,表示源程序结束等等。

这些指令并不产生目标程序,不影响程序的执行,仅仅产生供汇编用的某些指令,以便在汇编时执行一些特殊操作,称之为伪指令。

一、设置起始地址ORGORG nnORG伪指令总是出现在每段源程序或数据块的开始。

它可使程序员把程序、子程序或数据块存放在存贮器的任何位置。

ORG2000HMOV A,20H┇表示后续目标程序从2000H单元开始存放。

一般要求ORG定义空间地址由小到大,且不能重叠。

二、定义字节DB或DEFB〈标号:〉DB〈项或项表〉其中项或项表是指一个字节,数或字符串,或以引号括起来的ASCⅡ码字符串(一个字符用ASCⅡ码表示,相当于一个字节)。

该指令的功能是把项或项表的数值(字符则用它的ASCⅡ码)存入从标号开始的连续单元中。

ORG 1000HSEG1:DB 53H,74H,78H,‘1’,‘2’SEG2:DB 23H,‘DAY’则:(1000H)=53H(1001H)=74H(1002H)=78H(1003H)=31H 数字1的ASCⅡ码(1004H)=32H 数字2的ASCⅡ码(1005H)=23H(1006H)=44H(1007H)=41H‘DAY’ 的ASCⅡ码(1008H)=59H三、定义字DW或DEFW〈标号:〉DW〈项或项表〉DW的基本含义与DB相同,但DB一般用于定义8位数据(一个字节),而DW则定义16位数据,即一个字(规定为两个字节,即一个字为16位二进制数)。

在执行汇编程序时,机器会自动按高位字节在前,低位字节在后的格式排列(与程序中的地址规定一致)。

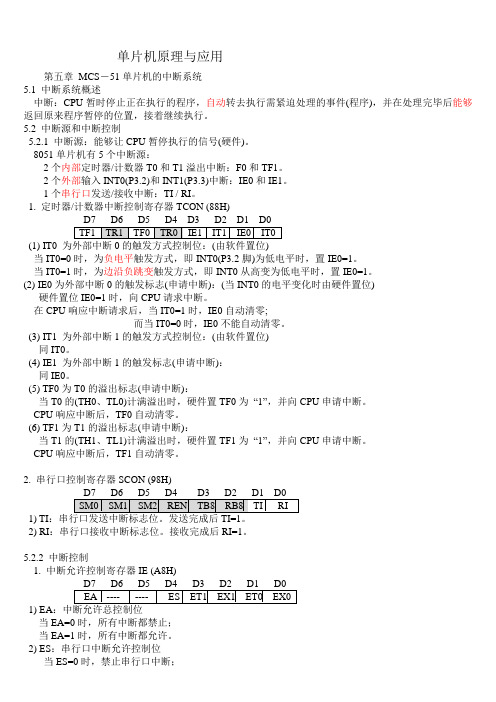

单片机原理与应用第五章MCS-51单片机的中断系统5.1 中断系统概述中断:CPU暂时停止正在执行的程序,自动转去执行需紧迫处理的事件(程序),并在处理完毕后能够返回原来程序暂停的位置,接着继续执行。

5.2 中断源和中断控制5.2.1 中断源:能够让CPU暂停执行的信号(硬件)。

8051单片机有5个中断源:2个内部定时器/计数器T0和T1溢出中断:F0和TF1。

2个外部输入INT0(P3.2)和INT1(P3.3)中断:IE0和IE1。

1个串行口发送/接收中断:TI / RI。

1. 定时器/计数器中断控制寄存器TCON (88H)D7 D6 D5 D4 D3 D2 D1 D0TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0(1) IT0 为外部中断0的触发方式控制位:(由软件置位)当IT0=0时,为负电平触发方式,即INT0(P3.2脚)为低电平时,置IE0=1。

当IT0=1时,为边沿负跳变触发方式,即INT0从高变为低电平时,置IE0=1。

(2) IE0为外部中断0的触发标志(申请中断):(当INT0的电平变化时由硬件置位)硬件置位IE0=1时,向CPU请求中断。

在CPU响应中断请求后,当IT0=1时,IE0自动清零;而当IT0=0时,IE0不能自动清零。

(3) IT1 为外部中断1的触发方式控制位:(由软件置位)同IT0。

(4) IE1 为外部中断1的触发标志(申请中断):同IE0。

(5) TF0为T0的溢出标志(申请中断):当T0的(TH0、TL0)计满溢出时,硬件置TF0为“1”,并向CPU申请中断。

CPU响应中断后,TF0自动清零。

(6) TF1为T1的溢出标志(申请中断):当T1的(TH1、TL1)计满溢出时,硬件置TF1为“1”,并向CPU申请中断。

CPU响应中断后,TF1自动清零。

2. 串行口控制寄存器SCON (98H)D7 D6 D5 D4 D3 D2 D1 D0SM0 SM1 SM2 REN TB8 RB8 TI RI1) TI:串行口发送中断标志位。

第1章习题1-1 什么是单片机?单片机是把微型计算机中的微处理器、存储器、I/O接口、定时器/计数器、串行接口、中断系统等电路集成在一块芯片上形成的单片计算机。

因此被称为单片微型计算机,简称为单片机。

1-2 单片机的主要特点是什么?单片机主要特点有:在存储器结构上,单片机的存储器采用哈佛(Harvard)结构;在芯片引脚上,大部分采用分时复用技术;在内部资源访问上,通过采用特殊功能寄存器(SFR);在指令系统上,采用面向控制的指令系统;单片机内部一般都集成有一个全双工的串行接口;单片机有很强的外部扩展能力。

1-3 指明单片机的主要应用领域。

单片机具有体积小、功耗低、面向控制、可靠性高、价格低廉、可以方便地实现多机和分布式控制等优点,使其广泛的应用于各种控制系统和分布式系统中,主要应用于以下这几个领域:工业测控、智能设备、家用电器、商用产品以及网络与通信智能接口。

1-4 C51单片机的分类。

C51单片机的分类,就是特指MCS-51系列。

那么MCS-51系列的单片机基本上没什么区别,至少内核都是一模一样的。

不同的就是功能模块稍有不同。

比如说:有些具有AD/DA模块,有些没有;有些有EEPROM(STC89C52),有些没有(AT89S52);有些ROM 有8K(AT89S52),有些只有2K;有些RAM有256B,而有些只有128BIT;有些40个管脚(AT89C51、89C52、89S52),有些20个管脚(AT89C2051、89C4051);有些有内部晶振,有些没有;但这些都是稍微一点点的区别,基本都还是算一样的。

1-5 80C51与8051的区别和联系。

MCS-51单片机是指美国INTEL公司生产的一系列单片机的总称,包括有8031,8051,8751,8032,8052,8752等,其中8051是最典型的产品,该系列其它单片机都是在8051的基础上发展来的,人们习惯于用8051来称呼MCS-51系列单片机。

第5章单片机中断系统本章主要内容5.1 中断概述5.2 中断系统结构及控制5.3 中断响应及处理过程5.4 中断应用举例§5.1 中断概述§5.1.1 微机的输入/输出方式单片机系统中,CPU和外部设备之间不断进行信息的传输。

通常CPU和外设之间的信息传送方式一般有以下几种方式:程序控制方式中断方式直接存储器存取(DMA)方式§5.1.1 微机的输入/输出方式1、程序控制方式信息传送过程是在程序控制下进行。

可以分为以下两种方式。

无条件传送方式:当外设已准备就绪,那就不必查询外设的状态而进行信息传输,称为无条件传送方式。

此种信息传送方式只适用于简单的外设。

如开关和数码段显示器等。

§5.1.1 微机的输入/输出方式1、程序控制方式条件查询传送方式:CPU通过执行程序不断读取并测试外部设备状态,如果输入设备处于准备好状态或输出设备为空闲状态时,则CPU 执行传送信息指令。

由于条件传送方式是CPU在不断查询外部设备的当前状态后才进行信息传送,所以也称为“查询式传送”。

§5.1.1 微机的输入/输出方式2、中断控制方式外部设备与CPU之间以中断信号作为数据交换的控制信号。

当外部设备需要与CPU进行数据交换时,由接口部件向CPU发出一个请求信号,CPU响应这一中断请求后,便可在中断服务程序中完成一个字节或一个字的信息交换。

中断控制方式一般用低速外部设备与CPU之间的信息交换。

中断控制方式每操作一次,CPU要打断原来执行的程去执行一段中断服务程序,对速度较高的外部设备将会产生信息丢失,因此不能采用。

所以也称为“查询式传送”。

3、DMA 控制方式(直接存储器存取)DMA 控制方式主要用于存储器和外设之间直接传送。

一般是数据块为单位传送数据的方式。

当某一外部设备需要输入/输出一批数据时,向DMA 控制器发出请求,DMA 控制器接收到这一请求后,向CPU 发出总线请求信号。

§5.1.1 微机的输入/输出方式§5.1.1 微机的输入/输出方式3、DMA控制方式(直接存储器存取)CPU响应DMA的请求,把总线使用权赋给DMA控制器,外设利用DMA通道直接将数据写入存储器或将数据从存储器中读出,传送过程不需要CPU参与。

当这批数据传送后,DMA控制器再向CPU发出“结束中断请求”,CPU响应这一中断请求,即可收回总线使用权。

采用DMA控制方式,CPU只需在数据传送结束时响应一次中断,减轻了CPU的负担,系统的速度会大大增加。

§5.1.2 中断的概念1、中断当CPU正在处理某段程序的时候,外部或者内部发生的某一事件请求CPU迅速去处理,于是CPU暂时中断当前的工作,去处理所发生的事件。

处理完该事件后,再返回到原来被中断的地方继续原来的工作,此过程称为中断。

2、中断源引起CPU中断的内部或外部事件就是中断源。

3、中断请求中断源向CPU发的处理请求即中断请求或中断申请。

§5.1.2 中断的概念主程序响应中断请求中断服务程序返回主程序继续执行主程序¾示例1§5.1.2 中断的概念4、中断响应CPU暂时中止正在处理的事情,转去处理突发事件的过程,称为中断响应。

5、其它概念实现中断功能的部件称为中断系统,又称中断机构。

CPU响应中断后,处理中断事件的程序称中断服务程序。

在CPU暂时中止执行的程序,转去执行中断服务程序时PC值即为断点地址。

CPU执行完中断服务程序后回到断点的过程称为中断返回。

§5.1.2 中断的概念6、中断的主要功能 使CPU与外设同步工作 实现实时处理 故障及时处理 7、中断方式的优点: 消除了CPU在查询方式中的等待现象,大大提高了CPU 的工作效率。

将从现场采集的数据通过中断方式及时传送给CPU,经 过处理后可立即作出反应,实现现场控制。

采用查询方 式很难做到及时采集,实时控制。

§5.2 中断系统的结构及控制主要内容: §5.2.1 MCS-51的中断结构 §5.2.2 MCS-51的中断源§5.2.1 MCS-51 中断结构TCON INT0 IT0=0 IT0=1 T0 IT1=0 INT1 IT1=1 T1 TX RX T2 T2EX TF1 TI RI TF2 EXF2 + + 1 IE1 TF0 ET0 PX1 EX1 PT1 ET1 PS ES PT2 ET2 EA 1 IE0 EX0 IE IP PX0 1 0 PT0 1 0 1 0 1 0 1 0 1 0 自 然 优 先 级 中断 矢量地址 硬件查询 自 然 优 先 级 中断 矢量地址 低 级 中 断 请 求 PC 高 级 中 断 请 求 PC各中断 总允许 源允许优先级图5-2 89C52单片机的中断系统结构§5.2.2 MCS-51的中断源MCS-51中断系统主要是对5个中断源进行管理, 增强型单片机(如89C52)是6个中断源,依次为: ① ② ③ ④ ⑤ ⑥ 外部中断0(P3.2); 外部中断1(P3.3); 定时器/计数器0; 定时器/计数器1; 定时器/计数器2; 串行口中断; CPU主要是通过以下几个特殊寄存器对中断源进 行管理。

§5.2.2 MCS-51的中断源1. 寄存器TCON中的中断标志8FH 8EH 8DH TCON TF1 (88H) 定时器/计 数器T1溢 出中断请 求标志位 TF0 8CH 8BH 8AH 89H IE1 IT1 IE0 88H IT0当启动T1计数后,T1从初值开始加 1计数,计数器最高位产生溢出时, 由硬件使TF1置1,并向CPU发出中 断请求。

当CPU响应中断时,硬件 将自动对TF1清0。

§5.2.2 MCS-51的中断源1. 寄存器TCON中的中断标志8FH 8EH 8DH TCON TF1 (88H) TF0 8CH 8BH 8AH 89H IE1 IT1 IE0 88H IT0定时器/计 数器T0溢 出中断请 求标志位当启动T0计数后,T0从初值 开始加1计数,计数器最高位 产生溢出时,由硬件使TF0置 1,并向CPU发出中断请求。

当CPU响应中断时,硬件将自 动对TF0清0。

§5.2.2 MCS-51的中断源1. 寄存器TCON中的中断标志8FH 8EH 8DH TCON TF1 (88H) TF0 8CH 8BH 8AH 89H IE1 IT1 IE0 88H IT0当检测到外部中断引脚1 上存在有效的中断请求 信号时,由硬件使IE1置 1。

当CPU响应中断请求 时,由硬件使IE1清0。

外部中断1 (P3.3)的中 断请求标 志位§5.2.2 MCS-51的中断源1. 寄存器TCON中的中断标志8FH 8EH 8DH TCON TF1 (88H) TF0 8CH 8BH 8AH 89H IE1 IT1 IE0 88H IT0当检测到外部中断引脚0 上存在有效的中断请求 信号时,由硬件使IE0置 1。

当CPU响应中断请求 时,由硬件使IE0清0。

外部中断0 (P3.2)的中 断请求标 志位§5.2.2 MCS-51的中断源1. 寄存器TCON中的中断标志8FH 8EH 8DH TCON TF1 (88H) TF0 8CH 8BH 8AH 89H IE1 IT1 IE0 88H IT0IT1=0时,外部中断1为电平触发方 式。

CPU在每一个机器周期S5P2 期间采样外部中断请求引脚的输入 电平。

若外部中断1请求为低电平, 则使IE1置1;若为高电平,则使IE1 清0。

外部中断1 的中断触 发方式控 制位§5.2.2 MCS-51的中断源1. 寄存器TCON中的中断标志8FH 8EH 8DH TCON TF1 (88H) TF0 8CH 8BH 8AH 89H IE1 IT1 IE0 88H IT0注意:在电平触发方式中,CPU响应中断时不会清除IE1标志,所 以在中断返回前必须撤销INT1引 脚上的低电平,否则将再次中断 造成出错。

外部中断1 的中断触 发方式控 制位§5.2.2 MCS-51的中断源1. 寄存器TCON中的中断标志8FH 8EH 8DH TCON TF1 (88H) TF0 8CH 8BH 8AH 89H IE1 IT1 IE0 88H IT0IT1=1时,外部中断1为边沿触发方式。

CPU在每一个机器周期S5P2期间采 样外部中断请求引脚的输入电平。

如果在 相继的两个机器周期采样过程中,一个机 器周期采样到外部中断1请求引脚为高电 平,接着的下一个机器周期采样到为低电 平(下降沿) ,则使IE1置1。

直到CPU 响应该中断时,才由硬件使IE1清0。

外部中断1 的中断触 发方式控 制位§5.2.2 MCS-51的中断源1. 寄存器TCON中的中断标志8FH 8EH 8DH TCON TF1 (88H) TF0 8CH 8BH 8AH 89H IE1 IT1 IE0 88H IT0注意:为保证CPU在两个机器周期内检测到“负跳变”,输入高、低 电平的持续时间起码要保持12个 时钟周期。

外部中断1 的中断触 发方式控 制位§5.2.2 MCS-51的中断源1. 寄存器TCON中的中断标志8FH 8EH 8DH TCON TF1 (88H) TF0 8CH 8BH 8AH 89H IE1 IT1 IE0 88H IT0外部中断0 的中断触 发方式控 制位§5.2.2 MCS-51的中断源2. 寄存器SCON中的中断标志SCON (98H) 99H TI 98H RI§5.2.2 MCS-51的中断源2. 寄存器SCON中的中断标志SCON (98H) 99H TI 98H RICPU将一个数据写入发送 缓冲器SBUF时,就启动发送。

每发送完一帧串行数据后,硬 件置位TI。

但CPU响应中断 时,并不清除TI,必须在中断 服务程序中由软件对TI清0。

串行口 发送中 断请求 标志位§5.2.2 MCS-51的中断源2. 寄存器SCON中的中断标志SCON (98H) 99H TI 98H RI在串行口允许接收时,每 接收完一个串行帧,硬件置位 RI。

同样,CPU响应中断时不 会清除RI,必须在中断服务程 序中由软件对RI清0。

串行口 接收中 断请求 标志位§5.2.2 MCS-51的中断源3. 中断允许寄存器IE功能:控制各个中断源的允许和屏蔽,能够位寻址,单片 机复位时其值为00H。

AFH AEH ADH ACH ABH AAH A9H A8H IE EA (A8H) ET2 ES ET1 EX1 ET0 EX0§5.2.2 MCS-51的中断源3. 中断允许寄存器IEAFH AEH ADH ACH ABH AAH A9H A8H IE EA (A8H) 中断 允许 总控 制位 ET2 ES ET1 EX1 ET0 EX0EA =0,屏蔽所有的中断请求; EA =1,开放CPU中断。