FPGA有限状态机模拟I2C总线设计

时间:2007-08-01 来源: 作者:潘小冬点击:2758 字体大小:【大中小】

摘要:以I2C总线协议为根据。用有限状态机(FSM:Finite State Machine)设计了基于FPGA的I2C初始化程序模块。主要内容包括简述I2C总线的特点;介绍用FPGA中FSM 开发I2C总线模块时的设计思想和实现过程;给出并解释了部分用Verilog HDL描述I2C总线初始化SAA7111和SAA7121的程序,最后在QuartusII中进行了I2C总线主从模式下的时序仿真和用其内嵌逻辑软分析仪SignalTap II完成了硬件调试。

在现代电子系统中,有为数众多的IC需要进行相互之间以及与外界的通信。为了简化电路的设计,Philips公司开发了一种用于内部IC控制的简单的双向两线串行总线PC (Intel-Integrated Circuit bus)。该总线具有接口线少、通讯效率高等特点。

在进行FPGA设计时,经常需要和外围提供PC接口的芯片通信,虽然市场上有专用I2C 总线接口芯片,但是地址可选范围小、性能指标固定、功能单一、使用不方便。根据I2C 总线的电气特性及其通讯协议,在Altera公司的FPGA(EP2S30)上可以很方便地实现I2C总线的通讯接口,且具有高速、易调试、可以灵活地实现地在线配置等优点,同时大大地减少了系统的开发周期。

1 I2C总线协议概述

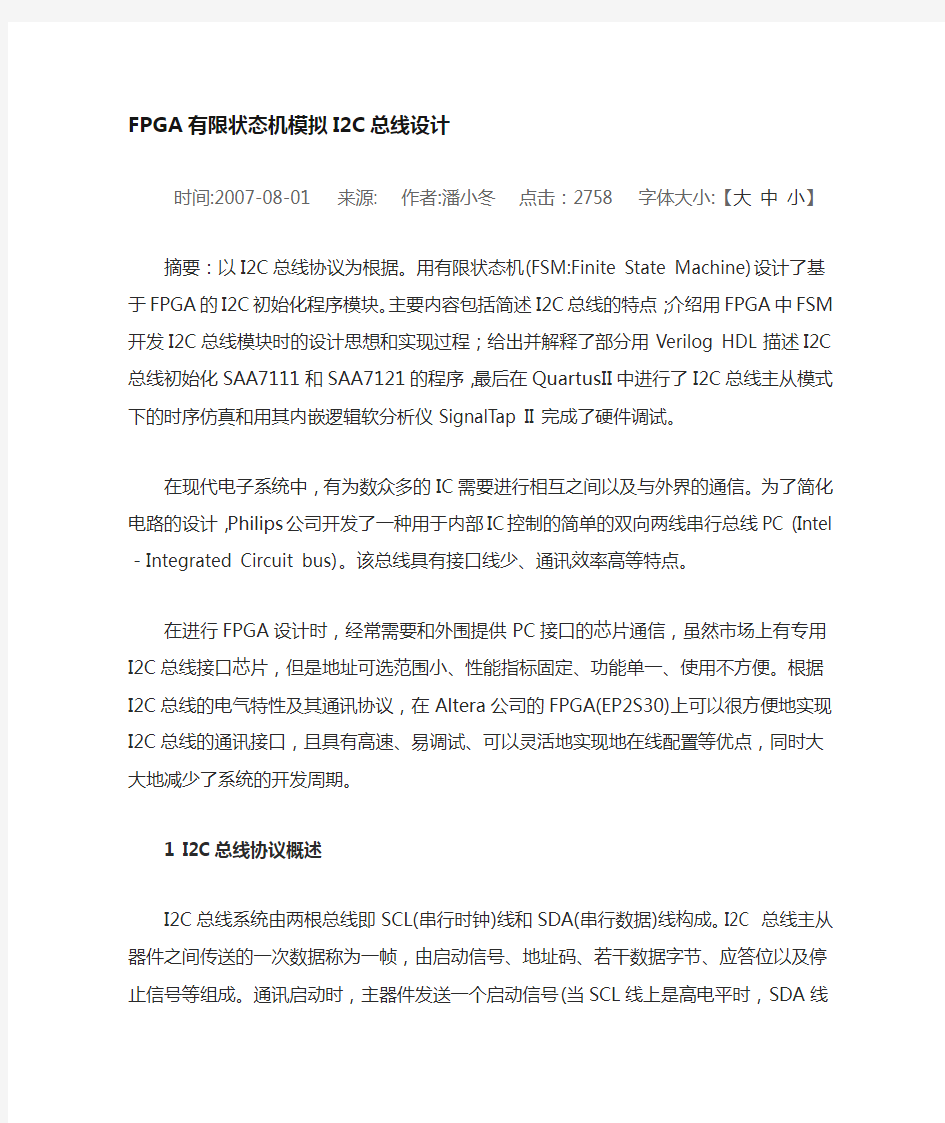

I2C总线系统由两根总线即SCL(串行时钟)线和SDA(串行数据)线构成。I2C 总线主从器件之间传送的一次数据称为一帧,由启动信号、地址码、若干数据字节、应答位以及停止信号等组成。通讯启动时,主器件发送一个启动信号(当SCL线上是高电平时,SDA线上产生一个下跳沿)、从器件的地址(唯一的7位地址码)和1位读写方向标志位;通讯停止时,主器件发送一个停止信号(当SCL线上是高电平时,SDA线上产生一个上跳沿)。在数据传送过程中。当SCL线上是高电平时,必须保证SDA线上的数据稳定,传完一个字节的数据,必须由从器件送回一个应答信号。总线的传输速率为100kbit/s(标准)-400kbit/s(快速)。

这种总线可以设计成很多种通讯配置,考虑到在课题中的实际应用,该I2C总线模型如下:单主操作,只实现简单的写和读操作,写地址连续,没有竞争和仲裁,是很简单的I2C 总线系统。在本设计中,用FPGA模拟的I2C总线协议模块完成对SAA7111和

SAA7121(Philips公司的视频解码和编码芯片)先后进行初始化。

2 I2C 模块的设计与实现

2.1 I2C模块设计思路

I2C 总线写命令格式如下:

写信号: Index> 图1为I2C总线一次完整的数据传输时序图,可以将整个过程分为5个状态:(1)起始,(2)写数('0'或'1'),(3)应答,(4)暂停,(5)结束。针对SAA7111进行初始化,需要在I2C总线上传输的参数共有34个字节:从器件地址(7bits)和写操作位(1bit)占一个字节,基地址参数占一个字节,再加上内部地址连续的32个寄存器(每个寄存器写一个字节数据),写完最后第34个字节后产生一个信号,作为初始化SAA7111的启动信号,初始化SAA7121的过程与前者类似只是传输的参数共有130个字节,就不再赘述。整个初始化SAA711l的具体状态转化过程如图2所示。 为了准确控制和描述每个状态,将SDA和SCL的每一状态都分成四部分(00,01,10,11),如下图3,图中是Ack'1'是非应答状态,Ack'0'是应答状 态,另外设置Idle状态是为了在传输完一个字节后如果继续传输数据,则在这个状态准备下一个要传输的数据.保障了传输过程中的可靠性。 图中每一状态的四个部分都用4个时钟周期来描述,也就是说时钟频率是总线的传输速率(100kb/s—400kb/s)的4倍,即其时钟频率为400kHz- 1600kHz(2.5us-O.625us),所以SDA与SCL之间的跳变沿,都相应地满足I2C通信协议中SDA与SCL之间的建立与保持时间(≥O.6us)。 2.2 I2C 模块程序编写 整个程序用Verilog HDL语言编制,选择I2C总线的传输速率为200kb/s,则输入时钟频率应为800kb/s。在这里把双向数据线SDA用分成两条线模拟:SDAOUT为SDA数据输出,SDAACK为SDA的应答信号。 程序由5个状态组成:Start,Write,Ack,Idle,Stop。状态机的编码方式会影响到逻辑设计的性能,针对FPGA触发器资源丰富,这里采用独热(One-Hot)的编码方式,虽然多用了触发器,但可以有效节省和简化组合电路,提高电路的速度和可靠性,也有利于提高器件资源的利用率。状态定义如下: parameter [19:0] St_Start0=20'b0000_0000_0000_0000_0001; parameter [19:0] St_Start1=20'b0000_0000_0000_0000_0010; parameter [19:0] St_Start2=20'b0000_0000_0000_0100,…… 2.2.1 状态机描述: (1)开始信号(Start)的产生 St_Start0:begin SCLOUT=1'b1;SDAOUT=1'b1; NS=St_Start1;end …… (2)写信号(Write)的产生 St_Write0:begin SCLOUT =1'b0; SDAOUT=SDA_TEMP;NS=St_Write1;end…… 2.2.2 数据输入 一般情况下,I2C总线传输的数据由外部ROM或其它专门的数据存储区来存储,但在数 据相对固定且数据量不是很大的情况下,可以将初始化的数据写在程序中,这样可减少频繁的数据交换,简化操作。SAA7111的初始化数据就属于这种情况,可以通过检测应答信号来改变输入的值。程序如下: always @(posedge CLKIN)begin //Input Data for Initializafion. case(ACK_CNT) //ACK_CNT is a counter for acknowlege. 8'h00:DATA_REG<=8'h48; //-Slave Address+Wr 8'h01:DATA_REG<=8'h00;…… 2.2.3 数据并串转换 由于数据寄存器的数据位宽是8bits,而在I2C总线上传输的是位宽是1bit,所以要进行并串转换,且需满足数据高位在前,低位在后。 2.2.4 产生初始化SAA7121的启动信号 当SAA7111初始化完后,应产生开始初始化SAA7121的启动信号,该信号的要求是平时为低电平,当检测到SAA7111的SDA和SCL均为高电平时,生成一个高脉冲,作为SAA7121初始化状态机的Reset信号。 3 I2C仿真与调试 下图4是在Quartus II中时序仿真的信号波形,其中SDAACK为高时,即模拟I2C总线上非应答时的情况,可以从SCL和SDA的波形看到,I2C总线又 重新进入开始状态,开始第二次初始化。这样万一初始化失败,还可以再次重新开始,提高了设计的可靠性。 图5(a)和图5(b)是在Quartus II中把相关程序下载到EP2S30中,用其内嵌的在线逻辑 分析仪SignalTap II采得的初始化SAA7111时的信号波形,信号依次为SCL,SDA,START7121。 4 结束语 以该I2C总线协议为基础,编写FPGA初始化SAA7111和SAA7121的程序,仿真顺利通过并在硬件上调试成功,实现了FPGA与SAA7111和SAA7121实际通讯实验,结果工作正常,验证了FPGA有限状态机模拟I2C总线设计的正确性和可行性。该模块只需修改“2.2.2数据输入”中的参数和ACK_CNT计数器的值,就能移植到对其它满足I2C总线通信协议的器件的初始化中,如AD公司的ADV7170,ADV7179等,效果不错。 基于FPGA/CPLD设计与实现UART(VHDL) 时间:2007-05-08 来源: 作者: 点击:7379 字体大小:【大中小】 1 引言 由于微电子学和计算机科学的迅速发展,给EDA(电子设计自动化)行业带来了巨大的变化。特别是进入20世纪90年代后,电子系统已经从电路板级系统集成发展成为包括ASIC、FPGA/CPLD和嵌入系统的多种模式。可以说EDA产业已经成为电子信息类产品的支柱产业。EDA之所以能蓬勃发展的关键因素之一就是采用了硬件描述语言(HDL)描述电路系统。就FPGA和CPLD开发而言,比较流行的HDL主要有Verilog HDL、VHDL、ABEL-HDL和AHDL 等,其中VHDL和Verilog HDL因适合标准化的发展方向而最终成为IEEE标准。 下面的设计就是用VHDL来完成实现的。 2 UART设计实例 通常设计数字电路大都采用自顶向下将系统按功能逐层分割的层次化设计方法,这比传统自下向上的EDA设计方法有更明显的优势(当时的主要设计文件是电路图)。因为由自顶向下的设计过程可以看出,从总体行为设计开始到最终逻辑综合,形成网络表为止。每一步都要进行仿真检查,这样有利于尽早发现系统设计中存在的问题,从而可以大大缩短系统 硬件的设计周期。 下面以UART的设计为例具体说明:(本设计只对本设计的总模块做各种基于 MAX+PLUS II环境下的各种分析,对于各分模块只是作些必要的说明。)UART(即Universal Asynchronous Receiver Transmitter 通用异步收发器)是一种应用广泛的短距离串行传输接口。UART允许在串行链路上进行全双工的通信。串行外设用到的RS232-C异步串行接口,一般采用专用的集成电路即UART实现。如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了FPGA/CPLD 器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核 心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于FPGA/CPLD 器件设计与实现UART。 2.1 UART简介 2.1.1 UART结构 UART主要有由数据总线接口、控制逻辑、波特率发生器、发送部分和接收部分等组成。 本设计主要设计UART中最重要的发送部分和接收部分,其他部分设计不在赘述。 功能包括发送缓冲器(tbr)、发送移位寄存器(tsr)、帧产生、奇偶校验、并转串、数据接收缓冲器(rbr)、接收移位寄存器(rsr)、帧产生、奇偶校验、串转并。图1是UART 的典型应用。 图1 2.1.2 UART的帧格式 UART的帧格式如图2所示。 图2 包括线路空闲状态(idle,高电平)、起始位(start bit,低电平)、5~8位数据位(data bits)、校验位(parity bit,可选)和停止位(stop bit,位数可为1、1.5、2位)。 这种格式是由起始位和停止位来实现字符的同步。 UART内部一般有配置寄存器,可以配置数据位数(5~8位)、是否有校验位和校验 的类型、停止位的位数(1,1.5,2)等设置。 本设计没有奇偶校验位,所设置的奇偶校验只是检验数据中是否有奇数或偶数个1。数 据位为8位,停止位为1位。 2.2 UART的设计与实现 2.2.1 UART发送器 发送器每隔16个CLK16时钟周期输出1位,次序遵循1位起始位、8位数据位、1位 停止位。 CPU何时可以往发送缓冲器tbr写入数据,也就是说CPU要写数据到tbr时必须判断当前是否可写,如果不判这个条件,发送的数据会出错。本设计由wrn控制。 数据的发送是由微处理器控制,微处理器给出wrn信号,发送器根据此信号将并行数据din[7..0]锁存进发送缓冲器tbr[7..0],并通过发送移位寄存器tsr[7..0]发送串行数据至串行数据输出端sdo。在数据发送过程中用输出信号tbre、tsre作为标志信号,当一帧数据由发送缓冲器tbr[7..0]送到发送发送移位寄存器tsr[7..0]时,tbre信号为1,而数据由发送移位寄存器tsr[7..0]串行发送完毕时,tsre信号为1,通知CPU在下个时钟装入新数据。 发送器端口信号如图3所示。 图3 引入发送字符长度和发送次序计数器no_bits_sent,实现设计的源程序如下。 library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all ; entity txmit is port (rst,clk16x,wrn : in std_logic ; din : in std_logic_vector(7 downto 0) ; tbre : out std_logic ; tsre : out std_logic ; sdo : out std_logic ) ; end txmit ; architecture v1 of txmit is signal clk1x_enable : std_logic ; signal tsr : std_logic_vector (7 downto 0) ; signal tbr : std_logic_vector (7 downto 0) ; signal parity : std_logic ; signal clkdiv : unsigned (3 downto 0) ; --用来控制数据采样时钟的 signal clk1x : std_logic ; signal no_bits_sent : unsigned (3 downto 0) ; signal wrn1 : std_logic ; signal wrn2 : std_logic ; begin process (rst,clk16x) --对wrn进行脉宽处理,以防接收数据错误 begin if rst = '1' then wrn1 <= '1' ; wrn2 <= '1' ; elsif clk16x'event and clk16x = '1' then wrn2 <= wrn1 ; wrn1 <= wrn ; end if ; end process ; process (rst,clk16x) --对clk1x_enable进行控制 begin if rst = '1' then clk1x_enable <= '0' ; tbre <= '1' ; elsif clk16x'event and clk16x = '1' then if wrn1 = '0' and wrn2 = '1' then tbre <= '0' ; clk1x_enable <= '1' ; elsif std_logic_vector(no_bits_sent) = "0010" then tbre <= '1' ; elsif std_logic_vector(no_bits_sent) = "1101" then clk1x_enable <= '0' ; end if ; end if ; end process ; process (rst,wrn) --接收数据至tbr begin if rst = '1' then tbr <= (others => '0') ; elsif wrn'event and wrn = '0' then tbr <= din ; end if ; end process ; process (rst,clk16x,clk1x_enable) begin if rst = '1' then clkdiv <= "0000" ; elsif clk16x'event and clk16x = '1' then if clk1x_enable = '1' then clkdiv <= clkdiv + "0001" ; end if ; end if ; end process ; clk1x <= clkdiv(3) ; --产生clk1x时钟 process (rst,clk1x,no_bits_sent,tbr) begin if rst = '1' then sdo <= '1' ; tsre <= '1' ; tsr <= "00000000" ; parity <= '1' ; elsif clk1x'event and clk1x = '1' then if std_logic_vector(no_bits_sent) = "0001" then tsr <= tbr ; --发送缓冲器tbr数据进入发送移位寄存器tsr tsre <= '0' ; --发送移位寄存器空标志置“0” elsif std_logic_vector(no_bits_sent) = "0010" then sdo <= '0' ; --发送起始位信号“0” elsif std_logic_vector(no_bits_sent) >= "0011" and std_logic_vector(no_bits_sent) <= "1010" then tsr <= tsr(6 downto 0) & '0' ; --从低位到高位进行移位输出至串行输出端sdo sdo <= tsr(7) ; parity <= parity xor tsr(7) ; --数据位中的1校验 end if ; end if ; end process ; process (rst,clk1x,clk1x_enable) --产生发送字符长度和发送次序计数器 begin if rst = '1' or clk1x_enable = '0' then no_bits_sent <= "0000" ; elsif clk1x'event and clk1x = '1' then if clk1x_enable = '1' then no_bits_sent <= no_bits_sent + "0001" ; end if ; end if ; end process ; end ; 2.2.2 UART接收器 串行数据帧和接收时钟是异步的,发送来的数据由逻辑1变为逻辑0可以视为一个数据帧的开始。接收器先要捕捉起始位,确定rxd输入由1到0,逻辑0要8个CLK16时钟周期,才是正常的起始位,然后在每隔16个CLK16时钟周期采样接收数据,移位输入接收移位寄存器rsr,最后输出数据dout。还要输出一个数据接收标志信号标志数据接收完。 接收器的端口信号如图4所示。 图4 引入接收字符长度和接收次序计数器no_bits_rcvd,实现设计的源程序如下。由于与发送器 的一些说明相似,这里就不再重复。 library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all ; entity rcvr is port (rst,clk16x,rxd,rdn : in std_logic ; dout : out std_logic_vector (7 downto 0) ; data_ready : out std_logic ; framing_error : out std_logic ; parity_error : out std_logic ) ; end rcvr ; architecture v1 of rcvr is signal rxd1 : std_logic ; signal rxd2 : std_logic ; signal clk1x_enable : std_logic ; signal clkdiv : unsigned (3 downto 0) ; signal rsr : unsigned (7 downto 0) ; signal rbr : unsigned (7 downto 0) ; signal no_bits_rcvd : unsigned (3 downto 0) ; signal parity : std_logic ; signal clk1x : std_logic ; begin process (rst,clk16x) begin if rst = '1' then rxd1 <= '1' ; rxd2 <= '1' ; elsif clk16x'event and clk16x = '1' then rxd2 <= rxd1 ; rxd1 <= rxd ; end if ; end process ; process (rst,clk16x,rxd1,rxd2,no_bits_rcvd) begin if rst = '1' or std_logic_vector(no_bits_rcvd) = "1100" then clk1x_enable <= '0' ; elsif clk16x'event and clk16x = '1' then if rxd1 = '0' and rxd2 = '1' then clk1x_enable <= '1' ; end if ; end if ; end process ; process (rst,clk16x,rdn,no_bits_rcvd) begin if rst = '1' or rdn = '0' then data_ready <= '0' ; elsif clk16x'event and clk16x = '1' then if std_logic_vector(no_bits_rcvd) = "1100" then data_ready <= '1' ; end if ; end if ; end process ; process (rst,clk16x,clk1x_enable) begin if rst = '1' then clkdiv <= "0000" ; elsif clk16x'event and clk16x = '1' then if clk1x_enable = '1' then clkdiv <= clkdiv + "0001" ; end if ; end if ; end process ; clk1x <= clkdiv(3) ; process (clk1x,rst) begin if rst = '1' then rsr <= "00000000" ; rbr <= "00000000" ; parity <= '1' ; framing_error <= '0' ; parity_error <= '0' ; elsif clk1x'event and clk1x = '1' then if std_logic_vector(no_bits_rcvd) >= "0001" and std_logic_vector(no_bits_rcvd) < "1001" then --- 数据帧数据由接收串行 数据端移位入接收移位寄存器 rsr(0) <= rxd2 ; rsr(7 downto 1) <= rsr(6 downto 0) ; parity <= parity xor rsr(0) ; elsif std_logic_vector(no_bits_rcvd) = "1010" then rbr <= rsr ; --接收移位寄存器数据进入接收缓冲器 elsif parity = '0' then parity_error <= '1' ; elsif std_logic_vector(no_bits_rcvd) = "1001" and rxd2 = '0' then framing_error <= '1' ; end if ; end if ; end process ; process (rst,clk1x,clk1x_enable,no_bits_rcvd) begin if rst = '1' or (std_logic_vector(no_bits_rcvd) = "1100" and clk1x_enable = '0') then no_bits_rcvd <= "0000" ; elsif clk1x'event and clk1x = '1' then if clk1x_enable = '1' then no_bits_rcvd <= no_bits_rcvd + "0001" ; end if ; end if ; end process ; dout <= std_logic_vector(rbr) when rdn = '0' else "ZZZZZZZZ" ; end ; 2.2.3 UART设计总模块 将发送器和接收器模块组装起来,就能较容易地实现通用异步收发器总模块,而且硬件实现不需要很多资源,尤其能较灵活地嵌入到FPGA/CPLD的开发中。 以下给出从模块源代码: library ieee; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all ; use ieee.std_logic_unsigned.all ; entity uart is PORT (rst,clk16x,rxd,rdn,wrn : in std_logic; din : in std_logic_vector(7 downto 0); dout : out std_logic_vector(7 downto 0); data_ready : out std_logic; parity_error : out std_logic; framing_error : out std_logic; tbre : out std_logic; tsre : out std_logic; sdo : out std_logic); end uart; architecture v1 of uart is component txmit port (rst,clk16x,wrn : in std_logic; din : in std_logic_vector(7 downto 0); tbre,tsre,sdo: out std_logic); end component ; component rcvr port (rst,clk16x,rxd,rdn : in std_logic; data_ready, parity_error, framing_error : out std_logic; dout : out std_logic_vector(7 downto 0)); end component ; begin u1 : txmit PORT MAP (rst => rst,clk16x => clk16x,din => din,tbre => tbre,tsre => tsre, sdo => sdo); u2 : rcvr PORT MAP (rst => rst,clk16x => clk16x,rxd => rxd,rdn => rdn,data_ready => data_ready,framing_error => framing_error,parity_error => parity_error,dout => dout) ; end v1 ; 总模块RTL图如图5 图5 SPI串行总线接口的Verilog实现 时间:2007-08-01 来源: 作者:孙丰军余春暄点击:4151 字体大小:【大中小】 摘要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。重点描述了SPI串行总线接口在一款802.11b芯片中的位置,及该接口作为基带和射频的通讯接口所完成的功能,并给出了用硬件描述语言Verilog HDL 实现该接口的部分程序。该实现已经在Modelsim 中完成了仿真, 并经过了FPGA 验证, 最后给出了仿真和验证的结果。 在SOC设计中,利用EDA 工具设计芯片实现系统功能已经成为支撑电子设计的通用平台.并逐步向支持系统级的设计方向发展。而且,在设计过程中,越来越强调模块化设计。 SPI总线是Motorola公司提出的一个同步串行外设接口,具有接口线少、通讯效率高等特点。本文给出的是利用Verilog HDL实现的SPI总线模块,该模块是802.11b无线局域网芯片中一个子模块,该模块完成了芯片中基带(base band)与RF的通讯工作. 1 SPI总线接口概述 SPI(Serial Parallel Bus)总线是Motorola公司提出的一个同步串行外设接口,允许CPU 与各种外围接口器件(包括模/数转换器、数/模转换器、液晶显示驱动器等)以串行方式进行通信、交换信息。他使用4条线:串行时钟线(SCK)、主机输入/从机输出线(MISO)、主机输出/从机输入线(MOSI)、低电平有效的使能信号线(CS)。这样,仅需3~4根数据线和控制线即可扩展具有SPI接口的各种I/O器件其典型结构如图1所示。 SPI总线具有以下特点: (1)连线较少,简化电路设计。并行总线扩展方法通常需要8根数据线、8~16根地址线、2~3根控制线。而这种设计,仅需4根数据和控制线即可完成并行扩展所实现的功能。 (2)器件统一编址,并与系统地址无关,操作SPI独立性好。 (3)器件操作遵循统一的规范,使系统软硬件具有良好的通用性。 2 SPI总线接口的设计与实现 该模块是802.1lb无线局域网芯片中的一子模块,其在芯片中的位置如图2所示。 其中base band(基带)为SPI的主控器(master),RF(射频)为SPI的受控器(slave)。SPI interface作为baseband与RF的通讯接口,主要完成以下工作: (1)将从base band接收到的16位的并行数据,转换为RF所能接收的串行数据,并将该数据根据SPI协议送给RF。 (2)产生RF所需的时钟信号SCLK,使能信号CSB。 (3)接收从RF传回的串行数据,并将其转换为并行数据。 (4)将base band发送的数据,与RF返回的数据进行比较,并把比较结果传给base band。 下面给出用Verilog HDL语言实现前两项功能的关键程序,相关变量的声明在此略去。//generate a counter always@ (posedge clock or negedge reset) begin if(!reset) counter<= 0; else if(enable) begin if(counter< 53) counter=counter + 1; end end //generate signal "csb" always@ (posedge clock or negedge reset) begin if(!reset) csb <=1; else if(counter>= 1 && counter <= 50) csb = 0; else csb = 1; end //Generate "sclk" always@ (posedge clock or negedge reset) begin case(counter) 6'd02: sclk = 1; 6'd05: sclk = 1; 6'd08: sclk = 1; 6'd11: sclk = 1; 6'd14: sclk = 1; 6'd17: sclk = 1; 6'd20: sclk = 1; 6'd23: sclk = 1; 6'd26: sclk = 1; 6'd29: sclk = 1; 6'd32: sclk = 1; 6'd35: sclk = 1; 6'd38: sclk = 1; 6'd41: sclk = 1; 6'd44: sclk = 1; 6'd47: sclk = 1; default sclk = 0; end always@ (counter or csb) begin if(csb == 0) case(counter) 6'h00, 6'h01, 6'h02, 6'h03:mosi_index = 5'h00; 6'h04, 6'h05, 6'h06:mosi_index = 5'h01; 6'h07, 6'h08, 6'h09:mosi_index = 5'h02; 6'h0A, 6'h0B, 6'h0C:mosi_index = 5'h03; 6'h0D, 6'h0E, 6'h0F:mosi_index = 5'h04; 6'h10, 6'h11, 6'h12:mosi_index = 5'h05; 6'h13, 6'h14, 6'h15:mosi_index = 5'h06; 6'h16, 6'h17, 6'h18:mosi_index = 5'h07; 6'h19, 6'h1A, 6'h1B:mosi_index = 5'h08; 6'h1C, 6'h1D, 6'hlE:mosi_index = 5'h09; 6'h20, 6'h21:mosi_index = 5'h0A ; 6'h22, 6'h23, 6'h24:mosi_index = 5'h0B; 6'h25, 6'h26, 6'h27:mosi_index = 5'h0C ; 6'h28, 6'h29, 6'h2A:mosi_index = 5'h0D ; 6'h2B, 6'h2C, 6'h2D:mosi_index = 5'h0E; 6'h2E, 6'h2F, 6'h30:mosi_index = 5'h0F; default:mosi_index = 5'h00; endcase else mosi_index = 5'h00: end assign mosi=spi_data[mosi_index3]; (声明:以上程序已经过修改,只供借鉴,不可用作商业用途) 用Verilog HDL实现的SPI总线接口模块,在ModelSim 中编译、调试,并做了前仿真。 前仿真通过后,又在Altera公司的EPXA10 Develop Board上做了FPGA验证,结果与在ModelSim 中的仿真结果一致。最后在base band与RF的联合调试过程中,该SPI总线接口模块达到了预期的要求。 参考文献 [1] 任志斌,车长征.串行外设接口SPI的应用[J].电子技术应用,2002,29(10):20-22. [2] 易志明.SPI串行总线接口及其实现[j].自动化与仪器仪表,2002,(6):45-48. [3] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003. 在FPGA中实现SPI与总线接口转换 时间:2007-06-22 来源: 作者:刘伯栋点击:2216 字体大小:【大中小】 摘要:FPGA和CPLD可编程逻辑器件具有可编程的特点,这为不同接口之间转换提供了灵活性。具有SPI接口或总线接口的各种芯片在电路设计中的应用日益广泛。为了能够对这些芯片进行设置以及实现相互之间的数据传输,往往需要在它们之间进行接口转换。主要介绍了在FPGA中通过时接口时序和接口速率的处理,实现SPI接口与总线接口转换,完成了M68HC912832和P89C5lRD2FA之间的数据双向传输,并给出了实现方案、仿真结果以及硬件调试结果。 1 引言 随着印刷电路板设计向着密集化、多功能化和小型化的方向发展,电路板上通常配置了多种不同芯片,为了能够对这些芯片进行设置以及实现相互之间的数据传输,往往需要在它们之间进行接口转换。 FPGA和CPLD等可编程逻辑器件具有现场可编程、逻辑资源丰富以及集成度高等特点,通过FPGA或者CPLD进行接口转换,具有很强的灵活性,因此在电路设计中被广泛应用。 2 器件介绍 本文主要介绍在FPGA中实现SPI接口与总线接口的转换,其中选用的芯片是:Motorola 公司的M68HC912B32,Philips公司的P89C51RD2FA,FPGA是Xilinx公司SPARTANⅡE系列中xc2s600e。接口之间的连接关系如图1所示,图中省去了电平适配的考虑。 M68HC912B32是Motorola公司的一款16bit微处理器。它具有32kbyte的FLASH EEPROM空间,1kbyte的RAM空间。该处理器含有丰富的外 部接口单元,除了同步串行外设接口(SPI),还有异步串行通信接口(SCII),8通道10bit的A/D转换器,以及4通道8bit或2通道16bit的脉宽调制 器(PWM)等。M68HC912832具有较强的处理能力,加上丰富的外设资源,使得该处理器在多种终端设备中得到应用。 P89C51RD2FA是Philips公司的一款单片机。P89C51RD2FA具有64kbyte的Flash EPROM,1kbyte的BOOTROM,用于在系统编程。与其他单片机相比,P89C51RD2FA具有在系统可编程的特点。通过改变P89C51RD2FA引脚psen接地,用标准串行接口,由普通 说明ARM、DSP、FPGA的异同点 ARM(Advanced RISC Machines)是微处理器行业的一家知名企业,设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。ARM架构是面向低预算市场设计的第一款RISC微处理器,基本是32位单片机的行业标准,它提供一系列内核、体系扩展、微处理器和系统芯片方案,四个功能模块可供生产厂商根据不同用户的要求来配置生产。由于所有产品均采用一个通用的软件体系,所以相同的软件可在所有产品中运行。目前ARM在手持设备市场占有90以上的份额,可以有效地缩短应用程序开发与测试的时间,也降低了研发费用。 DSP(digital signal processor)是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。一个数字信号处理器在一块不大的芯片内包括有控制单元、运算单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。DSP采用的是哈佛设计,即数据总线和地址总线分开,使程序和数据分别存储在两个分开的空间,允许取指令和执行指令完全重叠。也就是说在执行上一条指令的同时就可取出下一条指令,并进行译码,这大大的提高了微处理器的速度。另外还允许在程序空间和数据空间之间进行传输,因为增加了器件的灵活性。其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。它的强大数据处理能力和高运行速度,是最值得称道的两大特色。由于它运算能力很强,速度很快,体积很小,而且采用软件编程具有高度的灵活性,因此为从事各种复杂的应用提供了一条有效途径。 当然,与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。(缺点) 区别: ⒈我做个比喻吧,ARM呢就像是一个设计好的办公楼,那个部门负责什么事情都是定好的,你要做的就是合理调配部门资源合理搭配来完成你的目的。FPGA呢就是给你一大堆建筑材料和人员,你要它建成什么样子它就是什么样子 ⒉FPGA就像是一张白纸,里面可以写自己想要的逻辑,只要FPGA的逻辑门数够多,里面跑个ARM核还是很简单的。ARM是ASIC吧,专用芯片,只能使用。 ⒊DSP主要用做运算,如语音,图像等信号的运算处理,但基本不用做控制。 MCU,FPGA,ARM主要用做控制,MCU低价低功耗,但门限很少,结构简单,不能实现复杂控制。 ARM控制能力较强,但运算能力相对较弱。因此现在很多手持设备是用ARM+DSP来实现的,就是所谓的“双核心”。 FPGA可做复杂的逻辑控制,功能很强大。 ⒋单片机(MCU),又称为微控制器,在一块半导体芯片上集中了CPU,ROM,RAM,I/O Interface, timer/counter, interrupt system, 构成一台完整的数字计算机 ARM(Advanced RISC Machines)是微处理器行业的一家知名ARM企业,设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。ARM架构是面向低预算市场设计的第一款RISC微处理器,基本是32位单片机的行业标准,它提供一系列内核、体系扩展、微处理器和系统芯片方案,四个功能模块可供生产厂商根据不同用户的要求来配置ARM生产。由于所有产品均采用一个通用的软件体系,所以相同的软件可在所有产品中运行。目前ARM在手持设备市场占有90以上的份额,可以有效地缩短应用程序开发与测试的时间,也降低了研发费用。这里有一篇介绍ARM结构体系发展介绍。 DSP(digital singnal processor)是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。一个数字信号处理器在一块不大的芯片内包括有控制单元、运算单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。DSP采用的是哈佛设计,即数据总线和地址总线分开,使程序和数据分别存储在两个分开的空间,允许取指令和执行指令完全重叠。也就是说在执行上一条指令的同时就可取出下一条指令,并进行译码,这大大的提高了微处理器的速度。另外还允许在程序空间和数据空间之间进行传输,因为增加了器件的灵活性。其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。它的强大数据处理能力和高运行速度,是最值得称道的两大特色。由于它运算能力很强,速度很快,体积很小,而且采用软件编程具有高度的灵活性,因此为从事各种复杂的应用提供了一条有效途径。 FPGA既现场可编程门阵列:可由最终用户配置、实现许多复杂的逻辑功能的通用逻辑器件。常用于原型逻辑硬件设计。 ARM、DSP、FPGA的特点和区别 2008年05月09日星期五 16:33 ARM(Advanced RISC Machines)是微处理器行业的一家知名企业,设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。ARM架构是面向低预算市场设计的第一款RISC 微处理器,基本是32位单片机的行业标准,它提供一系列内核、体系扩展、微处理器和系统芯片方案,四个功能模块可供生产厂商根据不同用户的要求来配置生产。由于所有产品均采用一个通用的软件体系,所以相同的软件可在所有产品中运行。目前ARM在手持设备市场占有90以上的份额,可以有效地缩短应用程序开发与测试的时间,也降低了研发费用。 DSP(digital signal processor)是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。一个数字信号处理器在一块不大的芯片内包括有控制单元、运算单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。DSP采用的是哈佛设计,即数据总线和地址总线分开,使程序和数据分别存储在两个分开的空间,允许取指令和执行指令完全重叠。也就是说在执行上一条指令的同时就可取出下一条指令,并进行译码,这大大的提高了微处理器的速度。另外还允许在程序空间和数据空间之间进行传输,因为增加了器件的灵活性。其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。它的强大数据处理能力和高运行速度,是最值得称道的两大特色。由于它运算能力很强,速度很快,体积很小,而且采用软件编程具有高度的灵活性,因此为从事各种复杂的应用提供了一条有效途径。根据数字信号处理的要求,DSP芯片一般具有如下主要特点: (1)在一个指令周期内可完成一次乘法和一次加法; (2)程序和数据空间分开,可以同时访问指令和数据; (3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问; (4)具有低开销或无开销循环及跳转的硬件支持; (5)快速的中断处理和硬件I/O支持; (6)具有在单周期内操作的多个硬件地址产生器; (7)可以并行执行多个操作; (8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。 当然,与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。 FPGA是英文Field Programmable Gate Array(现场可编程门阵列)的缩写,它是在PAL、 FPGA和ARM和STM32和DSP区别 2012-12-02|分享 越详细越好,谢谢大侠们 10分钟内有问必答前往下载 满意回答 1.FPGA:是可编程逻辑阵列,常用于处理高速数字信号,不过随着科技的发展,现在很多FPGA CPLD可以集成mcu内核,甚至具备了ARM DSP的功能 2.ARM,是一类内核的称谓,就像51一样,具体到芯片的话,会有很多不同的厂家不同等级,诸如三星、易法、飞利浦、摩托罗拉等等,其中STM32是易法半导体的一款面向工控低功耗内核为Cortex M3内核的ARM芯片 3.DSP顾名思义就是数字信号处理,厂家主要是德州仪器(TI)主要用于数字型号处理等对运算速度有特殊要求的场合,诸如音频视频算法,军工等领域,但同时dsp有2000 5000 6000等系列也可满足不场合需要! 其他想要了解,可以追问,相互探讨哈! 追问 他们主要的应用领域,那个应用广泛点呢 回答 应用领域的话 1.FPGA一般不会用来做复杂的系统,只用来做些简单的系统如状态机实现的自动售货机...展开>等,多少还是用来做信号的高速变换和处理,毕竟它只是可编程逻辑阵列。 2.ARM和DSP就各有千秋了; ARM的系列从V3 V5 V7 V9 XSCALE,从thumb指令到arm指令(thumb arm也可同时实现),可以说遍布机会所有的领域,只要你接的价格可以接受(其实许多arm并不是很贵的),单片机所有的功能基本他都能实现,我就不用举例子,特别是现在与各种RTOS结合更是开发方便功能强大。 DSP相对arm价格要贵些,这也是可能个体厂家使用较少的一个原因吧,2000系列主要用于工控特别是2812这个用的人比较多,5000 6000主要用于手持设备、PDA、通信等领域; DSP还有一个特色就是对一些特殊算法的支持如快速福利叶变换等,所以对运算速度有特殊要求的场合一般会选择DSP; DSP因其性能和功能比较好,还广泛用于军工领域!<收起 清华大学 硕士毕业论文报告 课程名称:嵌入式系统课程设计 专业班级:应用电子技术09201班 学生姓名:崔剑 指导教师:袁里弛 完成时间:2011年12月26日 报告成绩: 评阅意见: 评阅教师日期 目录 第一章系统设计方案和主要器件选型 (2) 1.1 系统设计方案 (2) 1.2 ADC芯片选型 (2) 1.3 DA芯片选型 (2) 1.4 FPGA芯片选型 (3) 1.5 主控CPU选型 (3) 第二章数据采集与触发电路设计 (4) 2.1 前端采集电路设计 (4) 2.2 触发电路与触发控制 (5) 2.3 SDRAM控制器设计 (6) 第三章各芯片间的数据传输与处理 (7) 3.1 采集卡各芯片速度等级的划分和数据流向 (7) 3.2 ARM与FPGA通信 (7) 3.3 数据的模拟输出 (8) 第四章设计总结 (13) 参考文献 (13) 附录1 ARM外围电路 (14) 附录2 FPGA外围电路 (15) 附录3 ARM读取显示程序 (20) 第一章 系统设计方案和主要器件选型 1.1 系统设计方案 整个系统是由前端模拟通道、触发电路、FPGA 数据采集预处理、数据模拟输出和ARM 数据处理显示五部分组成。FPGA 数据采集预处理分为A/D 数据采集、触发控制、帧控制、SDRAM 控制器和ARM 数据交换五个部分,模拟数据经过A/D 装换后在FPGA 中缓冲,缓冲之后使用触发控制将采集到的数据分成512个数据点组成的数据帧,数据按照帧的顺序传输,经过SDRAM 存储后,通过ARM 与FPGA 中的共享存储区传输给ARM 。具体的数据采集系统的硬件结构图如下图2-1所示: 图2-1 数据采集卡硬件结构图 1.2 ADC 芯片选型 A/D 转换器是整个采集系统的核心,系统前端模拟电压调理电路、FPGA 数据采集和后端的采集控制部分都与A/D 直接相关,A/D 芯片的选择不但关系到系统设计的性能,而且直接决定了整板设计的难度。 1.3 DA 芯片选型 为了输出高性能的模拟信号,DAC 采用采样率高达175M 的高速DAC 。AD970X 系列DAC 针对低功耗特性进行了优化,同时仍保持出色的动态性能,适合用于手持便携式仪器等需要有效地合成宽带信号的场合。AD9707 精度高达14位 ,采样率为175MSPS ,内部集成边沿触发式输入锁存器,1V 温度补偿带隙基准电压源和自校准功能,使AD9707能提供真14位INL 与DNL 性能。 FPGA AD ARM 模 拟通道 SDRAM PLL DA GPIO 触发电路GPIO 晶振 复位JTAG FLASH SDRAM LCD UART 数据总线控制线 配置线 模拟输入 模拟输出时钟 地址总线 说明ARM、DSP、FPGA的异同点 3 ARM(Advanced RISC Machines)是微处理器行业的一家知名企业,设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。ARM架构是面向低预算市场设计的第一款RISC微处理器,基本是32位单片机的行业标准,它提供一系列内核、体系扩展、微处理器和系统芯片方案,四个功能模块可供生产厂商根据不同用户的要求来配置生产。由于所有产品均采用一个通用的软件体系,所以相同的软件可在所有产品中运行。目前ARM在手持设备市场占有90 以上的份额,可以有效地缩短应用程序开发与测试的时间,也降低了研发费用。 DSP(digital signal processor)是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。一个数字信号处理器在一块不大的芯片内包括有控制单元、运算单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。DSP采用的是哈佛设计,即数据总线和地址总线分开,使程序和数据分别存储在两个分开的空间,允许取指令和执行指令完全重叠。也就是说在执行上一条指令的同时就可取出下一条指令,并进行译码,这大大的提高了微处理器的速度。另外还允许在程序空间和数据空间之间进行传输,因为增加了器件的灵活性。其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。它的强大数据处理能力和高运行速度,是最值得称道的两大特色。由于它运算能力很强,速度很快,体积很小,而且采用软件编程具有高度的灵活性,因此为从事各种复杂的应用提供了一条有效途径。 当然,与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。 FPGA是英文Field Programmable Gate Array(现场可编程门阵列)的缩写,它是在PAL、GAL、PLD等可编程器件的基础上进一步发展的产物,是专用集成电路(ASIC)中集成度最高的一种。FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB (Input Output Block)和内部连线(Interconnect)三个部分。用户可对FPGA内部的逻辑模块和I/O模块重新配置,以实现用户的逻辑。它还具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改。作为专用集成电路(ASIC)领域中的一种半定制电路,FPGA既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。可以毫不夸张的讲,FPGA能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA来实现。FPGA如同一张白纸或是一堆积木, 在数据采集卡中ARM主要负责数据显示和数据分析,处理的速度处于MS 级;而FPGA在系统中处于数据的高速采集和高速处理,处理的速度是ns级。两个处理器的之间的数据传输属于典型的异步数据通信,它们之间通信的速度之间决定了系统处理数据的效率。FPGA与ARM之间属于大量数据交换,以异步并行读取的方式为例介绍ARM与FPGA的通信,实际设计中使用DMA方式来实现ARM 与FPGA之间的大数据量通信。 ARM存储系统分析 S3C2410A存储控制器提供访问外部存储器所需要的存储器控制信号。 S3C2410A支持大、小端模式,将存储空间分为8个组(Bank),每组大小是128M,共计1GB,如图1所示。所有存储器组都可用于ROMA或者SRAM,Bank6、Bank7还可以用于SDRAM。所有内部块的访问周期都可编程。总线访问周期可以通过插入外部等待来延长,支持SDRAM的自刷新和掉电模式。Bank0~Bank6的开始地址是固定的,Bank7的开始地址是Bank6的结束地址,灵活可变,并且Bank7的大小与Bank6的大小必须相等。除Bank0外,其余各存储器的总线宽度可编程设置为8位、16位或者32位,但是Bank0只支持16位或者32位。Bank0作为引导ROM,地址映射到0x0000_0000。OM[1:0]是系统的引导模式控制引脚,在复位时,系统将检测OM[1:0]上的逻辑电平,并根据这个电平来决定Bank0区存储器的总线宽度。 图1 ARM存储单元分配图 在设计中ARM的bank0用于Nor Flash,bank6和bank7用于两块SDRAM,我们选择bank4作为FPGA内部RAM映射的空间。Bank4在ARM的统一基地址为0x20000000,后面的采集的数据都是基于这个地址为首地址的。 ARM与FPGA通信接口板设计 关键词:双口RAM;乒乓操作;流控机制1 概述 某项目中需设计一块通信接口板,实现ARM 2440核心板和FPGA信号处理板之间的通信,因该板交换速率达到10Mbps,要求不能频繁中断ARM处理器,且具备流控机制,设计上有一定难度,基于双口RAM设计了乒乓操作机制和流控机制,有效地降低了系统负荷。 2 电路及驱动设计 2.1 接口板电路设计 接口板基于两片双口RAM芯片IDT CY7C007AV实现,电路示意图如图1所示。每片CY7C007AV有8KB的存储空间,12位地址总线,8位数据总线。为提高端口读写效率,FPGA对ARM发送时采用乒乓操作方式,ARM对FPGA发送时采用流控方式。 由于核心板扩展槽的地址总线和数据总线位宽限制,采用两片双口RAM,一片供FPGA向ARM发送数据用,另一片供ARM向FPGA发送数据用,以下分别建成上部双口RAM和下部双口RAM。上部双口RAM分为两部分,供FPGA采用乒乓操作方式写入数据,FPGA写完上半部后通过在EINT5上产生上升沿中断通知ARM,写完下半部后通过通过在EINT6上产生上升沿中断通知ARM。下部双口RAM供ARM向FPGA写入数据,其接线方式与上部双口RAM类似。 两块双口RAM的电路采用对称方式,其电路如图2所示。两片双口RAM可以互换,下部双口RAM也可供FPGA写入数据,而ARM则写入上部双口RAM。在实际测试中,两种方式均测试过。 ARM与双口RAM连接时,采用SRAM时序,为避免/减弱二次反射,ARM与总线驱动之间加33欧的串联匹配电阻,匹配电阻靠近扩展槽的近端。FPGA端对双口RAM的读写也采用SRAM时序,在与双口RAM连接时均串了33欧姆的匹配电阻。 由于核心板上ARM处理器距离接口板较远,接近十厘米,且核心板为四层板,总线驱动能力较弱,在ARM处理器和双口RAM之间添加四片总线驱动芯片,除增加总线驱动能力外还可通过关断总线驱动芯片,避免接口板噪声干扰核心板。 ARM的8位数据线通过245总线驱动芯片引出,其方向由LnOE读信号控制,地址总线则采用244和541芯片实现。ARM读时,数据由245流向ARM侧,ARM写时,数据由245流向双口RAM一侧。中断信号线连接在244芯片上,数据线连 详解ARM处理器和FPGA之间的通信技术 1前言在ARM+FPGA系统结构中,实现基于ARM的嵌入式处理器和FPGA之间通信最简单的方法就是通过异步串行接口EIARS232C。考虑选用集成有UART(Universal Asynchronous Receiver / TraNSmitter )控制器的嵌入式处理器(例如,EP7312),那么嵌入式处理器一侧就具有了利用异步串行接口收、发通信的能力。然而,FPGA内部并不拥有CPU控制单元,无法处理由UART控制器产生的中断,所以FPGA 一侧不能利用现成的UART控制器构成异步串行接口,必须将UART控制器的功能集成到FPGA内部。 同一个系统中的ARM与FPGA之间属于短距离通信连接,他们之间的异步串行通信并不需要完整的UART功能,那些RS232标准中的联络控制信号线可以省略,仅仅保留收、发数据线和地线,这样给UART功能的FPGA编程实现带来了极大的省略。嵌入式处理器EP7312带有2个支持异步串行通信RS232的16550类型的UART,UART1不仅有TX,RX,而且支持Modem控制信号,UART2只有标准的TX,RX以及地信号,刚好能够利用UART2与FPGA实现通信。 2简化UART功能的FPGA实现本文将详细地讨论简化UART功能在FPGA中的实现方法。简单回顾一下异步串行通信的数据格式。图2表明在异步传送中串行发送一个数据字节的位定时关系(图中没有包括奇偶校验位)。发送一个完整的字节信息,首先是一个作为起始位的逻辑0位,接着是8个数据位,然后是1个、1+1/2个或2个停止位逻辑1位,数据线空闲时呈现为高或1状态。在字符的8位数据部分,先发送数据的最低位,最后发送最高位。每位持续的时间是固定的,由发送器本地时钟控制,每秒发送的数据位个数,即为波特率。起始位和停止位起着很重要的作用。显然,他们标志每个字符的开始和结束,但更重要的是他们使接收器能把他的局部时钟与每个新开始接收的字符再同步。异步通信没有可参照的时钟信号,发送器随时都可能发送数据,任何时沿的出现时间,从而正确地采样紧接着的10~11位(包括开始位、数据位和停止位)。接收器的时钟与发送器的时钟不 1.引言 STM32是ST(意法半导体)公司推出的基于ARM内核Cortex-M3的32位微控制器系列。Cortex-M3内核是为低功耗和价格敏感的应用而专门设计的,具有突出的能效比和处理速度。通过采用Thumb-2高密度指令集,Cortex-M3内核降低了系统存储要求,同时快速的中断处理能够满足控制领域的高实时性要求,使基于该内核设计的STM32系列微控制器能够以更优越的性价比,面向更广泛的应用领域。 STM32系列微控制器为用户提供了丰富的选择,可适用于工业控制、智能家电、建筑安防、医疗设备以及消费类电子产品等多方位嵌入式系统设计。STM32系列采用一种新型的存储器扩展技术——FSMC,在外部存储器扩展方面具有独特的优势,可根据系统的应用需要,方便地进行不同类型大容量静态存储器的扩展。 2.FSMC机制 2.1FSMC技术优势 ①支持多种静态存储器类型。STM32通过FSMC町以与SRAM、ROM、PSRAM、NOR Flash 和NANDFlash存储器的引脚直接相连。 ②支持丰富的存储操作方法。FSMC不仅支持多种数据宽度的异步读/写操作,而且支持对NOR/PSRAM/NAND存储器的同步突发访问方式。 ③支持同时扩展多种存储器。FSMC的映射地址空间中,不同的BANK是独立的,可用于扩展不同类型的存储器。当系统中扩展和使用多个外部存储器时,FSMC会通过总线悬空延迟时间参数的设置,防止各存储器对总线的访问冲突。 ④支持更为广泛的存储器型号。通过对FSMC的时间参数设置,扩大了系统中可用存储器的速度范围,为用户提供了灵活的存储芯片选择空间。 ⑤支持代码从FSMC扩展的外部存储器中直接运行,而不需要首先调入内部SRAM。 # FSMC内部结构 STM32微控制器之所以能够支持NOR Flash和NAND Flash这两类访问方式完全不同的存储器扩展,是因为FSMC内部实际包括NOR Flash和NAND/PC Card两个控制器,分别支持两种截然不同的存储器访问方式。在STM32内部,FSMC的一端通过内部高速总线AHB连 工程师深谈ARM+FPGA的设计架构 最近学习了ARM+FPGA的设计架构,ARM和FPGA结构的通信大致可以分为两种: 一种是数据量小、通信速率要求不高的情况,可以考虑采用SPI、IIC等差UN星通信方式。ARM都带有相关的SPI通信控制器等,在ARM端直接对相关的SPI通信控制器操作就可以了。而FPGA这一端可作为SPI从,按照SPI协议的时序写好从设备接口,这个工作量没有多大,所以相对都比较容易。 另一种是数据量大、通信速率要求较高的情况,就要采用并行总线的方式了。这时把FPGA 当做ARM的一个片外的SRAM访问就可以,可以在FPGA内部生成一个双口RAM,输出的数据总线管腿直接连接到ARM的并行总线的数据总线上,双口RAM一端的地址总线也一样直接连接到ARM的并行总线中的地址总线。这样就可以实现FPGA从DPRAM 一端读写,ARM从DPRAM的另一端读写的功能了,当然还需要其他一些使能或片选的控制信号。这里FPGA一侧较好实现,而ARM一侧需要开发SRAM(FPGA)驱动,这个还没有实际做过,所以没有把握。 NXP的ARM即LPC系列的并行总线称之为外扩地址与数据总线,由EMC(外部存储器控制器)控制,通过对EMC寄存器的控制就可以实现在外扩地址和数据总线上的数据收发。若是采用LPC系列ARM加一片FPGA,实现他们通信的关键应该在于这个EMC寄存器的控制,不知道按照一定的顺序操作这个寄存器组写出来的数据收发程序是不是就可以称之为所谓的驱动,求大神解释。 TI的ARM或DSP都有一个GPMC(通用内存控制器),它类似于LPC的EMC,是TI 的芯片中用于与外部存储设备如NORFLASH、NANDFLASH、SRAM等通信的一个借口。对于这个同样也有上边的那个疑问。 三星的S5PV210则是有一组并行总线接口,称之为SROM,同样也有一个SROM控制器, FPGA与ARM核结合实现功能互补 时间:2012-08-20 11:08:35 来源:作者: 关键字:FPGA ARM 随着FPGA技术的不断发展和创新,使RISC处理器与FPGA集成、两种系统的融合与优化成为新一代FPGA的发展趋势。 如今,FPGA技术正处在高速发展时期,芯片规模越来越大,集成度越来越高,速度不断提高,性能不断提升,功耗也越来越低。FPGA凭借其强大的并行信号处理能力,在应对控制复杂度低、数据量大的运算时具有较强的优势。但是在复杂算法的实现上,FPGA却远没有32位精简指令集计算机(RISC)处理器灵活方便,所以在设计具有复杂算法和控制逻辑的系统时,往往需要RISC和FPGA结合使用。这样,电路设计的难度也就相应地增加。 RISC和FPGA结合成发展趋势 RISC处理器与FPGA集成,减小了硬件电路的复杂性和体积,降低了功耗,提高了可靠性。 FPGA技术的不断发展和创新使RISC处理器与FPGA集成,从而大大减小了硬件电路复杂性和体积,同时也降低了功耗,提高了系统可靠性,两种系统的融合与优化成为新一代FPGA的发展趋势。 2010年,FPGA厂商Xilinx和Altera先后联手英国ARM公司瞄准下一代消费电子、汽车及工业电子应用领域,推出了各自的FPGA内嵌ARM硬核嵌入式处理器架构。与传统嵌入式微处理器概念不同,基于ARM的FPGA单片系统通过内部高速总线有效的提升系统间信号传递的速度与稳定性,摆脱了PCB布线线宽对信号带宽的限制。在降低PCB布局布线复杂程度的同时,极大程度地缩小了芯片尺寸。作为高性能、低成本协处理器的最佳选择,FPGA 为处理器提供了硬件加速的空间。同时,FPGA庞大的可编程逻辑资源与灵活的可重配置能力使系统级芯片可以在内部进行软、硬件升级,解决了由升级系统功能带来的更换外部设备带来的成本问题。 作为迈入嵌入式系统领域的第一步,Altera和Xilinx(赛灵思)都成功地将片上系统硬核融入可编程逻辑。其中Xilinx仅与ARM合作,而Altera则提供更多嵌入式硬核的种类。然而两种系统的组合均可以根据实际应用需求进行优化与裁剪。Altera和Xilinx在2011年提出了以ARM为核心的可扩展式处理器平台。其中可编程逻辑仅作为可访问硬件资源被集成在ARM系统中。较以往的ARM处理器,这种可拓展式的嵌入式平台具有动态配置可编程逻辑的功能,可在需要时提升处理器速度,扩展处理器缓存容量。在FPGA与ARM系统接口方面,赛灵思提出的带有可编程逻辑的ARM系统解决了将FPGA嵌入ARM核方案中遇到的带宽问题。 FPGA与ARM核结合实现功能互补 两种高集成度芯片的融合将对已有的基于ARM和FPGA嵌入式系统重新定义。 FPGA与ARM融合的价值不仅仅体现在处理器性能的提升上。 用于视频监控领域的基于ARM的FPGA能够进行高级决策与控制处理,并管理复杂的控制系统结构和多个并行数据接入,同时进行高性能低延迟的信号处理,以通过分布式/远程智能视频系统对各种行为进行监控、分析和比较,并做出正确的行为决策。用于汽车电子领域的ARM嵌入式系统能够方便的连接到最新传感器技术,通过可编程逻辑的高性能并行处理能力处理多个数字信号输入(视频、雷达、红外等),并能快速将数据传输给ARM处理系统进行分析、比较,然后做出反应,并在汽车电子系统框架中进行通信。另外,用于通信领域的FPGA芯片内部集成了高频无线收发模块。该类型FPGA与ARM的结合将给软件无线电提供片 fpga arm dsp区别 2010-07-10 18:09 FPGA 区别于ASIC设计属于硬件设计的范畴ASIC是硬件全定制FPGA是硬件半定制 具体来说ASIC整个电路都由设计师设计的用多少资源设计多少资源一般多用于产品设计 FPGA资源事先由厂商给定例如Altera Xilinx等都提供不同系列的FPGA芯片设计师可以在给定资源下做硬件设计开发 DSP 主要用于处理信号事先算法特点是多级流水可以加快数据处理的速度开发环境主要是C语言可以说DSP应用的范围更专DSP的设计 可以理解为软件设计设计师不需要太了解DSP的结构 补充几个小概念 DSP愿意就是指数字信号处理只不过DSP芯片由于主要功能是实现数字信号处理实现各种算法所以简称为DSP(数字信号处理器) FPGA一样可以做DSP(数字信号处理),就意味着可以用FPGA做硬件设计来实现DSP芯片的功能,当然,相比较专业的DSP芯片成本太高 现在除了FPGA和DSP之外还有一个近几年热门的产品ARM ARM主要应用与手持设备和嵌入式产品几乎笼罩了90%的市场份额可以说ARM开发也偏向于软件开发设计者主要是讲wince系统或者 linux系统移植到ARM开发平台上,然后做各种软件应用开发 所以这三个方向都有其不同的应用场合很难讲谁更有前途不过作为我个人而言更喜欢做硬件设计所以我选择FPGA作为自己的方向FPGA 主要是给设计者提供了一个硬件平台开发的核心还是需要独立的应用设计和高效的算法设计所以设计者应该处理好工具的掌握和具体设 计的区别 这世界真是疯了,貌似有人连FPGA原理是什么都不知道就开始来学习FPGA了。 DSP就是一个指令比较独特的处理器。它虽然是通用处理器,但是实际上不怎么“通用”。技术很牛的人可以用DSP做一台电脑出来跑windows,而实际上真正这么干的肯定是蠢材。用DSP做信号处理,比其他种类的处理器要厉害;用DSP做信号处理之外的事情,却并不见长。而且信号处理的代码一般需要对算法很精通的人才能真正写好。数据结构里面的时间复杂度和空间复杂度在这里是一把很严酷的尺子。 FPGA只不过披着软件的外衣,实际上是硬件。FPGA内部有两层相对独立的电路。使用者“编码->编译”后生成一个映像,这个映像作用于第一层电路。这层电路之际上就是一个0,1的开关矩阵,这个开关矩阵用来控制第二层工作电路,将第二层工作电路配置成一个相应的处理器。理论上FPGA可以配置成任何需要的处理器,而实际上为了尽量少出bug,FPGA开发都使用已经开发好的“库文件”,也就是把人家能稳定工作的电路图拿过来。因此,对大多数FPGA开发者来说,FPGA内部有几个核基本上只能从库文件里面选——除非你有能力自己设计核心内部的电路和核间总线——ram和rom也是用宏来配置,自己只需要改改外部的专用电路和接线方式等等。甚至外部的专用电路都有库文件,搭个积木就完事了。玩FPGA真正挣钱的人是做积木的人,你原创几个积木并且能申请专利,迫使人家给你交专利费,那你这辈子可以衣食无忧了。 -----------------------------------------------------------------------------------------------------------------------------------ARM、DSP、FPGA的特点和区别

FPGA与ARM的关系

ARM、DSP、FPGA的特点和区别

FPGA和ARM和STM32和DSP区别

基于ARM和FPGA的高速数据采集卡的设计与实现 (1)

ARM、DSP、FPGA的特点和区别

ARM与FPGA通信

ARM与FPGA通信接口板设计.

详解ARM处理器和FPGA之间的通信技术

STM32与FPGA+之间的FSMC通信

工程师深谈ARM+FPGA的设计架构

FPGA与ARM核结合实现功能互补

fpga arm dsp区别