位同步信号提取实验

一、实验目的

1、掌握用数字锁相环提取位同步信号的原理及其对信息代码的要求。

2、掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念。

二、实验内容

1、观察数字锁相环的失锁状态和锁定状态。

2、观察数字锁相环锁定状态下位同步信号的相位抖动现象及相位抖动大小与固有频差的关系。

3、观察数字锁相环位同步器的同步保持时间与固有频差之间的关系。

三、实验仪器

1、信号源模块

2、同步信号提取模块

3、20M双踪示波器一台

四、实验原理

4.1、电路分析

位同步也称为位定时恢复或码元同步。在任何形式的数字通信系统中,位同步都是必不可少的,无论数字基带传输系统还是数字频带传输系统,无论相干解调还是非相干解调,都必须完成位同步信号的提取,即从接收信号中设法恢复出与发端频率相同的码元时钟信号,保证解调时在最佳时刻进行抽样判决,以消除噪声干扰所导致的解调接收信号的失真,使接收端能以较低的错误概率恢复出被传输的数字信息。因此,位同步信号的稳定性直接影响到整个数字通信系统的工作性能。

位同步的实现方法分为外同步法和自同步法两类。由于目前的数字通信系统广泛采用自同步法来实现位同步,故在此仅对位同步中的自同步法进行介绍。采用自同步法实现位同步首先会涉及两个问题:(1)如果数字基带信号中确实含有位同步信息,即信号功率谱中含有位同步离散谱,就可以直接用基本锁相环提取出位同步信号,供抽样判决使用;(2)如果数字基带信号功率谱中并不含有位定时离散谱,怎样才能获得位同步信号。

数字基带信号本身是否含有位同步信息与其码型有密切关系。应强调的是,无论数字基带信号的码型如何,数字已调波本身一般不含有位同步信息,因为已调波的载波频率通常要

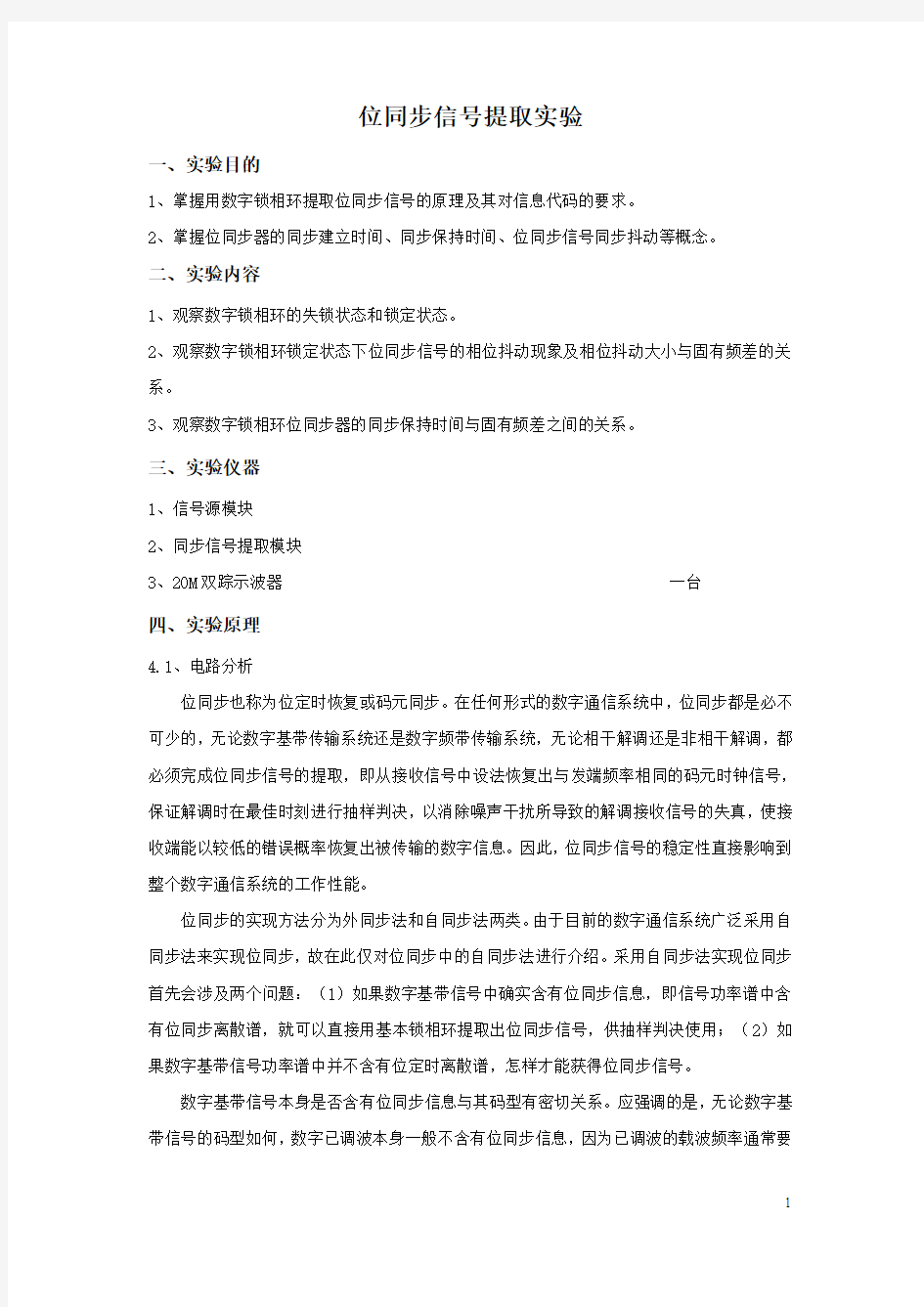

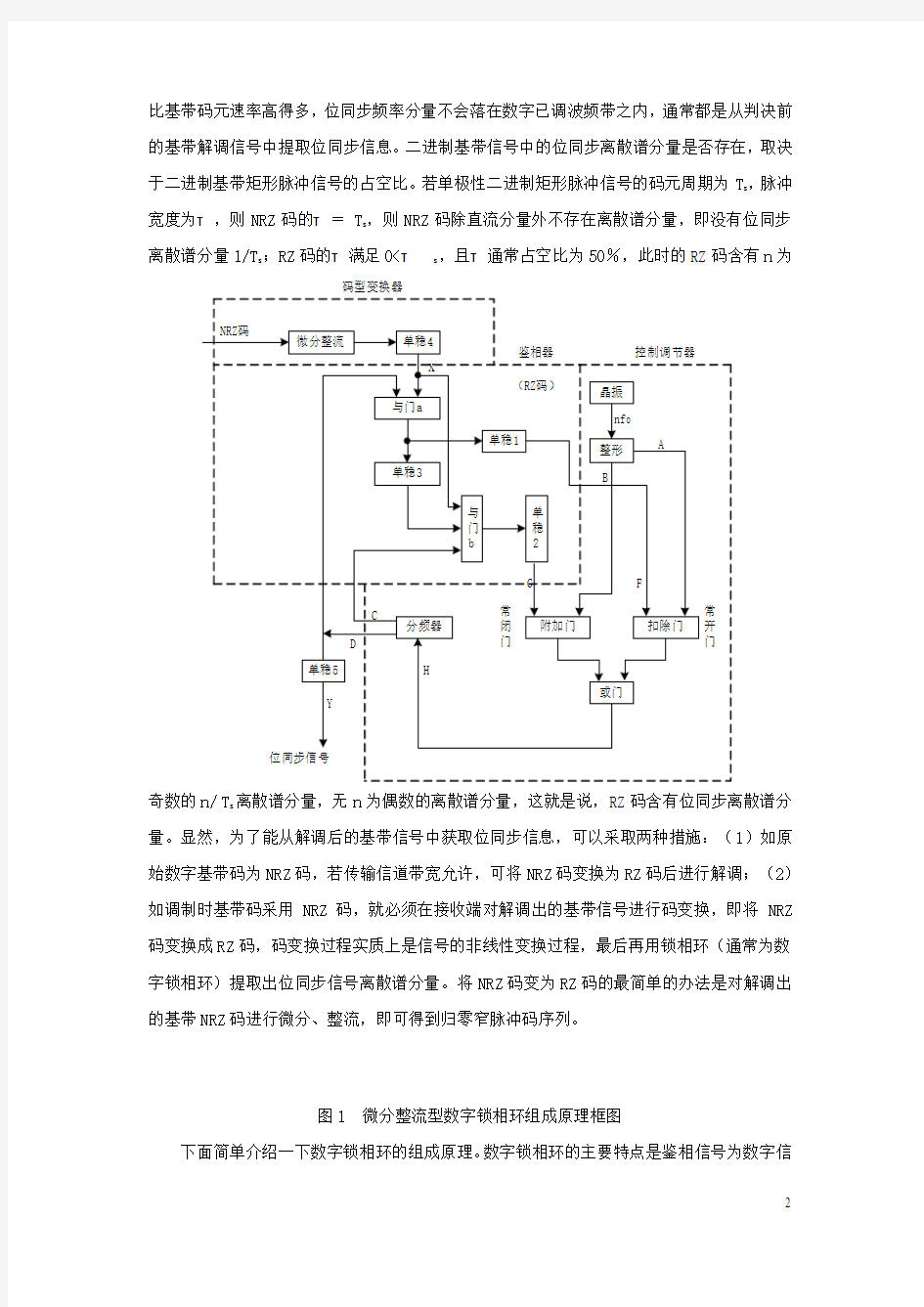

比基带码元速率高得多,位同步频率分量不会落在数字已调波频带之内,通常都是从判决前的基带解调信号中提取位同步信息。二进制基带信号中的位同步离散谱分量是否存在,取决于二进制基带矩形脉冲信号的占空比。若单极性二进制矩形脉冲信号的码元周期为T s,脉冲宽度为τ,则NRZ码的τ= T s,则NRZ码除直流分量外不存在离散谱分量,即没有位同步离散谱分量1/T s;RZ码的τ满足0<τ 码型变换器 奇数的n/ T s离散谱分量,无n为偶数的离散谱分量,这就是说,RZ码含有位同步离散谱分量。显然,为了能从解调后的基带信号中获取位同步信息,可以采取两种措施:(1)如原始数字基带码为NRZ码,若传输信道带宽允许,可将NRZ码变换为RZ码后进行解调;(2)如调制时基带码采用NRZ码,就必须在接收端对解调出的基带信号进行码变换,即将NRZ 码变换成RZ码,码变换过程实质上是信号的非线性变换过程,最后再用锁相环(通常为数字锁相环)提取出位同步信号离散谱分量。将NRZ码变为RZ码的最简单的办法是对解调出的基带NRZ码进行微分、整流,即可得到归零窄脉冲码序列。 图1 微分整流型数字锁相环组成原理框图 下面简单介绍一下数字锁相环的组成原理。数字锁相环的主要特点是鉴相信号为数字信 号,鉴相输出也是数字信号,即环路误差电压是量化的,没有模拟环路滤波器。由于数字锁相环的输入是经过微分和全波整流后的信号,故这种数字锁相环也称为微分整流型数字锁相环,其原理框图如图1所示。该电路由码型变换器、鉴相器、控制调节器组成,各部分的作用如下: ①码型变换器完成解调出的基带NRZ码到RZ码的变换,使鉴相输入信号X含有位同步离散谱分量。 ②鉴相器用于检测信号X与输出位同步信号(分频输出D)相位间的超前、滞后关系,并以量化形式提供表示实时相位误差的超前脉冲F和滞后脉冲G,供控制调节器使用。当分频输出位同步信号D相位超前与信号X时,鉴相器输出超前脉冲F(低电平有效);反之,则输出滞后脉冲G(高电平有效),二者均为窄脉冲。 ③控制调节器的作用是根据鉴相器输出的误差指示脉冲,在信号D与信号X没有达到同频与同相时调节信号D的相位。高稳定晶振源输出180°相位差、重复频率为nf0的A、B两路窄脉冲序列作为控制调节器的输入,经n分频后输出重复频率为f0的被调位同步信号D,它与信号X在鉴相器中比相。因超前脉冲F低电平有效并作用于扣除门(与门),平时扣除门总是让脉冲序列A通过,故扣除门为常开门,又因滞后脉冲G高电平有效并作用于附加门(与门),平时附加门总是对序列B关闭的,故附加门为常闭门。当信号D的相位超前与信号X 的相位时,鉴相器输出窄的低电平超前脉冲F,扣除门(与门)将从脉冲序列A中扣除一个窄脉冲,则n分频器输出信号D的相位就推迟了Ts /n(相移360°/n),信号D的瞬时频率也被调低;当信号D的相位滞后于信号X的相位时,鉴相器输出窄的高电平滞后脉冲G,附加门(与门)此时打开让脉冲序列B(与脉冲序列A保持180°固定相差)中的一个脉冲通过,经或门插进来自扣除门输出的脉冲序列A中,则分频器输入多插入的这个脉冲使n 分频器输出信号的D相位提前了Ts /n(相移360°/n),信号D的瞬时频率则被提高。由此可见,环路对信号D相位和频率的控制调节是通过对n分频器输入脉冲序列步进式加、减脉冲实现的,经环路的这种反复调节,最终可达到相位锁定,从而提取出位同步信号。4.2、性能指标 位同步系统的性能通常是用相位误差、建立时间、保持时间等指标来衡量。数字锁相法位同步系统的性能如下。 a)相位误差θe 数字锁相法提取位同步信号时,相位误差主要是由于位同步脉冲的相位在跳变地调整所引起的。因为每调整一步,相位改变2π/n(n是分频器地分频次数),故最大的相位误差为 2π/n 。用这个最大的相位误差来表示e θ,可得 360/e n θ= (1) 上面已经求得数字锁相法位同步的相位误差e θ有时不用相位差而用时间差T e 来表示相位误差。因每码元的周期为T ,故得 /e T T n = (2) b) 同步建立时间t s 同步建立时间即为失去同步后重建同步所需的最长时间。为了求这个最长时间,令位同步脉冲的相位与输入信号码元的相位相差T/2秒,而锁相环每调整一步仅能移T/n 秒,故所需最大的调整次数为 2 /2/n n T T N == (3) 接收随机数字信号时,可近似认为两相邻码元中出现01、10、11、00的概率相等,其中,有过零点的情况占一半。由于数字锁相法中是从数据过零点中提取作比相用的标准脉冲的,因此平均来说,每2T 秒可调整一次相位,故同步建立时间为 T s =2T ·N=nT (秒) (4) c) 同步保持时间t c 当同步建立后,一旦输入信号中断,由于收发双方的固有位定时重复频率之间总存在频差ΔF ,收端同步信号的相位就会逐渐发生漂移,时间越长,相位漂移量越大,直至漂移量达到某一准许的最大值,就算失步了。 设收发两端固有的码元周期分别为T 1=1/F 和T 2=1/F ,则 20 2 1122 1 2 1 11F F F F F F F F T T ?= -= - = - (5) 式中的F 0为收发两端固有码元重复频率的几何平均值,且有 00/1F T = (6) 由式(5)可得 F F T T F 0 2 10?= - (7) 再由式(6),上式可写为 F T 2 1= (8) 式(8)说明了当有频差ΔF 存在时,每经过T 0时间,收发两端就会产生12||T T -的时间漂移。反过来,若规定两端容许的最大时间漂移为T 0/K 秒(K 为一常数),需要经过多少时间才会达到此值呢?这样求出的时间就是同步保持时间t c 。代入式(8)后,得 F F t K T c 0/?= 解得 FK t c ?= 1 (9) 若同步保持时间t c 的指标给定,也可由上式求出收发两端振荡器频率稳定度的要求为 1 c F t K ?= 此频率误差是由收发两端振荡器造成的。若两振荡器的频率稳定度相同,则要求每个振荡器的频率稳定度不能低于 F K t F F c 0 212± =? (10) C D RST 1P3.02P3.03XTAL24 XTAL15P326P337P348P359GND 10 P3711 P1012P1113P1214P1315P1416P1517P1618P1719VCC 20U50889C2051VCC XTAL RST NRZ-IN 1234 5 678SW501 SW-DIP4I /O S502BN I /O S503BN TP502TP TP503TP 位同步输出 用将相位差进行量化后得到的数值对数字锁相环本振输出的相位进行调整,最后得到正确的位同步信号。 五、实验步骤 1、将信号源模块、同步信号提取模块小心地固定在主机箱中,确保电源接触良好。 2、插上电源线,打开主机箱右侧的交流开关,再分别按下两个模块中的开关POWER1、POWER2, 对应的发光二极管LED001、LED002、D500、D501发光,按一下信号源模块的复位键,两个模块均开始工作。(注意,此处只是验证通电是否成功,在实验中均是先连线,后打开电源做实验,不要带电连线) 3、将信号源模块的位同步信号的频率设置为15.625KHz(通过将拨码开关SW101、SW102设 置为00000001 00101000),将信号源模块输出的NRZ码设置为1、0交替码(通过拨码开关SW103、SW104、SW105进行设置)。 4、将同步信号提取模块的拨码开关SW501的第一位拨上,即将数字锁相环的本振频率设置 为15.625KHz,然后将信号源模块输出的NRZ码从信号输入点“NRZ-IN”输入,按一下同步信号模块上的“复位”键,使单片机开始工作,以信号源产生的位同步信号“BS” 为内触发源,用示波器双踪同时观察信号输出点“位同步输出”的信号与信号源中的“BS” 信号。 5、应特别注意的是,本模块只能提取NRZ码的位同步信号,而且当信号源模块中的位同步 信号的频率偏离同步信号提取模块设置的数字锁相环的本振频率过远时,将无法正确提取输入信号的位同步信号。本实验中数字锁相环共有15.625KHz、10KHz、8KHz、4KHz 四种本振频率可供选择,分别对应拨码开关SW501的1、2、3、4位,实验时请注意正确选择。(注意当锁相频率改变时,需重新按下同步模块上的“复位”键,位同步信号才能正确提取) 六、输入、输出点参考说明 1、输入点参考说明 NRZ-IN: NRZ码输入点。 2、输出点参考说明位同步输出:提取的位同步信号输出点。 3、拨码开关SW501的1、2、3、4位分别对应数字锁相环的15.625KHz、10KHz、8KHz、4KHz 四种本振频率。 七、实验思考题 1、设数字锁相环固有频差为△f,允许同步信号相位抖动范围为码元宽度Ts的η倍,求同 步保持时间t c及允许输入的NRZ码的连“1”或连“0”个数的最大值。 2、数字锁相环同步器的同步抖动范围随固有频差增大而增大,试解释此现象。 3、若将AMI码或HDB3码整流后作为数字锁相环位同步器的输入信号,能否提取出位同步信 号?为什么?对这两种码的连“1”个数有无限制?对AMI码的信息代码中连“0”个数有无限制?对HDB3码的信息代码中连“0”个数有无限制?为什么? 4、试提出一种新的环路滤波器算法,使环路具有更好的抗噪声能力。 八、实验报告要求 1、分析实验电路的工作原理,叙述其工作过程。 2、根据实验测试记录,在坐标纸上画出各测量点的波形图,并分析实验现象。 3、对实验思考题加以分析,按照要求做出回答。 4、写出完成本次实验后的心得体会以及对本次实验的改进意见。 实验十二位同步信号提取实验 一、实验目的 1、掌握用数字锁相环提取位同步信号的原理及其对信息代码的要求。 2、掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念。 二、实验内容 1、观察数字锁相环的失锁状态和锁定状态。 2、观察数字锁相环锁定状态下位同步信号的相位抖动现象及相位抖动大小与固有频差的关系。 3、观察数字锁相环位同步器的同步保持时间与固有频差之间的关系。 三、实验仪器 1、信号源模块 2、同步信号提取模块 3、20M双踪示波器一台 4、频率计(选用)一台 5、连接线若干 四、实验原理 1、电路分析 位同步也称为位定时恢复或码元同步。在任何形式的数字通信系统中,位同步都是必不可少的,无论数字基带传输系统还是数字频带传输系统,无论相干解调还是非相干解调,都必须完成位同步信号的提取,即从接收信号中设法恢复出与发端频率相同的码元时钟信号,保证解调时在最佳时刻进行抽样判决,以消除噪声干扰所导致的解调接收信号的失真,使接收端能以较低的错误概率恢复出被传输的数字信息。因此,位同步信号的稳定性直接影响到整个数字通信系统的工作性能。 位同步的实现方法分为外同步法和自同步法两类。由于目前的数字通信系统广泛采用自同步法来实现位同步,故在此仅对位同步中的自同步法进行介绍。采用自同步法实现位同步首先会涉及两个问题:(1)如果数字基带信号中确实含有位同步信息,即信号功率谱中含有位同步离散谱,就可以直接用基本锁相环提取出位同步信号,供抽样判决使用;(2)如果数字基带信号功率谱中并不含有位定时离散谱,怎样才能获得位同步信号。 数字基带信号本身是否含有位同步信息与其码型有密切关系。应强调的是,无论数字基带信号的码型如何,数字已调波本身一般不含有位同步信息,因为已调波的载波频率通常要比基带码元速率高得多,位同步频率分量不会落在数字已调波频带之内,通常都是从判决前的基带解调信号中提取位同步信息。二进制基带信号中的位同步离散谱分量是否存在,取决于二进制基带矩形脉冲信号的占空比。若单极性二进制矩形脉冲信号的码元周期为T s,脉冲宽度为τ,则NRZ码的τ= T s,则NRZ码除直流分量外不存在离散谱分量,即没有位同步离散谱分量1/T s;RZ码的τ满足0<τ 滤波法及数字锁相环法位同步提取实验和帧同步提取实验 滤波法及数字锁相环法位同步提取实验和帧同步提取实验 一、实验目的 1、掌握滤波法提取位同步信号的原理及其对信息码的要求; 2、掌握用数字锁相环提取位同步信号的原理及其对信息代码的要求; 3、掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念; 4、掌握巴克码识别原理; 5、掌握同步保护原理; 6、掌握假同步、漏同步、捕捉态、维持态的概念。 二、实验内容 1、熟悉实验箱 2、滤波法位同步带通滤波器幅频特性测量; 3、滤波法位同步恢复观测; 4、数字锁相环位同步观测; 5、帧同步提取实验。 三、实验条件/器材 滤波法及数字锁相环法位同步提取实验: 1、主控&信号源、8号(基带传输编译码)、13号(载波同步及位同步)模块 2、双踪示波器(模拟/数字) 3、连接线若干 帧同步提取实验: 1、主控&信号源、7号模块 2、双踪示波器(模拟/数字) 3、连接线若干 四、实验原理 滤波法及数字锁相环法位同步提取实验原理见通信原理综合实验指导书P129-P134; 帧同步提取实验原理见通信原理综合实验指导书P141。 五、实验过程及结果分析 (一)熟悉实验箱 (二)滤波法位同步带通滤波器幅频特性测量 1、连线及相关设置 (1)关电,连线。 (2)开电,设置主控,选择【信号源】→【输出波形】。设置输出波形为正弦波,调节相应旋钮,使其输出频率为200Khz,峰峰值3V。 (3)此时系统初始状态为:输入信号为频率200KHz、幅度为3V的正弦波。 2、实验操作及波形观测 分别观测13号模块的“滤波法位同步输入”和“BPF-Out”,改变信号源的频率,测量“BPF-Out” 的幅度填入下表,并绘制幅频特性曲线。 实验十九滤波法及数字锁相环法位同步提取实验 实验项目三数字锁相环法位同步观测 (1)观测“数字锁相环输入”和“输入跳变指示”,观测当“数字锁相环输入”没有跳变和有跳变时“输入跳变指示”的波形。 从图中可以观察出,若前一位数据有跳变,则判断有效,“输入跳变指示”输出表示1;否则,输出0表示判断无效。 (2)观测“数字锁相环输入”和“鉴相输出”。观测相位超前滞后的情况 数字锁相环的超前—滞后鉴相器需要排除位流数据输入连续几位码值保持不变的不利影响。在有效的相位比较结果中仅给出相位超前或相位滞后两种相位误差极性,而相位误差的绝对大小固定不变。经观察比较,“鉴相输出”比“数字锁相环输入”超前两个码元。 (3)观测“插入指示”和“扣除指示”。 (4)以信号源模块“CLK ”为触发,观测13号模块的“BS2”。 思考题:分析波形有何特点,为什么会出现这种情况。 因为可变分频器的输出信号频率与实验所需频率接近,将其和从信号中提取的相位参考信号同时送入相位比较器,比较的结果若是载波频率高了,就通过补抹门抹掉一个输入分频器的脉冲,相当于本地振荡频率降低;相反,若示出本地频率低了时就在分频器输入端的两个输入脉冲间插入 一个脉冲,相当于本地振荡频率上升,从而了达到同步的目的。 思考题:BS2恢复的时钟是否有抖动的情况,为什么?试分析BS2抖动的区间有多大?如何减小这个抖动的区间? 有抖动的存在,是因为可变分频器的存在使得下一个时钟沿的到来时间不确定,从而引入了相位抖动。而这种引入的误差是无法消除的。减小相位抖动的方法就是将分频器的分频数提高。 实验二十 模拟锁相环实验 实验项目一 VCO 自由振荡观测 (1)示波器CH1接TH8,CH2接TH4输出,对比观测输入及输出波形。 实验项目二 同步带测量 (1) 示波器CH1接13号模块TH8模拟锁相环输入,CH2接TH4输出BS1,观察TH4 输出处于锁定状态。将正弦波频率调小直到输出波形失锁,此时的频率大小f1为 400Hz ;将频率调大,直到TH4输出处于失锁状态,记下此时频率f2为 9.25kHz 。 对比波形可以发现TH8与TH4信号输入与输出错位半个周期 如右图所示,方波抖动,说明处于失锁状态。 记下两次波形失锁的频率,可计 算 出 同 步 带 f=9.25KHz-400Hz=8.85KHz 。 中南大学 《通信原理》实验报告 学生姓名 指导教师 学院 专业班级 完成时间 数字基带信号 1、实验名称 数字基带信号 2、实验目的 (1)了解单极性码、双极性码、归零码、不归零码等基带信号波形特点。 (2)掌握AMI、HDB 3 码的编码规则。 (3)掌握从HDB 3 码信号中提取位同步信号的方法。 (4)掌握集中插入帧同步码时分复用信号的帧结构特点。 (5)了解HDB 3 (AMI)编译码集成电路CD22103。 3、实验内容 (1)用示波器观察单极性非归零码(NRZ)、传号交替反转码(AMI)、三阶高密度双极性码 (HDB 3)、整流后的AMI码及整流后的HDB 3 码。 (2)用示波器观察从HDB 3 码中和从AMI码中提取位同步信号的电路中有关波形。 (3)用示波器观察HDB 3 、AMI译码输出波形。 4、基本原理(简写) 本实验使用数字信源模块和HDB 3 编译码模块。 1、数字信源 本模块是整个实验系统的发终端,模块内部只使用+5V电压,其原理方框图如图1-1所示,电原理图如图1-3所示(见附录)。本单元产生NRZ信号,信号码速率约为170.5KB,帧结构如图1-2所示。帧长为24位,其中首位无定义,第2位到第8位是帧同步码(7位巴克码1110010),另外16位为2路数据信号,每路8位。此NRZ信号为集中插入帧同步码时分复用信号,实验电路中数据码用红色发光二极管指示,帧同步码及无定义位用绿色发光二极管指示。发光二极管亮状态表示1码,熄状态表示0码。 本模块有以下测试点及输入输出点: ? CLK 晶振信号测试点 ? BS-OUT 信源位同步信号输出点/测试点(2个) ? FS 信源帧同步信号输出点/测试点 ? NRZ-OUT(AK) NRZ信号(绝对码)输出点/测试点(4个) 图1-1中各单元与电路板上元器件对应关系如下: ?晶振CRY:晶体;U1:反相器7404 ?分频器U2:计数器74161;U3:计数器74193;U4:计数器40160 ?并行码产生器K1、K2、K3:8位手动开关,从左到右依次与帧同步码、数 实验项目三 数字锁相环法位同步观测 (1)观测“数字锁相环输入”和“输入跳变指示”,观测当“数字锁相环输入”没有跳变和有跳变时“输入跳变指示”的波形。 (2)观测“数字锁相环输入”和“鉴相输出”。观测相位超前滞后的情况。 (4)以信号源模块“CLK ”为触发,观测13号模块的“ BS2”。 实验二十 实验项目一 VCO 自由振荡观测 (1)示波器CH1接TH8,CH2接TH4 实验项目二 同步带测量 (1)示波器CH1接13号模块TH8模拟锁相环输入,CH2接TH4输出BS1,观察TH4输出处于锁定状态。将正弦波频率调小直到输出波形失锁,此时的频率大小f1为 400Hz ;将频率调大,直到TH4输出处于失锁状态,记下此时频率f2为。 实验二十一载波同步实验 实验项目载波同步 (1)本实验利用科斯塔斯环法提取BPSK调制信号的同步载波,对比观测信号源“256K”和13号模块的“SIN”,调节13号模块的压控偏置调节电位器,观测载波同步情况。 实验二十二帧同步实验 实验项目帧同步提取实验 (1)观测在没有误码的情况下“失步”,“捕获”,“同步”三个灯的变化情况经过多次实验反复观察,“失步”指示灯一直没有亮过,其余两个灯的顺序为捕捉指示灯先亮,之后熄灭,同步指示灯变亮。 (2)关闭7号模块电源。按住“误码插入”不放,打开7号模块电源。再观测“失步”,“捕获”,“同步”三个灯的变化情况。 经过多次实验反复观察,“失步”指示灯一直没有亮过,其余两个灯的顺序为捕捉指示灯先亮,之后熄灭,同步指示灯变亮。 (3)观察同步保护现象:如下图所示。 (4) 现误码时三个LED (5)观察假同步现象: 观察结果知, 分析原因:此时出现假同步状态,即时分复用单元将拨码开关S1的码值做为帧 头码,其他码元和原来的巴克码被当做了数据码元,从而在检查到01110010时 就开始按照8位为一个用户的数据,接着进行下面的数据采集。 帧同步识别、保护、提取实验 一、实验目的 1.掌握巴克码识别电路原理; 2.掌握同步保护电路原理; 3.掌握假同步、漏同步、捕捉态、维持态等概念; 4.通过设计性实验,培养学生用EPROM器件写入软件和利用应用手册,完成 该模块中识别、比较器的软、硬件的设计能力。 二、实验内容: 1、观察帧同步码元无误码时帧同步电路的维持态; 2、观察帧同步有一位错码时,帧同步的维持态和捕捉态; 3、观察同步电路的假同步现象和同步保护作用; 4、修改本模块中EPROM的参数即改变比较器的设置,完成相同的电路功能。(选做) 三、基本原理 (一)帧同步模块的原理框图及电原理图分别如图7-1和图7-2所示。 图7-1 帧同步模块原理框图 图7-1中各功能部分在图7-2中所对应元器件关系如下: 1.分频器:U3(74LS161)、U4(4075)、U2(74LS74)、U5(74H04) 2.串/并变换器:U9(74LS164) 3.识别器:U7(2764) 4.判决器:U10(74LS85) 5.人工与门限选择器:U13(74LS157) 6.自动门限:U14(74LS157) 7.人工门限:S1 8.人工门限显示:U16(74247)、U12(LCD) (二)电路基本原理 1.帧同步信号的识别与判决 串/并变换器U9将串行码变成并行码,并完成移位功能,当七位巴克码全部进入U9时,U9的输出端Q6Q5Q4Q3Q2Q1Q0=1110010,并送入U7(2764)帧头识别器。 识别器U7为EPROM器件,在U7中将串/并变换的输出信号与1110010码进行相关运算,使U7的数据输出端的D3D2D1D0有对应的相关输出。如当U7的A6A5A4A3A2A1A0=1110010时,则对应的 D3D2D1D0=0111时(十进制数为7),若A6A5A4A3A2A1A0=1110011(与巴克码错一位)时,则对应的D3D2D1D0=0110(十进制数为6) 比较判决器Ul0(74LS85)有两组输入数据,一组来自帧头识别器,另一组来白人工与白动门限选择器U13。U10的曲组输入数据A3A2A1A0与B3B2B1B0进行比较。只当A3A2A1A0大于或等于B3B2B1B0时U10的输出为“1”,其余输出为:“0”。因此,U10端不仅与来自识别器的数据有关。还与判决门限数据B3B3B1B0有关,还与判决门限数据B3B2B1B0有关。 2.帧同步信号的捕捉与同步保护 本模块是在捕捉态时,Ul0的B3B2B1B0=0111(十进制数为7);另一种是在同步态时,U10的B3B2B1B0=O110(十进制数为6)。在捕捉态时,只有当巴克码到来时(1110010),U10的A3A2A1A0=01111(十进制为7),满足A3A2A1A0A 大于或等于B3B2B1B0的条件,才有判决脉冲输出。 人工门限可以从略0000--0111(0--7)任意置定,可据实验需要,自行选择其门限值。同步保护电路输出的帧同步信号(图7-1)受状态触发器Q端输出的信号所控制。÷32分频信号的周期与比较器输出一个帧同步信号的周期相同,但相位一定相同。但只要比较器输出一个帧同步信号,对÷3 2分频器置零,使÷32分频信号T2的上升沿与判决输出信号Tl的下降沿同相。清零信号由判决器输出信号及÷3 2分频信号共同决定。当无基带信号输入(或虽有基带信号输入但识别器的输出低于门限值)时,判决器输出为0,与门l关闭,与门4打丌。÷32信号经与门4,输入到÷5计数电路。÷5计数电路的输出信号使状态触发器置“0”,从而关闭与门2无帧同步信号输出。此时Q的高电平把判决器门限置为7(门限开关为“自动”),且关闭或门,打开与门1,同步电路进入捕捉态。这时,只要比较器输出一个脉冲信号(认定为帧同步头),与门3就输出一个置“0”脉冲,使÷32电路置“0”,从而输出与帧同步信号同频同相的周期信号。判决器输出的脉冲信号通过与门1后,使状态触发器置“l”,从而打开与门2,输出输出帧同步信号。同时,Q=0,使判决门限降为6,打开或门。同步电路处于维持态。在维持态下,因判决门限低,故与门1,与门3禁止输出假同步信号使,假同步信号小改变÷32的工作状态,与门2的输出仍为正确的同步态。 在维持状态下,识别比较器也可能出现漏同步。但由于漏同步概率比较小,只要识别比较器小连续出现五次漏同步,则÷5电路就小输出信号,使维持状态小变。若识别器连续出现五交漏同步,则÷5电路输出要一个脉冲信号使维持态为捕捉态,重新捕捉帧同步码。(同步指示灯亮,表示同步态;同步指示灯灭表示捕捉态) 实验十八位同步提取实验 一、实验目的 1、掌握用滤波法提取位同步信号的原理及其对信息代码的要求。 2、掌握用数字锁相环提取位同步信号的原理及其对信息代码的要求。 3、掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念。 二、实验内容 1、观察滤波法提取位同步信号各观测点波形。 2、观察数字锁相环的失锁状态和锁定状态。 3、观察数字锁相环锁定状态下位同步信号的相位抖动现象及相位抖动大小与固有频差的 关系。 4、观察数字锁相环位同步器的同步保持时间与固有频差之间的关系。 三、实验器材 1、信号源模块一块 2、⑥号模块一块 3、⑦号模块一块 4、20M双踪示波器一台 5、频率计(选用)一台 四、实验原理 位同步锁相法的基本原理和载波同步的类似。在接收端利用鉴频器比较接收码元和本地产生的位同步信号的相位,若两者相位不一致(超前或滞后),鉴相器就产生误差信号去调整位同步信号的相位,直至获得准确的位同步信号为止。前面讨论的滤波法原理图中,窄带滤波器可以是简单的单调谐回路或晶体滤波器,可以是锁相环路。 我们把采用锁相环来提取位同步信号的方法称为锁相法。下面介绍在数字通信中常采用的数字锁相环法提取位同步信号的原理。 数字锁相环(DPLL)是一种相位反馈控制系统。它根据输入信号与本地估算时钟之间的相位误差对本地估算时钟的相位进行连续不断的反馈调节,从而达到使本地估算时钟相位跟踪输入信号相位的目的。DPLL 通常有三个组成模块:数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)。根据各个模块组态的不同, DPLL 可以被划分出许多不同的类型。根据设计 的要求,本实验系统采用超前滞后型数字锁相环(LL-DPLL)作为解决方案,图18-3是其实现结构。在LL- DPLL中,DLF 用双向计数逻辑和比较逻辑实现,DCO 采用加扣脉冲式数控振荡器。这样设计出来的DPLL具有结构简洁明快,参数调节方便,工作稳定可靠的优点。 六、实验步骤 1、锁相环法位同步提取 (1)将信号源模块上S5拨为“1010”,拨动拨码开关S1、S2、S3,使“NRZ”输出的24位NRZ码设置为01110010 10101010 10101010。模块7上的S2拨为“0110”, 即提取时钟选512K。 (2)在电源关闭的状态下,依照下表完成连线: 源端口目的端口连线说明 信号源:NRZ(32K)模块7:DIN 32KNRZ码输入同步提取 * 检查连线是否正确,检查无误后打开电源 (3)以信号源模块“CLK2”的信号为内触发源,用示波器双踪观察模块7上“BS”波形,并与原始时钟CLK2相比较。 (4)把信号源模块上的S1拨为00000000,S2、S3不变,用示波器双踪同时观察“NRZ” 和模块7上“ABSVAL”两点的波形。(结果可以看到,“NRZ”连零时“ABSVAL”为 0,“NRZ”有跳变时“ABSVAL”为1) 帧同步提取系统实验 一.实验目的 1、了解帧同步的机理 2、熟悉帧同步的性能 3、熟悉帧失步对数据业务的影响 二.实验内容 1、帧同步过程观察; 2、误码环境下的帧同步性能测试; 3、帧失步下对接受帧内的数据信号传输的定性观测。 三.实验仪器 1、JH5001通信原理综合实验系统一台 2、20MHz双踪示波器一台四.原理与电路 在TDM复接系统中,要保证接收端分路系统和发送端一致,必须要有一个同步系统,以实现发送端和接收端同步。帧定位同步系统是复接/解复接设备中最重要的部分。在帧定位系统中要解决的设计问题有:1)同步搜索方法;2)帧定位码型设计;3)帧长度的确定;4)帧定位码的码长选择;5)帧定位保护方法;6)帧定位保护参数的选择;等等。这些设计完成后就确定了复接系统的下列技术性能:1)平均同步搜捕时间;2)平均发现帧时间;3)平均确认同步时间;4)平均发生失帧的时间间隔;5)平均同步持续时间;6)失帧引入的平均误码率,等等。 通常帧定位同步方法有两种:逐码移位同步搜索法和置位同步搜索法。通信原理综合实验系统中的解复接同步搜索方法采用逐码移位同步法。逐码移位同步搜索法的基本工作原理是调整收端本地帧定位码的相位,使之与收到的总码流中的帧定位码对准。同步后用收端各 分路定时脉冲就可以对接收到的码流进行正确的分路。如果本地帧同步码的相位没有对准码流接收信号码流的帧定位码位,则检测电路将输出一个一定宽度的扣脉冲,将接收时钟扣除一个,这等效将数据码流后移一位码元时间,使帧定位检测电路检测下一位信码。如果下一位检测结果仍不一致,则再扣除一位时钟,这过程称“同步搜索”。搜索直至检测到帧定位码为止。因接收码流除有帧定位码型外,随机的数字码流也可能存在与帧定位码完全相同的码型。因此,只有在同一位置,多次连续出现帧定位码型,方可算达到并进入同步。这一部分功能由帧定位检测电路内的校核电路完成。 无论多么可靠的同步电路,由于各种因素(例如强干扰、短促线路故障等),总会破坏同步工作状态,使帧失步。从帧失步到重新获得同步的这段时间(亦称同步时间)将使通信中断。误码也将会造成帧失步。因此,从同步到下一次失步的时间因尽量长一些,否则将不断的中断通信。这一时间的长短表示TDM同步系统的抗干扰能力。抗误码造成的帧失步主要由帧定位检测电路内的保护记数电路完成,只有当在一定的时间内在帧定位码位置多次检测不到帧定位码,才可判定为帧失步,需重新进入同步搜索状态。逐码移位同步搜索法系统组成框图见图1所示。 语音信号的中断时间短于100ms,将不易被人耳分辨出来。但对某些数据终端传输却是不允许的。为能让学生能深入了解在有误码的环境下帧失步、同步和抗误码性能,在复接模块内专门设计了一个错码产生器(3种类型误码),通过错码设置跳线开关SWB02(E_SEL0,E_SEL1)选择不同的信道误码率(分别约为4×10—3、1.6×10—2和1×10—1)。学生能够观测到复接/解复接具有抗误码性能,即在小误码时帧同步锁定状态,加大误码帧帧失步,进入帧同步搜索(扫描)状态;另可测试不同误码和帧失步对话音业务的影响和观测对数据业务的影响。 五.实验步骤 准备工作:首先将解复接模块内的输入信号和时钟选择跳线开关KB01、KB02设置LOOP(自环)位置,使复接模块和解复接模块连接成自环测试方式;将复接模块内的工作状态选择跳线开关SBW02的m序列选择跳线开关M_SEL1、M_SEL2拔下,使m序列发生器产生全0码,将错码选择跳线开关E_SEL0、E_SEL1拔下,不在传输帧中插入误码。 实验一 1. 根据实验观察和纪录回答: (1)不归零码和归零码的特点是什么? (2)与信源代码中的“1”码相对应的AMI码及HDB3码是否一定相同? 答: 1)不归零码特点:脉冲宽度τ等于码元宽度Ts 归零码特点:τ<Ts 2)与信源代码中的“1”码对应的AMI码及HDB3码不一定相同。因信源代码中的“1”码对应的AMI码“1”、“-1”相间出现,而HDB3码中的“1”,“-1”不但与信源代码中的“1”码有关,而且还与信源代码中的“0”码有关。举例: 信源代码 1 0 0 0 0 1 1 0 0 0 0 1 0 0 0 0 0 1 AMI 1 0 0 0 0 -1 1 0 0 0 0 -1 0 0 0 0 0 1 HDB3 1 0 0 0 1 -1 1 -1 0 0 -1 1 0 0 0 1 0 -1 2. 设代码为全1,全0及0111 0010 0000 1100 0010 0000,给出AMI及HDB3码的代码和波形。 答: 信息代码 1 1 1 1 1 1 1 AMI 1 -1 1 -1 1-1 1 HDB3 1 -1 1 -1 1 -1 1 信息代码0 0 0 0 0 0 0 0 0 0 0 0 0 AMI0 0 0 0 0 0 0 0 0 0 0 0 0 HDB3 0 0 0 1-10 0 1-1 0 0 1 -1 信息代码0 1 1 1 0 0 1 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 0 0 AMI0 1 -1 1 0 0 -1 0 0 0 0 0 1 -1 0 0 0 0 1 0 0 0 0 0 HDB30 1 -1 1 0 0 -1 0 0 0-1 0 1 -1 1 0 0 1 -1 0 0 0 –1 0 3. 总结从HDB3码中提取位同步信号的原理。 答: HDB3中不含有离散谱f S(f S在数值上等于码速率)成分。整流后变为一个占空比等于0.5的单极性归零码,其连0个数不超过3,频谱中含有较强的离散谱f S成分,故可通过窄带带通滤波器得到一个相位抖动较小的正弦信号,再经过整形、移相后即可得到合乎要求的位同步信号。 姓名:学号:班级: 第周星期第大节实验名称:自定义帧结构的帧形成及其传输/自定义帧结构的帧同步系统 一、实验目的 1.加深对PCM30/32系统帧结构的理解。 2.加深对PCM30/32路帧同步系统及其工作过程的理解。 3.加深对PCM30/32系统话路、信令、帧同步的告警复用和分用过程的理解。 二、实验仪器 1.ZH5001A通信原理综合实验系统 2.20MHz双踪示波器 三、实验内容 (一)自定义帧结构的帧形成及其传输 1.发送传输帧结构观测 (1)(2) m序列输入的序列为全0 所找的帧在图上标注了。 (3)调整开关信号。 箭头所指为改变的开关信号。 (4)调整m序列 什么都不接是全0可以看清,接时,可以看清。接M_SEL1和两2.发送帧同步指示的观测 可以观测到已经同步 3.解复接开关信号输出的观测 4.解复接m序列数据输出观测 接M_SEL0 & M_SEL1 接M_SEL0 接M_SEL1 全不接 只要接M_SEL0接收就看不清,全1(M_SEL0)和全0(都不接)都可以 (二)自定义帧结构的帧同步系统 1.帧同步过程观测 (1)输入全0码 可以同步 可以同步 (3)将开关信号设置为帧定位信号,将KB01拔出插入 左边是假同步,右边是真同步。说明开关序列边位帧同步序列以后会影响 2.在误码环境下的帧同步性能测试和数据传输的定性测试(1)通过设置,使信道的误码率为1*10^-1 无法同步,同时观察LED灯,发现LED灯闪烁无规律。 (2)通过设置,使信道的误码率为1.6*10^-2 仍旧不能同步。 (3)通过设置,使信道的误码率为4*10^-3 在误码率较小的情况下,可以同步。 xxxx学院 毕业设计论文 题目:基于单片机和FPGA的位同步信号提取专业班级:电子信息工程 学生姓名:学号: 完成日期: 指导教师: 评阅教师: 2006 年6月 湖南工程学院应用技术学院毕业设计(论文) 诚信承诺书 本人慎重承诺和声明:所撰写的《基于单片机和FPGA的位同步信号提取》是在指导老师的指导下自主完成,文中所有引文或引用数据、图表均已注解说明来源,本人愿意为由此引起的后果承担责任。 设计(论文)的研究成果归属学校所有。 学生(签名) 年月日 湖南工程学院应用技术学院 毕业设计(论文)任务书 设计(论文)题目:基于单片机和FPGA的位同步信号提取 姓名专业电子信息工程班级 0281 学号 16 指导老师刘正青职称实验师教研室主任 刘望军 一、基本任务及要求: 本课题是设计一具有通用性的输入信号的位同步提取系统,系统可以实现10HZ~1MHZ 的信号同步。使用单片机进行实时控制现场可编程逻辑门阵列FPGA完成位同步信号提取, 通过理论和实验研究,完成硬件电路和软件设计并试制样机,要求完成: 1、单片机实时控制FPGA,完成实时频率跟踪测量和自动锁相; 2、在FPGA 内部,设计完成以下部分: A、全数字锁相环DPLL,主要包含:数控振荡器、鉴相器、可控模分频 器 B、LED动态扫描电路、FPGA和单片机的数字接口,以完成两者之间的 数字传递 3、设计辅助电路:键盘、LED; 二、进度安排及完成时间: (1)第二周至第四周:查阅资料、撰写文献综述和开题报告; (2)第五周至第六周:毕业实习; (3)第六周至第七周:项目设计的总体框架:各个模块以及各个模块之间的关 系确定,各个模块的方案选择与各个模块的所用主要器件的确定; (4)第八周至第十三周:各个模块的主要器件熟悉及相关知识的熟悉;各个模 块的具体任务实现:硬件电路、软件编程; (5)第十四周至第十五周:系统的总体仿真与调试 (6)第十六周至第十七周:撰写设计说明书; (7)第十八周:毕业设计答辩; 实验八 帧同步信号恢复实验 一、实验目的 1. 掌握巴克码识别原理。 2. 掌握同步保护原理。 3. 掌握假同步、漏同步、捕捉态、维持态概念。 二、实验内容 1. 观察帧同步码无错误时帧同步器的维持态。 2. 观察帧同步码有一位错误时帧同步器的维持态和捕捉态。 3. 观察同步器的假同步现象和同步保护作用。 三、基本原理 (A )原理说明 一、帧同步码插入方式及码型 1.集中插入(连贯插入) 在一帧开始的n 位集中插入n 比特帧同步码,PDH 中的A 律PCM 基群、二次群、三次、四次群,μ律PCM 二次群、三次群、四次群以及SDH 中各个等级的同步传输模块都采用集中插入式。 2.分散插入式(间隔插入式) n 比特帧同步码分散地插入到n 帧内,每帧插入1比持,μ律PCM 基群及△M 系统采用分散插入式。 分散插入式无国际标准,集中插入式有国际标准。 帧同步码出现的周期为帧周期的整数信,即在每N 帧(N≥1)的相同位置插入帧同步码。 3.帧同步码码型选择原则 (1)假同步概率小 (2)有尖锐的自相关特性,以减小漏同步概率 如A 律PCM 基群的帧同步码为001101,设“1”对应正电平1,“0”码对应负电平-1,则此帧同步码的自相关特性如下图所示 0 1 2 3 4 5 6 -6 -5 -4 -3 -2 -1 -1 -1 -1 -1 -5 -5 -5 -5 3 3 3 3 j 7 R(j) 二、帧同步码识别 介绍常用的集中插入帧同步码的识别方法。设帧同码为0011011,当帧同步 码全部进入移位寄存器时它的7个 输出端全为高电平,相加器3个输出端全为高电平,表示u i =1+2+4=7。 门限L 由3个输入电平决定,它们 的权值分别为1,2,4。 比较器的功能为? ??<≥=L u L u u i i o ,0,1据此可得以下波形: 三、识别器性能 设误码率为P e ,n 帧码位,L=n-m ,(即允许帧同步码错m 位),求漏识别概率P 1和假识别概率P 2以及同步识别时间t s 。 1.漏识别概率 正确识别概率为∑=--m n e e n P P C 0 )1(γγγ γ,故 ∑=--- =m n e e p P n P 0 1)1((1γ γ γγ,m=0时e nP P ≈1 门限L 越低,P e 越小,则漏识别概率越小。 2.假识别概率 n 位信码产生一个假识别信号的概率为n m n n P m C P -=-===∑202 20 2时γ γ 门限越高,帧码位数越多,则假识别概率越小。 3.同步识别时间t s P 1=P 2=0时,t s =NT s ,N 为一个同步帧中码元位数,T s 为码元宽度 一个同步帧中产生一个假识别信号概率为22)(NP P n N ≈-,故当P 1≠0、P 2≠0时 s s NT NP P t )1(21++= 分散插入帧同步码的同步识别时间为 s s T N t 2= L u 0 移位寄存器 PCM 码流 u 0 (精编)哈工大通信原理 实验报告 H a r b i n I n s t i t u t e o f T e c h n o l o g y 通信原理 实验报告 课程名称:通信原理 院系:电子与信息工程学院 班级: 姓名: 学号: 指导教师:倪洁 实验时间:2015年12月 哈尔滨工业大学 实验二帧同步信号提取实验 一、实验目的 1.了解帧同步的提取过程。 2.了解同步保护原理。 3.掌握假同步,漏同步,捕捉动态和维持态的概念。 二、实验原理 时分复用通信系统,为了正确的传输信息,必须在信息码流中插入一定数量的帧同步码,帧同步码应具有良好的识别特性。本实验系统帧长为24比特,划分三个时隙,每个时隙长度8比特,在每帧的第一时隙的第2至第8码元插入七位巴克码作为同步吗。第9至24比特传输两路数据脉冲。帧结构为:X11100101010101011001100,首位为无定义位。 本实验模块由信号源,巴克码识别器和帧同步保护电路三部分构成,信号源提供时钟脉冲和数字基带脉冲,巴克码识别器包裹移位寄存器、相加器和判决器。其余部分完成同步保护功能。 三、实验内容 1.观察帧同步码无错误时帧同步器的维持状态。 2.观察帧同步码有一位错误时帧同步器的维持态和捕捉态 3.观察帧同步器假同步现象和同步保护器。 四、实验步骤 1.开关K301接 2.3脚。K302接1.2脚。 2.接通电源,按下按键K1,K2,K300,使电路工作。 3.观察同步器的同步状态 将信号源中的SW001,SW002,SW003设置为11110010,10101010,11001100(其中第2-8位为帧同步码),SW301设置为1110,示波器1通道接TP303,2通道接TP302,TP304,TP305,TP306,观察上述信号波形,使帧同步码(SW001的2-8位)措一位,重新做上述观察,此时除了TP303外,个点波形不变,说明同步状态仍在维持。 4.观察同步器的失步状态。 关闭电源,断开K302,在开电源(三个发光二极管全亮)。使帧同步码措一位后再将 实验十 载波同步提取实验 一、 实验目的 1、掌握用科斯塔斯(Costas )环提取相干载波的原理与实现方法。 2、了解相干载波相位模糊现象的产生原因。 二、 实验内容 1、观察科斯塔斯环提取相干载波的过程。 2、观察科斯塔斯环提取的相干载波,并做分析。 三、 实验器材 1、信号源模块 一块 2、 ③号模块 一块 3、 ⑦号模块 一块 4、 60M 双踪示波器 一台 四、 实验原理 提取载波的方法一般分为两类:一类是在发送有用信号的同时,在适当的频率位置上,插入一个(或多个)称为导频的正弦波,接收端就由导频提取出载波,这类方法称为导频插入法;另一类就是不专门发送导频,而在接收端直接从发送信号中提取载波,这类方法称为直接法。下面就重点介绍直接法的两种方法。 1、平方变换法和平方环法 设调制信号为()m t ,()m t 中无直流分量,则抑制载波的双边带信号为 t t m t s c ωcos )()(= 接收端将该信号进行平方变换,即经过一个平方律部件后就得到 t t m t m t t m t e c c ωω2cos )(2 12 )(cos )()(2 2 2 2 + = = 由式看出,虽然前面假设了()m t 中无直流分量,但2()m t 中却有直流分量,而()e t 表示式的第二项中包含有2ωc 频率的分量。若用一窄带滤波器将2ωc 频率分量滤出,再进行二分频,就获得所需的载波。根据这种分析所得出的平方变换法提取载波的方框图如图10-1所示。若调制信号()m t =±1,该抑制载波的双边带信号就成为二相移相信号,这时可得到下式,因而,用图10-1所示的方框图同样可以提取出载波。 t t t m t e c c ωω2cos 2 12 1]cos )([)(2 + = = 图10-1 平方变换提取载波 由于提取载波的方框图中用了一个二分频电路,故提取出的载波存在180°的相位模糊问题。对移相信号而言,解决这个问题的常用方法是采用相对移相。平方交换法提取载波方框图中的2c f 窄带滤波器若用锁相环代替,构成如图10-2所示的方框图,就称为平方环法提取载波。由于锁相环具有良好的跟踪、窄带滤波和记忆性能,平方环法比一般的平方变换法具有更好的性能。因此,平方环法提取载波应用较为广泛。 图10-2 平方环法提取载波 实验十五帧同步信号提取实验 实验十五帧同步信号提取实验一、实验目的1.掌握巴克码识别原理。2.掌握同步保护原理。3.掌握假同步、漏同步、捕捉态、维持态的概念。二、实验内容1.观察帧同步码无错误时帧同步器的维持态。2.观察帧同步器的假同步现象、漏识别现象和同步保护现象。三、实验器材1.信号源模块2.同步信号提取模块3.20M双踪示波器4.频率计一台一台四、实验原理于数字通信系统传输的是一个接一个按节拍传送的数字信号单元,即码元,因而在接收端必须按与发送端相同的节拍进行接收,否则,会因收发节拍不一致而导致接收性能变差。此外,为了表述消息的内容,基带信号都是按消息内容进行编组的, 因此,编组的规律在收发之间也必须一致。在数字通信中,称节拍一致为“位同步”,称编组一致为“帧同步”。在时分复用通信体统中,为了正确地传输信息,必须在信息码流中插入一定数量的帧同步码,它可以是一组特定的码组,也可以是特定宽度的脉冲,可以集中插入,也可以分散插入。集中式插入法也称为连贯式插入法,即在每帧数据开头集中插入特定码型的帧同步码组,这种帧同步法只适用于同步通信系统,需要位同步信号才能实现。适合做帧同步码的特殊码组很多,对帧同步码组的要求是它们的自相关函数尽可能尖锐,便于从随机数字信息序列中识别出这些帧同步码组,从而准确定位一帧数据的起始时刻。于这些特殊码组{x1,x2,x3,?,xn}是一个非周期序列或有限序列,在求它的自相关函数时,除了在时延j=0的情况下,序列中的全部元素都参加相关运算外;在j≠0的情况下,序列中只有部分元素参加相关运算,其表示式为 R(j)??xixi?j i?1n?j通常把这种非周期序列的自相关函数称为局部自相关函数。对同步码组的另一个要求是识别器应该尽量简单。目前,一种常用的帧同步码组是巴克码。巴克码是一种非周期序列。一个n位的巴克码组为{x1,x2,x3,?,xn},其中xi取值为+1或-1,它的局部自相关函数为15-1 R(j)??xixi?ji?1n?j?n???0或?1?0?j?00?j?n j?n目前已找到的所有巴克码组如表15-1所列。表15-1 巴克码组n 2 3 4 5 7 11 13 巴克码组++ ++- +++-;++-+ ++++-+ +++――+- +++――― 《通信原理》实验报告 实验十:载波同步提取试验 系别:信息科学与工程学院 专业班级:通信1003 学生姓名:揭芳 学号:20101182073 同组学生:杨亦奥 成绩: 指导教师:惠龙飞 (实验时间:20 12 年12 月28 日——20 12 年12 月28 日) 华中科技大学武昌分校 一、实验目的 1、 掌握用科斯塔斯(Costas )环提取相干载波的原理与实现方法。 2、 了解相干载波相位模糊现象的产生原因。 二、实验内容 1、 观察科斯塔斯环提取相干载波的过程。 2、 观察科斯塔斯环提取的相干载波,并做分析。 三、实验器材 1、 信号源模块 一块 2、 ③号模块 一块 3、 ⑦号模块 一块 4、 60M 双踪示波器 一台 四、实验原理 (一)基本原理 同步是通信系统中一个重要的实际问题。当采用同步解调或相干检测时,接收端需要提供一个与发射端调制载波同频同相的相干载波。这个相干载波的获取方法就称为载波提取,或称为载波同步。 提取载波的方法一般分为两类:一类是在发送有用信号的同时,在适当的频率位置上,插入一个(或多个)称为导频的正弦波,接收端就由导频提取出载波,这类方法称为导频插入法;另一类就是不专门发送导频,而在接收端直接从发送信号中提取载波,这类方法称为直接法。下面就重点介绍直接法的两种方法。 1、 平方变换法和平方环法 设调制信号为()m t ,()m t 中无直流分量,则抑制载波的双边带信号为 t t m t s c ωcos )()(= 接收端将该信号进行平方变换,即经过一个平方律部件后就得到 由式(17-1)看出,虽然前面假设了()m t 中无直流分量,但2()m t 中却有直流分量,而()e t 表示式的第二项中包含有2ωc 频率的分量。若用一窄带滤波器将2ωc 频率分量滤出, 实验十三 帧同步信号提取实验 一、实验目的 1、掌握巴克码识别原理。 2、掌握同步保护原理。 3、掌握假同步、漏同步、捕捉态、维持态的概念。 二、实验内容 1、观察帧同步码无错误时帧同步器的维持态。 2、观察帧同步器的假同步现象、漏识别现象和同步保护现象。 三、实验仪器 1、信号源模块 2、同步信号提取模块 3、20M 双踪示波器 一台 4、频率计(选用) 一台 5、连接线 若干 四、实验原理 由于数字通信系统传输的是一个接一个按节拍传送的数字信号单元,即码元,因而在接收端必须按与发送端相同的节拍进行接收,否则,会因收发节拍不一致而导致接收性能变差。此外,为了表述消息的内容,基带信号都是按消息内容进行编组的,因此,编组的规律在收发之间也必须一致。在数字通信中,称节拍一致为“位同步”,称编组一致为“帧同步”。在时分复用通信系统中,为了正确地传输信息,必须在信息码流中插入一定数量的帧同步码,它可以是一组特定的码组,也可以是特定宽度的脉冲,可以集中插入,也可以分散插入。集中式插入法也称为连贯式插入法,即在每帧数据开头集中插入特定码型的帧同步码组,这种帧同步法只适用于同步通信系统,需要位同步信号才能实现。适合做帧同步码的特殊码组很多,对帧同步码组的要求是它们的自相关函数尽可能尖锐,便于从随机数字信息序列中识别出这些帧同步码组,从而准确定位一帧数据的起始时刻。由于这些特殊码组123{,,,...,}n x x x x 是一个非周期序列或有限序列,在求它的自相关函数时,除了在时延j =0的情况下,序列中的全部元素都参加相关运算外,在j ≠0的情况下,序列中只有部分元素参加相关运算,其表示式为 ∑-=+=j n i j i i x x j R 1)( (13-1) 通常把这种非周期序列的自相关函数称为局部自相关函数。对同步码组的另一个要求是识别器应该尽量简单。目前,一种常用的帧同步码组是巴克码。 巴克码是一种非周期序列。一个n 位的巴克码组为{x 1,x 2,x 3,…,x n },其中x i 取值为 课程设计任务书 学生姓名:专业班级: 指导教师:阙大顺王虹工作单位:信息工程学院 题目: 位同步信号提取电路功能模块的设计与建模 初始条件: (1)MAX PLUSII、Quartus II、ISE等软件; (2)课程设计辅导书:《通信原理课程设计指导》 (3)先修课程:数字电子技术、模拟电子技术、电子设计EDA、通信原理。 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)(1)课程设计时间:周; (2)课程设计题目:位同步信号提取电路功能模块的设计与建模; (3)本课程设计统一技术要求:按照要求题目进行逻辑分析,掌握锁相法,画出实现电路原理图,设计出各模块逻辑功能,编写VHDL语言程序,上机调试、仿真,记录实验结果波形,对实验结果进行分析; (4)课程设计说明书按学校“课程设计工作规范”中的“统一书写格式”撰写,并标明参考文献至少5篇; (5)写出本次课程设计的心得体会(至少500字)。 时间安排:第19周 参考文献:段吉海.数字通信系统建模与设计.北京:电子工业出版社,2004 江国强.EDA技术与应用. 北京:电子工业出版社,2010 John G. Proakis.Digital Communications. 北京:电子工业出版社,2011 指导教师签名:年月日 系主任(或责任教师)签名:年月日 目录 1 软件介绍 (2) 2 设计原理 (3) 3 设计思路 (4) 3.1设计方法 (4) 3.2思路流程 (4) 4 电路仿真 (6) 4.1 码型变换模块 (6) 4.2鉴相模块 (7) 4.3 控制调节模块 (8) 5 运行结果与总结 (9) 6 总电路图 (10) 7 心得体会 (11) 8 参考文献 (12) 9 成绩评定表 (13)实验十二优选资料位同步信号提取实验

滤波法及数字锁相环法位同步提取实验和帧同步提取实验教学文案

滤波法及数字锁相环法位同步提取实验 模拟锁相环实验 载波同步帧同步实验

中南大学通信原理实验报告(截图完整)

通信原理载波提取实验报告

帧同步、帧识别实验报告

实验十八 位同步提取实验

帧同步提取试验

通信原理实验习题解答

通信原理实验 自定义帧结构的帧形成及其传输 自定义帧结构的帧同步系统 实验报告

基于FPGA的基带信号的位同步信号提取(附程序)【毕业设计论文】

帧同步信号恢复实验报告

(精编)哈工大通信原理实验报告

实验十 载波同步提取实验

实验十五 帧同步信号提取实验

载波同步提取试验概要

实验十三 帧同步信号提取实验

位同步信号提取电路功能模块的设计与建模