ASIC设计-FPGA原型验证

- 格式:pdf

- 大小:8.70 MB

- 文档页数:124

一种具有双PCI接口的ASIC验证系统

何妍;李树国;羊性滋

【期刊名称】《微电子学》

【年(卷),期】2006(36)2

【摘要】针对集成PCI接口功能的ASIC的设计开发,提出了一种具有双PCI接口的ASIC验证系统。

该系统充分复用软硬件资源,可应用于开发流程的全过程,有效地缩短了开发时间,降低了成本。

文章最后给出了高速RSA加密芯片验证系统的应用实例。

【总页数】5页(P162-166)

【关键词】PCI接口;ASIC验证;FPGA

【作者】何妍;李树国;羊性滋

【作者单位】清华大学微电子学研究所

【正文语种】中文

【中图分类】TN702

【相关文献】

1.一种FPGA模拟射频在ASIC原型验证系统中的应用 [J], 商阳;王茜竹

2.一种具有双CANBUS接口的通用多功能DI模块设计和应用 [J], 戴荣平;李振华;屠勤

3.一种具有双CANBUS接口的ISA(PC104)板卡的设计和应用 [J], 戴荣平;李振华

4.一种基于FPGA的双接口NFC芯片验证系统 [J], 彭广;李小进;初建朋;曹玉升

5.具有PCI链接功能的单片GPIB ASIC解决方案 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

ASIC用封装技术

村上元;蔡萌华

【期刊名称】《杭州电子工业学院译丛》

【年(卷),期】1990(000)002

【总页数】7页(P77-83)

【作者】村上元;蔡萌华

【作者单位】不详;不详

【正文语种】中文

【中图分类】TN405

【相关文献】

1.Effects of Agaricus blazei Murill Polysaccharides on Leadinduced Disturbance of Morphology and ASIC1a and ASIC2b Gene Expression in Hippocampus of Rats [J], Xin LI;Xiru LV;Cuiping FENG;Mingchang CHANG;Hongyan CHENG;Junlong MENG;;;;;;;;;;;;;;;;

2.从ASIC到FPGA,到类似ASIC用心寻找道路,走向设计成功 [J], John East

3.提高ASIC验证的速度与可视性基于FPGA的ASIC/SoC原型设计及基于FPGA 的系统在实时硬件速度下可以实现100%的内部信号可视性 [J], Mario Larouche

4.慢性缺氧对大鼠岩神经节神经元ASIC1a和ASIC1b表达的影响 [J], 杨荫;郑煜;陈祁;王乾成;赵书;陈丽

5.拥有ASIC级架构和ASIC增强型设计方案的20nm UltraScale产品 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

SOC设计原理结课论文基于FPGA的图像处理开发板设计姓名:XX班级:XX学号:XX论文要求:结课论文1、题目自拟。

2、内容要求:FPGA方面,SOC方面,SOPC方面,硬件语言HDL(Verilog或者VHDL),处理器软核(NiosII或Microblaze)方面;论文以应用类为主。

3、要按照通用格式来写,摘要、关键词、正文、参考文献一定要有。

4、字数不少于3000字(至少3页,行距1.5)。

基于FPGA的SoC原型验证的设计与实现摘要随着SoC设计规模的与日俱增,其功能日趋复杂,芯片的验证阶段占据了整个芯片开发的大部分时间。

为了缩短验证时间,在传统的仿真验证的基础上涌现了许多新的验证手段,如SDV(Software Driven verification)、BFM(Bus Function Model)等,以及基于FPGA的原型验证技术。

因FPGA工艺及技术的发展,其速度、容量和密度都大大增加,功耗和成本在不断的降低,使得基于FPGA的原型验证得到广泛的应用。

基于FPGA的原型验证可以比软件仿真速度高出4~6个数量级,而且还可以提高流片成功率,并为软件开发提供了硬件平台,加速了软件的开发速度。

关键字:时序分析原型验证布局布线存储单元本文主要论述了FPGA基原型验证的实现方法,并且针对ARM1136为内核的SoC,如何快速而有效地搭建一个原型验证平台做了详细的论述,最后还以UART为例来说明一种简单、可重用性好、灵活性强的测试程序架构。

1 基于ARM1136的SoC设计本文验证的SoC芯片是定位于手持视频播放设备、卫星导航产品的高性能应用处理器,采用了ARM1136作为内核,ARM11在提供超高性能的同时,还能保证功耗、面积的有效性。

同时在这个架构中还采用了ARM公司的AMBA(Advanced Microcontroller Bus Architecture)总线,它是一组针对基于ARM核的片上系统之间通信而设计的标准协议。

SoC原型验证平台开发中国科学院计算技术研究所,北京中科亿芯信息技术有限公司蒋毅飞[摘要] 工艺的进步使芯片的规模越来越大,在单个芯片内集成多个IP核、甚至集成多个CPU核成为可能,这对在FPGA上进行功能验证提出了更高的要求。

由于FPGA容量的增长速度远远落后于ASIC芯片规模的增长速度,因此构建多FPGA系统(MFS,Multi-FPGA Systems)成为唯一可行的解决方案。

本文介绍了一种面向SoC的多FPGA验证平台:SEE(SoC Emulation Engine)。

SEE1.0平台具有大容量、模块化、可扩展等优点,单个SEE1.0模块可提供相当于4000万门的容量,可满足大规模SoC设计的FPGA验证需求。

本文还介绍了如何利用Mentor Graphics公司的DxDesigner、IO Designer、Expedition PCB、ICX Pro等设计/仿真工具来完成SEE1.0系统的设计实例。

[关键词] FPGA验证 多FPGA系统 SoC模拟平台1 引言随着设计与制造技术的发展,集成电路设计从晶体管的集成发展到逻辑门的集成,现在又发展到IP的集成,即SoC(System-on-Chip)设计技术。

SoC就是将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上[Zhan05]。

SoC的出现使集成电路发展成为集成系统,整个电子整机的功能将可以集成到一块芯片中。

在不久的将来,集成电路与电子整机之间的界限将被彻底打破。

SoC可以有效降低电子信息系统产品的开发成本、缩短开发周期、提高产品的竞争力,是未来业界将采用的最主要的产品开发方式。

在设计SoC的过程中,功能验证(Functional Verification)使用的资源已经超过整个设计的48%[Youn05]。

通过仿真(simulation)可以在设计周期中发现许多问题并加以改正,这使得仿真已经成为设计验证的最可行的方式。

VLSI设计的FPGA验证标准实验报告实验三:计数器改进设计及其FPGA验证实验电子科技大学·《电子设计自动化技术》课程组实验(一)标准实验报告实验原理:参见《VLSI设计的FPGA验证实验指导书》实验步骤及实验记录:1.步骤一:实验准备FPGA开发板(主芯片型号:某CS10某L)用跳线块将FPGA开发板上的program引脚与GND短接。

4.步骤四:FPGA开发板上电操作方法为:程序→某ilin某FoundationSerie3.1i→Acceorie→JTAGprogrammer。

加载PROM配置文件(audio.mc),选择PROM器件封装型号(某c18v02_pc44)。

8.步骤八:FPGA配置项设置PROM器件某c18v02_pc44的Operation选项选择为program,FPGA 器件某CS10某L_PC84的Operation选项选择为Bypa。

取下FPGA开发板上的program与GND短接的跳线块,FPGA进入运行状态;接上耳机试听音乐播放,听到了播放的音乐。

实验结论与分析:实验(二)标准实验报告实验名称:LED数码显示型计数器的FPGA验证实验实验目的:通过VHDL源程序编写与仿真、FPGA综合、FPGA物理实现及FPGA实验原理:参见《VLSI设计的FPGA验证实验指导书》实验步骤及实验记录:1.第一步:计数器的VHDL编程与源代码录入①计数器的VHDL源代码:LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITYcount10enISPORT(i,clr,en:INSTD_LOGIC;qa,qb,qc,qd:OUTSTD_LOGIC);ENDcount 10en;ARCHITECTURErtlOFcount10enISSIGNALcount_4:STD_LOGIC_VECTOR(3downto0);BEGINproce(i,clr)be ginif(clr='1')thencount_4<="0000";elif(i'eventandi='1')thenif(en='1')thenif(count_4="1001")thencount_4<="0000";elecount_4<=count_4+1;endif;endif;endif;endproce;qa<=count_4(0);qb<=count_4(1);qc<=count _4(2);qd<=count_4(3);ENDrtl;②LED数码显示驱动模块的源代码:libraryIEEE;ueIEEE.STD_LOGIC_1164.all;entitydiplayiport(I0,I1,I2,I3:inSTD_LOGIC;O_A,O_B,O_C,O_D,O_E,O_F,O_G:outSTD_LOGIC);enddiplay;architecturediplayofdiplayiignalM:STD_LOGIC_VECTOR(3downto0);ignalO:STD_LOGIC_VECTOR(6d ownto0);beginM<=I3&I2&I1&I0;PROCESS(M)BEGINcaeMiwhen"0000"=>O<="1000000";--0when"0001"=>O<="1111001";--1when"0010"=>O<="0100100";--2when"0011"=>O<="0110000";--3when"0100"=>O<="0011001";--4when"0101"=>O<="0010010";--5when"0110"=>O<="0000010";--6when"0111"=>O<="1011000";--7when"1000"=>O<="0000000";--8when"1001"=>O<="0010000";--9whenother=>O<="0000110";--Eendcae;endproce;O_A<=O(0);O_B<=O(1);O_C<=O(2);O_D<=O(3);O_E< =O(4);O_F<=O(5);O_G<=O(6);enddiplay;2.第二步:VHDL程序功能仿真仿真工具选择:Active-HDL。

INPA IPS设计验证平台1.产品介绍1.1.用途在电子系统(特别是算法逻辑密集型的电子系统)设计中,FPGA作为一种高速高集成度,灵活可靠的实现手段日益受到工程师的重视,特别是FPGA 芯片技术的发展一日千里,规模提升,速度加快,各种微处理器内核IP的使用,使得FPGA在很大程度上可以成为电子系统的主要(或唯一)计算核心。

而在SoC/ASIC设计领域,FPGA也是设计前端的主要验证方法。

FPGA的开发主要要依靠HDL硬件描述语言来完成,对于这类特殊的语言开发有一套完整的设计流程来约束。

其中最重要的一个环节就是软件开发完成后的软仿真和硬件仿真验证工作。

在软仿真阶段通常包括RTL仿真和门级电路仿真,使用ModelSim,VCS等一类仿真工具(称为逻辑仿真器)。

但是由于FPGA的高速特性和逻辑算法密集的设计要求,往往在进行软仿真时速度非常慢,仿真验证是需要反复进行的,这就极大降低了FPGA开发的效率。

如果采用直接在FPGA硬件中进行硬件仿真调试,又缺乏调试所需的信号和变量的可见性,增大了缺陷定位和除错的难度。

基于此,需要在FPGA仿真验证阶段引入从软仿真到硬件仿真一体化集成的仿真验证工具,既能够通过仿真加速改善纯粹软仿真的效率低下问题,也能够在硬件仿真阶段通过强化信号可见性与软硬件测试集成提高FPGA设计的缺陷检测与除错能力。

InPA的IPS设计验证平台正是基于这样一个思路,为用户提供基于FPGA 的原型设计提供仿真加速、软硬件协同设计、以及验证暨除错的集成解决方案。

到目前为止,包括三大EDA厂商,以及一些业内著名的单点工具提供商均没有软硬件集成的FPGA仿真验证解决方案。

InPA所提供的IPS是唯一能够做到软件仿真加速,软硬件协同验证的工具平台。

2.IPS工具介绍2.1.IPS功能组成IPS 拥有一系列完整的工具套件,核心组件包括:●IPS Compiler:能自动执行编译流程,建立从RTL 到FPGA 的映射关系,帮助设计师合成、编译RTL 源代码,并能以用户控制的方式将大规模ASIC 设计和SoC 设计分割(Partition)到多颗FPGA 上,是实现联合仿真和仿真的自动编译器(Co‐Emulation and Emulation Compiler)。

数字集成电路物理设计作者:陈春章艾霞王国雄出版社:科学出版社出版日期:2008年1月页数:285 装帧:开本:16 版次:商品编号:2022071 ISBN:703022031 定价:36元丛书序前言第1章集成电路物理设计方法1.1数字集成电路设计挑战1.2数字集成电路设计流程l.2.1展平式物理设计1.2.2硅虚拟原型设计1.2.3层次化物理设计1.3数字集成电路设计收敛1.3.1时序收敛1.3.2功耗分析1.3.3可制造性分析1.4数字集成电路设计数据库1.4.1数据库的作用与结构1.4.2数据库的应用程序接口1.4.3数据库与参数化设计1.5总结习题参考文献第2章物理设计建库与验证2.1集成电路工艺与版图2.1.1 CMOS集成电路制造工艺简介2.1.2 CMOS器件的寄生闩锁效应2.1.3版图设计基础2.2设计规则检查2.2.1版图设计规则2.2.2 DRC的图形运算函数2.2.3 DRC在数字IC中的检查2.3电路规则检查2.3.1电路提取与比较2.3.2电气连接检查2.3.3器件类型和数目及尺寸检查数字集成电路物理设计2.3.4 LVS在数字IC中的检查2.4版图寄生参数提取与设计仿真2.4.1版图寄生参数提取2.4.2版图设计仿真2.5逻辑单元库的建立2.5.1逻辑单元类别2.5.2逻辑单元电路2.5.3物理单元建库与数据文件2.5.4时序单元建库与数据文件2.5.5工艺过程中的天线效应2.6总结习题参考文献第3章布图规划和布局3.1布图规划3.1.1布图规划的内容和目标3.1.2 I/0接口单元的放置与供电3.1.3布图规划方案与延迟预估3.1.4模块布放与布线通道3.2电源规划3.2.1电源网络设计3.2.2数字与模拟混合供电3.2.3时钟网络3.2.4多电源供电3.3布局3.3.1展平式布局3.3.2层次化布局3.3.3布局目标预估3.3.4标准单元布局优化算法3.4扫描链重组3.4.1扫描链定义3.4.2扫描链重组3.5物理设计网表文件3.5.1设计交换格式文件3.5.2其他物理设计文件3.6总结习题参考文献第4章时钟树综合4.1时钟信号4.1.1系统时钟与时钟信号的生成4.1.2时钟信号的定义4.1.3时钟信号延滞4.1.4时钟信号抖动4.1.5时钟信号偏差4.2时钟树综合方法4.2.1时钟树综合与标准设计约束文件4.2.2时钟树结构4.2.3时钟树约束文件与综合4.3时钟树设计策略4.3.1时钟树综合策略4.3.2时钟树案例4.3.3异步时钟树设计4.3.4锁存器时钟树4.3.5门控时钟4.4时钟树分析4.4.1时钟树与时序分析4.4.2时钟树与功耗分析4.4.3时钟树与噪声分析4.5总结习题参考文献第5章布线5.1全局布线5.1.1全局布线目标5.1.2全局布线规划5.2详细布线5.2.1详细布线目标5.2.2详细布线与设计规则5.2.3布线修正5.3其他特殊布线5.3.1电源网络布线5.3.2时钟树布线5.3.3总线布线数字集成电路物理设计5.3.4实验布线5.4布线算法5.4.1通道布线和面积布线5.4.2连续布线和多层次布线5.4.3模块设计和模块布线5.5总结习题参考文献第6章静态时序分析6.1延迟计算与布线参数提取6.1.1延迟计算模型6.1.2电阻参数提取6.1.3电容参数提取6.1.4电感参数提取6.2寄生参数与延迟格式文件6.2.1寄生参数格式sPF文件6.2.2标准延迟格式SDF文件6.2.3 sDF文件的应用6.3静态时序分析6.3.1时序约束文件6.3.2时序路径与时序分析6.3.3时序分析特例6.3.4统计静态时序分析6.4时序优化6.4.1造成时序违例的因素6.4.2时序违例的解决方案6.4.3原地优化6.5总结习题参考文献第7章功耗分析7.1静态功耗分析7.1.1反偏二极管泄漏电流7.1.2门栅感应漏极泄漏电流7.1.3亚阈值泄漏电流7.1.4栅泄漏电流7.15静态功耗分析第8章信号完整性分析第9章低功耗设计技术与物理实施第10章芯片设计的终验证与签核附录索引数字专用集成电路的设计与验证本书作者:杨宗凯,黄建,杜旭编著第1章概述1.1 引言1.2 ASIC的概念1.3 ASIC开发流程1.4 中国集成电路发展现状第2章Verilog HDL硬件描述语言简介2.1 电子系统设计方法的演变过程2.2 硬件描述语言综述2.3 Verilog HDL的基础知识2.4 Verilog HDL的设计模拟与仿真第3章ASIC前端设计3.1 引言3.2 ASIC前端设计概念3.3 ASIC前端设计的工程规范3.4 设计思想3.5 结构设计3.6 同步电路3.7 ASIC前端设计基于时钟的划分3.8 同步时钟设计3.9 ASIC异步时钟设计4.10 小结第4章ASIC前端验证4.1 ASIC前端证综述4.2 前端验证的一般方法4.3 testbench4.4 参考模型4.5 验证组件的整合与仿真4.6 小结第5章逻辑综合5.1 综合的原理和思路5.2 可综合的代码的编写规范5.3 综合步骤5.4 综合的若干问题及解决……第6章可测性技术第7章后端验证附录A 常用术语表附录B Verilog语法和词汇惯用法附录C Verilog HDL关键字附录D Verilog 不支持的语言结构参考文献yoyobao编号:book194094作者:杨宗凯,黄建,杜旭编著(点击查看该作者所编图书)出版社:电子工业出版社(点击查看该出版社图书)出版日期:2004-10-1ISBN:7121003783装帧开本:胶版纸/0开/ 0页/480000字版次:1原价:¥28VLSI设计方法与项目实施点击看大图市场价:¥43.00 会员价:¥36.55【作者】邹雪城;雷鑑铭;邹志革;刘政林[同作者作品]【丛书名】普通高等教育“十一五”规划教材【出版社】科学出版社【书号】9787030194510【开本】16开【页码】487【出版日期】2007年8月【版次】1-1【内容简介】本书以系统级芯片LCD控制器为例,以数模混合VLSI电路设计流程为线索,系统地分析了VLSI系统设计方法,介绍了其设计平台及流行EDA软件。

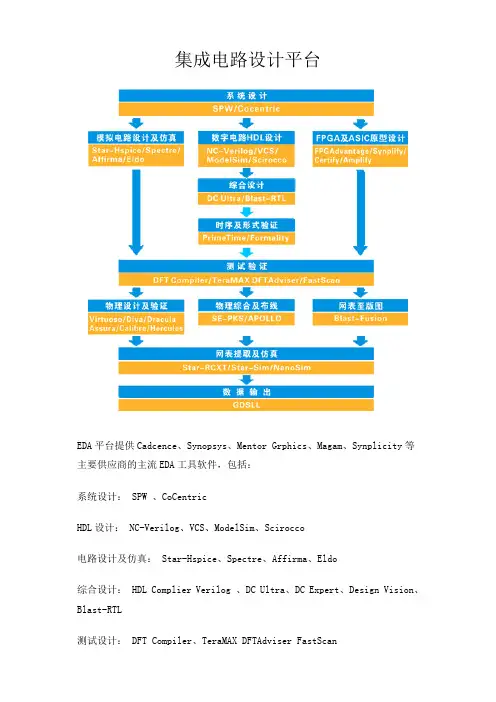

集成电路设计平台EDA平台提供Cadcence、Synopsys、Mentor Grphics、Magam、Synplicity等主要供应商的主流EDA工具软件,包括:系统设计: SPW 、CoCentricHDL设计: NC-Verilog、VCS、ModelSim、Scirocco电路设计及仿真: Star-Hspice、Spectre、Affirma、Eldo综合设计: HDL Complier Verilog 、DC Ultra、DC Expert、Design Vision、Blast-RTL设计验证:LEDA Checker 、LEDA Specifier、PrimeTime 、Formality 、PowerMill物理设计及验证:Hspice/AvanWaves、Virtuoso、Diva、Dracula、Assura、Calibre、Hercules物理综合及布线: SE-PKS、Apollo网表提取及后仿真: Star-RCXT、Star-Sim、NanoSim网表至版图: Blast-FusionFPGA及ASIC原型设计:FPGAdvantage、Synplify、Certify、Amplify数字电路设计工具模拟/数.模混合信号电路设计工具Hard/Soft协调设计工具LSI Layout设计工具测试工具印刷电路版设计工具其他的工具PLD开发系统采用Synopsys的Galaxy设计和发现验证平台(Design and Discovery Verification Platforms),以及广泛的DesignWare知识产权组合,作为智芯科技的主要内部设计流程。

Galaxy设计平台所采用的工具包括Physical Compiler、PrimeTime SI、DFT Compiler、TetraMAX、Power Compiler、Jupiter XT、Astro、Star-RCXT和Hercules。

FPGA技术正处于高速发展时期,新型芯片的规模越来越大,成本也越来越低,低端的FPGA已逐步取代了传统的数字元件,高端的FPGA不断在争夺AS IC的市场份额。

本节从FPGA软、硬件来展望未来的FPGA设计技术,给读者留一个FPGA技术的宏观轮廓。

1 未来可编程器件的发展趋势先进的ASIC生产工艺已经被用于FPGA的生产,越来越丰富的处理器内核被嵌入到高端的FPGA芯片中,基于FPGA的开发成为一项系统级设计工程。

随着半导体制造工艺的不同提高,FPGA的集成度将不断提高,制造成本将不断降低,其作为替代ASIC来实现电子系统的前景将日趋光明。

workcodi (1)大容量、低电压、低功耗FPGA大容量FPGA是市场发展的焦点。

FPGA产业中的两大霸主:Altera和Xili nx在超大容量FPGA上展开了激烈的竞争。

2007年Altera推出了65nm工艺的S tratixIII系列芯片,其容量为67200个L E (Logic Element,逻辑单元),Xilinx 推出的65nm工艺的VitexVI系列芯片,其容量为33792个Slices (一个Slices约等于2个L E)。

采用深亚微米(DSM)的半导体工艺后,器件在性能提高的同时,价格也在逐步降低。

由于便携式应用产品的发展,对FPGA的低电压、低功耗的要日益迫切。

因此,无论那个厂家、哪种类型的产品,都在瞄准这个方向而努力。

(2)系统级高密度FPGA随着生产规模的提高,产品应用成本的下降,FPGA的应用已经不是过去的仅仅适用于系统接口部件的现场集成,而是将它灵活地应用于系统级(包括其核心功能芯片)设计之中。

在这样的背景下,国际主要FPGA厂家在系统级高密度F PGA的技术发展上,主要强调了两个方面:FPGA的IP( Intellec2tual Property,知识产权)硬核和IP软核。

当前具有IP内核的系统级FPGA的开发主要体现在两个方面:一方面是FPGA厂商将IP硬核(指完成版图设计的功能单元模块)嵌入到FPGA器件中,另一方面是大力扩充优化的IP软核(指利用HDL语言设计并经过综合验证的功能单元模块),用户可以直接利用这些预定义的、经过测试和验证的IP核资源,有效地完成复杂的片上系统设计。

新思科技Synphony HLS解决方案新思科技公司(Synopsys)推出该公司最新研发的Synphony HLS (High Level Synthesis)解决方案。

该解决方案集成了M语言和基于模型的综合法,与传统RTL流程相比,能够为通信和多媒体应用提供高达10倍速的更高的设计和验证能力。

Synphony HLS 为ASIC 和FPGA的应用、架构和快速原型生成最优化的RTL。

Synphony HLS解决方案架构图新思科技公司高层级综合法和系统级别营销总监Chris Eddington介绍说,Synphony HLS 解决方案可显着地改变ASIC和FPGA在系统验证和嵌入式软件开发中的应用方式。

传统的HLS方法继续承担着重要的硬件工程资源,将算法翻译成RTL,在ASIC和FPGA芯片上进行运行。

Synphony HLS能够用MATLAB进行高层级仿真和产品编码,这意味着以往要用数月或数年的时间从仿真到达硬件,现在使用Synphony HLS解决方案仅用几小时或几天的时间就能够完成。

Chris Eddington说,这主要原因是Mathworks的MATLAB环境能够在极高的抽象层级上进行简洁地行为表达,现已被广泛地用于算法探索和设计。

在这种环境下开发的M语言模型通常在RT 层级(RTL)下被进行重新编码和重新验证,有些情况下用C/C++进行实施和验证。

与效率低下和容易出错的人工重新编码流程不同,Synphony HLS直接从高层次的M语言编码和Synphony HLS 优化的IP模型库中创建可执行的RTL和C模型。

通过采用独特的约束驱动的定点传播功能,设计师们可以快速和直观地从高层次浮点M 码的可综合子集中获得定点模型。

然后Synphony HLS引擎将合成已从架构上进行了优化的RTL,以满足面积、速度和功耗等目标要求。

Synphony HLS允许设计师们能够保留他们喜欢的算法建模语言,无需重新编码和重新验证模型,从而确保了早期的系统级别的验证和核查。

项目管理基础——ASIC项目管理实例邹志革华中科技大学电子系ASIC项目管理实例1.立项2.团队组建3.制定项目计划4.项目实施5.项目控制6.项目收尾Zou Zhige VLSI, EST2Zou Zhige VLSI, EST 31 立项¾项目来源?¾项目背景?¾谁是项目经理,谁是上级领导?¾项目的基本要求?¾项目基本的可用资源?¾在项目团队组建之前的立项实际上是意向上的立项!Zou Zhige VLSI, EST 4ASIC 项目立项¾项目策划立项阶段的流程是:市场需求Æ调研Æ可行性研究Æ论证Æ决策Æ任务书。

¾在这个阶段必须形成项目任务书(项目进度,周期管理等)和ASIC 规格定义。

¾此阶段的任务是:初步的体系结构设计、预估芯片的面积、风险及成本分析、初步的资源需求计划、预估完成项目所需的时间及所需的资源研发费用、确定项目总体设计目标及阶段性设计目标、设计工具及设计所采取工艺设计路线图等。

Zou Zhige VLSI, EST 5LCD 控制器的项目立项¾近年以来,全球通信、网络、便携式产品日新月异,这其中包括移动电话、个人数字助理(PDA )、便携式VCD 和DVD 、数码相机、数码摄像机、汽车导航系统等应用LCD 面板的主要产品。

¾LCD 具有轻薄短小、低耗电量、无辐射危险,平面直角显示以及影像稳定不闪烁等优势。

并且,随着价格的不断下跌,LCD 逐渐成为显示主流。

¾现在市场上常见的LCD 显示器主要包括两种:STN (Super Twisted Nematic )——超扭曲相列,和TFT (Thin Film Transistor )——薄膜晶体管。

Zou Zhige VLSI, EST 6LCD 控制器的项目立项¾LCD 控制器作为平板显示系统的核心部分,是影响显示效果的关键元件,它在LCD 显示系统中完成图像显示处理和时序控制功能。

用于ASIC的PGA外壳设计与工艺

高尚通

【期刊名称】《半导体情报》

【年(卷),期】1992(029)006

【摘要】本文叙述了用于ASIC的高密度封装之一-PGA外壳的设计和工艺方法。

【总页数】7页(P44-50)

【作者】高尚通

【作者单位】机电部第13研究所,石家庄050051

【正文语种】中文

【中图分类】TN305.94

【相关文献】

1.适用于FPGA、GPU和ASIC系统的电源管理 [J], Afshin Odabaee;

2.适用于FPGA、GPU和ASIC系统的电源管理 [J], Afshin Odabaee

3.提高ASIC验证的速度与可视性基于FPGA的ASIC/SoC原型设计及基于FPGA 的系统在实时硬件速度下可以实现100%的内部信号可视性 [J], Mario Larouche

4.从FPGA中的ASIC单元到ASIC中的FPGA单元 [J], Rodney Myrvaagnes

5.用于下一代汽车专用集成电路(ASIC)的嵌入式现场可编程逻辑门阵列(eFPGA) [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

在多核存储架构中,验证主要聚焦于确保多个处理器核心之间的数据一致性以及整个存储系统的正确操作。

这是因为多核处理器中的每个核心通常都有自己的本地缓存,并且可能会并发地对共享主内存进行读写操作,这就涉及到了缓存一致性(Cache Coherence)、内存一致性(Memory Consistency)以及互斥访问(Synchronization)等问题。

以下是多核存储架构验证的一些关键方面:缓存一致性验证:1.协议验证:o验证设计是否遵循特定的缓存一致性协议,如MESI(Modified, Exclusive, Shared, Invalid)、MOESI(加上Owned状态)或其他定制协议,确保在不同核心间的数据更新能够被正确传播和同步。

2.事件模拟:o模拟各种可能的缓存交互场景,包括缓存行迁移、缓存失效、写回等操作,检查是否按照预期工作,防止数据不一致。

3.硬件测试:o设计并执行硬件测试向量,通过实际电路或FPGA原型验证缓存一致性逻辑的实际行为。

4.形式化验证:o使用形式化方法证明缓存一致性逻辑的正确性,例如模型检测、定理证明等工具来保证设计不会违反一致性原则。

内存一致性模型验证:1.编程模型验证:o确保编译器和运行时环境支持并遵循特定的内存模型,比如顺序一致性模型、释放一致性模型等。

2.软件模拟和测试:o开发并执行多线程软件测试用例,特别关注临界区代码、锁机制和原子操作,观察它们在多核环境下的表现是否符合预期。

3.性能与正确性综合测试:o采用专门的多核测试框架和工具来生成复杂的内存访问模式,分析多核程序在真实环境下的性能和正确性。

互斥与同步机制验证:1.锁机制验证:o对于互斥锁、读写锁等同步原语进行详尽测试,确认其在多核间的并发环境下能正确防止竞态条件。

2.原子操作验证:o确认原子操作如CAS(Compare and Swap)等在硬件层面的支持正确有效。

3.死锁和饥饿检测:o设计测试用例来发现潜在的死锁情况,并验证调度算法可以避免进程饥饿现象。

Goke MicroelectronicsASIC设计-FPGA原型验证ASIC Design TeamIASIC设计-FPGA原型验证目录1ASIC验证技术 (1)1.1 ASIC设计流程 (1)1.2 FPGA验证技术 (3)1.3 Altera与Xilinx工具对比 (3)1.4 VHDL与Verilog对比 (5)1.5 Verilog良好编程习惯 (6)2 基于ALTERA的ASIC验证 (9)2.1 Stratix IV FPGA资源与架构 (9)2.2 QuartusII设计工具 (10)2.3 ASIC设计转换 (11)2.3.1 PLL设计 (11)2.3.1 RAM设计 (16)2.4 时序约束 (19)2.4.1 QSF&Tcl (22)2.4.2 LogicLock (23)2.5 综合布局布线 (23)2.5.1综合设置 (24)2.5.2增量编译 (25)2.5.3 VQM & QXP (30)2.5.4 时序分析 (30)2.6 下载设计文件 (32)2.7 Debug (32)2.7.1 In-System Memory Content Editor (33)2.7.2 ChipPlanner (34)2.7.3 SignalTapII (38)2.7.4 Keep Signals (43)2.8 Example工程 (45)3 基于XILINX的ASIC验证 (49)3.1 Vertex-7 FPGA资源与架构 (49)3.2 设计工具ISE与Vivado (49)3.3 ASIC设计转换 (54)3.3.1 时钟资源 (54)3.3.2 PLL设计 (58)3.3.3 RAM设计 (61)IIGoke Microelectronics3.4 时序约束 (64)3.5 综合布局布线 (70)3.5.1 Blackbox (70)3.5.2 Keep Signals (71)3.5.3 Strategies (72)3.5.4 Incremental Compile (75)3.5.5 时序分析 (77)3.5.6 Generate Bitstream (81)3.6 下载设计文件 (84)3.6.1 下载bit文件 (84)3.6.2 下载mcs文件 (87)3.7 Debug (88)3.8 Example工程 (94)3.8.1 导入ISE & Synplify工程 (94)3.8.2 Working with Tcl (95)3.9 Gate Clock处理 (99)3.10多片FPGA验证 (101)4 DDR相关技术 (104)4.1 DDR Controller (108)4.2 DDR PHY (111)4.2.1 Altera PHY (111)4.2.2 Xilinx PHY (113)5 硬件技术 (117)5.1 PCB设计注意事项 (117)5.2 电磁兼容与信号完整性 (117)5.2.1 端接匹配 (118)5.2.2 防止地弹 (118)5.2.3 减小串扰 (118)5.2.4 降低电磁干扰 (119)5.3 FPGA开发板使用注意事项 (120)总结 (121)IIIGoke Microelectronics1 ASIC验证技术1.1 ASIC设计流程ASIC分为全定制和半定制。

全定制设计需要设计者完成所有电路的设计,因此需要大量人力物力,灵活性好但开发效率低下。

如果设计较为理想,全定制能够比半定制的ASIC芯片运行速度更快。

半定制使用库里的标准逻辑单元(Standard Cell),设计时可以从标准逻辑单元库中选择SSI、MSI、数据通路、存储器甚至系统级模块(如乘法器、微控制器等)和IP核,这些逻辑单元已经布局完毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。

现代ASIC常包含处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块. 这样的ASIC常被称为SoC(片上系统)。

由于SoC设计复杂度不断增加,使得缩短面市时间的压力越来越重。

虽然充分利用IP核大大减少了SoC的设计时间,但SoC验证仍然非常复杂耗时。

SoC 和ASIC的最大不同之处在于它的系统特性,除了大量硬件模块之外,SoC还需要大量的固件和软件,如操作系统、驱动程序、通讯协议以及应用程序等。

这使得传统的软件仿真工具已经无法完全解决验证的问题。

而且随着越来越多的需要处理大量实时数据的应用(如视频)出现,验证技术就要求能够在接近实时频率的条件下进行验证。

现在越来越多的ASIC 设计者自己设计FPGA 验证板来进行ASIC 设计验证。

用FPGA 验证ASIC 的好处是可以使软件的开发调试和ASIC 的开发调试并行的进行。

图1-1为典型的半定制设计流程,一般用来设计数字IC电路。

全定制的设计,一般用于设计模拟电路和数模混合电路。

本文主要讨论设计流程中的仿真验证,RTL仿真工具一般用到的有Cadence 的NC-verilog,Synopsys的VCS和Mentor的ModelSim。

RTL验证包括基于UVM等方法学的逻辑验证和基于FPGA的原型验证。

基于方法学的验证主要使用SystemVerilog产生可重用性好、功能覆盖率高和调试简易的测试激励。

常见的验证平台有UVM、OVM和VMM,都基于SystemVerilog 搭建的。

UVM是在OVM和VMM基础上推出的验证方法学的新的标准。

2006年,Synopsys公司推出了验证方法学手册(VMM),这个是RVM从vera语言过度到SystemVerilog的方法学。

2008年,Cadence公司和Mentor公司共同推出了OVM。

2010年,ACCELLERA采用了OVM作为基础,推出了UVM验证方法1ASIC 设计-FPGA 原型验证2学。

同时引入了VMM 的一些概念,作为业界方法学统一的一个雏形。

基于FPGA 的原型验证,主要有基于Altera 和Xilinx 的 FPGA 验证平台。

设计流程设计工具Matlab C C++SystemC C C++VHDL Verilog VCS NC-Verilog ModelSim SystemVerilog UVM FPGA DesignCompiler BuildGates Formality LEC PrimeTime Pearl Astro ICC Encounter Star-RCXT Assure-RCX Calibre-xRC Hercules Dracula Calibre图1-1数字IC 设计流程Goke Microelectronics1.2 FPGA验证技术随着SoC设计规模的与日俱增,其功能日趋复杂,芯片的验证阶段占据了整个芯片开发的大部分时间。

为了缩短验证时间,在传统的仿真验证的基础上涌现了许多新的验证手段,如SDV(Software Driven verification)、BFM(Bus Function Model)等,以及基于FPGA的原型验证技术。

因FPGA工艺及技术的发展,其速度、容量和密度都大大增加,功耗和成本在不断的降低,使得基于FPGA的原型验证得到广泛的应用。

基于FPGA的原型验证可以比软件仿真速度高出4~6个数量级,而且还可以提高流片成功率,并为软件开发提供了硬件平台,加速了软件的开发速度。

FPGA原型验证平台的硬件设计应该考虑FPGA的逻缉资源、应用资源、扩展能力、PCB信号质量、调试难度、组态和成本等方面的因素。

本原型验证系统采用的是基于Altera公司Stratix IV EP4SE820的开发板,和基于Xilinx公司Vertex-7 XC7V2000T的开发板,扩展板是根据SoC整体验证需求而设计的PCB 板。

虽然FPGA和ASIC所用资源和实现方式不同,但在进行原型设计中需要遵循的一个原则就是“尊重原设计”。

在FPGA现有资源情况下实现SoC时,尽可能地少改动原SoC设计,在此基础上需要对原设计做如下转换:1. 存储模块。

存储单元是必须进行代码转换的,ASIC中的存储单元通常用代工厂所提供的Memory Compiler来定制。

如果直接将ASIC代码中的存储单元作为FPGA的输入,通常综合器是综合不出来的,即使能综合出来,也要花费很长时间,并且资源消耗多、性能不好。

而FPGA厂商一般提供经过验证并优化的存储单元,因此存储单元要进行代码转换。

在设计里用FPGA的RAM宏单元来替换ESRAM,SoC芯片里面的DDR PHY是模拟的模块,此要替换成Altera或Xilinx公司的DDR PHY的IP核。

2. 时钟和门控。

数字电路中,时钟是整个电路最重要、最特殊的信号。

在ASIC中,用布局布线工具来放置时钟树,利用代工厂提供的PLL进行时钟设计。

而FPGA中通常已经配置一定数量的PLL宏单元,并有针对时钟优化的全局时钟网络,一般是经过FPGA的特定全局时钟管脚进入FPGA内部,后经过全局时钟BUF适配到全局时钟网络,这样的时钟网络可以保证相同的时钟沿到达芯片内部每一个触发器的延迟时间差异可以忽略不计,因此时钟单元需要采用FPGA 的PLL宏单元和专门的时钟布线资源来替换。

为了减少功耗,SoC设计中使用了门控时钟(clockgating),对于FPGA来说这种门控时钟容易产生毛刺,导致数据不正确,所以在FPGA设计中要使用时钟使能寄存器代替门控时钟。

1.3 Altera与Xilinx工具对比3ASIC设计-FPGA原型验证Altera和Xilinx是最大的两家FPGA厂商,Altera目前的高端器件是Stratix IV 系列,Xilinx是Vertex-7。

在SoC的验证过程中,我们希望FPGA的频率能够达到和SoC一样,但是验证过程中对于超过400万门的SoC,FPGA的最高运行频率不超过200M。

Altera和Xilinx这两家,在高端器件,Xilinx处于领先地位。

现在FPGA的规模越来越大,资源两家的高端器件都能满足一般开发验证,所以使用的瓶颈已经在软件这个层面。

从EDA软件来说,Altera软件要做的好,特别是编译综合和时序收敛方面,Xilinx的v7资源占用率才40%左右,就时序很难收敛,然后要用SmartXplorer来跑多个case,看下有没有能编译通过的,编译同样规模的工程要比Quartus慢很多,而且内存开销很大,route一个800万门的design要占用20G左右的内存。

毕竟对于用户来说,实现FPGA工程到成功编译下载的中间过程越短越好。

Xilinx从v7系列开始,使用新的软件vivado编译工具,ISE后面不在出新的版本,从这个角度也可以看出Xilinx自己都认为原来的ISE软件太差,vivado是新的软件架构,编译综合功能还是很差劲,但是布局布线功能改善很大,同样规模的design,要比ISE快一倍,内存开销少一半,所以一般用synplify综合,用vivado布局布线。