14-复习

- 格式:doc

- 大小:404.00 KB

- 文档页数:24

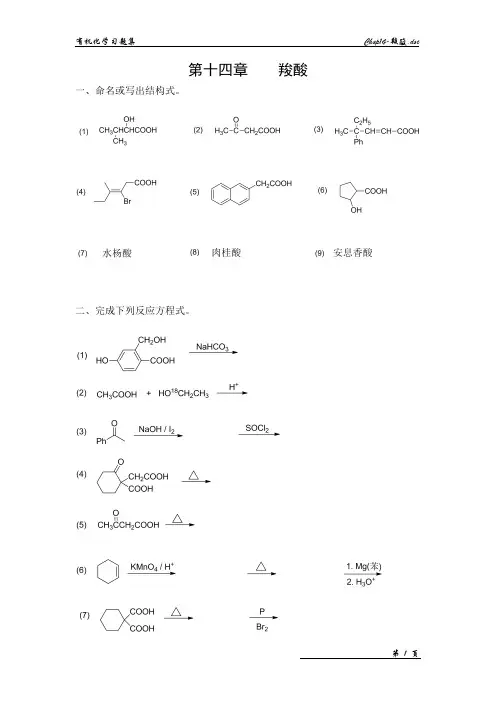

第十四章羧酸一、命名或写出结构式。

二、完成下列反应方程式。

三、选择题。

1.比较取代羧酸FCH2COOH(I),ClCH2COOH(II),BrCH2COOH(III),ICH2COOH(IV)的酸性大小是:()A.I>II>III>IVB.IV>III>II>IC.II>III>IV>ID.IV>I>II>III2.下列羧酸,酸性最强的是()A.对甲氧基苯甲酸B.对甲基苯甲酸C.对氯苯甲酸D.对硝基苯甲酸3.下列羧酸,酸性最强的是()A.邻硝基苯甲酸B.间硝基苯甲酸C.对硝基苯甲酸D.苯甲酸4.下列羧酸,酸性最弱的是()A.邻甲基苯甲酸B.间甲基苯甲酸C.对甲基苯甲酸D.苯甲酸5.下列化合物按酸性从大到小排列的次序为:()①乙酸②苯酚③水④碳酸⑤乙醇A.①>④>②>③>⑤B.④>①>②>③>⑤C.①>④>③>②>⑤D.④>①>③>⑤>②6.下列四种离子,碱性最强的是:()A.HO-B.CH3O-C.C6H5O-D.CH3COO-7.下列化合物中既能与托伦试剂发生银镜反应,又能与碳酸氢钠反应的是()A.乙醇B.乙醛C.甲酸D.乙二酸8.下列化合物沸点最高的是()A.CH3CH2CH2OHB.CH3CH2CHOC.CH3CH2CH2CH3D.CH3COOH9.下列哪个试剂能将CH3CH=CHCHO氧化成CH3CH=CHCOOH?A.托伦试剂B.酸性K2CrO7C.酸性KMnO4溶液D.臭氧10.乙醇与下列羧酸在酸催化下生成酯,反应速率哪个最快()A.(CH3)3CCOOHB.CH3CH2COOHC.(CH3)2CHCOOHD.CH3COOH四、用化学方法区别下列化合物。

1.乙醇、乙醛、乙酸2.草酸、丙二酸、丁二酸五、指出完成下列转变的较好的方法是(I)腈水解法、还是(II)格氏试剂法?六、从指定原料合成,其他试剂任选。

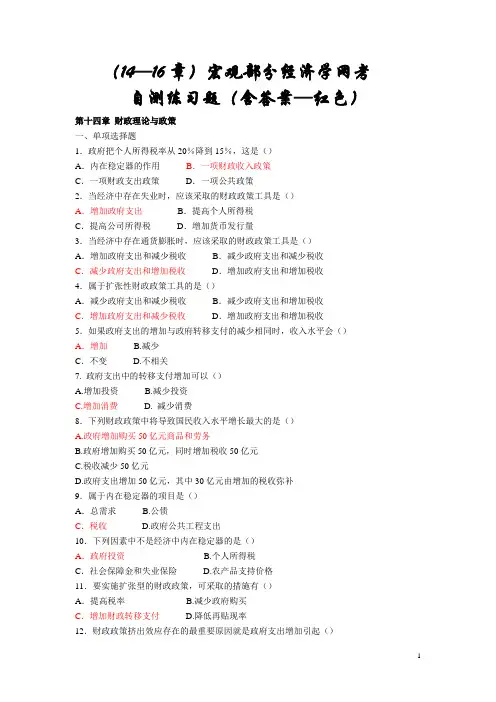

(14—16章)宏观部分经济学网考自测练习题(含答案—红色)第十四章财政理论与政策一、单项选择题1.政府把个人所得税率从20%降到15%,这是()A.内在稳定器的作用B.一项财政收入政策C.一项财政支出政策D.一项公共政策2.当经济中存在失业时,应该采取的财政政策工具是()A.增加政府支出B.提高个人所得税C.提高公司所得税D.增加货币发行量3.当经济中存在通货膨胀时,应该采取的财政政策工具是()A.增加政府支出和减少税收B.减少政府支出和减少税收C.减少政府支出和增加税收D.增加政府支出和增加税收4.属于扩张性财政政策工具的是()A.减少政府支出和减少税收B.减少政府支出和增加税收C.增加政府支出和减少税收D.增加政府支出和增加税收5.如果政府支出的增加与政府转移支付的减少相同时,收入水平会()A.增加 B.减少C.不变 D.不相关7. 政府支出中的转移支付增加可以()A.增加投资B.减少投资C.增加消费D. 减少消费8.下列财政政策中将导致国民收入水平增长最大的是()A.政府增加购买50亿元商品和劳务B.政府增加购买50亿元,同时增加税收50亿元C.税收减少50亿元D.政府支出增加50亿元,其中30亿元由增加的税收弥补9.属于内在稳定器的项目是()A.总需求 B.公债C.税收 D.政府公共工程支出10.下列因素中不是经济中内在稳定器的是()A.政府投资 B.个人所得税C.社会保障金和失业保险 D.农产品支持价格11.要实施扩张型的财政政策,可采取的措施有()A.提高税率 B.减少政府购买C.增加财政转移支付 D.降低再贴现率12.财政政策挤出效应存在的最重要原因就是政府支出增加引起()A.利率上升 B. 利率下降C.利率为零 D. 利率为负数13.在LM曲线不变的情况下,政府支出的增加会引起国民收入()A.增加,利率上升 B.增加,利率下降C.减少,利率上升 D.减少,利率下降14.赤字增加的时期是()A.经济衰退时期 B.经济繁荣时期C.高通货膨胀时期 D.低失业率时期二、多项选择题1.公共财政的基本特征是(ABC)A.满足社会公共需要B.具有非盈利性C.收支行为规范化D.公共分配E.具有盈利性2.公共财政的主要职能有(BCD)A.支付职能B.分配职能C.配置职能D.稳定职能E.调控职能3.财政支出的政策工具包括(CDE)A.税收B.公债C.政府购买D.转移支付E.政府投资4. 扩张性的财政政策包括(AD)A.增加政府支出B.减少政府支出C.增加税收D. 减少税收E.调节货币供给5.政府购买支出乘数的作用是(BCD)A.单方面的B.是双重的C.使国民收入数倍增加D.使国民收入数倍减少E.不存在的6.属于内在稳定器的项目是(BC)A.政府购买B.税收C.政府转移支付D.政府公共工程支付E.以上说法均正确7.经济萧条时政府应该(ADE)A.增加政府购买支出B.减少政府财政支出C.增加税收D.减少税收E.增加转移支付8.以下何种情况会引起收入水平的上升(ABC)A.增加自主性支出B.减少自主性税收C.增加自主性转移支付D.增加税收E.减少支出9.在经济衰退时期,依靠发行公债扩大政府支出的扩张性财政政策对经济有下述影响(AB)A.缓和经济萧条B.增加政府债务C.缓和了通货膨胀D.减少了政府债务E.税收增加10.实行赤字财政(AC)A.在短期内可以刺激经济增长B. 在长期内可以刺激经济增长C.在经济萧条时使经济走出衰退D.可以使经济持久繁荣E.对经济没有影响三、判断题错1.公共财政具有非盈利的特点,因此不必讲究效益问题。

13年《稀土材料化学》复习思考题1、什么叫稀土?写出所有稀土元素的名称及符号。

答:我们把位于元素周期表的第三副族,包括钪(Sc,)、钇(Y,)和镧系元素[包括镧(La,))、铈(Ce,)、镨(Pr,)、钕(Nd)、钷(Pm)、钐(Sm)、铕(Eu)、钆(Gd)、铽(Tb)、镝(Dy)、钬(Ho)、铒(Er)、铥(Tm)、镱(Yb)、镥(Lu)]的十七种元素总称为稀土元素.2、可以从哪几个方面来可以描述一个电子的运动状态?原子核外电子排布需要遵守哪几个原理?答:一个电子的运动状态要从4个方面来进行描述,即它所处的电子层、电子亚层、电子云的伸展方向、电子的自旋方向。

它们还要遵守能量最低原理、保里不相容原理和洪特规则。

对于多电子元素,还要考虑钻穿效应和屏蔽效应。

能量最低原理:电子在原子核外排布时,要尽可能使电子的能量最低。

保里不相容原理:在同一个原子中没有也不可能有运动状态完全相同的两个电子存在,即每一个轨道中只能容纳两个自旋方向相反的电子洪特规则: 一、电子在原子核外排布时,将尽可能分占不同的轨道,且自旋平行;二、对于同一个电子亚层,当电子排布处于全满、半满全空时比较稳定.3、什么叫屏蔽效应、钻穿效应?答:由于其他电子对某一电子的排斥作用而抵消了一部分核电荷,从而引起有效核电荷的降低,削弱了核电荷对该电子的吸引,这种作用称为屏蔽作用或屏蔽效应在原子核附近出现的概率较大的电子,可更多地避免其余电子的屏蔽,受到核的较强的吸引而更靠近核,这种进入原子内部空间的作用叫做钻穿效应。

4、写出稀土元素的电子层排布通式及镧、钪、钆、铥、铽、镝、铈等元素的核外电子排布方式.答:稀土元素的电子层排布通式:【Xe】4f x5d0-16s2镧、原子序数57,电子排布方式:【Xe】5d16s2钪、原子序数21,电子排布方式:【Ar】3d14s2钆、原子序数64,电子排布方式:【Xe】4f75d16s2铥、原子序数69,电子排布方式:【Xe】4f136s2铽、原子序数65,电子排布方式:【Xe】4f96s2镝、原子序数66,电子排布方式:【Xe】4f106s2铈、原子序数58,电子排布方式:【Xe】6s24f15d15、稀土电子结构具有哪几个显著特点?答:第一,所有稀土原子最外层都是s2结构,这就决定所有稀土金属都是活泼金属;第二,次外层具有nd 0~1 ns2np6结构第三、从铈到镥,电子开始填充在倒数第三层的4f轨道上。

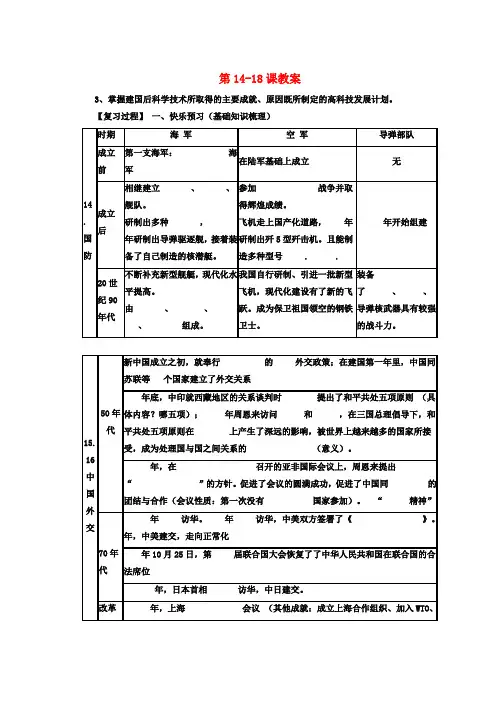

第14-18课教案3、掌握建国后科学技术所取得的主要成就、原因既所制定的高科技发展计划。

【复习过程】一、快乐预习(基础知识梳理)二、合作探究、拓展提高(重点知识讲解)1、关于新中国的海军、空军及导弹部队的建立及发展概况。

(1)海军建立: 舰队组建:①新中国成立前夕,中国人民解放军的第一支海军——华东军区海军建立;②新中国成立后,又相继建立了北海、东海和南海舰队。

军事装备:①1971年自行研制导弹驱逐舰;②1974③进入海军现代化水平有了明显提高,海军已由水面舰艇部队、潜艇部队、海军航空兵、海军陆战队等多兵种组成。

(2 开放后,空军现代化有了新的飞跃。

(3武器:中程、远程、洲际2、新中国外交的政策、主要成就、原因和意义?(1)政策:新中国成立之初,就奉行独立自主的和平外交政策。

70年代: 410月25法席位。

5、1972年,尼克松总统访华,中美双方在上海签署了《中美联合公报》,中美关系走向正常化 6、改革开放后:7、2001年,中国承办亚太经合组织会议(上海APEC会议),是中国迄今举行的规模最大、规格最高的多边外交活动。

(主题是“新世纪、新挑战:参与、合作,举办北京奥运会和上海世博会)(3)原因:①采取了积极灵活的外交政策②全国人民的共同努力(4)意义:为我国的现代化营造了一个和平的建设环境,加强了我国与世界各国各地区的经贸联系,为我国的改革开放和经济建设奠定了基础。

3、新中国所取得的的科技成就有哪些?著名科学家及所体现出来的精神?取得的的科技成就的原因?(110力量,也打破了帝国主义的核垄断,对维护世界和平具有重要意义)。

②1966年10(第五个独立发射卫星的国家,一箭三星、返回式卫星。

两弹一星指:原子弹、导弹和人造地球卫星)④1999年,成功发射第一艘无人飞船。

⑤2003年,成。

⑥1973)。

⑦1986年3月,制定发展高科技的(2精神:学习他们刻苦钻研、奋发图强、勇于创新和强烈的爱国、奉献精神,继承和发扬他们的优良品质,进一步增强建设有中国特色社会主义的决心和信心)。

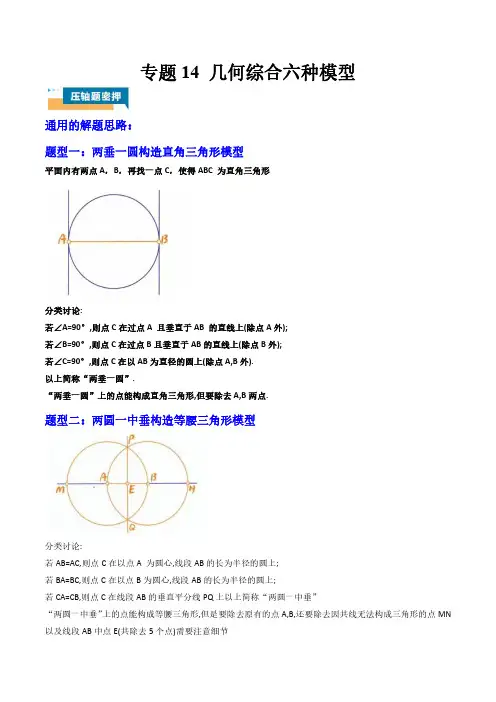

专题14几何综合六种模型通用的解题思路:题型一:两垂一圆构造直角三角形模型平面内有两点A,B,再找一点C,使得ABC为直角三角形分类讨论:若∠A=90°,则点C在过点A且垂直于AB的直线上(除点A外);若∠B=90°,则点C在过点B且垂直于AB的直线上(除点B外);若∠C=90°,则点C在以AB为直径的圆上(除点A,B外).以上简称“两垂一圆”.“两垂一圆”上的点能构成直角三角形,但要除去A,B两点.题型二:两圆一中垂构造等腰三角形模型分类讨论:若AB=AC,则点C在以点A为圆心,线段AB的长为半径的圆上;若BA=BC,则点C在以点B为圆心,线段AB的长为半径的圆上;若CA=CB,则点C在线段AB的垂直平分线PQ上以上简称“两圆一中垂”“两圆一中垂”上的点能构成等腰三角形,但是要除去原有的点A,B,还要除去因共线无法构成三角形的点MN 以及线段AB中点E(共除去5个点)需要注意细节题型三:胡不归模型【模型解读】一动点P 在直线MN 外的运动速度为V 1,在直线MN 上运动的速度为V 2,且V 1<V 2,A 、B 为定点,点C 在直线MN 上,确定点C 的位置使21AC BC V V +的值最小.(注意与阿氏圆模型的区分)1)121121=V AC BC BC AC V V V V ⎛⎫++ ⎪⎝⎭,记12V k V =,即求BC +kAC 的最小值.2)构造射线AD 使得sin ∠DAN =k ,CH k AC =,CH =kAC ,将问题转化为求BC +CH 最小值.3)过B 点作BH ⊥AD 交MN 于点C ,交AD 于H 点,此时BC +CH 取到最小值,即BC +kAC 最小.【解题关键】在求形如“PA +kPB ”的式子的最值问题中,关键是构造与kPB 相等的线段,将“PA +kPB ”型问题转化为“PA +PC ”型.(若k >1,则提取系数,转化为小于1的形式解决即可)。

一、基础知识 1、AT89C51、87C51、80C51和80C31单片机的相同之处是—— 制造工艺都为CHMOS,都有128字节片内RAM、两个定时/计数器、4个8位I/O并行口,一个串行口和5个中断源。 主要区别是:① 89C51片内4K字节FLASHROM; ② 87C51片内4K字节EPROM; ③ 80C51片内4K字节 掩膜ROM; ④ 80C31片内无程序存储器。

2.80C51单片机内部主要包含CPU、程序存储器、数据存储器、可编程I/O口、中断控制器、定时器/计数器、串行口等。 具体回答: ① 一个8位CPU; ② 4KB ROM or EPROM(8031无ROM); ③ 128字节RAM数据存储器; ④ 21个特殊功能寄存器SFR; ⑤ 4个8位并行I/O口,其中P0、P2为地址/数据线,可寻址64KB 程序存储器和64KB 数据存储器; ⑥ 一个可编程全双工串行口; ⑦ 具有5个中断源,两个优先级,嵌套中断结构; ⑧ 两个16位定时器/计数器; ⑨ 一个片内振荡器及时钟电路。

3.80C51单片机的CPU主要包含运算器(算术逻辑单元ALU、累加器ACC、寄存器B和程序状态字PSW)、控制器(时钟电路 、复位电路 、指令寄存器和指令译码器、程序计数器PC、堆栈指针SP、数据指针寄存器DPTR)。 CPU中的ALU能完成的算术运算有“+、-、×、÷”;逻辑运算有“取反、与 或、异或 ”。

4.对于8051来说, 程序存储器(ROM)的内部地址为 0000H~0FFFH, 共 4 KB; 外部地址为 1000H~FFFFH, 共 60 KB。 如果EA引脚接低电平则不使用内部程序存储器,而直接使用外部程序存储器;如果EA引脚接高电平,则当程序计数器由内部 0FFFH执行到外部 1000H 时, 会自动跳转。对于 8751 来说, 内部有 4 KB的EPROM, 将它作为内部程序存储器,外部最多可以扩展60KB程序存储器。 8031 内部无程序存储器, 必须外接程序存储器,使用时EA引脚需要接低电平,8031 最多可外扩 64 KB程序存储器。 程序存储器中 6 个单元地址具有特殊用途, 是保留给系统使用的。0000H是系统的启动地址, 一般在该单元中存放一条绝对跳转指令。0003H、000BH、 00013H、001BH和 0023H对应 5 种中断源的中断服务入口地址。

5.80C51单片机数据存储器可划分为:片内256 B数据存储器地址空间,片外最大可扩展64 KB的数据存储器地址空间。 MCS-51 单片机片内RAM为 256 字节, 地址范围为00H~FFH, 分为两大部分: 低 128 字节(00H~7FH)为真正的RAM区; 高 128 字节(80H~FFH)为特殊功能寄存器区SFR。 在低 128 字节RAM中, 00H~1FH共 32个单元是 4 个通用工作寄存器区。每一个区有 8 个通用寄存器R0~R7;R0和R1能用作间接寻址寄存器用,但R2~R7不能。 单片机系统开机复位后,CPU使用的是第0组工作寄存器。它们的地址是 00~07H。CPU通过对程序状态字PSW中RS1和RS0的设置来确定和改变当前工作寄存器组(RS1 RS0=00时,使用第0组工作寄存器;RS1 RS0=01时,使用第1组工作寄存器;RS1 RS0=10时,使用第2组工作寄存器;RS1 RS0=11时,使用第3组工作寄存器)。

20H~2FH共 16个 单元是可位寻址区;30H~7FH共 80个 单元称为数据缓冲区。 外部数据存储器一般由静态RAM构成,其容量大小由用户根据需要而定, 最大可扩展到 64 KB , 地址是 0000H~0FFFFH。 CPU通过MOVX指令访问外部数据存储器, 用间接寻址方式。 R0、R1和 DPTR都可作间接寄存器。注意, 外部RAM和扩展的I/O接口是统一编址的, 所有的外扩I/O口都要占用 64 KB中的地址单元。

6.MCS-51单片机有4个8位双向I/O接口P0~P3,共32根输入/输出线,每一条I/O口线都能独立使用(就是都可以位寻址的意思),且都由数据锁存器、输入缓冲器和输出驱动器等组成。4个口线都可以作为通用口使用。其中只有P1口是真正的用户口。而对于其他三个口线。 ① 当外接程序存储器或数据存储器时,P0口作为数据口线,同时P0口也分时复用地址线的低8位;P2口作为地址线高8位。 ② P3口有第二功能:串行接收和发送、外中断0和1、计数器输入0和1、外部数据存储器写读选通。

7.当MCS-51单片机的CPU访问外部存储器时,ALE用来锁存P0口输出的地址信号的低8位。 8.单片机并行输入、输出接口带载能力: ① P0 :8个LSTTL负载; ② P1、P2和P3口:4个LSTTL负载。

9.CPU总线信号在时间上的顺序关系称为时序(CPU的控制器实质是一个复杂的同步时序电路,所有工作都是在时钟信号控制下进行的)。每执行一条指令,CPU的控制器都要发出一系列特定的控制信号,这些控制在时间上的相互关系就是CPU的时序。 (1) 振荡周期: 也称时钟周期, 是指为单片机提供时钟脉冲信号的振荡源的周期。 (2) 状态周期: 每个状态周期为时钟周期的 2 倍, 是振荡周期经二分频后得到的。 (3) 机器周期: 一个机器周期包含 6 个状态周期S1~S6, 也就是 12 个时钟周期。 在一个机器周期内, CPU可以完成一个独立的操作。 (4) 指令周期: 它是指CPU完成一条操作所需的全部时间。 每条指令执行时间都是有一个或几个机器周期组成。 MCS - 51 系统中, 有单周期指令、双周期指令和四周期指令。 当单片机的时钟频率为12MHz时,一个机器周期是多少1μs(微秒);ALE引脚的输出频率是多少2MHz;当单片机的时钟频率选择6MHz时,一个机器周期为2μs ALE引脚的输出频率是多少1MHz。(机器周期=12/晶振频率)。

10. MCS-51单片机的,,EAALEPSEN信号各自的功能: 都是控制总线 ① PPVEA/:访问内部程序存储器的控制信号/编程电压输入端。1EA 时,CPU从片内读取指令,0EA CPU从片外读取指令。 ② PROGALE/:地址锁存允许/编程信号线。 ③ PSEN:外部程序存储器读选通信号。 ④VPDRSE/:复位输入信号/掉电保护后备电源引脚。 11.特殊功能寄存器PSW中: Cy—进位标志位、AC—辅助进位标志位、F0—用户标志位、OV—溢出标志位、P—奇偶 标志位。

12、MCS-51指令系统: ① 按功能分为5类,数据传送类、算术操作类、逻辑操作类、控制转移类和位操作类; ② 具有7种寻址方式; 立即寻址,寻址范围是程序存储器; 直接寻址,寻址范围是内部RAM低128字节和高128字节; 寄存器寻址,寻址范围是四组工作寄存器R0~R7; 寄存器间接寻址,寻址范围是内部RAM的低128和外部RAM低64K可寻址空间; 基址寄存器加变址寄存器间接寻址,寻址范围是程序存储器; 相对寻址,寻址范围是以下一条指令为相对地址的-128~+127字节范围内; 位寻址,寻址范围是可位寻址空间,包括内部RAM的可寻址位,特殊功能寄存器中的可寻址位。

13、伪指令又称汇编程序控制译码指令,属于说明性汇编指令,汇编时不产生机器指令代码,不影响程序的执行,仅产生供汇编用的某些命令,在汇编时执行某些特殊操作。 常用的伪指令有: 汇编起始地址伪指令 ORG 汇编终止伪指令 END 汇编赋值伪指令 EQU 定义字节伪指令 DB 定义字伪指令 DW 定义空间伪指令 DS 位定义伪指令 BIT

14.对80C51单片机,访问内部数据存储器可用直接寻址方式,也可以用寄存器间接寻址方式;但访问特殊功能寄存器必须用直接寻址方式;访问片外数据存储器只能用寄存器间接寻址方式。 15.访问片外数据存储器的间址寄存器可以是R0、R1或DPTR,但使用R0、R1时,寻指范围是00H~0FFH(256B);而使用DPTR寻指范围是0000H~0FFFFH(64KB)。

16.80C51单片机的压栈指令的作用是将数据存入堆栈中。其执行过程是先将堆栈指针(SP)的内容加1,然后将直接寻址单元中的数据送到堆栈指针(SP)所指的单元中。

17. 单片机系统复位后,堆栈指针(SP)= 07H,也就是说,单片机内部RAM的08H~7FH 都可以作为堆栈使用。但通常,我们把堆栈区设置的要高一些(如:60H以上),其它的RAM区,作为数据存储器使用。 18.指令系统中有两条查表指令,可以查找程序存储器中的固定数据或“表格”,其寻址方式都是基址寄存器加变址寄存器间接寻址方式。其中基址寄存器分别是PC或DPTR,变址寄存器是累加器A。 MOVC A,@A+PC MOVC A,@A+DPTR 19.80C51单片机的中断源分别为:两个外部输入中断源、两个片内定时/计数器的溢出中断源和一个片内串行口中断源。五个中断源的顺序和入口地址分别是: ① 外部中断0的入口地址是03H; ② 定时器/计数器0中断的入口地址是0BH; ③ 外部中断1的入口地址是13H; ④ 定时器/计数器1中断的入口地址是1BH; ⑤ 串行口中断的入口地址是23H;

20. 若CPU允许响应中断,CPU必须在现行的指令执行完后,把断点处的PC值(即下一条应该执行的指令地址)推入堆栈保护起来,这一步是硬件自动完成的。 编写中断子程序时,子程序的末尾要由“RETI”指令结束,以便清除相应的中断标志位。如果采用“RET”指令结束中断程序,则不能清除相应的中断标志位,有可能使系统再次进入相应的中断程序。

21.中断优先级处理的原则是:当两个或者两个以上的中断源同时提出中断请求时,计算机首