proteus8位加法器电路设计

- 格式:docx

- 大小:11.69 KB

- 文档页数:3

![[高等教育]实验三 用原理图输入法设计8位全加器](https://uimg.taocdn.com/642a8f09f8c75fbfc67db21b.webp)

实验三用原理图输入法设计8位全加器1、实验目的:学习利用原理图输入法设计简单组合电路,掌握层次化设计的方法,掌握用原理图进行设计的整体流程。

2、实验内容:一个8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin相接。

利用QuartusII完成1位全加器文本编辑输入设计,并以此为依据,再利用原理图输入法设计8位全加器,得出仿真输出波形,并进行硬件引脚锁定,在实验系统上进行硬件测试,验证其硬件实现功能。

3、主要仪器设备:EDA实验箱、QuartusII软件和计算机。

4、实验内容及过程:在E:/EDA/下建立一个新的文件夹为ADDER8。

本设计的思路是先设计1个1位半加器,因此建立新建文件夹E:/EDA/ ADDER8/h_adder;要利用1位的半加器构造1位的全加器,因此建立新建文件夹E:/EDA/ ADDER8/f_adder;要利用1位的全加器构造8位的全加器,因此建立新建文件夹E:/EDA/ ADDER8/adder8;(1)、用原理图输入法构造1位半加器打开QuartusII软件,选择新建一个原理图文件,进入原理图编辑窗。

在空白编辑窗的地方电击鼠标右键,选择加入模块。

此图电击OK,为加入输入引脚。

以同样的方法加入其它模块,如下图所示。

对其连线。

连线时注意,若信号为1位,则用导线进行连接,若信号为多位,则用总线进行连接。

注意连线时,最后连好的线平滑,无x等标识方能表明线正确连接。

连好后更改输入输出引脚。

保存到E:/EDA/ ADDER8/h_adder路径下,文件名为h_adder。

建立相应的工程文件,并编译。

编译成功后转换为原理图模块。

(2)、用原理图输入法构造1位全加器把1位半加器的模块和原理图拷入文件夹E:/EDA/ ADDER8/f_adder。

用两个1位半加器构造1位全加器,以同样的步骤和方式建立1位全加器的原理图,如下图所示。

VHDL与集成电路设计实验报告实验二:在QuartusII中用原理图输入法设计8位全加器姓名院系学号任课教师指导教师评阅教师实验地点实验四号楼611室实验时间2012 年11月实验目的:熟悉QuartusⅡ的VHDL文本设计过程,学习简单时序电路的设计、仿真和测试实验原理:一个8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin相接。

而一个1位全加器可以按照6.1节的方法来完成实验内容:实验内容1:按照6.1节介绍的方法与流程,完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设置成一个硬件符号入库。

键1、键2、键3(PIO0/1/2)分别接ain、bin、cin;发光管D2、D1(PIO9/8)分别接sum 和cout实验内容2:实验内容2,建立一个更高层次的原理图设计,利用以上获得的1位全加器构成8位全加器,并完成编译、综合、适配、仿真和硬件测试。

建议选择电路模式1(附录图3);键2、键1输入8位加数;键4、键3输入8位被加数;数码6/5显示加和;D8显示进位cout实验过程:1、先建立工程,再建立第一个半加器.bdf文件,进行元件逻辑器件选择,放置好端口器件,连接好线,改好名字2、进行编译综合。

3、再在半加器的基础上建立全加器。

注意半加器要进行包装成一个元件。

4、再在全加器的基础上建立起8位全加器。

同样要把全加器进行包装。

5、仿真分析:建立一个.vwf文件,设定好各个输入端口频率,进行仿真分析。

6、硬件测试:引脚锁定,综合,接实验箱的线,打开电源,如果没有驱动,进行驱动选择。

点击下载按钮,进行下载测试。

5、测试过程及结果:引脚锁定4个按键,按前两个按键,前两位的数码管的前两个数码管显示两个数,还有另外两个数码管6/5显示和,按另外两个键,后两位的数码管显示当前的数,结果那6/5两个数码管显示这两个数加起来的和。

原理图输入设计8位全加器一、实验目的掌握运用MAX+plusII原理图编辑器进行层次电路系统设计的方法。

进一步熟悉利用MAX+plusII进行电路系统设计的一般流程。

掌握8位全加器原理图输入设计的基本方法及过程。

二、实验原理一个8位全加器可以由8个1位全加器构成,加法器间的进位可以以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相连接。

而一个1位全加器则可由实验一包装元件入库得到。

实验步骤1、为本项设计建立文件夹2、输入设计项目和存盘根据8位全加器原理图输入设计8位全加器。

并另存(Save As)在为本设计建立的文件夹中。

3、将设计项目设置成工程文件将8位全加器设置为工程文件。

4、选择目标器件并编译首先在Assign选项的下拉菜单中选择器件选择项Device,此窗口的Device Family是器件序列栏,应该首先在此拦中选定目标器件对应的序列名,为了选择EPF1K30TC144-3器件,应将此栏下方标有Show only Fastest Speed Grades的勾消去,以便显示出所有速度级别的器件。

完成器件选择后,按OK键。

最后启动编译器,首先选择左上角的MAX+plusII选项,在其下拉菜单中选择编译器项Compiler。

(此编译器的功能包括网表文件提取、设计文件排错、逻辑综合、逻辑分配、适配(结构综合)、时序仿真文件提取和编程下载文件装配等。

)点击Start,开始编译!如果发现有错,排除错误后再次编译。

5、时序仿真接下来应该测试设计项目的正确性,即逻辑仿真,具体步骤如下:(1)建立波形文件。

(2)输入信号节点。

(3)设置波形参量。

(4)设定仿真时间宽度。

(5)加上输入信号。

(6)波形文件存盘。

(7)运行仿真器。

选择MAX+plusII项及其中的仿真器Simulator选项,点击跳出的仿真器窗口中的Start键。

(注意,刚进入窗口时,应该将最下方的滑标拖向最左侧,以便可观察到初始波形)。

Q u a r t u s_I I设计八位加法器(总19页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--摘要关键词: 8位加法器;EDA(电子设计自动化);QuartusⅡ(可编程逻辑软件)目录第1章概述..................................................................................................... 错误!未定义书签。

EDA的概念 ...................................................................................................... 错误!未定义书签。

硬件描述语言概述........................................................................................ 错误!未定义书签。

第2章QUARTUS II ...................................................................................... 错误!未定义书签。

QUARTUSII概述............................................................................................. 错误!未定义书签。

QUARTUSII建立工程项目......................................................................... 错误!未定义书签。

QUARTUSII建立原理图输入文件 .......................................................... 错误!未定义书签。

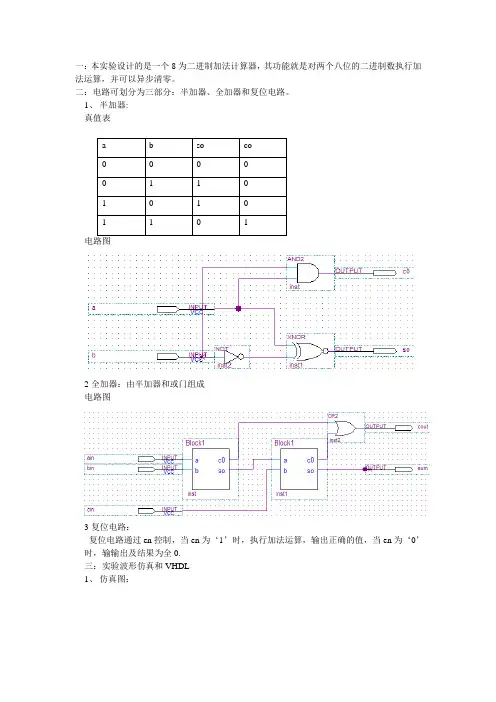

一:本实验设计的是一个8为二进制加法计算器,其功能就是对两个八位的二进制数执行加法运算,并可以异步清零。

二:电路可划分为三部分:半加器、全加器和复位电路。

1、半加器:真值表a b so co0 0 0 00 1 1 01 0 1 01 1 0 1电路图2全加器:由半加器和或门组成电路图3复位电路:复位电路通过en控制,当en为‘1’时,执行加法运算,输出正确的值,当en为‘0’时,输输出及结果为全0.三:实验波形仿真和VHDL1、仿真图:2、VHDL代码1)半加器h_adder:library ieee;use ieee.std_logic_1164.all;entity h_adder isport (a,b :in std_logic;co,so :out std_logic);end entity h_adder;architecture fh1 of h_adder isbeginso <= not(a xor (not b));co <= a and b ; end architecture fh1;2)或门or2a:library ieee;use ieee.std_logic_1164.all;entity or2a isport (a,b :in std_logic;c: out std_logic);end entity or2a;architecture one of or2a isbeginc <= a or b ;end architecture one;3)全加器f_adder:library ieee;use ieee.std_logic_1164.all;entity f_adder isport (ain,bin,cin:in std_logic;cout,sum:out std_logic);end entity f_adder;architecture fd1 of f_adder iscomponent h_adderport (a,b :in std_logic;co,so :out std_logic);end component;component or2aport (a,b :in std_logic;c: out std_logic);end component;signal d,e,f: std_logic;beginu1:h_adder port map(a=>ain,b=>bin,co=>d,so=>e);u2:h_adder port map(a=>e,b=>cin,co=>f,so=>sum);u3: or2a port map(a=>d,b=>f,c=>cout);end architecture fd1;4)与门and2a:library ieee;use ieee.std_logic_1164.all;entity and2a isport (a,b :in std_logic;c: out std_logic);end entity and2a;architecture one of and2a isbeginc <= a and b ;end architecture one;5)顶层设计文件library ieee;use ieee.std_logic_1164.all;entity zong isport (a1,a2,a3,a4,a5,a6,a7,a8,b1,b2,b3,b4,b5,b6,b7,b8,en :in std_logic;solution1,solution2,solution3,solution4,solution5,solution6,solution7,solution8,solution9 :out std_logic );end entity zong;architecture fh1 of zong iscomponent h_adderport (a,b :in std_logic;co,so :out std_logic);end component;component f_adderport (ain,bin,cin:in std_logic;cout,sum:out std_logic);end component;component and2aport (a,b :in std_logic;c: out std_logic);end component;signale2,e3,e4,e5,e6,e7,e8,e9,e10,e11,e12,e13,e14,e15,e16,e17,e18,e19,e20,e21,e22,e23,e24 :std_logi c;beginu1:and2a port map(a=>en,b=>a1,c=>e2);u2:and2a port map(a=>en,b=>a2,c=>e3);u3:and2a port map(a=>en,b=>a3,c=>e4);u4:and2a port map(a=>en,b=>a4,c=>e5);u5:and2a port map(a=>en,b=>a5,c=>e6);u6:and2a port map(a=>en,b=>a6,c=>e7);u7:and2a port map(a=>en,b=>a7,c=>e8);u8:and2a port map(a=>en,b=>a8,c=>e9);u9:and2a port map(a=>en,b=>b1,c=>e10);u10:and2a port map(a=>en,b=>b2,c=>e11);u11:and2a port map(a=>en,b=>b3,c=>e12);u12:and2a port map(a=>en,b=>b4,c=>e13);u13:and2a port map(a=>en,b=>b5,c=>e14);u14:and2a port map(a=>en,b=>b6,c=>e15);u15:and2a port map(a=>en,b=>b7,c=>e16);u16:and2a port map(a=>en,b=>b8,c=>e17);u17:h_adder port map(a=>e2,b=>e10,co=>e18,so=>solution1);u18:f_adder port map(ain=>e3,bin=>e11,cin=>e18,cout=>e19,sum=>solution2);u19:f_adder port map(ain=>e4,bin=>e12,cin=>e19,cout=>e20,sum=>solution3);u20:f_adder port map(ain=>e5,bin=>e13,cin=>e20,cout=>e21,sum=>solution4);u21:f_adder port map(ain=>e6,bin=>e14,cin=>e21,cout=>e22,sum=>solution5);u22:f_adder port map(ain=>e7,bin=>e15,cin=>e22,cout=>e23,sum=>solution6);u23:f_adder port map(ain=>e8,bin=>e16,cin=>e23,cout=>e24,sum=>solution7);u24:f_adder port map(ain=>e9,bin=>e17,cin=>e24,cout=>solution9,sum=>solution8);end architecture fh1;。

EDA 技术》实验报告实验名称:8 位二进制全加器设计姓名:班级:学号:实验日期:2010-3-29指导教师:、实验设计要求以一位二进制全加器为基本元件,用例化语句写出8位并行二进制全加器的顶层文件,并讨论此加法器的电路特性。

、设计原理电路功能描述定义了8位二进制全加器顶层设计元件端口信号,输入端口:AIN, BIN, 是八个二进制数,数据类型被定义为STD_LOGIC_VECTOR。

CIN是输入的进位,数据类型IN STD_LOGIC ;输出端口:SUM为和,数据类型IN STD_LOGIC COUT 为输出的进位。

三、实验程序程序:一位二进制全加器设计顶层描述功能:程序功能简介程序: 位并行二进制全加器顶层文件功能:程序功能简介四、编译及仿真结果 选用器件型号cyclone编译后使用器件资源情况、引脚配置情况(硬件实验) Flev Si^t-uE^@x sful — M on 12 29 21:22:33 2010 II Version5.1 Build ne 10/26/2005 SJ Full Version Revi si on. Ifame h aiderT 四一Ent i ty IhmtF .ADDERSF wnilyCycl on! Devi eeEP1C6G240C6 Tinni ns ModelsFiMl timing requiremerLisZ Tiotal logic elefTkents16 / 5,900 ( < 1怕) T^tal pins26/185 C 14 $ \ Total virtual pinsaTotil wy bitia f 92,100 ( 0 % ) Total PLLs 0 / 2〔 D % ) 仿真结果显示:该 设计是成功的。

输入的进位也要加上去。

0---255 全加器的COUNT 没有进位,而当加至U 256,COUNT=1SUM 输出0. 五、总结.1编译不通过,检查后发现在建立工程时,同一工程的所有文件都必须放在同 一文件夹中,而这一步没做。

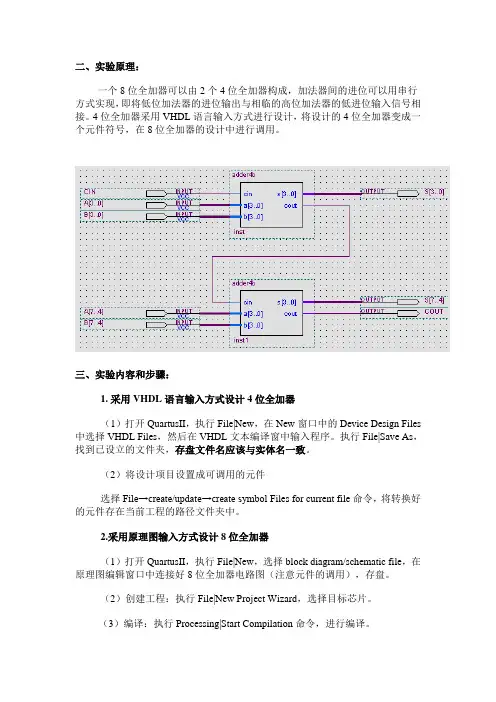

二、实验原理:一个8位全加器可以由2个4位全加器构成,加法器间的进位可以用串行方式实现,即将低位加法器的进位输出与相临的高位加法器的低进位输入信号相接。

4位全加器采用VHDL语言输入方式进行设计,将设计的4位全加器变成一个元件符号,在8位全加器的设计中进行调用。

三、实验内容和步骤:1. 采用VHDL语言输入方式设计4位全加器(1)打开QuartusII,执行File|New,在New窗口中的Device Design Files 中选择VHDL Files,然后在VHDL文本编译窗中输入程序。

执行File|Save As,找到已设立的文件夹,存盘文件名应该与实体名一致。

(2)将设计项目设置成可调用的元件选择File→create/update→create symbol Files for current file命令,将转换好的元件存在当前工程的路径文件夹中。

2.采用原理图输入方式设计8位全加器(1)打开QuartusII,执行File|New,选择block diagram/schematic file,在原理图编辑窗口中连接好8位全加器电路图(注意元件的调用),存盘。

(2)创建工程:执行File|New Project Wizard,选择目标芯片。

(3)编译:执行Processing|Start Compilation命令,进行编译。

(4)引脚锁定:在菜单Assignments中选Assignments Editor按钮,先单击右上方的Pin,再双击下方最左栏的“New”选项,弹出信号名栏,锁定所有引脚,进行编译,存盘。

选择编程模式1,键2、键1输入8位加数,键4、键3输入8位被加数,键8输入进位cin,数码管6/5显示和,D8显示进位cout。

5. 编程下载及验证:执行Tool|Programmer命令,选择program/config;执行start,进行验证,记录结果。

4位全加器的参考源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY adder4b ISPORT(cin:IN STD_LOGIC;a,b:IN STD_LOGIC_VECTOR(3 DOWNTO 0);s:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);cout:OUT STD_LOGIC);END ENTITY adder4b;ARCHITECTURE art OF adder4b ISSIGNAL sint,aa,bb:STD_LOGIC_VECTOR(4 DOWNTO 0);BEGINaa<='0'&a;bb<='0'&b;sint<=aa+bb+cin;s<=sint(3 downto 0);cout<=sint(4);END art;触发器功能的模拟实现三、实验内容:基本RS触发器、同步RS触发器、集成JK触发器和D触发器同时集成在一个芯片上,实现的原理图如下:输入信号Sd、Rd对应的管脚接按键开关,CLK1、CLK2接时钟源(频率<5Hz);J,K,D,R,S对应的管脚分别接拨码开关;输出信号QRS,NQRS,QRSC,NQRSC,QJK,NQJK,QD,NQD对应管脚分别接LED灯。

硬件技术课程设计课题名称 8位全加器的设计与实现组名组员班级1201专业计算机科学与技术指导教师计算机学院2014年12 月目录一、设计目的 (1)二、设计内容 (1)三、实验原理图 (1)半加器原理图 (1)1位全加器原理图 (1)4位全加器原理图 (2)8位全加器原理图 (2)锁引脚图 (3)四、设计与说明 (3)五、时序仿真 (4)六、实验步骤 (5)七、设计总结 (8)八、参考文献 (8)8位全加器的设计与实现一、设计目的1、掌握运用MAX+plusII原理图编辑器进行层次电路系统设计的方法。

2、进一步熟悉利用MAX+plusII进行电路系统设计的一般流程。

3、掌握8位全加器原理图输入设计的基本方法及过程。

二、设计内容一个8位全加器可以由8个1位全加器构成,加法器间的进位可以以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相连接。

而一个1位全加器则可由实验一包装元件入库得到。

三、实验原理图半加器原理图:1位全加器原理图:1 /84位全加器原理图:8位全加器原理图:2 / 8锁引脚原理图:四、设计与说明8位全加器可由2个4位的全加器串联组成,因此,先由一个半加器构成一个全加器,再由4个1位全加器构成一个4位全加器并封装成元器件。

加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin相接最高位的输出即为两数之和。

最后一个Cout输出进位,D8显示。

3 / 8五、时序仿真1、建立波形文件。

为此设计建立一个波形测试文件。

选择File项及其New,再选择右侧New窗中的vector Waveform file项,打开波形编辑窗。

2、输入信号节点。

在波形编辑窗的左方双击鼠标,在出现的窗口中选择Node finder,在弹出的窗口中首先点击List键,这时左窗口将列出该项设计所以利用中间的“=>”键将需要观察的信号选到右栏中。

基于原理图的8位全加器设计实验目的:熟悉利用Quartus II的原理图输入方法设计简单的组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。

实验原理:一个8位全加器可以由8个1位全加器串行构成,即将低位加法器的进位输出cout与相临的高位加法器的最低位输入信号cin相接。

试验任务:1.完成半加器和全加器的设计。

2.建立一个更高层次的原理图设计,利用以上获得的1位全加器构成8位全加器,完成编译、综合、适配、仿真和硬件测试。

实验步骤:一、1位全加器设计1.建立工程文件夹adder,路径d:\adder。

2.输入设计项目和存盘原理图编辑输入流程如下:(1)打开Quartus II,选择file—>new命令,在弹出的窗口中选择block diagram/schematic file 选项,单击ok按钮后将打开原理图编辑窗口。

(2)在编辑窗口中的任何一个位置上右击,将弹出快捷菜单,选择inset—>symbol命令,将弹出元件输入对话框。

(3)单击“…”按钮,找到基本元件库路径d:/altera/90/quartus/libraries/primitives/logic项(假设软件安装在D盘),选中需要的元件,单击“打开”按钮,此元件即显示在窗口中,然后单击symbol窗口中的ok按钮,即可将元件调入原理图编辑窗口中。

也可以在name栏输入需要的元件名。

调入好元件和引脚后,连接好电路,再输入各引脚名。

(4)选择file—>save as命令,选择刚才为自己的工程建立的目录d:\adder,将已设计好的原理图取名为h_adder.bdf,并存盘此文件夹内。

3.将设计好的项目设置成可调用的元件为了构成全加器的顶层设计,必须将以上设计的半加器h_adder.bdf设置成可调用的元件。

在打开半加器原理图文件的情况下,选择file—>create/update—>create symbol file for current file命令,即可将当前文件h_adder.bdf变成一个元件符号存盘,以待高层次设计中调用。

原题目:实现一个8位全加器电路。

实现一个8位全加器电路介绍本文档旨在说明如何实现一个8位全加器电路。

全加器电路是一种用于对两个二进制数进行加法运算的电路。

原理全加器电路由三个输入和两个输出组成。

输入包括两个二进制数位和一个进位位,输出为一个和位和一个进位位。

全加器电路的逻辑如下:- 和位的输出等于输入位和进位位的异或结果- 进位位的输出等于输入位和进位位的与运算结果以及输入位间的或运算结果实现要实现一个8位全加器电路,需要按照以下步骤进行:1. 首先,确定所需的器件和元件。

一个全加器电路通常由逻辑门和触发器构成。

逻辑门可以使用与门、或门、异或门等。

触发器可以使用D触发器、JK触发器等。

2. 根据所需的功能和规格,选择适合的逻辑门和触发器。

3. 依照全加器电路的原理,设计电路图。

将逻辑门和触发器按照一定的连接方式进行连接,满足和位和进位位的运算要求。

4. 制作电路板并连接电路。

根据设计的电路图,将所选的逻辑门和触发器按照正确的接线方式进行连接。

5. 进行电路测试。

使用适当的输入信号(两个二进制数位和一个进位位),检查和位和进位位的输出是否符合预期的结果。

6. 优化电路。

根据测试结果,如果电路效果不好或未能达到预期的输出结果,可以尝试优化电路的设计,调整逻辑门和触发器等元件的选择,重新布线等。

7. 验证电路的正确性。

通过多次测试,确保电路能够稳定地进行加法运算,输出正确的和位和进位位。

结论通过以上步骤,我们可以成功实现一个8位全加器电路。

全加器电路在计算机系统中扮演重要的角色,用于进行二进制数的加法运算。

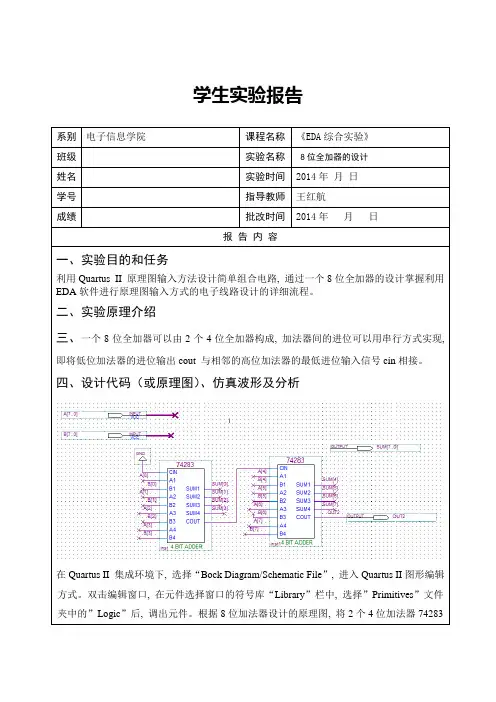

学生实验报告系别电子信息学院课程名称《EDA综合实验》班级实验名称8位全加器的设计姓名实验时间2014年月日学号指导教师王红航成绩批改时间2014年月日报告内容一、实验目的和任务利用Quartus II 原理图输入方法设计简单组合电路, 通过一个8位全加器的设计掌握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。

二、实验原理介绍三、一个8位全加器可以由2个4位全加器构成, 加法器间的进位可以用串行方式实现, 即将低位加法器的进位输出cout 与相邻的高位加法器的最低进位输入信号cin相接。

四、设计代码(或原理图)、仿真波形及分析在Quartus II 集成环境下, 选择“Bock Diagram/Schematic File”, 进入Quartus II图形编辑方式。

双击编辑窗口, 在元件选择窗口的符号库“Library”栏中, 选择”Primitives”文件夹中的”Logic”后, 调出元件。

根据8位加法器设计的原理图, 将2个4位加法器74283及输入、输出元件符号调入, 完成电路内部的连接及输入、输出元件的连接, 并将相应的输入、输出元件符号名分别更改为A[7..0]、B[7..0]、SUM[7...0]和OUT2。

再将当前设计设定为工程, 目标芯片类型为ACEX1K;型号为EP1K30TC144-3。

编译设计文件, 选择“Start Compilation”对文件进行编译。

然后进行逻辑仿真设计, 先建立波形文件, 然后输入信号节点, 设置波形参量, 编辑输入信号, 保存文件。

时序仿真图功能仿真图由图片可以看出, 当8位全加器的输入端口A输入为60时, B端口输入为160时, 输出SUM 为220, 进位OUT2为0;当输入端口A输入为60时, B输入为200时, SUM为4, 进位OUT2为1.当8位全加器的输入端口A输入为80时, B端口输入为200时, 输出SUM为24, 进位OUT2为1;当输入端口A输入为80时, B输入为160时, SUM为240, 进位OUT2为0.证明设计是正确的。

计算机组成原理实现八位串行加法器下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!实现八位串行加法器的计算机组成原理介绍在计算机组成原理中,串行加法器是一种重要的数字电路,用于在计算机中执行加法操作。

实验二 8位全加器的设计与实现[实验目的]1 掌握Quartus II 环境下原理图输入、编译综合、仿真、引脚锁定、下载及硬件测试测试方法;2 掌握Quartus II 对FPGA 的设计方法。

3 学习8位全加器原理图的设计,掌握Quartus II 原理图层次化设计方法。

[实验仪器]Pentium PC 机 、EDA 实验箱 各一台 Quartus II 6.0软件 [实验内容]采用Quartus II 原理图输入方式及层次化设计方法设计8位全加器并进行器件编程、检测。

1. 完成全加器的设计(包括原理图输入、编译综合、适配、仿真并将它们设置成硬件符号入库)。

2. 建立顶层原理图文件。

采用已产生的全加器元件设计一个8位串行全加器电路,并完成编译综合、适配、仿真和硬件测试。

一、一位全加器每个全加器有三位输入,分别是加数A,B 和一个进位位CI 。

将这三个数相加,得出全加和数D 和进位数CO 。

这个过程称为”全加”,全加器的真值表参见表1。

全加器的真值表1 A B CI CO D0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 11由表2得: ABCI CI AB CI B A BCI A CO +++= D ABCI ABCI ABCI ABCI =+++ 可用两个四选一芯片完成。

原理图如下:ABCI100011110111cout D0D1D2D31ABCI100011110111S D0D1D2D31可得:Cout 的连接方式如下: D0=0;D1=CI=D2;D3=1 S 的连接方式如下: D0=CI;D1=CI =D2;D3=CI选用两片4选1,可绘制全加器如图1所示。

VCCciINPUT VCC A INPUT VCCBINPUT SOUTPUTCOUTOUTPUT S0D2S1D3D0INH D1QMUX41inst9NOTinst10S0D2S1D3D0INH D1Q MUX41instGNDVCC图1一位全加器1. 为全加器项目工程设计建立文件夹Windows 环境下在D :盘建立8位加法器设计项目的文件夹,取名为adder8, 路径为d :\adder8。

实验二八位加法器的设计一、实验目的1、掌握QUARTUSII设计工具进行电子设计的基本流程。

2、了解可编程器件设计的全过程。

二、实验内容设计并调试一个由两个4位二进制并行加法器级联而成的8位二进制加法器,并进行硬件验证。

三、实验条件QUARTUSII软件,GW48试验箱,计算机。

四、实验设计(1)系统的原理框图(2)VHDL源程序--四位加法器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;use ieee.std_logic_arith.all;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADD4 ISPORT(C4: IN STD_LOGIC;A4: IN STD_LOGIC_VECTOR(3 DOWNTO 0);B4: IN STD_LOGIC_VECTOR(3 DOWNTO 0);S4: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO4: OUT STD_LOGIC);END ENTITY ADD4;ARCHITECTURE ART OF ADD4 ISSIGNAL S5: STD_LOGIC_VECTOR(4 DOWNTO 0);SIGNAL A5,B5: STD_LOGIC_VECTOR(4 DOWNTO 0);BEGINA5<='0'&A4;B5<='0'&B4;S5<=A5+B5+C4;S4<=S5(3 DOWNTO 0);CO4<=S5(4);END ARCHITECTURE ART;--顶层文件LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADD8 ISPORT(C8: IN STD_LOGIC;A8: IN STD_LOGIC_VECTOR(7 DOWNTO 0);B8: IN STD_LOGIC_VECTOR(7 DOWNTO 0);S8: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);CO8: OUT STD_LOGIC);END ENTITY ADD8;ARCHITECTURE ART1 OF ADD8 ISCOMPONENT ADD4 ISPORT(C4: IN STD_LOGIC;A4: IN STD_LOGIC_VECTOR(3 DOWNTO 0);B4: IN STD_LOGIC_VECTOR(3 DOWNTO 0);S4: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO4: OUT STD_LOGIC);END COMPONENT;SIGNAL S1,S3,AH4,BH4,AL4,BL4 :STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL S2:STD_LOGIC;BEGINAL4<=A8(3 DOWNTO 0);BL4<=B8(3 DOWNTO 0);AH4<=A8(7 DOWNTO 4);BH4<=B8(7 DOWNTO 4);U1:ADD4 PORT MAP(C8,AL4,BL4,S1,S2);U2:ADD4 PORT MAP(S2,AH4,BH4,S3,CO8);S8<=S3&S1;END ARCHITECTURE ART1;(3)管脚锁定实验设备:CW48系统;试验芯片:EP1C6/12Q240;试验模式:NO.1;五、实验结果及总结(1)系统仿真情况(2)硬件验证情况A8 19 19 CC CC B8 2C 2C F1 F1 C8 0 1 0 1S8 45 46 BD BECO8 0 0 1 1。

计算机科学与技术学院计算机组成原理实验报告书实验名称八位补码加/减法器的设计与实现班级学号姓名指导教师日期成绩实验1八位补码加/减法器的设计与实现一、实验目的1.掌握算术逻辑运算单元(ALU)的工作原理。

2.熟悉简单运算器的数据传送通路。

3.掌握8位补码加/减法运算器的设计方法。

4.掌握运算器电路的仿真测试方法二、实验任务1.设计一个8位补码加/减法运算器(1)参考图1,在QUARTUS II里输入原理图,设计一个8位补码加/减法运算器。

(2)创建波形文件,对该8位补码加/减法运算器进行功能仿真测试。

(3)测试通过后,封装成一个芯片。

2.设计8位运算器通路电路参考下图,利用实验任务1设计的8位补码加/减法运算器芯片建立运算器通路。

3.利用仿真波形,测试数据通路的正确性。

设定各控制信号的状态,完成下列操作,要求记录各控制信号的值及时序关系。

(1)在输入数据IN7~IN0上输入数据后,开启输入缓冲三态门,检查总线BUS7~BUS0上的值与IN0~IN7端输入的数据是否一致。

(2)给DR1存入55H,检查数据是否存入,请说明检查方法。

(3)给DR2存入AAH,检查数据是否存入,请说明检查方法。

(4)完成加法运算,求55H+AAH,检查运算结果是否正确,请说明检查方法。

(5)完成减法运算,分别求55H-AAH和AAH-55H,检查运算结果是否正确,请说明检查方法。

(6)求12H+34H-56H,将结果存入寄存器R0,检查运算结果是否正确,同时检查数据是否存入,请说明检查方法。

三、实验要求(1)做好实验预习,掌握运算器的数据传送通路和ALU的功能特性。

(2)实验完毕,写出实验报告,内容如下:①实验目的。

②实验电路图。

③按实验任务3的要求,填写下表,以记录各控制信号的值及时序关系。

表中的序号表示各控制信号之间的时序关系。

要求一个控制任务填一张表,并可用文字对有关内容进行说明。

⑤实验体会与小结。

四、实验预习内容1.实验电路设计原理及思路说明本实验利用基本逻辑门电路设计一位全加器(FA),如表1:表1-一位全加器(FA)电路的输入输出信号说明然后以此基础上实现八位补码加/减法器的设计,考虑到实现所需既可以实现加法又可以实现减法,所以使用了一个M输入来进行方式控制加减。

8位加减发器设计前两天刚帮朋位友做了一个数字电路里的8位加减发器,感触颇深啊!一个简单的8位加减发器都做了好久,而且……•简单说一下题目:熟悉计算机的加、减法运算的原理和硬件电路的实现,掌握带符号加减法的溢出方法判断和硬件电路的实现方法。

1、输入数据为原码,其中高1位为符号位,低7位为数据位,运算结果需要转换为原码表示。

2、具有进位信号输入,输出能力,溢出判断能力。

3、通过功能选择控制信号M选择运算功能,M =0,加法运算,M=1,进行减法运算。

4、用数码管显示两个输入数据和运算结果。

用发光二极管显示溢出与否,绿灯表示未溢出,红灯表示溢出。

•要求1、在multisim上进行电路设计及仿真2、输入、输出数码显示正确,另外溢出指示正确3、结果验证,选择四组数据依次验证:结果为正不溢出、结果为负不溢出、结果正溢出和结果负溢出四种情况个人感觉刚读完题有点懵,没听过这位老的讲的课谁能看懂什么意思……每个人看到这个题的第一反应应该是分类,加法有几种情况,减法有几种情况,但是这种情况你就陷入了误区,这时候你应该问一下小伙伴学的课本,大概那个章节,重新学习一下(反正我是栽了跟头以后,要了他们的课本,看了几个例题就知道他们老师想干什么了):.这是好几天以前写的了,忘了思路了,下面把小伙伴的报告直接贴上摘要采用一款优秀的软件Multisim13作为设计平台,,对任意一个8位二进制并行加/减法运算电路的设计原理及构成方法作了详细的介绍,通过按键输入被减数和减数,并设置+、-号按键;允许减数大于被减数,负号可采用数码管或其他显示器件,并利用LED灯显示计算结果。

提出至少两种设计实现方案,并优选方案进行设计。

利用该软件能实现电子电路的快速设计和仿真,大大缩短了电子电路的设计开发周期。

本文以任意一个8位二进制并行加/减法运算电路的设计为例,详细介绍了基于Multisim13的数字电路加减法运算的设计与仿真。

【关键词】Multisiml3,寄存器,显示器,门元件,数字电路第1章概述1.1 课题分析目前人类社会已逐步实现了高度发达的信息化,各种电子产品不但在性能上不断增强,而且更新换代的频率也越来越快,实现这种进步的主要原因是生产制造技术和电子设计技术的发展,特别是以EDA为核心的电子设计技术得到了飞速发展。

proteus8位加法器电路设计

一、引言

随着计算机科学和电子工程的快速发展,设计和实现高性能的加法器电路对于数字系统的工程师来说变得越来越重要。

加法器电路是计算机中最基本的数字电路之一,其功能是实现数字的加法运算。

在本文中,我们将探讨关于proteus8位加法器电路设计的内容。

首先,我们将介

绍与加法器电路设计相关的基本概念。

然后,我们将学习如何使用Proteus软件进行电路设计和仿真。

最后,我们将展示一个完整的8位加法器电路设计示例。

二、基本概念

2.1 加法器电路的基本原理

加法器电路是用于执行数字加法运算的电路。

它由一组逻辑门和触发器构成,能够对两个输入数字进行加法运算,并输出运算结果。

常见的加法器电路有半加器、全加器和并行加法器等。

2.2 8位加法器电路的设计要求

在设计一个8位加法器电路时,我们需要考虑以下要求:

1.能够同时处理8位二进制数的加法运算;

2.采用并行加法器的设计方法,以提高运算效率;

3.能够正确处理进位并输出最终的运算结果;

4.使用适当的逻辑门和触发器实现加法器功能;

5.能够进行仿真和测试,确保设计的正确性。

三、Proteus软件介绍

Proteus是一款广泛用于电子电路设计和仿真的软件。

它提供了完整的电路设计和

仿真环境,能够帮助工程师快速进行电路设计和验证。

3.1 Proteus的基本功能

Proteus具有以下基本功能:

1.电路设计:通过拖放元件和连接线,可以设计各种类型的电路,包括数字电

路、模拟电路和混合电路等。

2.仿真器:Proteus提供了强大的仿真器,可以对设计的电路进行仿真和验证,

以确保设计的正确性。

3.PCB设计:Proteus还提供了PCB设计的功能,可以将设计的电路转化为实

际的PCB板。

4.系统级仿真:Proteus能够在电路和软件之间建立联系,进行系统级仿真和

调试。

3.2 Proteus的使用步骤

使用Proteus进行电路设计和仿真,通常需要以下步骤:

1.创建新工程:在Proteus中创建一个新的工程,并选择适合的电路类型。

2.添加元件:从Proteus元件库中选择需要的元件,并将其拖放到工程中的画

布上。

3.连接元件:使用连线工具连接元件,以建立电路的连接关系。

4.设置仿真参数:设置仿真参数,如输入信号和仿真时间等。

5.运行仿真:运行仿真器,对设计的电路进行仿真和验证。

6.分析仿真结果:分析仿真结果,确保设计的正确性。

7.PCB设计(可选):如果需要,可以将设计的电路转化为PCB板,并进行

PCB设计。

四、8位加法器电路设计示例

下面是一个完整的8位加法器电路设计示例:

4.1 电路设计思路

我们采用并行加法器的设计方法,即将8位加法器分为8个单独的加法器模块,并行地进行加法运算。

每个加法器模块处理两个输入位和一位来自上一位加法器的进位信号,输出一个加法结果位和一个向下一位加法器的进位信号。

4.2 电路设计步骤

1.创建新工程:在Proteus中创建一个新的工程,并选择适合的电路类型。

2.添加元件:从Proteus元件库中选择需要的元件,包括逻辑门、触发器和连

接线等。

3.连接元件:根据设计思路,使用连线工具连接元件,以建立加法器电路的连

接关系。

4.设置仿真参数:设置输入信号和仿真时间等仿真参数。

5.运行仿真:运行仿真器,对加法器电路进行仿真和验证。

6.分析仿真结果:分析仿真结果,检查加法器电路的运算结果是否正确。

4.3 加法器电路设计结果

经过仿真验证,我们的8位加法器电路能够正确地进行加法运算,并输出正确的结果。

五、结论

本文介绍了关于proteus8位加法器电路设计的内容。

我们先学习了加法器电路的基本概念,然后介绍了Proteus软件的基本功能和使用步骤。

最后,我们展示了一个完整的8位加法器电路设计示例,并验证了设计的正确性。

通过本文的学习,我们可以更好地理解和掌握加法器电路的设计原理和方法,并能够使用Proteus软件进行电路设计和仿真。

希望本文能对读者在电路设计和仿真方面的学习和实践有所帮助。