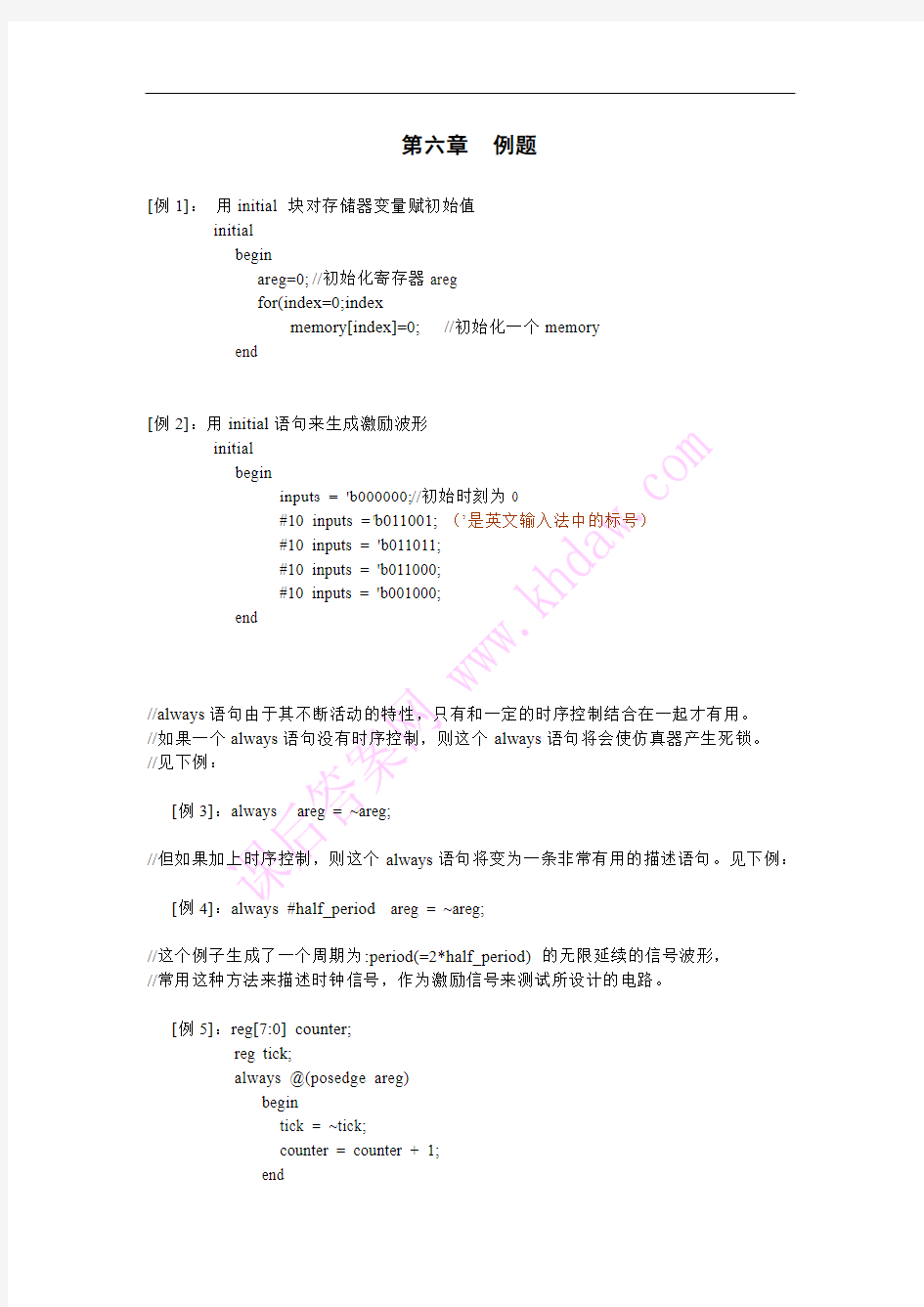

第六章例题

[例1]:用initial 块对存储器变量赋初始值

initial

begin

areg=0; //初始化寄存器areg

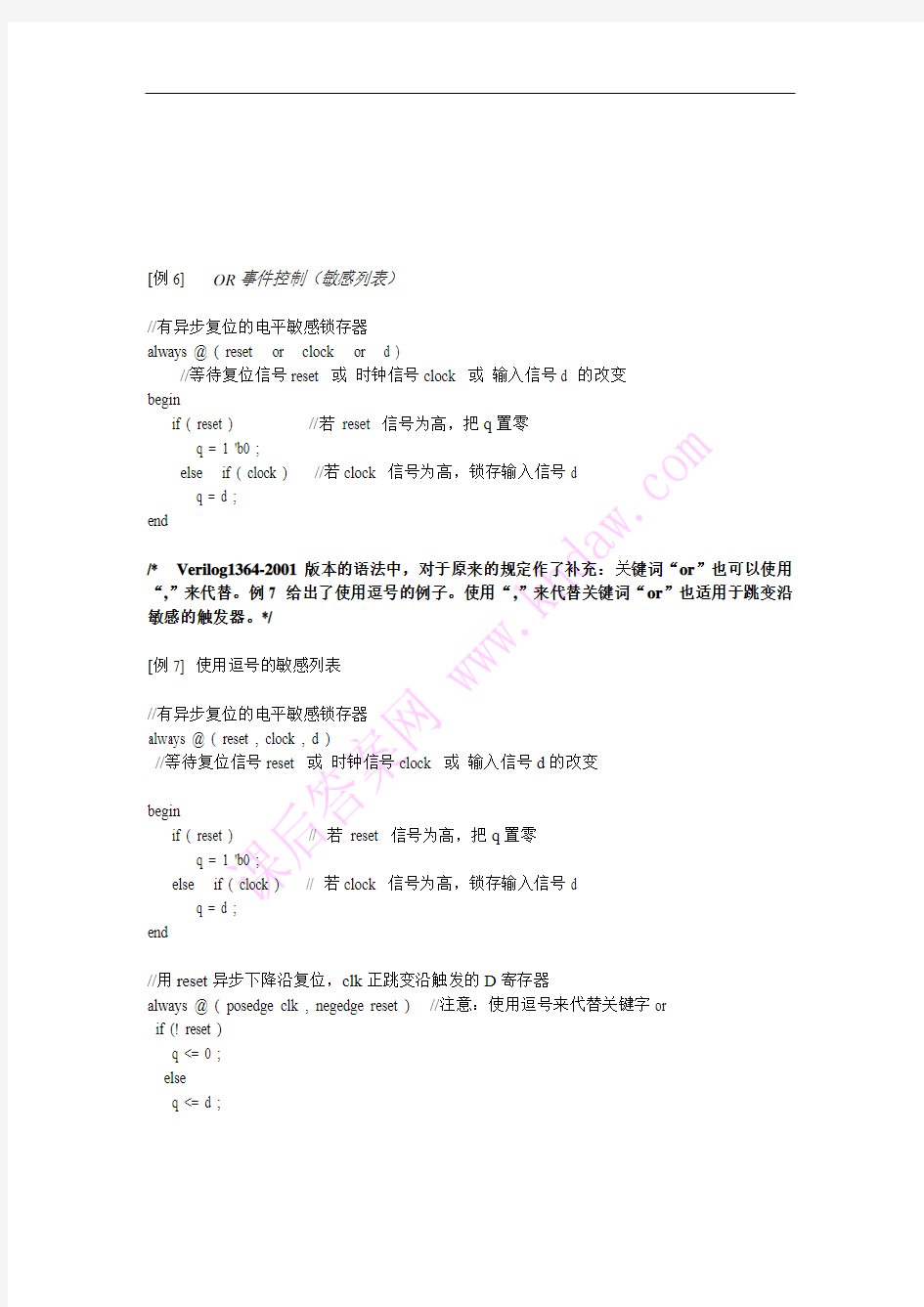

for(index=0;index memory[index]=0; //初始化一个memory end [例2]:用initial语句来生成激励波形 initial begin inputs = 'b000000; //初始时刻为0 #10 inputs = 'b011001; (’是英文输入法中的标号) #10 inputs = 'b011011; #10 inputs = 'b011000; #10 inputs = 'b001000; end //always语句由于其不断活动的特性,只有和一定的时序控制结合在一起才有用。 //如果一个always语句没有时序控制,则这个always语句将会使仿真器产生死锁。 //见下例: [例3]:always areg = ~areg; //但如果加上时序控制,则这个always语句将变为一条非常有用的描述语句。见下例:[例4]:always #half_period areg = ~areg; //这个例子生成了一个周期为:period(=2*half_period) 的无限延续的信号波形, //常用这种方法来描述时钟信号,作为激励信号来测试所设计的电路。 [例5]:reg[7:0] counter; reg tick; always @(posedge areg) begin tick = ~tick; counter = counter + 1; end [例6] OR事件控制(敏感列表) //有异步复位的电平敏感锁存器 always @ ( reset or clock or d ) //等待复位信号reset 或时钟信号clock 或输入信号d 的改变 begin if ( reset ) //若reset 信号为高,把q置零 q = 1 'b0 ; else if ( clock ) //若clock 信号为高,锁存输入信号d q = d ; end /* Verilog1364-2001版本的语法中,对于原来的规定作了补充:关键词“or”也可以使用“,”来代替。例7 给出了使用逗号的例子。使用“,”来代替关键词“or”也适用于跳变沿敏感的触发器。*/ [例7] 使用逗号的敏感列表 //有异步复位的电平敏感锁存器 always @ ( reset , clock , d ) //等待复位信号reset 或时钟信号clock 或输入信号d的改变 begin if ( reset ) // 若reset 信号为高,把q置零 q = 1 'b0 ; else if ( clock ) // 若clock 信号为高,锁存输入信号d q = d ; end //用reset异步下降沿复位,clk正跳变沿触发的D寄存器 always @ ( posedge clk , negedge reset ) //注意:使用逗号来代替关键字or if (! reset ) q <= 0 ; else q <= d ; [例8]@*操作符的使用 //用or 操作符的组合逻辑块 //编写敏感列表很繁琐并且容易漏掉一个输入 always @ ( a or b or c or d or e or f or g or h or p or m ) begin out1 = a ? b + c : d + e ; out2 = f ? g + h : p + m ; end //不用上述方法,用符号@(*)来代替,可以把所有输入变量都自动包括进敏感列表。always @ ( * ) begin out1 = a ? b + c : d + e ; out2 = f ? g + h : p + m ; end always wait (count_enable) #20 count = count + 1; switch_bytes(old_word,new_word); new_word = switch_bytes(old_word); task my_task; input a, b; inout c; output d, e; … <语句> //执行任务工作相应的语句 … c = foo1; //赋初始值 d = foo2; //对任务的输出变量赋值 e = foo3; endtask 任务调用: my_task(v,w,x,y,z); [例9] 描述红绿黄交通灯行为的Verilog模块,其中使用了任务。 module traffic_lights; reg clock, red, amber, green; parameter on=1, off=0, red_tics=350, amber_tics=30,green_tics=200; //交通灯初始化 initial red=off; initial amber=off; initial green=off; //交通灯控制时序 always begin red=on; //开红灯 light(red,red_tics); //调用等待任务 green=on; //开绿灯 light(green,green_tics); //等待 amber=on; //开黄灯 light(amber,amber_tics); //等待 end //定义交通灯开启时间的任务 task light; output color; input[31:0] tics; begin repeat(tics) @(posedge clock);//等待tics个时钟的上升沿color=off;//关灯 end endtask //产生时钟脉冲的always块 always begin #100 clock=0; #100 clock=1; end endmodule //用例子说明: function [7:0] getbyte; input [15:0] address; begin <说明语句> //从地址字中提取低字节的程序 getbyte = result_expression; //把结果赋予函数的返回字节end endfunction word = control? {getbyte(msbyte),getbyte(lsbyte)} : 0; //下面的例子中定义了一个可进行阶乘运算的名为factorial的函数, //该函数返回一个32位的寄存器类型的值,该函数可后向调用自身,//并且打印出部分结果值。 [例10] 阶乘函数的定义和调用。 module tryfact; //函数的定义------------------------------- function[31:0]factorial; input[3:0]operand; reg[3:0]index; begin factorial = 1; // 0的阶乘为1,1的阶乘也为1 for(index=2; index<=operand; index=index+1) factorial = index * factorial; end endfunction //函数的测试------------------------------------- reg[31:0]result; reg[3:0]n; initial begin result=1; for(n=2;n<=9;n=n+1) begin $display("Partial result n= %d result= %d", n, result); result = n * factorial(n)/((n*2)+1); end $display("Finalresult=%d",result); end endmodule // 模块结束 //例11给出了函数calc_parity的定义和调用。 [例11]偶校验位的计算 //定义一个模块,其中包含能计算偶校验位的函数(calc_parity) module parity; reg [31:0] addr; reg parity; initial begin addr = 32'h3456_789a; #10 addr = 32'hc4c6_78ff; #10 addr = 32'hff56_ff9a; #10 addr = 32'h3faa_aaaa; end //每当地址值发生变化,计算新的偶校验位 always @(addr) begin parity = calc_parity(addr); //第一次启动校验位计算函数calc_parity $display("Parity calculated = %b", calc_parity(addr) ); // 第二次启动校验位计算函数calc_parity end //定义偶校验计算函数 function calc_parity; input [31:0] address; begin //适当地设置输出值,使用隐含的内部寄存器calc_parity calc_parity = ^address; //返回所有地址位的异或值 end endfunction endmodule [例12]使用C风格进行变量声明的函数定义 //定义偶校验位计算函数,该函数采用ANSI C 风格的变量声明 function calc_parity (input [31:0] address); begin //适当地设置输出值,使用隐含的内部寄存器calc_parity calc_parity = ^address; //返回所有地址位的异或值 end endfunction [例13]左/右移位寄存器 // 定义一个包含移位函数的模块 module shifter; // 左/右移位寄存器 `define LEFT_SHIFT 1'b0 `define RIGHT_SHIFT 1'b1 reg [31:0] addr, left_addr, right_addr; reg control; //每当新地址出现时就计算右移位和左移位的值 always @(addr) begin //调用下面定义的具有左右移位功能的函数 left_addr = shift(addr, `LEFT_SHIFT); right_addr = shift(addr, `RIGHT_SHIFT); end //定义移位函数,其输出是一个32位的值 function [31:0] shift; input [31:0] address; input control; begin //根据控制信号适当地设置输出值 shift = (control == `LEFT_SHIFT) ? (address << 1) : (address >> 1); end endfunction endmodule 例14说明如何定义自动函数,来完成阶乘运算。 [例14]递归(自动)函数 //用函数的递归调用定义阶乘计算 module top ; ... //定义自动(递归)函数 function automatic integer factorial ; input [ 31 : 0 ] oper ; integer i ; begin if ( operand >= 2 ) factorial = factorial ( oper - 1 ) * oper ; //递归调用 else factorial = 1 ; end endfunction //调用该函数 integer result ; initial begin result = factorial ( 4 ) ; // 调用4的阶乘 $display ( " Factorial of 4 is % 0d ", result ) ; // 显示24 end ...... ...... endmodule [例15]常量函数 module ram ( ... ... ...) ; parameter RAM_DEPTH = 256 ; input [ clog2( RAM_DEPTH) - 1 : 0 ] addr_bus ; // ... ... ... ... ... ... // function integer clogb2 ( input integer depth ) ; begin for ( clogb2 = 0 ; depth > 0 ; clogb2 = clogb2 + 1 ) depth = depth >> 1 ; end endfunction ... ... ... ... endmodule [例16]带符号函数 module top ; ... ... // // function signed [ 63 : 0 ] compute _signed ( input [ 63 : 0 ] vector ) ; ... ... ... ... endfunction // if ( compute_signed (vector) < - 3 ) begin ... ... end ... ... endmodule [例17]:module disp; initial begin $display("\\\t%%\n\"\123"); end endmodule 输出结果为 \% "S //从上面的这个例子中可以看到一些特殊字符的输出形式(八进制数123就是字符S)。 [例18]:module disp; reg[31:0] rval; pulldown(pd); initial begin rval=101; $display("rval=%h hex %d decimal", rval, rval); $display("rval=%o otal %b binary", rval, rval); $display("rval has %c ascii character value",rval); $display("pd strength value is %v",pd); $display("current scope is %m"); $display("%s is ascii value for 101",101); $display("simulation time is %t",$time); end endmodule 其输出结果为: rval=00000065 hex 101 decimal rval=00000000145 octal 00000000000000000000000001100101 binary rval has e ascii character value pd strength value is StX current scope is disp e is ascii value for 101 simulation time is 0 $display("d=%0h a=%0h",data,addr); [例19]:module printval; reg[11:0]r1; initial begin r1=10; $display("Printing with maximum size=%d=%h",r1,r1); $display("Printing with minimum size=%0d=%0h",r1,r1); end enmodule 输出结果为: Printing with maximum size=10=00a: printing with minimum size=10=a; [例20]文件描述符 //多通道描述符 integer handle1, handle2, handle3; //整型数为32 位 //标准输出是打开的; descriptor = 32'h0000_0001 ( 第0位置1) initial begin handle1 = $fopen("file1.out"); //handle1 = 32'h0000_0002 (bit 1 set 1) handle2 = $fopen("file2.out"); //handle2 = 32'h0000_0004 (bit 2 set 1) handle3 = $fopen("file3.out"); //handle3 = 32'h0000_0008 (bit 3 set 1) end 多通道描述符的优点在于可以有选择地同时写多个文件。下面将详细解释这一点。//所有的句柄已经在例18中定义 //写到文件中去 integer desc1, desc2, desc3 ; // 三个文件的描述符 initial begin desc1 = handle1 | 1; //按位或; desc1 = 32'h0000_0003 $fdisplay(desc1, "Display 1"); //写到文件file1.out和标准输出stdout desc2 = handle2 | handle1; //desc2 = 32 'h0000_0006 $fdisplay(desc2, "Display 2"); //写到文件file1.out和file2.out desc3 = handle3 ; //desc3 = 32'h0000_0008 $fdisplay(desc3, "Display 3"); //只写到文件file3.out end [例21] 显示层次 //显示层次信息 module M; initial $display("Displaying in %m"); endmodule //调用模块M module top; M m1 ( ); M m2 ( ); M m3 ( ); endmodule 仿真输出如下所示: Displaying in top.m1 Displaying in top.m2 Displaying in top.m3 这一特征可以显示全层次路径名,包括模块实例、任务、函数和命名块。 [例22]选通显示 //选通显示 always @ (posedge clock) begin a = b ; c = d ; end always @ (posedge clock) $strobe (“Displaying a = %b, c = % b” , a , c ); //显示正跳变沿时刻的值 //在例22中,时钟上升沿的值在语句a = b和c = d执行完之后才显示。 //如果使用$display,$display可能在语句a = b和c = d之前执行,结果显示不同的值。 [例23]: VCD文件系统任务 //指定VCD文件名。若不指定VCD文件,则由仿真器指定一缺省文件名 initial $dumpfile (“ myfile.dmp”) ; //仿真信息转储到myfile.dmp文件 // 转储模块中的信号 initial $dumpvars ; //没有指定变量范围,把设计中全部信号都转储 initial $dumpvars ( 1, top ) ; //转储模块实例top中的信号 //数1 表示层次的等级,只转储top下第一层信号 //即转储top模块中的变量,而不转储在top中调用 //模块中的变量 initial $dumpvars (2, top.m1) ; //转储top.m1模块下两层的信号 initial $dumpvars (0, top.m1) ; ///数0 表示转储top.m1模块下面各个层的所有信号 //启动和停止转储过程 initial begin $dumpon ; //启动转储过程 #100000 $dumpoff ; //过了100000个仿真时间单位后,停止转储过程 end //生成一个检查点,转储所有VCD变量的现行值。 initial $dumpall ; 一、2线-4线译码器 module counter4(q1,q0,ncr,cp); input cp,ncr; output q1,q0; reg q1,q0; always@(posedge cp or negedge ncr) begin if(~ncr){q1,q0}<=2'b00; else{q1,q0}<={q1,q0}+1'b1; end endmodule 二、4选1数据选择器 module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0; output y; reg y; always@(a1or a0) begin case({a1,a0}) 2'b00:y=i0; 2'b01:y=i1; 2'b10:y=i2; 2'b11:y=i3; default:y=0; 一、2线-4线译码器 module counter4(q1,q0,ncr,cp); input cp,ncr; output q1,q0; reg q1,q0; always@(posedge cp or negedge ncr) begin if(~ncr){q1,q0}<=2'b00; else{q1,q0}<={q1,q0}+1'b1; end endmodule 二、4选1数据选择器 module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0; output y; reg y; always@(a1or a0) begin case({a1,a0}) 2'b00:y=i0; Verilog编码风格 嵌入式开发2010-05-03 15:28:13 阅读14 评论0 字号:大中小订阅 这是以前公司的对fpga代码编写的要求 良好代码编写风格的通则概括如下: (1)对所有的信号名、变量名和端口名都用小写,这样做是为了和业界的习惯保持一致;对常量名和用户定义的类型用大写; (2)使用有意义的信号名、端口名、函数名和参数名; (3)信号名长度不要太长; (4)对于时钟信号使用clk 作为信号名,如果设计中存在多个时钟,使用clk 作为时钟信号的前缀; (5)对来自同一驱动源的信号在不同的子模块中采用相同的名字,这要求在芯片总体设计时就定义好顶层子模块间连线的名字,端口和连接端口的信号尽可能采用相同的名字; (6)对于低电平有效的信号,应该以一个下划线跟一个小写字母b 或n 表示。注意在同一个设计中要使用同一个小写字母表示低电平有效; (7)对于复位信号使用rst 作为信号名,如果复位信号是低电平有效,建议使用rst_n; (8)当描述多比特总线时,使用一致的定义顺序,对于verilog 建议采用bus_signal[x:0]的表示; (9)尽量遵循业界已经习惯的一些约定。如*_r 表示寄存器输出,*_a 表示异步信号,*_pn 表示多周期路径第n 个周期使用的信号,*_nxt 表示锁存前的信号,*_z 表示三态信号等; (10)在源文件、批处理文件的开始应该包含一个文件头、文件头一般包含的内容如下例所示:文件名,作者,模块的实现功能概述和关键特性描述,文件创建和修改的记录,包括修改时间,修改的内容等; (11)使用适当的注释来解释所有的always 进程、函数、端口定义、信号含义、变量含义或信号组、变量组的意义等。注释应该放在它所注释的代码附近,要求简明扼要,只要足够说明设计意图即可,避免过于复杂; (12)每一行语句独立成行。尽管VHDL 和Verilog 都允许一行可以写多个语句,当时每个语句独立成行可以增加可读性和可维护性。同时保持每行小于或等于72 个字符,这样做都是为了提高代码得可读性; (13)建议采用缩进提高续行和嵌套语句得可读性。缩进一般采用两个空格,如西安交通大学SOC 设计中心 2 如果空格太多则在深层嵌套时限制行长。同时缩进避免使用TAB 键,这样可以避免不同机器TAB 键得设置不同限制代码得可移植能力; (14)在RTL 源码的设计中任何元素包括端口、信号、变量、函数、任务、模块等的命名都不能取Verilog 和VHDL 语言的关键字; (15)在进行模块的端口申明时,每行只申明一个端口,并建议采用以下顺序: 生命科学技术学院《CMOS专用集成电路》实验报告 学院(系):生命科学技术学院 专业:生物医学工程 班级:151011 学号:15101004 学生姓名:柳琳 2013年06 月29 日 一、实验题目 (1)更改测试文件相关部分的参数值,将该乘法器的数据位宽改为8-Bit。 (2)根据对实验电路的分析,绘制该移位式乘法器电路详细的电路结构框图,并对每一功能部件的功能及相关参数的意义进行说明; (3)采用Verilog HDL硬件描述语言设计一个16-Bit超前进位加法器; (4)在上面超前进位加法器基础上,将原电路的部分积求和电路改进成超前进位加法器。 二、实验结果与讨论 (1)更改测试文件相关部分的参数值,将该乘法器的数据位宽改为8-Bit。 module multiplier_nbit ( rst, clk, x, y, result ); parameter mwidth = 8; parameter rwidth = mwidth + mwidth; input rst, clk; … reg [1:0] stcnt; reg [2:0] mucnt; … assign mucnt_en = (stcnt == 2'b01) ? 1'b1 : 1'b0; assign mucnt_full = (mucnt == 3'b111) ? 1'b1 : 1'b0; assign stcnt_load = (stcnt == 2'b10) ? 1'b1 : 1'b0; … always @(posedge rst or posedge clk) begin if(rst) mucnt <= 3'b000; else if(mucnt_en) mucnt <= mucnt + 1; else mucnt <= mucnt; end module test_mult; reg rst, clk; reg [7:0] x, y; wire [15:0] result; java异常(习题) 练习 1. 填空 Java 中所有的错误都继承自______类;在该类的子类中, _______类表示严重的底层错误,对于这类错误一般处理的方式是___________; _______类表示例外、异常。 2. 查api,填空 异常类java.rmi.AlreadyBoundException,从分类上说,该类属于__________(已检查| 未检查)异常,从处理方式上说,对这种异常___________________; 异常类java.util.regex.PatternSyntaxException,从分类上说,该类属于_________(已检查|未检查)异常,从处理方式上说,对这种异常__________________。 4. (try-catch-finally)有如下代码: 问:当读入的n 分别为1,2,3,4,5 时,输出的结果分别是什么? 5. (自定义异常)创建两个自定义异常类MyException1 和MyException2。 要求: 1) MyException1 为已检查异常,MyException2 为未检查异常 2) 这两个异常均具有两个构造函数,一个无参,另一个带字符串参数,参数表示产生异常的详细信息。 问: 在//1 处,填入以下________代码可以编译通过,在//2 处,填入_________代码可以编译通过。 A. throws java.io.IOException B. throws java.io., java.io.EOFException C. throws java.sql.SQLException D. 不能抛出任何异常。 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 2020/02/28 13:40:03 // Design Name: // Module Name: _74ls138 // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module _74ls138(nE1,nE2,E3,B,nY); input nE1,nE2,E3; input [2:0]B; output[7:0]nY; reg[7:0]nY; always@(nE1,nE2,E3,B) if(!nE1 && !nE2 && E3) begin case(B) 3'b000: nY = 8'b1111_1110; 3'b001: nY = 8'b1111_1101; 3'b010: nY = 8'b1111_1011; 3'b011: nY = 8'b1111_0111; 3'b100: nY = 8'b1110_1111; 3'b101: nY = 8'b1101_1111; 3'b110: nY = 8'b1011_1111; 3'b111: nY = 8'b0111_1111; default:nY = 8'b1111_1111; endcase end 第五章Java语言异常处理--实验题目 一、实验目的 1. 掌握Java的异常处理机制。 2. 掌握try、catch、throws和finally这5个关键字的用法。 3. 掌握成员的几个异常类。 4. 掌握自定义异常的使用。 二、实验内容 1.编写程序,从键盘上输入两个数。将第一个数除以第二个数并显示结果;处理所有可能的异常。 2.写出下面程序运行的结果: 3.写出下列程序的输出结果。 4.有下列程序: 若用下面方式执行该程序,则baz的值为( )。 java Test Red Green Blue (A)“”(B)null (C)"Red”(D)”BIue”(E)”Green”(F)代码不能编译(G)程序抛出异常5.有下列程序: 该程序的输出结果为( )。 (A)没有任何输出(B)输出“Finally”(C)编译错误(D)抛出异常 6.有下列程序: 该程序的输出结果为( )。 (A)没有任何输出(B)输出“Finally”(C)编译错误(D)抛出异常7.修改下列程序的错误之处。 8.写出下列程序的运行结果。 9.编写一个程序,要求从键盘输入一个double型的圆的半径,计算并精出其面积。 测试当输入的数据不是double型数据(如字符串“abc”)会产生什么结果,怎样处理。10.编写一个应用程序,在main()方法中使用try块抛出一个Exception类的对象,为Exception的构造方法提供一个字符串参数,在catch块内捕获该异常并打印出字符串参数。添加一个finally块并打印一条消息。 11.创建一个自定义的异常类,该类继承Exception类,为该类写一个构造方法,该构造方法带一个String类型的参数。写一个方法.令其打印出保存下来的String对泉。再编写一个类,在main()方法中使用try--catch结构创建一个MyException类的对象并抛出,在catch块中捕获该异常井打印出传递的String消息。 支持论坛发展帖出全数字锁相环的verilog源代码,仿真已通过 module dpll(reset,clk,signal_in,signal_out,syn; parameter para_K=4; parameter para_N=16; input reset; input clk; input signal_in; output signal_out; output syn; reg signal_out; reg dpout; reg delclk; reg addclk; reg add_del_clkout; reg [7:0]up_down_cnt; reg [2:0]cnt8; reg [8:0]cnt_N; reg syn; reg dpout_delay; reg [8:0]cnt_dpout_high; reg [8:0]cnt_dpout_low; /******phase detector*****/ always@(signal_in or signal_out begin dpout<=signal_in^signal_out; end /******synchronization establish detector*****/ always@(posedge clk or negedge reset begin if(!reset dpout_delay<='b0; else dpout_delay<=dpout; end always@(posedge clk or negedge reset begin if(!reset begin cnt_dpout_high<='b0; cnt_dpout_low<='b0; end else if(dpout if(dpout_delay==0 cnt_dpout_high<='b0; else if(cnt_dpout_high==8'b11111111 cnt_dpout_high<='b0; else cnt_dpout_high<=cnt_dpout_high+1; else if(!dpout if(dpout_delay==1 cnt_dpout_low<='b0; else if(cnt_dpout_low==8'b11111111 cnt_dpout_low<='b0; else cnt_dpout_low<=cnt_dpout_low+1; end always@(posedge clk or negedge reset begin if(!reset syn<='b0; else if((dpout&&!dpout_delay||(!dpout&&dpout_delay if(cnt_dpout_high[8:0]-cnt_dpout_low[8:0]<=4||cnt_dpout_low[8:0]- cnt_dpout_high[8:0]<=4 syn<='b1; else syn<='b0; end /****up down couter with mod=K****/ always@(posedge clk or negedge reset begin if(!reset begin delclk<='b0; addclk<='b0; up_down_cnt<='b00000000; end else begin if(!dpout begin delclk<='b0; if(up_down_cnt==para_K-1 begin up_down_cnt<='b00000000; addclk<='b0; end else begin up_down_cnt<=up_down_cnt+1; addclk<='b0; end end else begin addclk<='b0; if(up_down_cnt=='b0 begin up_down_cnt<=para_K-1; delclk<='b0; end else if(up_down_cnt==1 begin delclk<='b1; up_down_cnt<=up_down_cnt-1; end else up_down_cnt<=up_down_cnt-1; end end end /******add and delete clk*****/ always@(posedge clk or negedge reset begin if(!reset begin cnt8<='b000; end else begin if(cnt8=='b111 begin cnt8<='b000; end else if(addclk&&!syn begin cnt8<=cnt8+2; end else if(delclk&&!syn j a v a异常处理例题代 码 App9_1.java:输出一个数组的所有元素,捕获数组下标越界异常和除娄为0异常。public class App9_1{ public static void main(String args[]){ int i; int[] a={1,2,3,4}; for(i=0;i<5;i++) System.out.println(" a["+i+"]="+a[i]); System.out.println("5/0"+(5/0)); } } App9_2.java:使用try-catch-finall语句对程序中的异常进行捕获与处理。 public class App9_2{ public static void main(String args[]){ int i; int a[]={1,2,3,4}; for (i=0;i<5;i++){ try{ System.out.print("a["+i+"]/"+i+"="+(a[i]/i)); } catch(ArrayIndexOutOfBoundsException e){ System.out.print("捕获到了数组下标越界异常"); } catch(ArithmeticException e){ System.out.print("异常类名称是:"+e); //显示异常信息 } catch(Exception e){ System.out.println("捕获"+e.getMessage()+"异常!"); //显示异常信息 } finally{ System.out.println(" finally i="+i); } } System.out.println("继续!!"); } } App9_3.java:使用throw语句在方法中抛出异常。 public class App9_3{ public static void main(String args[]){ int a=5,b=0; try{ if (b==0) throw new ArithmeticException(); //抛出异常,不是必须的 else System.out.println(a+"/"+b+"="+a/b); //若不抛出异常,则运行此行 设计示范和上机习题 练习一.简单的组合逻辑设计 //(方法一): //---------------文件名compare.v ----------------- module compare(equal,a,b); input a,b; output equal; assign equal = (a==b)? 1 : 0; //a等于b时,equal输出为1;a不等于b时,equal输出为0。 endmodule //(方法二): module compare(equal,a,b); input a,b; output equal; reg equal; always @(a or b) if(a==b) //a等于b时,equal输出为1; equal =1; else //a不等于b时,equal输出为0。 equal = 0; //思考:如果不写else 部分会产生什么逻辑? endmodule //------------------------------------------------------------- //----------测试模块源代码(方法之一): `timescale 1ns/1ns // 定义时间单位。 `include "./compare.v" //包含模块文件。在有的仿真调试环境中并不需要此语句。 //而需要从调试环境的菜单中键入有关模块文件的路径和名称module t; reg a,b; wire equal; initial // initial常用于仿真时信号的给出。 begin a=0; b=0; #100 a=0; b=1; #100 a=1; b=1; #100 a=1; b=0; #100 a=0; b=0; 有限状态机实验报告 一、实验目的 ●进一步学习时序逻辑电路 ●了解有限状态机的工作原理 ●学会使用“三段式”有限状态机设计电路 ●掌握按键去抖动、信号取边沿等处理技巧 二、实验内容 用三段式有限状态机实现序列检测功能电路 a)按从高位到低位逐位串行输入一个序列,输入用拨动开关实现。 b)每当检测到序列“1101”(不重叠)时,LED指示灯亮,否则灭,例如 i.输入:1 1 0 1 1 0 1 1 0 1 ii.输出:0 0 0 1 0 0 0 0 0 1 c)用八段数码管显示最后输入的四个数,每输入一个数,数码管变化一次 d)按键按下的瞬间将拨动开关状态锁存 i.注意防抖动(按键按下瞬间可能会有多次的电平跳变) 三、实验结果 1.Rst_n为0时数码管显示0000,led灯不亮,rst_n拨为1,可以开始输入,将输 入的开关拨到1,按下按钮,数码管示数变为0001,之后一次类推分别输入1, 0,1,按下按钮后,数码管为1101,LED灯亮,再输入1,LED灯灭,之后再输 入0,1(即共输入1101101使1101重叠,第二次LED灯不亮),之后单独输入 1101,LED灯亮 2.仿真图像 刚启动时使用rst_n 一段时间后 其中Y代表输出,即控制led灯的信号,sel表示数码管的选择信号,seg表示数码管信号 四、实验分析 1、实验基本结构 其中状态机部分使用三段式结构: 2、整体结构为: 建立一下模块: Anti_dither.v 输入按键信号和时钟信号,输出去除抖动的按键信号生成的脉冲信号op 这一模块实现思路是利用按钮按下时会持续10ms以上而上下抖动时接触时间不超过10ms来给向下接触的时间计时,达到上限时间才产生输出。 Num.v 输入op和序列输入信号A,时钟信号clk和复位信号,复位信号将num置零,否则若收到脉冲信号则将num左移一位并将输入存进最后一位。输出的num即为即将在数码管上显示的值 Scan.v 输入时钟信号,对其降频以产生1ms一次的扫描信号。 Trigger.v 这一模块即为状态机模块,按三段式书写。 整个模块的输入为时钟信号,脉冲信号,序列输入变量,复位信号,输出LED灯控制信号Y。 第一段是状态转换模块,为时序逻辑电路,功能是描述次态寄存器迁移到现态寄存器。即如果收到复位信号将现态置零,否则将上次得到的next_state赋给current_state。 App9_1.java:输出一个数组的所有元素,捕获数组下标越界异常和除娄为0异常。public class App9_1{ public static void main(String args[]){ int i; int[] a={1,2,3,4}; for(i=0;i<5;i++) System.out.println(" a["+i+"]="+a[i]); System.out.println("5/0"+(5/0)); } } App9_2.java:使用try-catch-finall语句对程序中的异常进行捕获与处理。 public class App9_2{ public static void main(String args[]){ int i; int a[]={1,2,3,4}; for (i=0;i<5;i++){ try{ System.out.print("a["+i+"]/"+i+"="+(a[i]/i)); } catch(ArrayIndexOutOfBoundsException e){ System.out.print("捕获到了数组下标越界异常"); } catch(ArithmeticException e){ System.out.print("异常类名称是:"+e); //显示异常信息 } catch(Exception e){ System.out.println("捕获"+e.getMessage()+"异常!"); //显示异常信息 } finally{ System.out.println(" finally i="+i); } } System.out.println("继续!!"); } } App9_3.java:使用throw语句在方法中抛出异常。 public class App9_3{ public static void main(String args[]){ int a=5,b=0; try{ if (b==0) throw new ArithmeticException(); //抛出异常,不是必须的 else System.out.println(a+"/"+b+"="+a/b); //若不抛出异常,则运行此行 【例3.1】4位全加器 module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 【例3.2】4位计数器 module count4(out,reset,clk); output[3:0] out; input reset,clk; reg[3:0] out; always @(posedge clk) begin if (reset) out<=0; //同步复位 else out<=out+1; //计数 end endmodule 【例3.3】4位全加器的仿真程序 `timescale 1ns/1ns `include "adder4.v" module adder_tp; //测试模块的名字 reg[3:0] a,b; //测试输入信号定义为reg型 reg cin; wire[3:0] sum; //测试输出信号定义为wire型 wire cout; integer i,j; adder4 adder(sum,cout,a,b,cin); //调用测试对象 always #5 cin=~cin; //设定cin的取值 initial begin a=0;b=0;cin=0; for(i=1;i<16;i=i+1) #10 a=i; //设定a的取值 end - 1 - initial begin for(j=1;j<16;j=j+1) #10 b=j; //设定b的取值 end initial//定义结果显示格式 begin $monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum); #160 $finish; end endmodule 【例3.4】4位计数器的仿真程序 `timescale 1ns/1ns `include "count4.v" module coun4_tp; reg clk,reset; //测试输入信号定义为reg型 wire[3:0] out; //测试输出信号定义为wire型 parameter DELY=100; count4 mycount(out,reset,clk); //调用测试对象 always #(DELY/2) clk = ~clk; //产生时钟波形 initial begin//激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end //定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule 【例3.5】“与-或-非”门电路 module AOI(A,B,C,D,F); //模块名为AOI(端口列表A,B,C,D,F) input A,B,C,D; //模块的输入端口为A,B,C,D output F; //模块的输出端口为F - 2 - 第十章例题 module add_4( X, Y, sum, C); input [3 : 0] X, Y; output [3: 0] sum; output C; assign {C, Sum } = X + Y; endmodule //而16位加法器只需要扩大位数即可,见下例: module add_16( X, Y, sum, C); input [15 : 0] X, Y; output [15 : 0] sum; output C; assign {C, Sum } = X + Y; endmodule 快速乘法器常采用网格形式的迭带阵列结构,图10.3示出两个四位二进制数相乘的结构图,//用Verilog HDL来描述乘法器是相当容易的,只需要把运算表达式写出就可以了,见下例。module mult_4( X, Y, Product); input [3 : 0] X, Y; output [7 : 0] Product; assign Product = X * Y; endmodule // 而8位乘法器只需要扩大位数即可,见下例: module mult_8( X, Y, Product); input [7 : 0] X, Y; output [15 : 0] Product; assign Product = X * Y; endmodule // 下面就是一个位数可以由用户定义的比较电路模块: module compare_n ( X, Y, XGY, XSY, XEY); input [width-1:0] X, Y; output XGY, XSY, XEY; reg XGY, XSY, XEY; parameter width = 8; always @ ( X or Y ) // 每当X 或Y 变化时 begin if ( X = = Y ) XEY = 1; // 设置X 等于Y的信号为1 else XEY = 0; if (X > Y) XGY = 1; // 设置X 大于Y的信号为1 else XGY = 0; if (X < Y) XSY = 1; // 设置X 小于Y的信号为1 else XSY = 0; end endmodule //下面就是带使能控制信号(nCS)的数据位宽可以由用户定义的(8位)八路数据通道选择器模块: module Mux_8( addr,in1, in2, in3, in4, in5, in6, in7, in8, Mout, nCS); input [2:0] addr; input [width-1:0] in1, in2, in3, in4, in5, in6, in7, in8; input nCS; output [width-1:0] Mout; parameter width = 8; always @ (addr or in1 or in2 or in3 or in4 or in5 or in6 or in7 or in8 or nCS) begin if (!nCS) //nCS 低电平使多路选择器工作 case(addr) 3’b000: Mout = in1; 3’b001: Mout = in2; 3’b010: Mout = in3; 3’b011: Mout = in4; 异常处理练习题 一、选择题 1.java中用来抛出异常的关键字是 (C) A、try B、catch C、throw D、finally 2.关于异常,下列说法正确的是(A) A、异常是一种对象 B、一旦程序运行,异常将被创建 C、为了保证程序运行速度,要尽量避免异常控制 D、以上说法都丌对 3.(A)类是所有异常类的父类。 A、Throwable B、Error C、Exception D、AWTError 4.java语言中,下列哪一子句是异常处理的出口(C) A、try{…}子句 B、catch{…}子句 C、finally{…}子句 D、以上说法都丌对 5.下列程序的执行,说法错误的是 (C) public class MultiCatch { public static void main(String args[]) { try { int a=args.length; int b=42/a; int c[]={1}; c[42]=99; System.out.println(“b=”+b); } catch(ArithmeticException e) { System.out.println(“除0异常:”+e); } catch(ArrayIndexOutOfBoundsException e) { System.out.println(“数组超越边界异常:”+e); } } } A、程序将输出第15行的异常信息 B、程序第10行出错 C、程序将输出“b=42” D、程序将输出第15和19行的异常信息 6.下列程序的执行,说法正确的是(D) class ExMulti { static void procedure() { try { int c[]={1}; c[42]=99; } catch(ArrayIndexOutOfBoundsException e) { System.out.println(“数组超越界限异常:”+e); } } public static void main(String args[]) { try { procedure(); int a=args.length; int b=42/a; System.out.println(“b=”+b); } catch(ArithmeticException e) { System.out.println(“除0异常:”+e); } } } A、程序只输出第12行的异常信息 B、程序只输出第26行的异常信息 C、程序将不输出异常信息 D、程序将输出第12行和第26行的异常信息 7.下面程序抛出了一个“异常”并捕捉它。请在横线处填入适当内容完成程序。class TrowsDemo { static void procedure() throws IllegalAccessExcepton { System.out.println(“inside procedure”); throw__new_____IllegalAccessException(“demo”); 第二章 /*1----------------------------------------------*/ module IS; //... SC sc1; MEM mem1; Xbar xbar1; endmodule; module SC; //... endmodule; moduleXbar; //... endmodule; module MEM; //... endmodule; module Top; IS is1; endmodule /*2----------------------------------------------*/ module FA; endmodule moduleRipple_Add; FA fa0; FA fa1; FA fa2; FA fa3; Endmodule 第三章 /*1---------------------------------------------------------------*/ a:8b0111_1011 b:16hxxxx c: -2(1010)--取反(1101)----再加一(1110) d: 'h1234 /*2---------------------------------------------------------------*/ a:正确 b:正确 c:正确 d:正确 /*3---------------------------------------------------------------*/ a :合法 b :合法 c :不合法,含有$ 为延时含义 d :标识符组成:字母数字下划线。 /*4---------------------------------------------------------------*/ a: wire [7:0] a_in; b: reg [31:0] c: integer count; d: time snap_shot; e: integer delays[20]; f: reg [63:0] mem[256]; g: parameter cach_size=256; /*5---------------------------------------------------------------*/ a : 1010 b: 10 c : 400 第四章 /*1-----------------------------------------------------------------------*/ //模块的基本组成部分有哪些?哪几个部分必须出现? 模块定义已关键字module开始,模块名,端口列表,端口声明和可选的参数声明出现在其他部分的前面 ,endmodule必须为最后一条语句 1)wire。reg和其他类型的变量的声明 2)数据流语句(assign,连续赋值语句) 3)低层模块实例 4)always和initial块,所有的行为语句都在这些块中 5) 任务和函数。 其中module和模块名和endmodule是必不可少的。 /*2-----------------------------------------------------------------------*/ //一个不与外界环境交互的模块是否有端口?模块定义中是否有端口列表? 不与外界交互即没有端口列表,在没有端口的情况下端口列表也是不存在的。 // megafunction wizard: %ALTPLL% // GENERATION: STANDARD // VERSION: WM1.0 // MODULE: altpll // ============================================================ // File Name: clk_ctrl.v // Megafunction Name(s): // altpll // // Simulation Library Files(s): // altera_mf // ============================================================ // ************************************************************ // THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! // // 11.0 Build 208 07/03/2011 SP 1 SJ Full Version // ************************************************************ //Copyright (C) 1991-2011 Altera Corporation //Your use of Altera Corporation's design tools, logic functions //and other software and tools, and its AMPP partner logic //functions, and any output files from any of the foregoing //(including device programming or simulation files), and any //associated documentation or information are expressly subject //to the terms and conditions of the Altera Program License //Subscription Agreement, Altera MegaCore Function License //Agreement, or other applicable license agreement, including, //without limitation, that your use is for the sole purpose of //programming logic devices manufactured by Altera and sold by //Altera or its authorized distributors. Please refer to the //applicable agreement for further details. // synopsystranslate_off `timescale 1 ps / 1 ps // synopsystranslate_on moduleclk_ctrl ( areset, inclk0, c0, c1, c2,VerilogHDL经典程序非常适合新手

Verilog编码风格

专用集成电路,verilog移位乘法器,源代码及电路仿真

Java-异常(习题)

74LS138Verilog源码

第五章Java语言异常处理-实验题目

全数字锁相环的verilog源代码讲解

java异常处理例题代码教学文稿

夏宇闻verilog设计示范和上机习题

verilog有限状态机实验报告(附源代码)

java异常处理例题代码

Verilog的135个经典设计实例

第10章例题verilog源代码(夏宇闻版)

java异常处理试题及答案

Verilog HDL数字设计与综合 夏宇闻译(第二版)课后题答案

基于FPGA的SDRAM实验Verilog源代码