时序逻辑电路实验报告

实验六时序逻辑电路测试及研究

一、实验目的

1、掌握计数器电路分析及测试方法。

2、训练独立进行实验的技能。

二、实验仪器及器件

1、双踪示波器、实验箱

2、实验用元器:74LS00 1片 74lS73 2片 74LS175 1片 74LS10 1片

三、实验内容、测试电路及测试表格

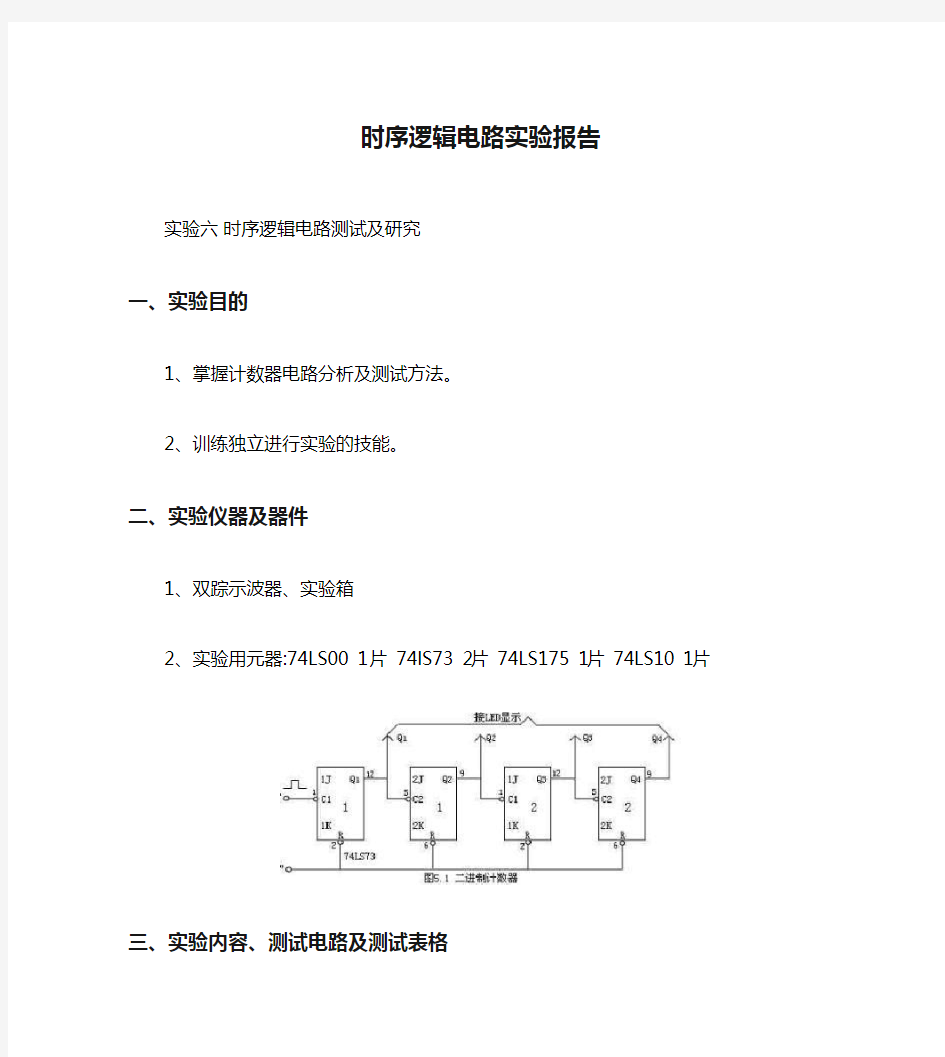

1、异步二进制计数器

(1) 按图5.1 接线。

(2) 由CP 端输入单脉冲,测试并记录 Q1—Q4 状态及波形(可调连续脉冲)。

表6.1

Q4 Q3 Q2 Q1 Q4 Q3 Q2 Q1 0 0 0 0 0 9 1 0 0 1 1 0 0 0 1 10 1 0 1 0 2 0

0 1 0 11 1 0 1 1 3 0 0 1 1 12 1 1 0 0 4 0 1 0 0 13 1 1 0 1 5 0 1 0 1 14

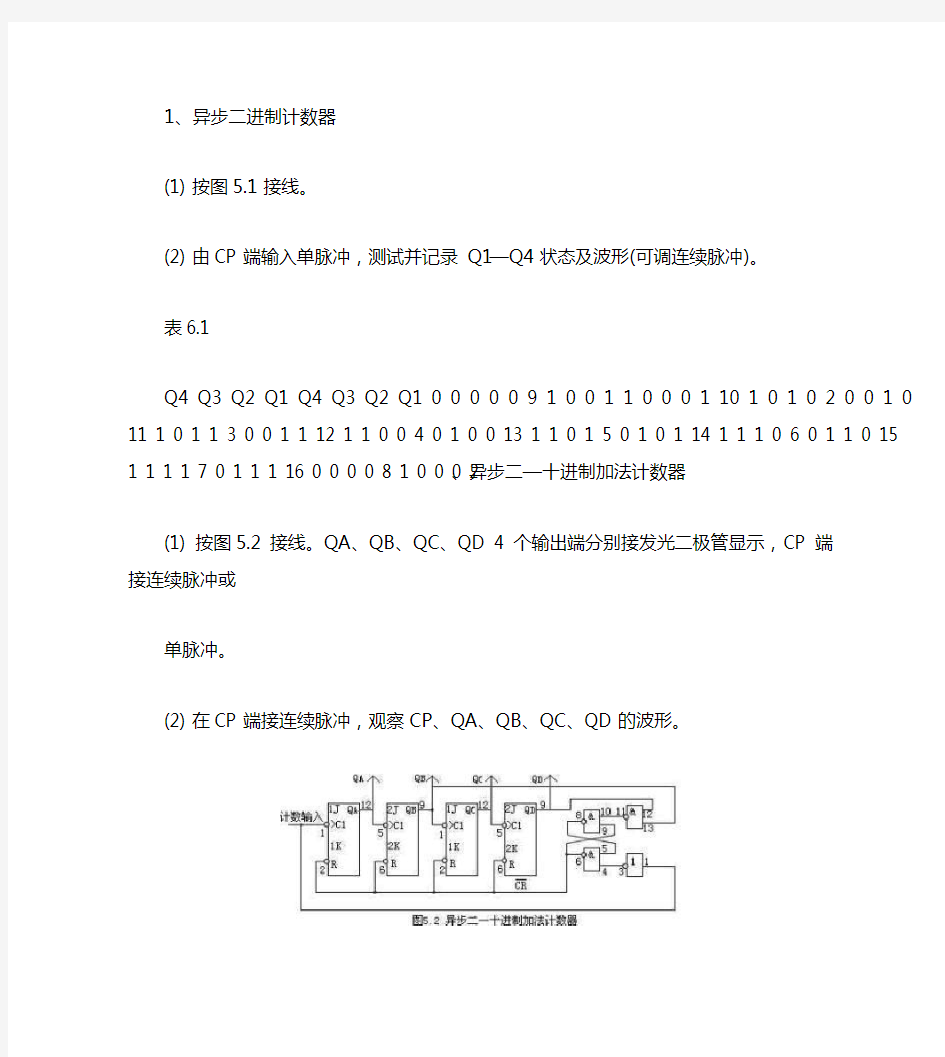

1 1 1 0 6 0 1 1 0 15 1 1 1 1 7 0 1 1 1 16 0 0 0 0 8 1 0 0 0 2、异步二—十进制加法计数器

(1) 按图5.2 接线。QA、QB、QC、QD 4 个输出端分别接发光二极管显示,CP 端接连续脉冲或

单脉冲。

(2) 在CP 端接连续脉冲,观察CP、QA、QB、QC、QD 的波形。

(3) 画出CP、QA、QB、QC、QD 的波形。

表6.2

QD QC QB QA QD QC QB QA

0 0 0 0 0 6 0 1 1 0

1 0 0 0 1 7 0 1 1 1

2 0 0 1 0 8 1 0 0 0

3 0 0 1 1 9 1 0 0 1

4 0 1 0 0 10 0 0 0 0

5 0 1 0 1 11 0 0 0 1

3、移位寄存器型计数器

(1) 按图5.3 接线构成环形计数器,将A、B、C、D 置为1000,用单脉冲计数,记录各触发器状态。

表6.3

A B C D

1 1 0 0 0

2 0 1 0 0

3 0 0 1 0

4 0 0 0 1

5 1 0 0 0

(2) 改为连续脉冲计数,并将其中一个状态为“0”的触发器置为“1”(模拟干扰信号作用的结果),观察计数器能否正常工作。分析原因。

分析:输出端没有任何波形,故计数器没有正常工作。这是因为在这个计数器循环中,当有且只有一位被置“1”时,才可以进入有效循环。而出现两个“1”时,不在有效循环内,故无法工作。

从此部分实验,我明白了设计时序电路最后一步要检查电路是否能经过若干个有效循环后进入自启动。因为有些同步时序电路设计中会出现不在循环内的无效状态,开始很有可能是无效状态,故应检查自启动能力。

时序逻辑电路的特点:

时序逻辑电路是指任意时刻的输出状态不仅与该时刻的输入信号状态有关,而且还与信

号作用前电路的状态有关,在电路结构上,必定含有具有记忆功能的存储电路。

在任意时刻的输出状态不仅与该时刻的输入信号状态有关,而且还与信号作用前电路的状态有关,其结构特点是由存储电路和组合电路两部分组成。时序电路的状态是由存储电路来记忆的,因而在时序逻辑电路中,触发器是必不可少的,而组合逻辑电路在有些时序电路中则可以没有。时序电路又分为同步时序逻辑电路和异步时序逻辑电路两大类。在同步时序电路中,所有触发器的时钟输入端CP都连在一起,而在异步时序逻辑电路中,外加时钟脉冲CP只触发部分触发器,其余触发器则是由电路内部信号触发的。