CRC循环码

- 格式:doc

- 大小:352.00 KB

- 文档页数:21

循环冗余校验码计算例题

假设有一组数据101101,我们要计算它的循环冗余校验码(CRC码),假定生成多项式为x^3+1(即二进制表示为1011),则计算过程如下:

1. 将数据101101左侧填充3个0,得到0101101 000。

2. 取出左侧的4位作为初始值,即0101。

3. 从左至右取出剩余的位,包括生成多项式的次数所对应的位,即从第5位开始。

每次计算的方法是:将当前的4位和下一位(或生成多项式的次数所对应的位)进行异或操作,将结果作为新的4位。

重复此过程,直到取出所有位。

- 第一次计算:0101 异或 1 = 0100

- 第二次计算:1000 异或 1 = 1001

- 第三次计算:0011 异或 0 = 0011

- 最终得到的4位就是计算出来的CRC码,即0011。

4. 将CRC码添加到原始数据末尾,得到最终的发送数据:101101 0011。

接收端收到数据后,也可以按照同样的方式计算CRC码,然后将计算出的CRC码和接收到的CRC码进行比较,如果相同则说明数据未出错,否则说明数据出现了错误。

需要注意的是,生成多项式的选择对于CRC码的计算和校验非常重要,不同的生成多项式可能会产生不同的CRC码,导致校验结果不准确。

因此,在实际应用中,需要根据具体情况选择合适的生成多项式。

crc循环冗余校验码校验规则英文回答:Introduction to CRC (Cyclic Redundancy Check)。

Cyclic Redundancy Check (CRC) is an error-detecting code commonly used in digital networks and storage devices. It is a type of polynomial code that generates a fixed-length checksum based on the input data. The checksum is appended to the data and used to verify the integrity of the data during transmission or storage.How CRC Works.CRC works by dividing the input data by a predetermined polynomial. The remainder of this division is known as the CRC value. The CRC value is then appended to the input data and transmitted or stored.When the data is received or retrieved, the CRC valueis recalculated using the same polynomial. If the recalculated CRC value matches the original CRC value, it indicates that the data has not been corrupted during transmission or storage.Types of CRC Polynomials.There are various types of CRC polynomials, each with its own characteristics. Some common CRC polynomials include:CRC-16: Used in various applications, including data communication protocols and storage devices.CRC-32: Widely used in file transfer protocols, such as ZMODEM and Kermit.CRC-64: Used in high-performance computing and storage systems.Applications of CRC.CRC is used in a wide range of applications, including:Data communication: CRC is used to detect errors in data transmitted over networks and communication channels.Storage devices: CRC is used to protect data stored on hard drives, RAID systems, and other storage media.Error correction: Some CRC algorithms can correct errors in addition to detecting them.CRC Calculation Methods.There are two main methods for calculating CRC values:Hardware implementation: CRC values can be calculated using dedicated hardware circuits.Software implementation: CRC values can be calculated using software algorithms.Benefits of Using CRC.Error detection: CRC is effective in detecting errors that occur during data transmission or storage.Data integrity verification: CRC ensures that the received data is identical to the data that was sent.Efficient error detection: CRC can detect errors quickly and efficiently.Error correction (in some cases): Certain CRC algorithms can also correct errors.Limitations of CRC.False positives: CRC can sometimes detect errors that do not actually exist.Limited error detection: CRC can only detect errors that occur within the scope of the CRC calculation.Polynomial selection: The choice of CRC polynomial canaffect the effectiveness of error detection.Conclusion.Cyclic Redundancy Check (CRC) is a powerful error-detecting code that plays a vital role in ensuring data integrity in various applications. By generating a checksum based on the input data and verifying it after transmission or storage, CRC helps detect errors and maintain the reliability of data.中文回答:什么是CRC循环冗余校验码?CRC(循环冗余校验码)是一种常用于数字网络和存储设备中的错误检测码。

CRC循环冗余校验是一种用于检测数据传输过程中可能出现的错误的方法。

以下是一个简单的CRC循环冗余校验的例子:

假设我们有一个8位的数据块,其内容为01010101。

1.首先,我们选择一个生成多项式,例如CRC-8的生成多项式为X^8 + X^2 + X^1 + X^0。

2.将数据块左移8位,得到101010100。

3.对数据块进行模2除法,用生成多项式去除数据块。

在这个例子中,101010100除以X^8 + X^2 + X^1 + X^0得到余数0001。

4.将余数添加到数据块的末尾,得到新的数据块101010100001。

5.将新的数据块发送给接收方。

接收方收到数据块后,重复上述步骤:

1.对接收到的数据块进行模2除法,用生成多项式去除数据块。

2.如果余数为0,则说明数据块在传输过程中没有出现错误;如果余数不为0,则说明数据块在传输过程中出现了错误。

这个例子展示了CRC循环冗余校验的基本原理。

在实际应用中,CRC算法会更加复杂,但基本原理是相同的。

CRC循环冗余校验码总结(转)⼀、CRC简介先在此说明下什么是CRC:循环冗余码校验英⽂名称为Cyclical Redundancy Check,简称CRC,它是利⽤除法及余数的原理来作错误侦测(Error Detecting)的。

实际应⽤时,发送装置计算出CRC值并随数据⼀同发送给接收装置,接收装置对收到的数据重新计算CRC并与收到的CRC相⽐较,若两个CRC值不同,则说明数据通讯出现错误那么其实CRC有⽐较多种,⽐如CRC16、CRC32 ,为什么叫16、32呢。

在这⾥并⾮与位有和关系。

⽽是由所确定的多项式最⾼次幂确定的。

如下所⽰。

理论上讲幂次越⾼校验效果越好。

CRC(12位) =X12+X11+X3+X2+X+1 CRC(16位) = X16+X15+X2+1 CRC(CCITT) = X16+X12 +X5+1 CRC(32位) = X32+X26+X23+X16+X12+X11+X10+ X8+X7+X5+X4+X2+X+1⼆、循环冗余校验码(CRC)的基本原理:在K位信息码后再拼接R位的校验码,整个编码长度为N位,因此,这种编码⼜叫(N,K)码。

对于⼀个给定的(N,K)码,可以证明存在⼀个最⾼次幂为N-K=R的多项式G(x)。

根据G(x)可以⽣成K 位信息的校验码,⽽G(x)叫做这个CRC码的⽣成多项式。

校验码的具体⽣成过程为:假设发送信息⽤信息多项式C(X)表⽰,将C(x)左移R位,则可表⽰成C(x)*2R,这样C(x)的右边就会空出R位,这就是校验码的位置。

通过C(x)*2R除以⽣成多项式G(x)得到的余数就是校验码。

原理思维导图总结:三、通信与⽹络中常⽤的CRC在数据通信与⽹络中,通常k相当⼤,由⼀千甚⾄数千数据位构成⼀帧,⽽后采⽤CRC码产⽣r位的校验位。

它只能检测出错误,⽽不能纠正错误。

⼀般取r=16,标准的16位⽣成多项式有CRC-16=x16+x15+x2+1 和CRC-CCITT=x16+x15+x2+1。

循环冗余校验码和海明码循环冗余校验码(CRC)是一种在数据传输中常用的纠错码,它利用多项式除法来进行计算,用来验证数据在传输过程中是否出现错误。

CRC码的计算过程比较简单,适用于高速传输和实时应用。

CRC码通常由一个生成多项式来生成,接收端也使用同样的生成多项式来进行校验,当数据在传输中出现错误时,接收端可以通过生成多项式计算来检测错误。

海明码(Hamming code)是一种可以进行错误检测和纠正的线性分组码,它可以通过添加冗余位来实现在传输过程中发生错误的位的纠正。

海明码在计算中利用了奇偶校验的原理,通过添加适当的奇偶位,可以实现对数据的错误检测和纠正。

海明码的计算过程相对复杂一些,但可以实现对数据的高效纠错。

CRC码和海明码在实际应用中有着各自的优缺点。

CRC码适用于高速传输和实时应用,它的计算速度快,但只能检测错误,并不能进行纠正。

而海明码可以进行错误检测和纠正,但计算复杂度较高,适用于传输速度较慢的场景。

在实际应用中,通常会根据具体的需求和场景来选择适合的错误检测和纠正技术。

在数据传输和存储领域,CRC码和海明码都有着广泛的应用。

在网络通信中,CRC码常用于以太网、Wi-Fi等高速传输中,用来验证数据的完整性。

而在存储系统中,海明码常用于磁盘和闪存等存储介质中,用来保证数据的可靠性和一致性。

这些应用场景都充分展现了CRC码和海明码在错误检测和纠正中的重要作用。

总的来说,CRC码和海明码都是常用的错误检测和纠正技术,它们在数据传输和存储中发挥着重要的作用。

虽然它们在计算复杂度、纠错能力等方面有所不同,但在实际应用中,可以根据具体的需求和场景来选择适合的技术。

通过合理的使用和结合,可以有效地保证数据的可靠传输和存储。

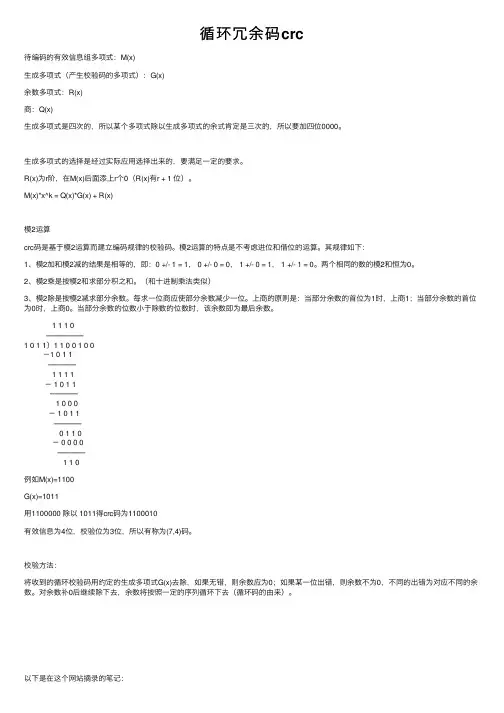

循环冗余码crc待编码的有效信息组多项式:M(x)⽣成多项式(产⽣校验码的多项式):G(x)余数多项式:R(x)商:Q(x)⽣成多项式是四次的,所以某个多项式除以⽣成多项式的余式肯定是三次的,所以要加四位0000。

⽣成多项式的选择是经过实际应⽤选择出来的,要满⾜⼀定的要求。

R(x)为r阶,在M(x)后⾯添上r个0(R(x)有r + 1 位)。

M(x)*x^k = Q(x)*G(x) + R(x)模2运算crc码是基于模2运算⽽建⽴编码规律的校验码。

模2运算的特点是不考虑进位和借位的运算。

其规律如下:1、模2加和模2减的结果是相等的,即:0 +/- 1 = 1, 0 +/- 0 = 0, 1 +/- 0 = 1, 1 +/- 1 = 0。

两个相同的数的模2和恒为0。

2、模2乘是按模2和求部分积之和。

(和⼗进制乘法类似)3、模2除是按模2减求部分余数。

每求⼀位商应使部分余数减少⼀位。

上商的原则是:当部分余数的⾸位为1时,上商1;当部分余数的⾸位为0时,上商0。

当部分余数的位数⼩于除数的位数时,该余数即为最后余数。

1 1 1 0────────1 0 1 1〕1 1 0 0 1 0 0-1 0 1 1──────1 1 1 1- 1 0 1 1──────1 0 0 0- 1 0 1 1──────0 1 1 0- 0 0 0 0──────1 1 0例如M(x)=1100G(x)=1011⽤1100000 除以 1011得crc码为1100010有效信息为4位,校验位为3位,所以有称为(7,4)码。

校验⽅法:将收到的循环校验码⽤约定的⽣成多项式G(x)去除,如果⽆错,则余数应为0;如果某⼀位出错,则余数不为0,不同的出错为对应不同的余数。

对余数补0后继续除下去,余数将按照⼀定的序列循环下去(循环码的由来)。

以下是在这个⽹站摘录的笔记:CRC校验码的编码⽅法是⽤待发送的⼆进制数据t(x)除以⽣成多项式g(x),将最后的余数作为CRC校验码。

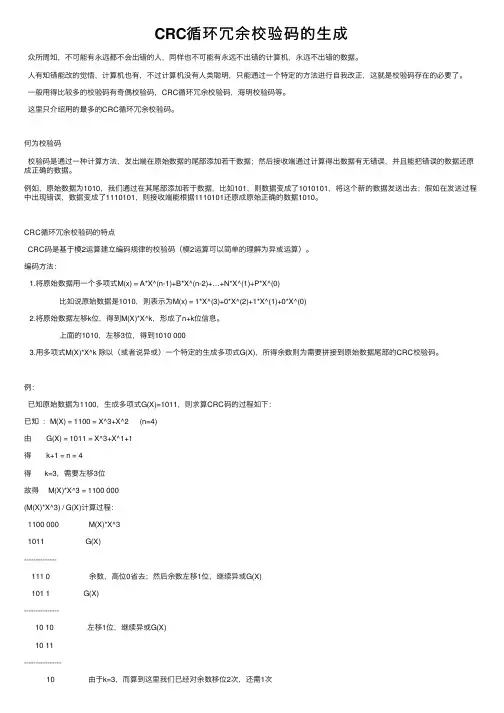

CRC循环冗余校验码的⽣成众所周知,不可能有永远都不会出错的⼈,同样也不可能有永远不出错的计算机,永远不出错的数据。

⼈有知错能改的觉悟,计算机也有,不过计算机没有⼈类聪明,只能通过⼀个特定的⽅法进⾏⾃我改正,这就是校验码存在的必要了。

⼀般⽤得⽐较多的校验码有奇偶校验码,CRC循环冗余校验码,海明校验码等。

这⾥只介绍⽤的最多的CRC循环冗余校验码。

何为校验码校验码是通过⼀种计算⽅法,发出端在原始数据的尾部添加若⼲数据;然后接收端通过计算得出数据有⽆错误,并且能把错误的数据还原成正确的数据。

例如,原始数据为1010,我们通过在其尾部添加若⼲数据,⽐如101,则数据变成了1010101,将这个新的数据发送出去;假如在发送过程中出现错误,数据变成了1110101,则接收端能根据1110101还原成原始正确的数据1010。

CRC循环冗余校验码的特点CRC码是基于模2运算建⽴编码规律的校验码(模2运算可以简单的理解为异或运算)。

编码⽅法:1.将原始数据⽤⼀个多项式M(x) = A*X^(n-1)+B*X^(n-2)+…+N*X^(1)+P*X^(0)⽐如说原始数据是1010,则表⽰为M(x) = 1*X^(3)+0*X^(2)+1*X^(1)+0*X^(0)2.将原始数据左移k位,得到M(X)*X^k,形成了n+k位信息。

上⾯的1010,左移3位,得到1010 0003.⽤多项式M(X)*X^k 除以(或者说异或)⼀个特定的⽣成多项式G(X),所得余数则为需要拼接到原始数据尾部的CRC校验码。

例:已知原始数据为1100,⽣成多项式G(X)=1011,则求算CRC码的过程如下:已知:M(X) = 1100 = X^3+X^2 (n=4)由 G(X) = 1011 = X^3+X^1+1得 k+1 = n = 4得 k=3,需要左移3位故得 M(X)*X^3 = 1100 000(M(X)*X^3) / G(X)计算过程:1100 000 M(X)*X^31011 G(X)--------------111 0 余数,⾼位0省去;然后余数左移1位,继续异或G(X)101 1 G(X)---------------10 10 左移1位,继续异或G(X)10 11----------------10 由于k=3,⽽算到这⾥我们已经对余数移位2次,还需1次则最后算出来的结果是010,则原始数据变成了1100 010,最后三位是CRC码。

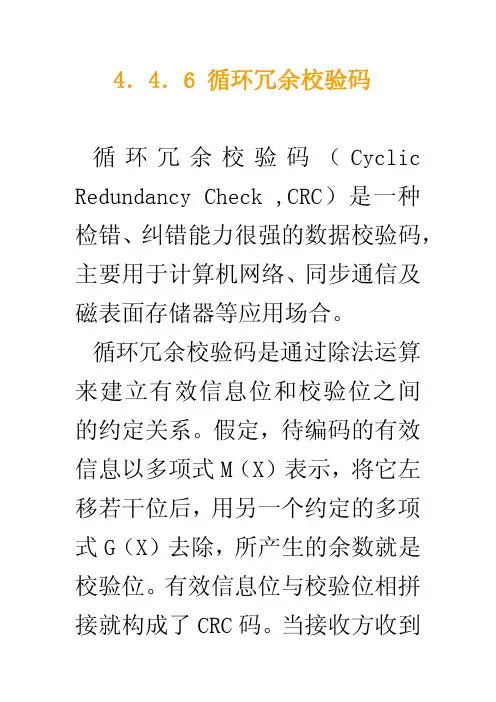

4.4.6 循环冗余校验码循环冗余校验码(Cyclic Redundancy Check ,CRC)是一种检错、纠错能力很强的数据校验码,主要用于计算机网络、同步通信及磁表面存储器等应用场合。

循环冗余校验码是通过除法运算来建立有效信息位和校验位之间的约定关系。

假定,待编码的有效信息以多项式M(X)表示,将它左移若干位后,用另一个约定的多项式G(X)去除,所产生的余数就是校验位。

有效信息位与校验位相拼接就构成了CRC码。

当接收方收到发来的CRC码后,他仍用约定的多项式G(X)去除,若余数为0,表明该代码接收无误;若余数不为0,表明某一位出错,再进一步由余数值确定出错的位置,并予以纠正。

1.循环冗余校验码的编码方法如图3-7所示,循环冗余校验码由两部分组成,左边为信息位,右边为校验位。

若信息位为N位,校验位为K位,则该校验码被称为(N +K,N)码。

循环冗余校验码的编码步骤如下:(1)将待编码的N位有效信息位表示为一个n-1阶的多项式M(X)。

(2)将M(X)左移K位,得到M (X)·X k(K由预选的K+1位的生成多项式G(X)决定)。

(3)用一个预选好的K+1位的生成多项式G(X)对M(X)·X k 作模2除法。

(4)把左移K位后的的有效信息位与余数作模2加法,即形成长度为N+K的CRC码。

M(X)·X k+R(X) =Q(X)·G(X) 这里,需介绍一下模2的运算规则。

模2运算不考虑加法的进位和减法的借位,即0±0=0,0±1=1,1±0=1,1±1=0。

作模2除法时,上商的原则是当部分余数首位是1时(即使被除数比除数小),商取1,反之商取0,然后按模2加减求得余数。

当被除数逐步除完时,最终的余数比除数少一位,此余数就是校验位。

例3.26:选择生成多项式为G(X)=X3+X+1,请把4位有效信息1100编码成CRC码。

Verilog语⾔实现并⾏(循环冗余码)CRC校验1 前⾔(1)什么是CRC校验?CRC即循环冗余校验码:是数据通信领域中最常⽤的⼀种查错校验码,其特征是信息字段和校验字段的长度可以任意选定。

循环冗余检查(CRC)是⼀种数据传输检错功能,对数据进⾏多项式计算,并将得到的结果附在帧的后⾯,接收设备也执⾏类似的算法,以保证数据传输的正确性和完整性。

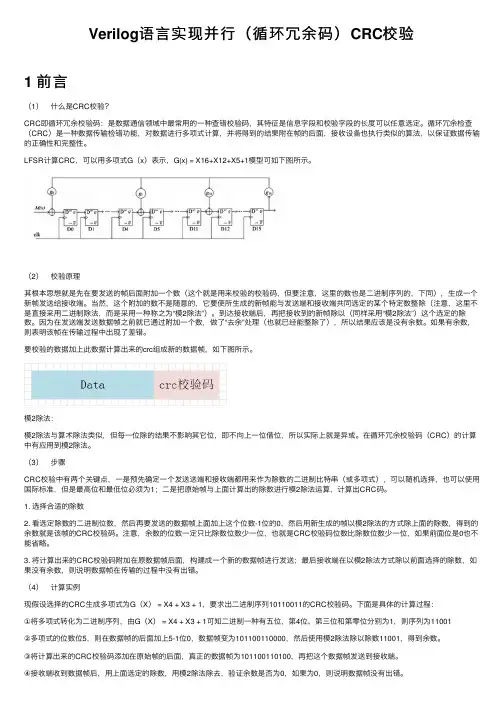

LFSR计算CRC,可以⽤多项式G(x)表⽰,G(x) = X16+X12+X5+1模型可如下图所⽰。

(2)校验原理其根本思想就是先在要发送的帧后⾯附加⼀个数(这个就是⽤来校验的校验码,但要注意,这⾥的数也是⼆进制序列的,下同),⽣成⼀个新帧发送给接收端。

当然,这个附加的数不是随意的,它要使所⽣成的新帧能与发送端和接收端共同选定的某个特定数整除(注意,这⾥不是直接采⽤⼆进制除法,⽽是采⽤⼀种称之为“模2除法”)。

到达接收端后,再把接收到的新帧除以(同样采⽤“模2除法”)这个选定的除数。

因为在发送端发送数据帧之前就已通过附加⼀个数,做了“去余”处理(也就已经能整除了),所以结果应该是没有余数。

如果有余数,则表明该帧在传输过程中出现了差错。

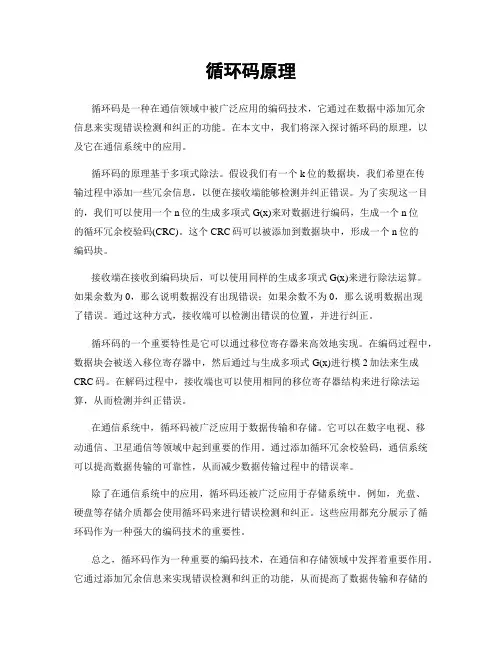

要校验的数据加上此数据计算出来的crc组成新的数据帧,如下图所⽰。

模2除法:模2除法与算术除法类似,但每⼀位除的结果不影响其它位,即不向上⼀位借位,所以实际上就是异或。

在循环冗余校验码(CRC)的计算中有应⽤到模2除法。

(3)步骤CRC校验中有两个关键点,⼀是预先确定⼀个发送送端和接收端都⽤来作为除数的⼆进制⽐特串(或多项式),可以随机选择,也可以使⽤国际标准,但是最⾼位和最低位必须为1;⼆是把原始帧与上⾯计算出的除数进⾏模2除法运算,计算出CRC码。

1. 选择合适的除数2. 看选定除数的⼆进制位数,然后再要发送的数据帧上⾯加上这个位数-1位的0,然后⽤新⽣成的帧以模2除法的⽅式除上⾯的除数,得到的余数就是该帧的CRC校验码。

循环码原理循环码是一种在通信领域中被广泛应用的编码技术,它通过在数据中添加冗余信息来实现错误检测和纠正的功能。

在本文中,我们将深入探讨循环码的原理,以及它在通信系统中的应用。

循环码的原理基于多项式除法。

假设我们有一个k位的数据块,我们希望在传输过程中添加一些冗余信息,以便在接收端能够检测并纠正错误。

为了实现这一目的,我们可以使用一个n位的生成多项式G(x)来对数据进行编码,生成一个n位的循环冗余校验码(CRC)。

这个CRC码可以被添加到数据块中,形成一个n位的编码块。

接收端在接收到编码块后,可以使用同样的生成多项式G(x)来进行除法运算。

如果余数为0,那么说明数据没有出现错误;如果余数不为0,那么说明数据出现了错误。

通过这种方式,接收端可以检测出错误的位置,并进行纠正。

循环码的一个重要特性是它可以通过移位寄存器来高效地实现。

在编码过程中,数据块会被送入移位寄存器中,然后通过与生成多项式G(x)进行模2加法来生成CRC码。

在解码过程中,接收端也可以使用相同的移位寄存器结构来进行除法运算,从而检测并纠正错误。

在通信系统中,循环码被广泛应用于数据传输和存储。

它可以在数字电视、移动通信、卫星通信等领域中起到重要的作用。

通过添加循环冗余校验码,通信系统可以提高数据传输的可靠性,从而减少数据传输过程中的错误率。

除了在通信系统中的应用,循环码还被广泛应用于存储系统中。

例如,光盘、硬盘等存储介质都会使用循环码来进行错误检测和纠正。

这些应用都充分展示了循环码作为一种强大的编码技术的重要性。

总之,循环码作为一种重要的编码技术,在通信和存储领域中发挥着重要作用。

它通过添加冗余信息来实现错误检测和纠正的功能,从而提高了数据传输和存储的可靠性。

希望本文对循环码的原理有所了解,并对其在通信系统中的应用有更深入的认识。

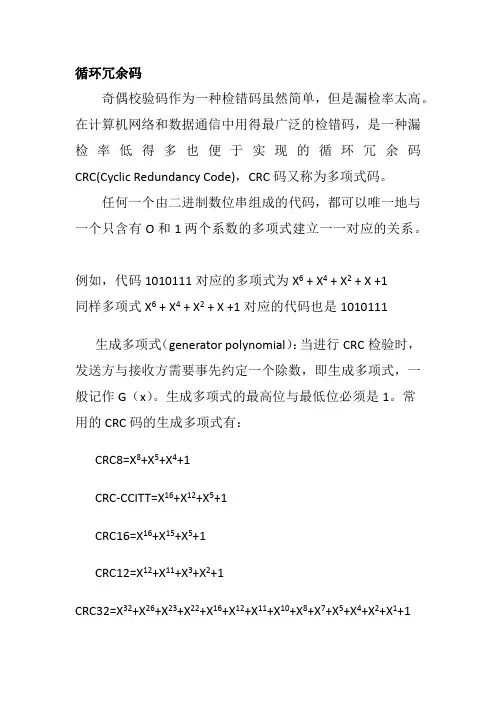

循环冗余码奇偶校验码作为一种检错码虽然简单,但是漏检率太高。

在计算机网络和数据通信中用得最广泛的检错码,是一种漏检率低得多也便于实现的循环冗余码CRC(Cyclic Redundancy Code),CRC码又称为多项式码。

任何一个由二进制数位串组成的代码,都可以唯一地与一个只含有O和1两个系数的多项式建立一一对应的关系。

例如,代码1010111对应的多项式为X6 + X4 + X2 + X +1同样多项式X6 + X4 + X2 + X +1对应的代码也是1010111 生成多项式(generator polynomial):当进行CRC检验时,发送方与接收方需要事先约定一个除数,即生成多项式,一般记作G(x)。

生成多项式的最高位与最低位必须是1。

常用的CRC码的生成多项式有:CRC8=X8+X5+X4+1CRC-CCITT=X16+X12+X5+1CRC16=X16+X15+X5+1CRC12=X12+X11+X3+X2+1CRC32=X32+X26+X23+X22+X16+X12+X11+X10+X8+X7+X5+X4+X2+X1+1计算示例设需要发送的信息为M = 1010001101,产生多项式对应的代码为P = 110101,R=5。

在M后加5个0,然后对P做模2除法运算,得余数r(x)对应的代码:01110。

故实际需要发送的数据是101000110101110。

错误检测当接收方收到数据后,用收到的数据对P(事先约定的)进行模2除法,若余数为0,则认为数据传输无差错;若余数不为0,则认为数据传输出现了错误,由于不知道错误发生在什么地方,因而不能进行自动纠正,一般的做法是丢弃接收的数据。

几点说明:1、CRC是一种常用的检错码,并不能用于自动纠错。

2、只要经过严格的挑选,并使用位数足够多的除数 P,那么出现检测不到的差错的概率就很小很小。

3、仅用循环冗余检验 CRC 差错检测技术只能做到无差错接受(只是非常近似的认为是无差错的),并不能保证可靠传输。

循环冗余编码

循环冗余编码(CRC,Cyclic Redundancy Check)是一种广泛用于数据传输和存储的错误检测方法。

它的基本思想是在数据中添加额外的校验位,以确保接收方可以验证数据的完整性。

CRC编码通常由生成多项式来表示,它定义了数据在传输或存储之前需要添加的校验位。

在发送方,数据被除以生成多项式,并保留余数作为校验位。

在接收方,数据被再次除以生成多项式,并检查是否与发送方的余数相同。

如果不同,则表示数据在传输或存储过程中发生了错误。

CRC编码具有简单、高效和广泛应用的优点。

它可以在各种通信协议和存储设备中使用,例如以太网、USB、硬盘驱动器等。

此外,CRC编码还可以与其他错误检测方法结合使用,以提供更高级别的数据完整性保护。

需要注意的是,CRC编码并不是完美的错误检测方法,它可能会在某些情况下发生误报或漏报。

因此,在使用CRC编码时,需要根据具体的应用场景和需求进行选择和调整。

循环冗余码crc校验方法原理CRC校验方法通过对待传输的数据进行计算,生成一组校验码,然后将校验码与数据一起传输。

接收方在收到数据后再次进行计算,如果接收到的校验码与计算得到的校验码一致,就表示数据传输过程中没有出错。

CRC校验是一种循环多项式计算方法。

具体原理如下:1. 定义一个产生多项式G,它是一个比特序列。

这个多项式进行无符号二进制数运算,通常写成如28-bit、32-bit等形式。

G为CRC生成多项式,与被校验数据的位数相关。

2.将待传输的数据D看做一个多项式,记为M(x),其中x为一个变量。

M(x)的次数不大于G的次数(G的次数等于M(x)的位数减去1)。

3.引入冗余位R,即是生成的校验码,也是一个比特序列。

R(x)的次数不大于G的次数。

4.计算M(x)乘以x的幂次后除以G,这个操作表示对M(x)进行长除法操作,最后得到商Q(x)和余数R(x)。

Q(x)表示M(x)与G的长除法过程中的商。

5.将R(x)作为冗余位添加到M(x)的低位,形成一个新的数M'(x)。

6.M'(x)除以G,得到R'(x)。

R`(x)通常是0,如果不为0,就表示传输过程中发生了错误。

7.将R'(x)作为校验码发送给接收方,接收方在收到数据后重复以上操作计算出的R’(x)与接收到的R'(x)进行比较。

如果在计算过程中R(x)和R'(x)相等,就表示数据没有出错。

如果不相等,则说明在数据传输过程中发生了错误。

接收方可以通过比较R(x)和R'(x)的差异来确定出错的位置,并进行识别和纠错。

CRC校验方法的优点在于简单、高效。

由于CRC码是通过位运算,可以通过硬件电路或者软件算法来实现,具有较高的速度和性能。

此外,CRC码还具有较好的错误检测能力,能够检测出多位、批量错误。

总的来说,CRC校验方法利用多项式的除法原理,在待传输的数据上附加一组冗余位校验码,接收方通过对数据进行相同的计算,可以判断数据传输是否出错,并进行错误检测和纠正。

CRC循环冗余码的计算三、循环冗余码(CRC)1.CRC的工作方法在发送端产生一个循环冗余码,附加在信息位后面一起发送到接收端,接收端收到的信息按发送端形成循环冗余码同样的算法进行校验,若有错,需重发。

2.循环冗余码的产生与码字正确性检验例子。

例1.已知:信息码:110011 信息多项式:K(X)=X^5+X^4+X+1生成码:11001 生成多项式:G(X)=X^4+X^3+1 (r=4)求:循环冗余码和码字。

解:1)(X5+X4+X+1)*X4的积是 X9+X8+X5+X4 对应的码是1100110000。

或者 G(X)的模是4,所以在信息码的后面加4个0得11001100002)积/G(X)(按模二算法)。

由计算结果知冗余码是1001,码字就是1100111001。

__________1 0 0 0 0 1←Q(X)G(x)→1 1 0 0 1)1 1 0 0 1 1 0 0 0 0←F(X)*Xr1 1 0 0 1 ,1 0 0 0 01 1 0 0 11 0 0 1←R(X)(冗余码)例2.已知:接收码字: 1100111001 多项式:T(X)=X^9+X^8+X^5+X^4+X^3+1生成码: 11001 生成多项式:G(X)=X^4+X^3+1 (r=4)求:码字的正确性。

若正确,则指出冗余码和信息码。

解:1)用接收码字除以生成码,余数为0,所以码字正确。

1 0 0 0 0 1←Q(X)1 1 0 0 1 )1 1 0 0 1 1 1 0 0 1←F(X)*Xr+R(x)G(x) 1 1 0 0 1 ,1 1 0 0 11 1 0 0 10←S(X)(余数)2)因r=4,所以冗余码是:1001,信息码是:110011四、海明码●对于16位的数据,需要(47)个校验位才能构成海明码。

在某个海明码的排列方式D9D8D7D6D5D4P4D3D2D1P3D0P2P1中,其中D i(0≤i≤9)表示数据位,P j(1≤j≤4)表示校验位,数据位D8由 (48) 进行校验。

CRC16计算方法CRC16是一种循环冗余校验码,用于数据传输的错误检测。

它通过生成一个16位的校验码,对传输的数据进行校验,以判断是否发生了传输错误。

CRC16计算方法是一种快速而可靠的校验方法,被广泛应用于各种通信协议和数据传输系统中。

生成多项式的选择:生成多项式是用来进行CRC计算的重要参数,不同的生成多项式会影响CRC的性能。

常用的生成多项式有多种,如CRC-16-CCITT、CRC-16-XMODEM等,它们的选择基于不同的应用需求和性能要求。

计算过程:1.初始化:首先,需要选择一个初始值,通常为0xFFFF或0x0000。

这个初始值在计算过程中会不断更新。

2.循环运算:循环运算是CRC16计算的关键步骤,它会对每个数据字节进行计算。

首先,将初始值与第一个数据字节进行异或运算。

然后,对每个数据字节进行8次循环运算。

循环运算的每一次都涉及到两个操作:左移和异或。

左移:将CRC寄存器的值左移1位。

异或:将CRC寄存器的最高位与下一个数据字节进行异或运算。

循环运算结束后,CRC寄存器中的值即为CRC16校验码。

3.结果反转:结果反转是为了将CRC16校验码按照数据传输的字节顺序进行反转。

反转后的校验码可以更好地与接收到的数据进行比对。

以上就是CRC16的计算方法。

当数据传输完成后,发送方会将数据和计算得到的CRC16校验码一起发送给接收方。

接收方通过对接收到的数据进行计算,得到一个接收方CRC16校验码。

接收方将发送方CRC16校验码与接收方CRC16校验码进行比对,如果两者相等,则数据传输没有发生错误。

如果两者不相等,则说明数据传输发生了错误,需要进行重传或其他差错处理。

EDA专用周实训报告课题:循环冗余校验编码(CRC)组员:指导老师:四川工程职业技术学院贰前言EDA (电子设计自动化)技术是现代电子工程领域的一门新技术,它提供了基于计算机和信息技术的电路系统设计方法。

EDA 技术的发展和推广应用极大地推动了电子工业的发展。

随着EDA 技术的发展,硬件电子电路的设计几乎可以完全依靠计算机来完成,这样就大大缩短了硬件电子电路设计的周期,从而使制造商可以快速开发出品种多、批量小的产品,以满足市场的需求。

EDA 教学和产业界的技术推广时当今世界的一个技术热点,EDA 技术是现代电子行 业中不可缺少的一项技术。

CRC (Cyclic Redundancy Check)循环冗余校验码是常用的校验码,在早期的通信中运用广泛,因为早期的通信技术不够可靠(不可靠性的来源是通信技术决定的,比如电磁波通信时受雷电等因素的影响),不可靠的通信就会带来‘确认信息’的困惑,对通信的可靠性检查就需要‘校验’,校验是从数据本身进行检查,它依靠某种数学上约定的形式进行检查,校验的结果是可靠或不可靠,如果可靠就对数据进行处理,如果不可靠,就丢弃重发或者进行修复。

通信技术叁目录一:实验目的 .................................................................................. 肆 二:实验内容 .................................................................................. 肆 三:实验步骤 .................................................................................. 肆 四:实验原理 .................................................................................. 伍 1.CRC 校验码介绍 ................................................................ 伍 2. 硬件电路的实现方法 ........................................................... 陆 五:程序设计………………………………………………………7 六:专用周总结 ...................................................................... 壹拾贰四川工程职业技术学院肆一:实验目的1:学习CRC 编码基本流程, 学会调试循环冗余校验码编码程序。

通信系统课程设计报告 课题名称 (24,16)CRC循环码编解码器的设计 学生姓名 杨阳 班 级 08通信2W 学 号 08313225 指导教师 程钦 任艳玲 设计地点 60#507

2011年 11 月 18 日 2

目 录 序言„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„3

第1章 课程设计要求及平台„„„„„„„„„„„„„„„„„„„„„„„4

1.1 课程设计要求和目的„„„„„„„„„„„„„„„„„„„„„„„„„„4 1.2 课程设计内容„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„4 1.3 个人在设计中的分工………………………………………………………„„4 1.4 课程设计平台………………………………………………………„………4 第2章 QUARTUSⅡ简介„„„„„„„„„„„„„„„„„„„„„„„„„„5

2.1 VHDL语言的优点………………………………………………………………5 2.2 VHDL语言的基本结构„„„„„„„„„„„„„„„„„„„„„5 2.2.1 实体(ENTITY)„„„„„„„„„„„„„„„„„„„„„„„„„„ 6 2.2.2 结构体(ARCHITECTURE)„„„„„„„„„„„„„„„„„„„„„„7 第3章 编解码器设计及仿真结果分析„„„„„„„„„„„„„„„„7

3.1编码器基本原理„„„„„„„„„„„„„„„„„„„„„„„„8 3.2编码器仿真及设计…………………………………………„„„„„„„8 3.3解码器基本原理…………………………………………„„„„„10 3.4 个人对译码原理的认识„„„„„„„„„„„„„„„„„„„„„„„„„11 3.5解码器仿真及设计……………………………………„„„„„„„„„13 第4章 心得与体会 „„„„„„„„„„„„„„„„„„„„„„„„„„ 18

参考文献„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„19

附录„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„„ 20 3

序言 CRC循环码是在严密的代数学理论基础上建立起来的,是线性分组码的一种。这种码的编码和解码设备都不太复杂,而且检错的能力较强。CRC循环码除具有线性码的一般性质之外,还具有循环性,即任一码组循环一位以后,仍为该码中的一个组码。 在代数编码理论中,为了便于计算,经常将循环码表示成码多项式的形式,设码组为 a= (an-1an-2...a1a0),则码多项式定义如下:T (X) =an-1x +an-2x +...+a1x+a0。 在循环码中除全 “ 0”码组外,再没有连续 k 位均为 “ 0”的码组,即连“0”的长度最多只有 (k-1) 位。否则,在经过若干次循环移位后将得到一个 k 位信息位全为“0”,但监督位不全为“0”的一个码组。因此,g (x) 必须是一个常数项不为“0”的 (n-k) 次多项式,而且这个 g (x) 还是这种 码中次数为 (n-k) 的唯一一个多项式。称这唯一的 (n-k) 次多项式g(x) 为码的生成多项式。一旦确定了 g (x),则整个 (n,k) 循环码就被确定了。由此,可以写出循环码的生成矩阵 G. 在本次计中,我使用的系统开发平台为 QuartusⅡ,在 QuartusⅡ上可以完成设计输入、元件适配、时序仿真和功能仿真、编程下载整个流程,它提供了一种与结构无关的设计环境,是设计者能方便地进行设计输入、快速处理和器件编程。 4

第1章 课程设计要求及平台 1.1课程设计目的和要求 目的:通信原理课程设计的目的是为了使学生加深对所学的通信原理知识的理解,培养学生的专业素质,提高其利用通信原理知识处理通信系统问题的能力,为今后专业课程的学习,毕业设计和工作打下良好的基础。 要求:拿到题目后首先根据通信原理的框图进行建模,然后在微机上进行设计和软件彷真。按题目要求的功能进行设计,电路各个组成部分须有设计说明;采用原理图或 VHDL 语言输入法,在微机上进行编译和软件仿真。

1.2课程设计内容 (24,16)CRC 循环码编解码器设计(2 人合作) 1、采用原理图输入法。 2、根据 CRC 循环码的编解码原理,确定编解码器具体设计方案。 3、设计(24,16)CRC 循环码编解码器电路图。

1.3 个人在设计中的分工

本次课程设计我和同组者所要完成的任务是(24,16)CRC 循环码编解码器

设计;我们进行了分工合作,同组者做的是编码,我所要完成的是解码部分的设计。

1.4 课程设计平台 本次课程设计应用的软件是QuartusⅡ。 5

第2章 QUARTUSⅡ简介

2.1 VHDL语言的优点 传统的硬件电路设计方法是采用自下而上的设计方法,即根据系统对硬件的要求,详细编制技术规格书,并画出系统控制流图;然后根据技术规格书和系统控制流图,对系统的功能进行细化,合理地划分功能模块,并画出系统的功能框图;接着就进行各功能模块的细化和电路设计;为了提高开发的效率,增加已有开发成果的可继承性以及缩短开发周期,各ASIC研制和生产厂家相继开发了具有自己特色的电路硬件描述语言(Hardware Description Language,简称HDL)。于是,美国于1981年提出了一种新的、标准化的HDL,称之为VHSIC(Very High Speed Integrated Circuit) Hardware Description Language,简称VHDL。这是一种用形式化方法来描述数字电路和设计数字逻辑系统的语言。设计者可以利用这种语言来描述自己的设计思想,然后利用电子设计自动化工具进行仿真,再自动综合到门级电路,最后用PLD实现其功能。 综合起来讲,VHDL语言具有如下优点: 1. 覆盖面广,描述能力强,是一个多层次的硬件描述语言。具有良好的可读性,即容易被计算机接受,也容易被读者理解。 2. 使用期长,不会因工艺变化而使描述过时。因为VHDL的硬件描述与工艺无关,当工艺改变时,只需修改相应程序中的属性参数即可。 3. 支持大规模设计的分解和已有设计再利用。一个大规模的设计不可能由一个人独立完成,必须由多人共同承担,VHDL为设计的分解和设计的再利用提供了有力的支持。

2.2 VHDL语言的基本结构 一个完整的VHDL语言程序通常包含实体(Entity)、构造体(Architecture)、配置(Configuration)、程序包(Package)和库(Library)5个部分。前4个部分是可 分别编译的源设计单元。实体用于描述所设计的系统的外接口信号;构造体用于描述系统内部的结构和行为;程序包存放各种设计模块都能共享的数据类型、常数和子程序等; 6

配置用于从库中选取所需单元来组成系统设计的不同版本;库存放已经编译的实体、构造体、程序包和配置。

2.2.1 实体(ENTITY) 在VHDL中,实体类似于原理图中的一个部件符号,它可以代表整个系统、1块电路板、一个芯片或一个门电路,是一个初级设计单元。在实体中,我们可以定义设计单元的输入输出引脚和器件的参数,其具体的格式如下: ENTITY 实体名 IS [ 类属参数说明;] [ 端口说明;] END 实体名; 1) 类属参数说明 类属参数说明为设计实体和其外部环境的静态信息提供通道,特别是用来规定端口的大小、实体中子元件的数目、实体的定时特性等等。 2) 端口说明 端口说明为设计实体和其外部环境的动态通信提供通道,是对基本设计实体与外部接口的描述,即对外部引脚信号的名称、数据类型、和输入输出方向的描述。其一般格式如下: PORT(端口名 :方向 数据类型; ∶ 端口名 :方向 数据类型); 端口名是赋予每个外部引脚的名称;端口方向用来定义外部引脚的信号方向是输入 还是输出;数据类型说明流过该端口的数据类型。 3) 数据类型 VHDL语言中的数据类型有多种,但在数字电路的设计中经常用到的只有两种,即BIT和BIT_VECTOR(分别等同于STD_LOGIC和STD_LOGIC_VECTOR)。当端口被说明为BIT时,该端口的信号取值只能是二进制数“1”和“0”,即位逻辑数据类型;而当端口被说明为BIT_VECTOR时,该端口的信号是一组二进制的位值,即多位二进制数。 7

2.2.2 结构体(ARCHITECTURE) 结构体描述一个设计的结构或行为,把一个设计的输入和输出之间的关系建立起来。一个设计实体可以有多个结构体,每个结构体对应着实体不同的实现方案,各个结构的地位是同等的。 结构体对其基本设计单元的输入输出关系可以用三种方式进行描述,即行为描述、寄存器传输描述和结构描述。不同的描述方式,只是体现在描述语句的不同上,而结构体的结构是完全一样的。 结构体分为两部分:结构说明部分和结构语句部分,其具体的描述格式为: ARCHITECTURE 结构体名 OF 实体名 IS --说明语句 BEGIN --并行语句 END 结构体名;