突发模式收发器芯片组的设计

https://www.doczj.com/doc/f7247394.html,/networks/ 2006年05月16日15:49 来源:光纤

新闻网作者:李维中刘文涛

【文章摘要】本文涉及与突发模式收发器相关的突发模式跨阻放大器、突发模式限幅放大器和突发模式激光二极管驱动器(BM-TIA、BM-LA和BM-LDD)的电路原理和特点。

一、前言

由于新型宽带应用和需求的增多,发展迅速,带宽逐渐成为制约DSL用户宽带网性能的关键。采用PON(无源光网络)可以解决此关键。它具有高带宽及网络协议透明的特点,是一种点对多点的光纤传输和接入技术。已成为处理光通信控制中心的(Central Office)连接到最终用户的最后里程(the Last Mile)的首选方案。

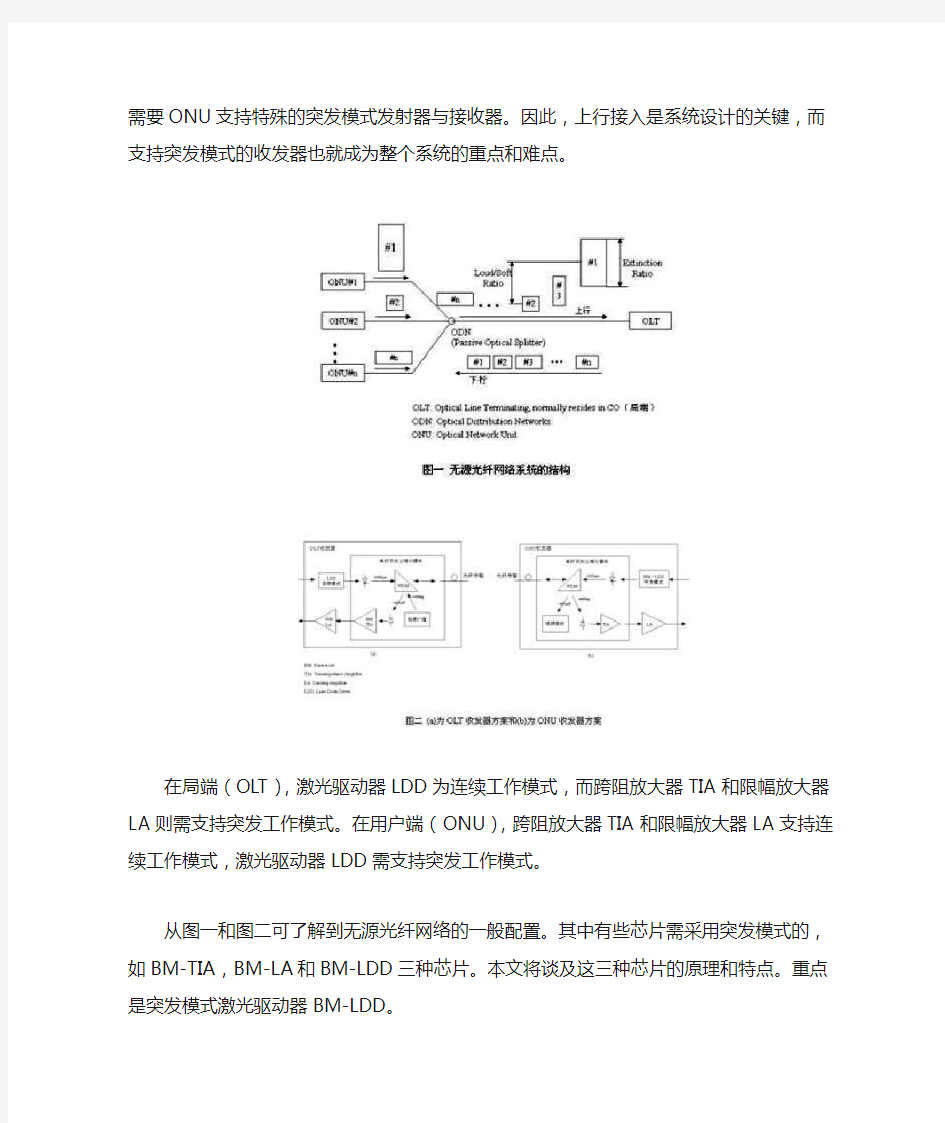

从图一,无源光纤网络系统的结构可看出,局端(OLT)与用户端(ONU)之间只有光纤,光分路器(Splitters)等无源器件。节省了光纤资源,无需有源器件和设备,可有效降低网络成本。同时,因为结构简单,大大节省运营维护成本。

目前无源光网络(PON)已成为光纤到户FTTH(Fiber to the home)主要的网络结构。系统从OLT到ONU为下行方向。下行通信时用TDM模式把所有的数据包汇成一个数据流,通过光纤采用广播方式传送。在接收端,用户以适当的地址选择获得其所需的数据包。上行通信(从ONU到OLT)是相当困难的,因为多个用户都用同样的光纤进行传送。在任何时刻只允许一个用户能传送数据包到OLT。TDMA协议可用来保证上述的条件。也就是要求ONU在没有传送信号时处于关断状态,而在传送信号时要很快打开,这就时需要ONU支持特殊的突发模式发射器与接收器。因此,上行接入是系统设计的关键,而支持突发模式的收发器也就成为整个系统的重点和难点。

在局端(OLT),激光驱动器LDD为连续工作模式,而跨阻放大器TIA和限幅放大器LA 则需支持突发工作模式。在用户端(ONU),跨阻放大器TIA和限幅放大器LA支持连续工作模式,激光驱动器LDD需支持突发工作模式。

从图一和图二可了解到无源光纤网络的一般配置。其中有些芯片需采用突发模式的,如BM-TIA,BM-LA和BM-LDD三种芯片。本文将谈及这三种芯片的原理和特点。重点是突发模式激光驱动器BM-LDD。

以下主要讲述突发模式跨阻放大器(BM-TIA)、突发模式限幅放大器(BM-LA)和突发模式激光驱动器(BM-LDD)与连续工作模式激光驱动器的主要差别。

二、突发模式TIA与突发模式LA

1. 突发模式TIA和一般TIA的主要差别在于:它必须应对没有直流分量的输入信号(要直流耦合)而且突发间的输出幅度变化要求大于30dB。有关输出基准偏移电压(output offset voltage)的问题可以留着待处理其后的BM-LA时再一起解决。也可以用以下所示的图三偏移检测电路来解决。

偏移控制:偏移控制电路能逐个地去除突发的输出偏移的机理是,在每次突发到来之前就把偏移(offset)调整好了。这种电路也称为“自适阈控制电路”(Adaptive Threshold control circuit)。

此电路是如何消除输出偏移电压的?现在我们先不管电流源IOS,当突发信息到来之前,峰值检测器被复位到放大器的两个输出端都输出共模电压。此时差分输出电压为0V。然后,突发的第一位“1”到达, VOP上升而VON下降。Vop的峰值存贮在峰值检测器内并反馈到放大器的输入端。当下一个“0”位到达时,峰值检测器的电压值会出现在VON输出端。因为RF’上没有电压降(没有输入电流),没有电压跨接在放大器输入端上,而且也没有跨接在RF的电压降(没有光电流)。因此,二个输出信号的峰值是相等的即输出偏移(output offset)就消除了。这种突发模式TIA的差分跨阻大约为2·RF。

啁啾控制(Chatter control):对BMTIA,除了偏移控制以外,还有另一个麻烦。即突发之间的间隔时间太长,长时间没有接收到突发光信号,也就TIA的峰值检测器复位时间维持太长,那么放大器的噪声会与输出信号交迭而产生序列随机码,被称之为啁啾。

有一个办法可以解决这个问题,就是人为的利用电流源IOS引进小的偏移电压,见图三中的虚线部分。此偏置电压必须经大于峰值噪声电压以控制啁啾,但也不能太大,否则会降低灵敏度。

2. 突发模式LA和连续模式LA有什么差别?图四(a)示出单边连续模式LA,其输入信号通过交流耦合网络。数据信号被AC耦合网络的平均直流削波。因为连续模式信号是DC 平衡的,其平均值相应于在眼图的垂直中心。假如我们用AC耦合来处理突发模式信号,如图四(b)所示的那样,其削波水平依旧是在信号的平均电平之上,但现在的眼图垂直中心部分会出现许多误码、脉宽畸变以及一些不合需要的后果。

在突发模式接收器的TIA和LA(也可包括CDR)必须是DC耦合,而且这些器件所产生的各种各样的偏移电压也必须是可控制的。就前面所述的BMTIA而言,如果由LA而产生的偏移不大的话则无需另加偏移控制电路。相反地,如果TIA没有偏移控制或是单端输出的话,那么LA就必须具有完成偏移控制的功能。

图五示出一种具有削波控制的单端输出的LA。图中符号VSL代表削波的电平

(Slice-level,可理解为单端输出信号的平均直流)。采用一种脉冲峰与谷检测器来分别地确定输入信号的最大值和最小值。其平均值由与之相匹配的电阻R和R’获得,并作为削波电平VSL。此电路总是在垂直眼图的中心削波输入数据信号与输入数据信号的平均值无关。为了准确地获取每次突发数据信号的脉冲幅度,此峰/谷检测器在每次突发间隔期间必须进行复位。必须牢记,在突发模式系统中,从一次突发到下一次突发,信号幅度发生很大变化情况是常见的。

如图一中所示的Loud/Soft Ratio(响/静比)较大。

三、突发模式激光驱动器

激光驱动器有两种工作模式:连续模式激光驱动器,缩写为LDD;突发模式激光驱动器,缩写为BM-LDD。以下均采用缩写。所谓突发就是突然瞬间发送一批数据信息,发完就停,且停发时间可长可短,带有随机性。BM-LDD和LDD的主要差别在于:

(1) BM-LDD要求突发与停止突发期间具有很高的消光比。

(2) BM-LDD的自动功率控制(APC)具有保持功能,能确保正确地传送突发的数据信号。

1、突发之间的消光比

突发模式发射器通常是用于多用户的网络。故要求在突发间隔期间不应有的光输出(干扰光)很低。例如,在PON系统中有32个用户,某一家的光数据信号输出在共用的传媒中就会受到其余31家干扰光输出的“污染”。这些背景光会减小光输出的消光比。一般情况下,对BMLDD而言,其突发之间的消光比应大于30dB。对突发期间内的消光比~10dB,和连续模式的LDD发射器的相似。

为达到如此之高的消光比,在二次突发之间激光器的偏流应尽可能地低(即工作点选择在刚好低于激光器阈值电流一点点)或者是零。在一旦突发发射时,偏流可以很快地增加上去,以减少导通延迟和抖动。此外,BMLDD为了在其它任何一家用户的下一次突发发射开始之前达到30dB的消光比往往在其激光二极管旁并联一个晶体管用来在突发发射结束时很快的去掉载流子(变暗)。

2、自动功率控制

为了满足突发工作模式,突发模式激光驱动器BM-LDD采用了具有保持功能的自动功率控制电路(APC)。给自动功率控制电路可以保持上一个突发时序的自动功率控制电路的直流偏置值,这样在下一个突发序列出现时,可以较快的建立一个稳定的APC回路。以下三种方式可应用于突发模式APC。

(1). 采用峰值检测器

如图六所示,从功率监控光电二极管来的电流经宽带TIA转换为电压,然后峰值检测器检测出与发射功率相对应的峰值。激光输出功率可调节直到峰值输出电压等于参考电压VREF为止。

然而,图六的方法存在着些缺点:1)当长时间没有突发发射时,在下一个突发到来之前,模拟峰值检测器的输出会偏离实际上的峰值,会引起输出功率出现差错。2)运行在高速码率时,需要用快速的光二极管。3)运行在高速码率时,TIA和峰值检测器的功率消耗是相当突出的。

(2)用一种积分与放电的电路和数字存储器来实现的突发模式APC。

这种APC可以克服上述的缺点,示于图七。功率水平被贮存在数字可上升/下降的计数器内,计数器所存的计数是不会随时间变化的。在电源开通时,它能保持住精确的功率水平。因此,在突发开始时输出功率的误差就可避免掉。在突发期间,可用“突发时钟”信号来增加或减小其功率水平。计数的增减可由上升/下降信号“u/d”来决定。产生的方法如下:在突发开始之前,电容器C(节点X)由复位开关SR放电简单的放一下电。在突发发射期间,光电二极管电流iPD(t)给电容器C充电(积分),而想要的峰值电流IREF由发射数据通过开关SD来调制而产生iREF(t),即对同样的电容器C进行放电的放电电流。当突发发射结束的那一刻,电容器被充电产生的电压如下:

其中,IPD是光电二极管电流的峰值,突发期间内1的数目(number of ones),B是码率(bit rate)。比较器将此电压与OV(复位电压)进行比较。从上述公式可见这比较的结果只受IPD-IREF影响而与C、B和n1无关。如果这个差值是正的,计数器的计数逐步减小,如果是负的,则计数器的计数就逐渐增加。

(3)采用数字功率控制器APC

从上述的第二种方法可看到其精确控制功率的技术是和数字化的计数器存贮相关的。已涉及点数字技术。数字控制APC确实是好办法,以市场上可获得的BM-LDD为例作些说明,它还可以通过对Enable和Disable功能管脚的设置来实现非突发模式(连续模式),以增加芯片的兼容性和节省功耗。

BM-LDD应具有三个主要部件,高速调制器、高速偏置驱动器和数字自动功率控制的激光偏置方块。器件功能示于图八。数字APC回路可自动补偿因环境温度和激光器寿命而引起的激光阈值电流的变化。数字APC由DAC(数字模拟变换)、DSP(数字信号处理)和ASP (模拟信号处理)三个部分组成。每当电源关断时,数字APC环路就复位。当电源再开通时,APC环路就自行完成初始化。初始化的时间一般为2.1-3.72μs与不同的设置状态有关。

数字APC的突发模式激光驱动器BM-LDD可应用于:FTTx宽带通信系统,无源网络(PON)发射器,APON、EPON和GPON上行发射器。

(4). 某些连续模式的LDD经适当的外围电路修改后加上快速模拟开关可用作为突发模式。(对突发模式应用,激光驱动器与激光二极管必须采用DC耦合)

四、小结

突发模式的特点就是其突发性,二次突发之间的时间间隔可长可短,而且突发还带有随机性。因此要求TIA、LA、LDD及CDR进入正常工作状态和结束工作状态的过程要快。它和连续模式有很大的不同,因为两者所采用APC方式不同,连续模式基本上就是个积分电路反馈,所以反应很慢。而突发模式采用的是脉冲峰值电平检测的办法,也有采用峰谷电平检测的办法。有的电路还采用了峰值和峰谷都检测的办法来实现突发模式电路。应达到如下的要求:

①高的Loud/soft ratio>30dB。②快速地响应数据包的首位信号。也就是要求减小其Turn-On和Turn-Off的时间。从毫秒减小到数十毫微秒。可用本文所提到的方法来实现。对突发模式接收器则要求有很高的灵敏度,可接受超低消光比的信号,灵敏度<-30dBm。

FPGA串行通用异步收发器设计 实验目的:1、掌握QuartusII6.0等EDA工具软件的基本使用; 2、熟悉VHDL硬件描述语言编程及其调试方法; 3、学习用FPGA实现接口电路设计。 实验内容: 本实验目标是利用FPGA逻辑资源,编程设计实现一个串行通用异步收发器。实验环境为EDA实验箱。电路设计采用VHDL硬件描述语言编程实现,开发软件为QuartusII6.0。 1、UART简介 UART(Universal Asynchronous Receiver Transmitter通用异步收发器)是一种应用广泛的短距离串行传输接口。常常用于短距离、低速、低成本的通讯中。8250、8251、NS16450等芯片都是常见的UART器件。 基本的UART通信只需要两条信号线(RXD、TXD)就可以完成数据的相互通信,接收与发送是全双工形式。TXD是UART发送端,为输出;RXD是UART接收端,为输入。 UART的基本特点是: (1)在信号线上共有两种状态,可分别用逻辑1(高电平)和逻辑0(低电平)来区分。在发送器空闲时,数据线应该保持在逻辑高电平状态。 (2)起始位(Start Bit):发送器是通过发送起始位而开始一个字符传送,起始位使数据线处于逻辑0状态,提示接受器数据传输即将开始。 (3)数据位(Data Bits):起始位之后就是传送数据位。数据位一般为8位一个字节的数据(也有6位、7位的情况),低位(LSB)在前,高位(MSB)在后。 (4)校验位(parity Bit):可以认为是一个特殊的数据位。校验位一般用来判断接收的数据位有无错误,一般是奇偶校验。在使用中,该位常常取消。 (5)停止位:停止位在最后,用以标志一个字符传送的结束,它对应于逻辑1状态。 (6)位时间:即每个位的时间宽度。起始位、数据位、校验位的位宽度是一致的,停止位有0.5位、1位、1.5位格式,一般为1位。 (7)帧:从起始位开始到停止位结束的时间间隔称之为一帧。 (8)波特率:UART的传送速率,用于说明数据传送的快慢。在串行通信中,数据是按位进行传送的,因此传送速率用每秒钟传送数据位的数目来表示,称之为波特率。如波特率9600=9600bps(位/秒)。 FPGA UART系统组成:如下图所示,FPGA UART由三个子模块组成:波特率发生器;接收模块;发送模块; 2、模块设计:

UART IP设计文档 1,主要特征; UART采用的是一种起止式异步协议,特点是一个字符一个字符地传输,并且传送一个字符总是以起始位开始,以停止位结束,字符之间没有固定的时间间隔要求。一个字符传送完成后,奇偶校验位之后的停止位和空闲位都规定为高电平,而起始位为低电平,这样就保证起始位开始处一定有个下降沿,这个下降沿用来界定一个字符传输的开始,它的到来就表示下面是数据位,要准备接收;而停止位标志一个字符的结束,它的出现表示一个字符传送完毕,这样就为通信双方提供了何时开始收发和何时结束的标志。 2,整体框图 图2.1 UART IP整体框图 UART IP的整体框图如图2.1所示。它有控制电路模块、发送控制模块和接收控制模块三部分组成。CPU通过对控制电路模块中的寄存器进行设置达到对内部电路的控制和管理,从而实现UART和CPU以及其它UART模块间的数据收发功能。3,整个模块的外部接口 图3.1 UART IP外部接口 4,子模块说明 (一)控制电路模块 该模块的主要功能为:a、与CPU接口,将CPU对内部控制寄存器的写操作转化

为对发送控制器和接收控制器的控制信号;b、将CPU写入到内部数据发送寄存器的数据进行锁存并提供给发送控制器;c、将接收控制器接收的数据提交给CPU,同时提交接收数据的状态信息;d、对收、发控制器的中断进行管理。对于中断寄存器的读操作同时对寄存器清零,以避免重复产生中断,这需要专门的电路进行维护和管理。 (二)发送控制模块 该模块的主要功能为:a、根据clk_div_ctl给出的时钟分频比将xmt_data上的数据按照从低位到高位的顺序依次发出。在数据发送过程中需要根据规范插入起始位、奇偶校验位和停止位。b、发送控制器在xmt_en为高电平时开始向线路方向发送数据。完成当前字节发送后通过xmt_over通知控制电路当前发送完成,由控制电路负责产生中断和进行中断管理。 发送控制模块的仿真波形如下: 图4.1发送控制模块仿真波形 a.当发送状态机处于idle状态时,如果xmt _en有效则产生一个clk_cnt_clr 信号,用于对时钟计数器清零,同时进入start状态,见图4.1中“1”处。 b.在start状态下,如果sample有效则输出起始位,同时进入data状态,见图 4.1中“2”处。 c.在data状态下,在sample有效时连续输出8位数据。最后一个比特开始输出后进入parity状态,准备输出奇偶校验位,,见图4.1中“3”处。 d.在parity状态下,如果出现sample则进入stop状态,在stop状态下如果sample有效则输出截止位,并进入waiting状态,见图4.1中“4”处。 e.在waiting状态下,截止位保持有效,并在sample有效时进入idle状态,sdout 持续为1,见图4.1中“5”处。 f在由waiting进入idle状态时,输出xmt_over信号,通知控制电路当前数据发送完成。注意这里的xmt_over信号只是在一个时钟周期内保持有效,见图4.1中“6”处. (三)接收控制模块 该模块的主要功能为:a、检测接收数据中的起始位,并完整地接收数据。b、根

《物联网技术》课程设计 物联网在校园一卡通中的应用研究 摘要 随着计算机应用技术及互联网的飞速发展,在互联网的基础之上扩展和延伸并形成了新一代的网络技术—物联网(internet of things ,IOT )。近年来,物联网技术层出不穷,移动互联网也广泛被应用,云计算逐渐走进人们的生活,随之而来的教育信息化也逐步被推进。物联网牵手高校,会给高校信息化发展带来怎样的契机? 其实,物联网在高校校园中的应用早已初见端倪,早在2008年,台湾就开始利用物联网技术支持学校安全管理;在国内高校中,使用RFID技术却已十分广泛,校园一卡通早已普及。然而,高校校园中的物联网实际应用往往只停留在基本层面上,更深层次的应用还有待进一步探索。 关键词物联网/一卡通/校园一卡通/RFID

目录 摘要 (1) 目录 (2) 1物联网 (3) 1.1物联网的概念 (3) 1.2物联网的发展及前景 (3) 1.3物联网的原理 (5) 1.4物联网的开展 (6) 1.5物联网存在的问题 (6) 1.6物联网的技术在实际中的应用 (7) 2一卡通技术 (9) 2.1一卡通的分类 (11) 2.2一卡通系统 (11) 2.3一卡通系统技术体系结构 (12) 3校园一卡通 (14) 3.1校园一卡通概念 (15) 3.2校园一卡通的功能 (16) 3.3校园一卡通系统 (17) 3.4校园一卡通的应用 (19) 3.5校园一卡通的目标 (22) 致谢 (23) 参考文献 (23)

1物联网 随着计算机应用技术及互联网的飞速发展,在互联网的基础之上扩展和延伸并形成了新一代的网络技术—物联网(internet of things ,IOT )。物联网技术的和应用视为及计算机、互联网和移动通讯技术之后,计算机信息技术领域的有一次发展机遇,有着重大科学意义和应用价值。随着物联网技术的进步与广泛的应用,必将对本世纪人类的生产活动带来革命性的改革。 目前,世界上主要的发达国家都对物联网发展高度重视,特别在国际金融危机持续恶化,世界经济前景不明的情况下物联网技术被当做新的经济增长点,在国内外抛起了新一轮研究浪潮。包括美国、奥盟、日本等国家纷纷出台物联网发展计划,进行相关技术和产业布局。在我国温家宝总理在2009年视察无锡时提出尽快建立“感知中国”中心,并在2010年政府工作报告中明确将“加快物联网的研究应用”纳入重点产业。 据美国权威咨询机构弗雷斯特研究公司(Forrester Research)预测,到2020年,世界上务队伍互联的业务与人对人通讯的业务竟达到30比1,物联网常视为下一个万亿级的通讯业务。 1.1物联网的概念 物联网(The Internet of things)的定义是:通过射频识别(RFID)、红外感应器、全球定位系统、激光扫描器等信息传感设备,按约定的协议,把任何物品与互联网连接起来,进行信息交换和通讯,以实现智能化识别、定位、跟踪、监控和管理的一种网络。物联网的概念是在1999年提出的。物联网就是“物物相连的互联网”。这有两层意思:第一,物联网的核心和基础仍然是互联网,是在互联网基础上的延伸和扩展的网络;第二,其用户端延伸和扩展到了任何物品与物品之间,进行信息交换和通讯。 物联网的概念是在1999年提出的。1999年,在美国召开的移动计算和网络国际会议就提出,“传感网是下一个世纪人类面临的又一个发展机遇”。 1.2物联网的发展及前景

2.5 UART串口通信设计实例(1) 接下来用刚才采用的方法设计一个典型实例。在一般的嵌入式开发和FPGA设计中,串口UART是使用非常频繁的一种调试手段。下面我们将使用Verilog RTL编程设计一个串口收发模块。这个实例虽然简单,但是在后续的调试开发中,串口使用的次数比较多,这里阐明它的设计方案,不仅仅是为了讲解RTL编程,而且为了后续使用兼容ARM9内核实现嵌入式开发。 串口在一般的台式机上都会有。随着笔记本电脑的使用,一般会采用USB转串口的方案虚拟一个串口供笔记本使用。图2-7为UART串口的结构图。串口具有9个引脚,但是真正连接入FPGA开发板的一般只有两个引脚。这两个引脚是:发送引脚TxD和接收引脚RxD。由于是串行发送数据,因此如果开发板发送数据的话,则要通过TxD线1 bit接着1 bit 发送。在接收时,同样通过RxD引脚1 bit接着1 bit接收。 再看看串口发送/接收的数据格式(见图2-8)。在TxD或RxD这样的单线上,是从一个周期的低电平开始,以一个周期的高电平结束的。它中间包含8个周期的数据位和一个周期针对8位数据的奇偶校验位。每次传送一字节数据,它包含的8位是由低位开始传送,最后一位传送的是第7位。

这个设计有两个目的:一是从串口中接收数据,发送到输出端口。接收的时候是串行的,也就是一个接一个的;但是发送到输出端口时,我们希望是8位放在一起,成为并行状态(见图2-10)。我们知道,串口中出现信号,是没有先兆的。如果出现了串行数据,则如何通知到输出端口呢?我们引入“接收有效”端口。“接收有效”端口在一般情况下都是低电平,一旦有数据到来时,它就变成高电平。下一个模块在得知“接收有效”信号为高电平时,它就明白:新到了一个字节的数据,放在“接收字节”端口里面。

学号11700224 天津城建大学 EDA技术及应用 设计说明书 题目 串行数据收发器设计 起止日期:2014年12 月22日至2014年12 月26日 学生姓名杨棋焱 班级11电信2班 成绩 指导教师(签字) 计算机与信息工程学院 天津城建大学

课程设计任务书 2012 —2013 学年第1 学期 电子与信息工程系电子信息工程专业 课程设计名称:EDA技术及应用 设计题目:串行数据收发器设计 完成期限:自2014 年12月22 日至2014 年12 月26 日共 1 周 一.课程设计依据 在掌握常用数字电路原理和技术的基础上,利用EDA技术和硬件描述语言,EDA开发软件(Quartus Ⅱ)和硬件开发平台(达盛试验箱CycloneⅡFPGA)进行初步数字系统设计。 二.课程设计内容 采用状态机结构设计简易全双工串行数据收发器,串行数据收发速率为9600bit/s,数据帧为RS232标准:1个起始位,8位数据,1位校验位,1.5位停止位。要求把数据发送、接收结果分别在2对数码管上以16进制显示出来。要求采用状态机或计数器设计,具有奇偶校验功能,接受错误时显示- - - -,并编写串行数据测试程序进行仿真。扩展设计:采用16倍超采样频率方法,实现串行数据接收和发送。三.课程设计要求 1. 要求独立完成设计任务。 2. 课程设计说明书封面格式要求见《天津城建大学课程设计教学工作规范》附表1 3. 课程设计的说明书要求简洁、通顺,计算正确,图纸表达内容完整、清楚、规范。 4. 测试要求:根据题目的特点,采用相应的时序仿真或者在实验系统上观察结果。 5. 课设说明书要求: 1) 说明题目的设计原理和思路、采用方法及设计流程。 2) 对各子模块的功能以及各子模块之间的关系作明确的描述。 3) 对实验和调试过程,仿真结果和时序图进行说明和分析。 4) 包含系统框图、电路原理图、HDL设计程序、仿真测试图。 指导教师(签字): 教研室主任(签字): 批准日期:2014 年12 月18 日 目录 第一章设计方案 (1) 1.1 设计原理 (1) 1.1.1 UART介绍 (1)

数字逻辑与处理器基础实验 串口收发器设计 实验报告 姓名: 学号:2012011250 班级:无21 组号:S2

目录 实验十:串口收发器设计 (3) 一、实验目的 (3) 二、实验内容 (3) (一) 设计方案 (3) 1. 串口基本原理 (3) 2. 实验设计原理 (3) 3. 模块介绍 (4) (二) 关键代码 (4) (三) 仿真波形 (8) (四) 综合结果 (8) 1. 综合电路图 (8) 2. 综合情况 (9) 3. 硬件调试情况 (11) 三、实验总结 (11)

实验十:串口收发器设计 一、实验目的 了解和掌握UART的工作原理 二、实验内容 (一)设计方案 1.串口基本原理 图1串口时序示意图 图1表明在异步传送中串行发送一个数据字节的位定时关系(图中没有包括奇偶校验位)。发送一个完整的字节信息,首先是一个作为起始位的逻辑“0”位,接着是8个数据位,然后是1个、1+1/2个或2个停止位逻辑“1”位,数据线空闲时呈现为高或“1”状态。在字符的8位数据部分,先发送数据的最低位,最后发送最高位。每位持续的时间是固定的,由发送器本地时钟控制,每秒发送的数据位个数,即为“波特率”。 起始位和停止位起着很重要的作用。显然,他们标志每个字符的开始和结束,但更重要的是他们使接收器能把局部时钟与每个新开始接收的字符再同步。异步通信没有可参照的时钟信号,发送器随时都可能发送数据,需要从任何边沿的出现时刻开始正确地采样紧接着的 10~11位(包括开始位、数据位和停止位)。接收器的时钟与发送器的时钟不是同一个,因此,接收器采样点的间隔跟由发送器时钟所确定的位间隔时间不同,接收器设计不好会导致采样错误。 2.实验设计原理

2 UART 原理 2.1 UART 的通信原理 UART 即通用异步收发器,是一种串行通信方式。数据在传输过程中是通过一位一位地进行传输来实现通信的,串行通信方式具有传输线少,成本底等优点,缺点是速度慢。串行通信分为两种类型:同步通信方式和异步通信方式。但一般多用异步通信方式,主要因为接受和发送的时钟是可以独立的这样有利于增加发送与接收的灵活性。异步通信是一个字符接着一个字符传输,一个字符的信息由起始位、数据位、奇偶校验位和停止位组成。每一个字符的传输靠起始位来同步,字符的前面一位是起始位,用下降沿通知收方开始传输,紧接着起始位之后的是数据位,传输时低位在前高位在后,字符本身由5~8位数据位组成。数据位后面是奇偶校验位,最后是停止位,停止位是用高电平来标记一个字符的结束,并为下一个字符的传输做准备。停止位后面是不同长度的空闲位。停止位和空闲位都规定为高电平,这样可以保证起始位有一个下降沿。UART 的帧格式如图2.1所示。 图2.1 UART 的帧格式 Figure 2.1 The frame format of UART UART 的帧格式包括线路空闲状态(idle ,高电平)、起始位(start bit ,低电平)、5~8位数据位(data bits)、校验位(parity bit ,可选)和停止位(stop bit ,位数可为1、1.5、2位)。 在串口的异步通信中,数据以字节为单位的字节帧进行传送。发送端和接收端必须按照相同的字节帧格式和波特率进行通信。其中字节帧格式规定了起始位、数据位、寄偶效验位、停止位。起始位是字节帧的开始。使数据线处于逻辑0状态 ,用于向接收端表明开始发送数据帧,起到使发送和接收设备实现同步。停止位是字节帧的终止,使数据线处于逻辑1状态。用于向接收端表明数据帧发送完毕。波特率采用标准速度9600bit/s 。

南通大学 智能家居监控系统设计 学院:电气工程 班级:电115 姓名:刘家辰 学号: 1112002083

目录 1 引言 (3) 2 系统设计 (3) 3 硬件设计 (4) 3.1单片机的选型 (4) 3.2温度监测模块 (5) 3.2.1 温度传感器简介 . (5) 3.2.2测量原理 (5) 3.2.3电路仿真 (6) 3.3烟雾监测模块 (7) 3.4 Zigbee 模块 (8) 3.5报警模块 (9) 3.6键盘输入模块 (10) 3.7液晶显示模块 (11) 3.8人体红外感应模块 . (11) 4 主机软件设计 (12) 4.1主机程序整体框架 (13) 4.2无线发送 / 接收程序 . (13) 4.3温度监测节点程序 . (15) 4.4烟雾监测节点程序 . (17) 4.5红外热释电监测节点程序 . (18) 5 设计体会 (20)

6 参考文献 (20) 7 附录 (21) 主机电路原理图 (21)

1引言 随着社会经济和科学技术的发展,社会信息化程度越来越高,物联网的推出是 时代发展的需要,“三网合一”、“ 三屏合一” 等新概念不断提出,智能家居 成为未来家居的发展方向。智能家居在两个方面具有重要作用: (1)家居智化,继而实现住户舒适最大化,家庭安全最大化。智能家居通过 其智能家庭控制帮助人们改进生活方式,重新安排每天的时间计划表,并为高质 量的生活环境提供安全保障。 (2)智能家居的另一个重要作用是降低能源消耗,操作成本最小化,帮助人们 节约日常能源消耗开支。 智能家居主要通过智能家庭控制系统实现,家庭控制网络是实现智能家庭控制 系统的关键。近几年,各种家庭网络推进组织相继成立,并各自推出了相 关建议和标准,但这些技术标准缺乏统一的通信接口,相互间不兼容 , 无法提供家 庭控制网络的完整解决方案。因此,智能家居研究者面临的最大挑战和机遇是家用 电子领域缺乏统一的通信标准和互操作协议。 2系统设计 智能家居监控系统的总体设计框图如图 1 所示。该系统采用主从方式,主机 负责接收无线信息、GSM远程报警、传感器阈值设置,从机负责温度、气体、烟雾、等环境信号采集处理及无线发送。本文研制的智能家居环境监测报警系统能够实时 监测煤气泄漏、火灾、电热毯过热等温度异常、外人闯入等危险状态, 并可实现电话号码报警,设置传感器阈值等功能。

第三章UART设计 3、1 UART得帧格式 在UART 中,数据位就是以字符为传送单位,数据得前、后要有起始位、停止位,另外可以在停止位得前面加上一个比特(bit)得校验位。其帧格式如图所示。 文章通过分析UART得功能,利用有限状态机来描述UART核心控制逻辑得方法,将其核心功能集成,从而使整个设计更加稳定、可靠。基本得UART通信只需要两条信号线就可以完成数据得相互通信。UART得功能模块如图3_2所示。

3、2 UART模块 在大规模电路得设计中,广泛采用层次化,结构化得设计方法。它将一个完整得硬件设计任务从系统级开始,划分为若干个可操作得模块,编制出相应得模型并进行仿真验证,最后在系统级上进行组合。这样在提高设计效率得同时又提高了设计质量,就是目前复杂数字系统实现得主要手段,也就是本文设计思想得基础。其系统模块可划分为4个部分,如波特发生器,控制器,接收器,发送器,如图3-3所示: 3 Data_in:并行输入data_out:并行输出 Cs:通知cpu接收数据位ks:通知cpu发送准备位 Reset:重启输入state:uart状态输入 Clk:48M时钟输入

3、2、2UART主体程序 `timescale 1ns/1ns module gs_opt( input wire read, input wire clk, input wire reset, input wire state, input wire [7:0] dat_in, output wire send, output wire cs, output wire ks, output wire [7:0] dat_out ); wire send_enable; wire read_enable; wire clk_enable3; wire clk_enable4; wire clear3 ; wire clear4 ; wire clk_enable; wire [7:0] counters; wire clear ; wire t1; /* read,send,cs,ks,reset,state,clk,dat_in,dat_out); //module uart(read,send,cs,ks,reset,state,clk,dat_in,dat_out); input read,clk,reset,state; //read为串行输入,clk为时钟输入50MHZ,reset为重启键input[7:0] dat_in;//并行数据输入 output send,cs,ks; //send为串行输出,cs为通知cpu接收数据位,ks为发送准备位output[7:0] dat_out;//并行数据输出 wire clear,clk_enable,read_enable,clear3,send_enable,clear4,t1; wire[7:0] counters,dat_in;*/

课程设计任务书 学生姓名: 瞿子敬专业班级: 通信1104 指导教师: 陈适工作单位: 信息工程学院 题目:FPGA通用异步收发器设计 课程设计目的: 1.熟练使用VHDL语言进行电路设计; 2.能够运用相关软件进行模拟分析; 3.掌握基本的文献检索与文献阅读的方法; 4.提高正确的撰写论文的基本能力。 课程设计内容与要求 1.内容:FPGA通用异步收发器设计 2、要求:使用VHDL语言完成电路设计,并在此基础上进行仿真,得到正确结果。初始条件 QuartusⅡ仿真平台 时间安排 1.方案设计,1天; 2.软件设计,2天; 3.系统调试,1天; 4.答辩,1天。 指导教师签名: 年月日系主任(或责任教师)签名: 年月日

目录 摘要................................................................................................................................ I Abstract.......................................................................................................................... I 1、UART简介 (1) 1、1 UART基本特点 (1) 1、2 FPGA URAT系统组成 (1) 2、模块设计 (2) 2、1 顶层模块 (2) 2、1 波特率发生器 (3) 2、3 UART接收器 (3) 2、3、1 接收器简介 (3) 2、3、2 UART接收器的接收状态机 (4) 2、4 URAT发送器 (5) 2、4、1 发送器简介 (5) 2、4、2 发送状态机 (5) 3、程序设计与仿真 (7) 3、1 顶层程序 (7) 3、2 波特率发生器程序 (9) 3、3 UART发送器程序 (10) 3、4 UART接收器程序 (13) 4、心得体会 (15) 5、参考文献 (16)

课程设计任务书 学生:瞿子敬专业班级:通信1104 指导教师:适工作单位:信息工程学院 题目:FPGA通用异步收发器设计 课程设计目的: 1.熟练使用VHDL语言进行电路设计; 2.能够运用相关软件进行模拟分析; 3.掌握基本的文献检索和文献阅读的方法; 4.提高正确的撰写论文的基本能力。 课程设计容和要求 1.容:FPGA通用异步收发器设计 2.要求:使用VHDL语言完成电路设计,并在此基础上进行仿真,得到正确结果。初始条件 QuartusⅡ仿真平台 时间安排

1.方案设计,1天; 2.软件设计,2天; 3.系统调试,1天; 4.答辩,1天。 指导教师签名: 年月日系主任(或责任教师)签名: 年月日

目录 摘要...................................................................................................................................... I Abstract ............................................................................................................................ II 1. UART简介 . (1) 1.1 UART基本特点 (1) 1.2 FPGA URAT系统组成 (2) 2. 模块设计 (3) 2.1 顶层模块 (3) 2.1 波特率发生器 (3) 2.3 UART接收器 (4) 2.3.1 接收器简介 (4) 2.3.2 UART接收器的接收状态机 (5) 2.4 URAT发送器 (6) 2.4.1 发送器简介 (6) 2.4.2 发送状态机 (6)

郑州交通职业学院 课程设计(论文) 题目:基于单片机的防盗报警系统的设计 系别:信息工程系 专业: 学号: 班级: 姓名: 指导教师: 日期: 2011.12.22

.1设计要求及方案论证 人们生活水平不断提高,对私有财产的保护意识在不断的增强,因而对防盗措施提出了新的要求。本设计就是为了满足预防抢劫、盗窃等意外事件的需要而设计的红外防盗报警系统。 本设计主要包括硬件和软件设计两个部分。硬件部分包括单片机控制电路、红外探头电路、驱动执行报警电路、LED控制电路等部分组成。处理器采用51系列单片机AT89C51。整个系统是在系统软件控制下工作的。软件部分可以划分为以下几个模块:数据采集、键盘控制、报警和显示等子函数。 [关键词]:单片机、红外传感器、数据采集、报警电路。 1.1设计任务与要求 (1)该设计主要包括硬件和软件设计两个部分。模块划分为数据采集、键盘控制、报警和显示等模块子函数。 (2)本红外线防盗报警系统由热释电红外传感器、智能报警器、单片机控制电路、LED控制电路及相关的控制管理软件组成。用户终端完成信息采集、处理、数据传送、功能设定、本地显示、本地报警等功能。终端由中央处理器、输入模块、输出模块、通信模块、功能设定模块等部分组成。 (3)系统可实现功能。为了探测移动人体,通常使用双元件型热释电红外传感器,在这种传感器内部,两个敏感元件反相连接,当人体静止时两元件极化程度相同,互相抵消。但人体移动时,两元件极化程度不同,净输出电压不为0 ,从而达到了探测移动人体的目的。因此可把报警系统设置在外出布防状态,使探测器工作。当有人闯入时,热释电红外传感器将探测到动作,设置在监测点上的红外探头将人体辐射的红外光谱变换成电信号,经放大电路、比较电路送至门限开关,打开门限阀门送出TTL 电平至AT89C51单片机,经单片机处理运算后驱动执行报警电路使警号发声。

以太网收发电路设计方案详解 以太网收发电路由RJ45 接口、耦合变压器、以太网收发器,以及收 发器与调制驱动电路、接收解调电路之间的接口组成。其中以太网收发器是核 心单元,直接决定了系统的工作性能。以太网收发器IP113IP113 是二端口 10/100Mbps 以太网集成交换器,由一个二端口交换控制器和两个以太网快速收发器组成。每个收发器都遵守IEEE802.3、IEEE802.3μ、IEEE802.3x 规则。为帧缓冲保留了SSRAM,可以存储1K 字节的MAC 地址,全数字自适应调整和时序恢复,基线漂移校正,工作在10/100baseTX 和100baseFX 的全双工/半双工方式。使用2.5V 单电源,25MHz 单时钟源,0.25μm 工艺,128 脚PQFP 封装。 Port1 的速率是自适应调整的结果,因而不需要外加存储器以缓冲数据包。每个端口都有自己的接收缓冲管理、发射缓冲管理、发射排队管理、发射 MAC 和接收MAC。各个端口共享一个散列单元、一个存储器接口单元、一个 空缓冲管理器和一个地址表。 主要由以太网收发芯片IP113、专用配置芯片EEPROM 93C46、LED 显示矩阵,以及IP113 的Port1 与TP 模块、Port2 与FX 模块之间的接口组成。 IP113 支持很多功能,通过设置适当的参数满足不同的需要,既可以由特定的 管脚设定,也可以用EEPROM 配置。为提高系统的整体性能,这里采用专用 串行EEP ROM 93C46 芯片。系统复位时,管脚LED_SEL[1:0]分别作为93C46 的时钟EESK 和片选EECS,BP_KIND[1:0]分别作为93C46 地址EEDI 和数据输出EEDO,将93C46 内部的参数读入IP113 内部的寄存器。复 位结束后,这些管脚均变成输入信号,以使IP113 脱离93C46 而独立工作。

10M光纤收发器的系统设计与实现 【摘要】介绍了光电介质转换芯片ML4664的原理,详细说明了以ML4664为主要芯片构成10M光纤收发器的设计方法,并给出了设计的具体原理图。 关键词:ML4664,光纤收发器,通信 1引言 随着信息用户群的不断增长以及用户对信息服务质量越来越高的要求,光纤传输从各种网络传输技术中脱颖而出,光纤网络建设逐步扩大,光纤网络产品应用也日益普及,很多用户开始考虑用“光纤到桌面”来替代水平布线系统中的铜缆方案。但是完整地考虑一个光纤到桌面的解决方案,不仅要有光纤信息出口和光纤配线箱,还需要价格昂贵的光纤网卡和光出口集线器,这使整个系统的成本大大提高。而一种经济有效的实现光纤到桌面的方法是使用光纤收发器(即光电介质转换器)。光纤收发器是一种透明传输的光电介质转换设备,不仅能大大简化局域网的升级,而且可以保护原有铜缆LAN设备的投资,因此成为当前市场迫切需要的设备之一。 2系统结构 本文介绍的光纤收发器系统结构如图1所示,它由光电介质转换芯片ML4664、光收发一体化模块、电接口模块、RJ45和电源这几部分组成。其中,光电介质转换芯片ML4664为光纤收发器系统的主芯片,它完成10Base-T的双绞线介质到10Base-FL光纤介质的转换;电接口模块除了将RJ45送来的电信号耦合至ML4664外,还包括一个低通滤波器,完成低通滤波功能;光收发一体化模块是与光纤介质的接口模块;由于ML4664需要数字电源和模拟电源,所以,在电源部分我们专门分出了数字电源和模拟电源两部分。 3ML4664功能简介 ML4664是Micro Linear公司推向市场的一款高性能光电介质转换芯片,可用于实现10Base-T的双绞线介质到10Base-FL光纤介质的转换,符合IEEE802.3的10Base-T和10Base-FL的规范标准,采用5V电源供电,且不需要外接晶体或晶振,是一款理想的光电介质转换芯片。随着光通信的飞速发展,ML4664必将有更广泛的应用。 3.1主要特征 ML4664的主要特征有: ·支持全双工方式; ·支持100Ω的非屏蔽双绞线和150Ω屏蔽双绞线; ·电流输出可高达100mA,并且具有较低的RFI噪声和很小的抖动; ·具有自动极性纠正功能; ·输入灵敏度可达2mVP-P; ·具有自动连接检测功能; ·带有高稳定性的数字均衡器,支持55dB的动态输入范围。

11.5U A R T收发器设计实例 U A R T(U n i v e r s a l A s y n c h r o n o u s R e c e i v e r T r a n s m i t t e r,通用异步收发器)是广泛使用的异步串行数据通信协议。下面首先介绍U A R T硬件接口及电平转换电路,分析U A R T的传输时序并利用V e r i l o g H D L语言进行建模与仿真,最后通过开发板与P C相连进行R S-232通信来测试U A R T收发器的正确性。 1.5.111.5.1U A R T界面介绍 本节所介绍的U A R T即美国电子工业协会定义的R S-232C,简称R S-232。R S-232的接口一般有9针的D B9和25针的D B25,这里以9针为例,它的各个引脚的定义如表11-8所示。 表11-8D B9的引脚定义 引脚功能缩写 1资料载波检测D C D 2接收数据R X D 3发送数据T X D 4数据终端准备就绪D T R 5信号地G N D 6数据准备就绪D S R 7发送请求R T S 8清除发送C T S 9振铃提示R I 由于R S-232的电气特性与F P G A引脚不相同,因此它们之间不能直接相连,对于R S-232的数据线,当为逻辑“1”时,对应电平是-15V~-3V;当为逻辑“0”时,对应电平是15V~3V。因此,与F P G A相连之前必须进行电平转换,转换原理图如图11-39所示。

图11-39R S-232电平转换原理图 1.5.211.5.2U A R T传输时序 U A R T传输时序如图11-40所示。 图11-40U A R T传输时序 发送数据过程:空闲状态,线路处于高电位;当收到发送数据指令后,拉低线路一个数据位的时间T,接着数据按低位到高位依次发送,数据发送完毕后,接着发送奇偶校验位和停止位(停止位为高电位),一帧资料发送结束。 接收数据过程:空闲状态,线路处于高电位;当检测到线路的下降沿(线路电位由高电位变为低电位)时说明线路有数据传输,按照约定的波特率从低位到高位接收数据,数据接收完毕后,接着接收并比较奇偶校验位是否正确,如果正确则通知后续设备准备接收数据或存入缓存。 由于U A R T是异步传输,没有传输同步时钟。为了能保证数据传输的正确性, U A R T采用16倍数据波特率的时钟进行采样。每个数据有16个时钟采样,取中

通信原理课程设计 题目:基于MAX7033接收器的课程设计学院名称:电气工程学院 指导老师: 班级: 学号: 学生姓名: 二0一二年六月

基于MAX7033接收器的课程设计 摘要 MAX7033完全集成的低功耗CMOS超外差接收机是接收300MHz至450MHz频段内幅移键控(ASK)数据的理想选择。这款接收机的RF输入信号范围是-114dBm至0dBm。MAX7033使用极少的外部元件并具有低电流关断模式,非常适用于对成本和功耗有严格要求的应用,如汽车和消费类电子领域。MAX7033包括一个低噪声放大器(LNA)、一个完全差分的镜频抑制混频器、一个带有集成压控振荡器(VCO)的片内锁相环(PLL)、一个带有接收信号强度指示器(RSSI)的10.7MHz IF限幅放大器和一个模拟基带数据恢复电路。MAX7033还有一个不连续的一步自动增益控制(AGC),当RF输入信号超过-62dBm时把LNA的增益降低35dB。AGC电路可以由外部控制进入保持状态。MAX7033采用28引脚TSSOP和32引脚TQFN封装,规定工作在扩展温度范围内(-40°C至+105°C)。 关键词:300MHz至450MHz 超外差接收器 集成镜频抑制电路作温度高达+105°C Abstract The MAX7033 fully integrated low power CMOS superheterodyne receiver is to receive an ideal choice for amplitude shift keying (ASK) data in the 300MHz to 450MHz band. The receiver has an RF input signal range is from-114dBm to 0dBm. MAX7033 use a few external components and has a low current shutdown mode is ideal for cost and power consumption critical applications, such as automtive and consumer electronics field. The MAX7033 includes a low noise amplifier (LNA), a fully differential image-rejection mixer, and one with integrated voltage-controlled oscillator (VCO) on-chip phase-locked loops (PLLs), with a received signal strength indicator (RSSI), a 10.7MHz IF limiting amplifier and an analog baseband data recovery circuit. MAX7033, there is a continuous one-step automatic gain control (AGC), when the RF input signal exceeds-62dBm reduce the LNA gain by 35dB. The AGC circuit by an external control into the hold. MAX7033 28-pin TSSOP and 32-pin TQFN package, specified over the extended temperature range (-40 ° C to 105 ° C). Key words: 300MHz to 450MHz superheterodyne receiver integrated image rejection circuit operating temperatures up to 105 ° C

CAN 收发器 TJA1040与TJA1050对比报告 1.简介 CAN总线,它是一种多主方式的串行通讯总线,基本设计规范要求有较高的位速率,高抗干扰性,而且能够检测出产生的任何错误。信号传输距离达到10Km时,仍然可提供高达5Kbps的数据传输速率。由于CAN串行通讯总线具有这些特性,它很自然的在汽车、制造业以及航空工业中受到广泛应用。 与CAN协议相关的芯片主要有两类,一类是:CAN控制器芯片,一类是:CAN收发器芯片,如TJA1040,TJA1050。 CAN控制器用于实现CAN总线的协议底层以及数据链路层,用于生成CAN帧并以二进制码流的方式发送,在此过程中进行位填充、添加CRC校验、应答检测等操作;将接收到的二进制码流进行解析并接收,在此过程中进行收发比对、去位填充、执行CRC校验等操作。此外还需要进行冲突判断、错误处理等诸多任务。 图1 CAN收发器在CAN总线应用系统中的位置 CAN收发器是CAN协议控制器和物理总线(双绞线)之间的接口,用于将二进制码流转换为差分信号发送,将差分信号转换为二进制码流接收,主要实现逻辑电平与“显性”,“隐性”的转换。它可以为总线提供差动的发送功能,为控制器提供差动的接收功能,是CAN-Bus 网络中的必须设备。 常见的CAN控制器芯片与CAN收发器芯片型号参见第5部分。 目前还没有看到把CAN控制器和CAN收发器集成在一起的CAN协议芯片,目前主要是独立的CAN控制器,独立的CAN接收器,集成CAN控制器的微处理器三类。因为CAN收发器和CAN控制器之间有时需要添加隔离单元。 总结:

CAN通信协议主要有CAN控制器完成,CAN控制器主要有实现CAN协议的电路和实现与微处理器接口的电路组成。 CAN收发器在CAN总线应用系统中的位置如下图所示。 图2 CAN收发器的典型应用电路 TJA1050 的设计采用了先进的绝缘硅SOI技术进行处理,以及最新的EMC技术,所以TJA1050具有优良的EMC性能。TJA1050不提供待机模式。特别要注意的是器件在不上电环境下的无源特性。 TJA1040 是以TJA1050的设计为基础,由于使用了相同的SOI技术,TJA1040具有和

UART 原理 2.1 UART 的通信原理 UART 即通用异步收发器,是一种串行通信方式。数据在传输过程中是通过一位一位地进行传输来实现通信的,串行通信方式具有传输线少,成本底等优点,缺点是速度慢。串行通信分为两种类型:同步通信方式和异步通信方式。但一般多用异步通信方式,主要因为接受和发送的时钟是可以独立的这样有利于增加发送与接收的灵活性。异步通信是一个字符接着一个字符传输,一个字符的信息由起始位、数据位、奇偶校验位和停止位组成。每一个字符的传输靠起始位来同步,字符的前面一位是起始位,用下降沿通知收方开始传输,紧接着起始位之后的是数据位,传输时低位在前高位在后,字符本身由5~8位数据位组成。数据位后面是奇偶校验位,最后是停止位,停止位是用高电平来标记一个字符的结束,并为下一个字符的传输做准备。停止位后面是不同长度的空闲位。停止位和空闲位都规定为高电平,这样可以保证起始位有一个下降沿。UART 的帧格式如图2.1所示。 图2.1 UART 的帧格式 Figure 2.1 The frame format of UART UART 的帧格式包括线路空闲状态(idle ,高电平)、起始位(start bit ,低电平)、5~8位数据位(data bits)、校验位(parity bit ,可选)和停止位(stop bit ,位数可为1、1.5、2位)。 在串口的异步通信中,数据以字节为单位的字节帧进行传送。发送端和接收端必须按照相同的字节帧格式和波特率进行通信。其中字节帧格式规定了起始位、数据位、寄偶效验位、停止位。起始位是字节帧的开始。使数据线处于逻辑0状态 ,用于向接收端表明开始发送数据帧,起到使发送和接收设备实现同步。停止位是字节帧的终止,使数据线处于逻辑1状态。用于向接收端表明数据帧发送完毕。波特率采用标准速度9600bit/s 。