FPGA结构介绍

由于PLD大都是基于ROM或者RAM的,因此先介绍下ROM和RAM

1.RAM(Random-Access Memory,随机存储器)

RAM正常状态下就可以随时快速的向存储器里写入和读出数据,断电丢失

RAM可以分为SRAM(静态随机存储)和DSRAM(动态随机存储)

1.1. SRAM

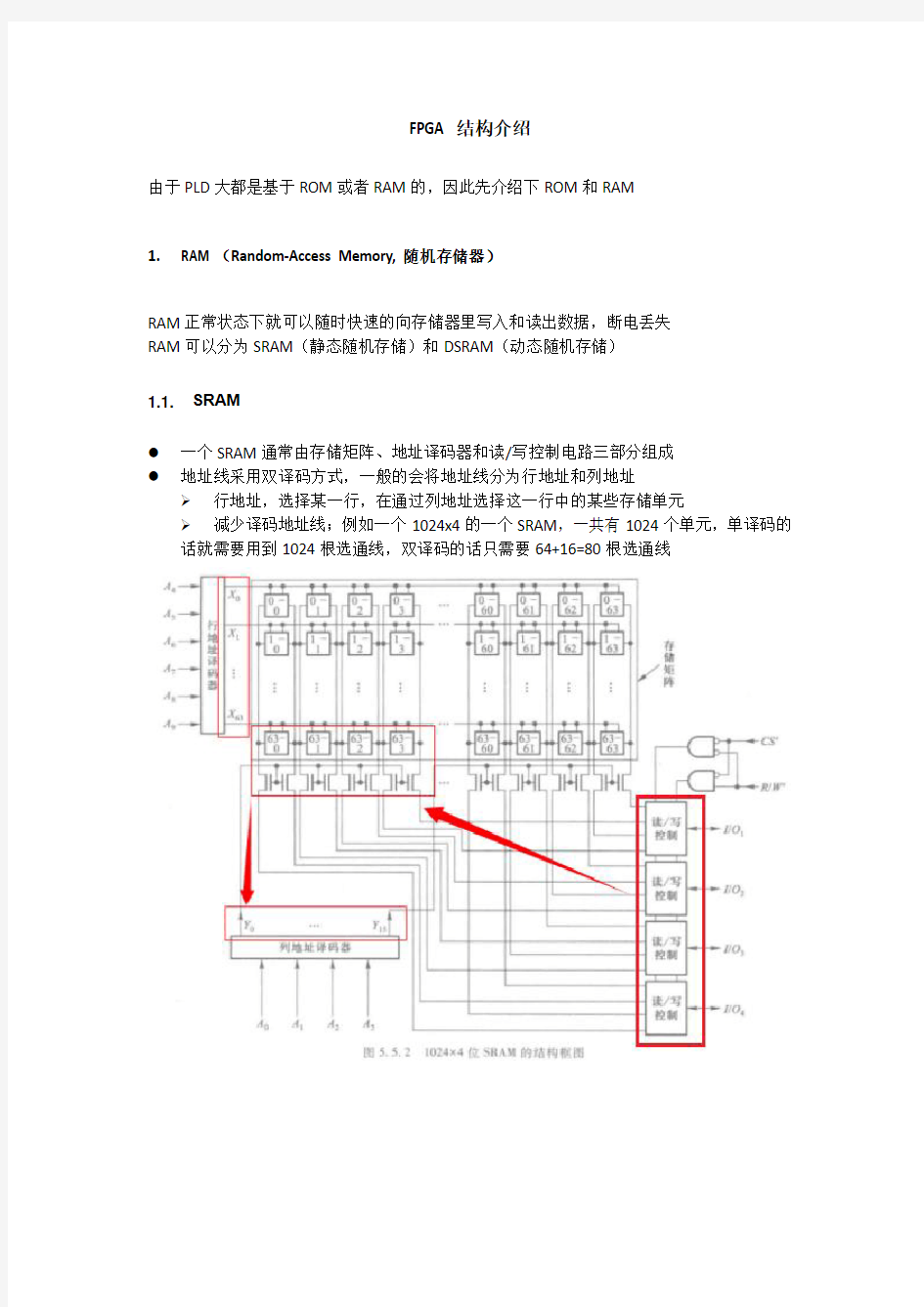

●一个SRAM通常由存储矩阵、地址译码器和读/写控制电路三部分组成

●地址线采用双译码方式,一般的会将地址线分为行地址和列地址

?行地址,选择某一行,在通过列地址选择这一行中的某些存储单元

?减少译码地址线;例如一个1024x4的一个SRAM,一共有1024个单元,单译码的话就需要用到1024根选通线,双译码的话只需要64+16=80根选通线

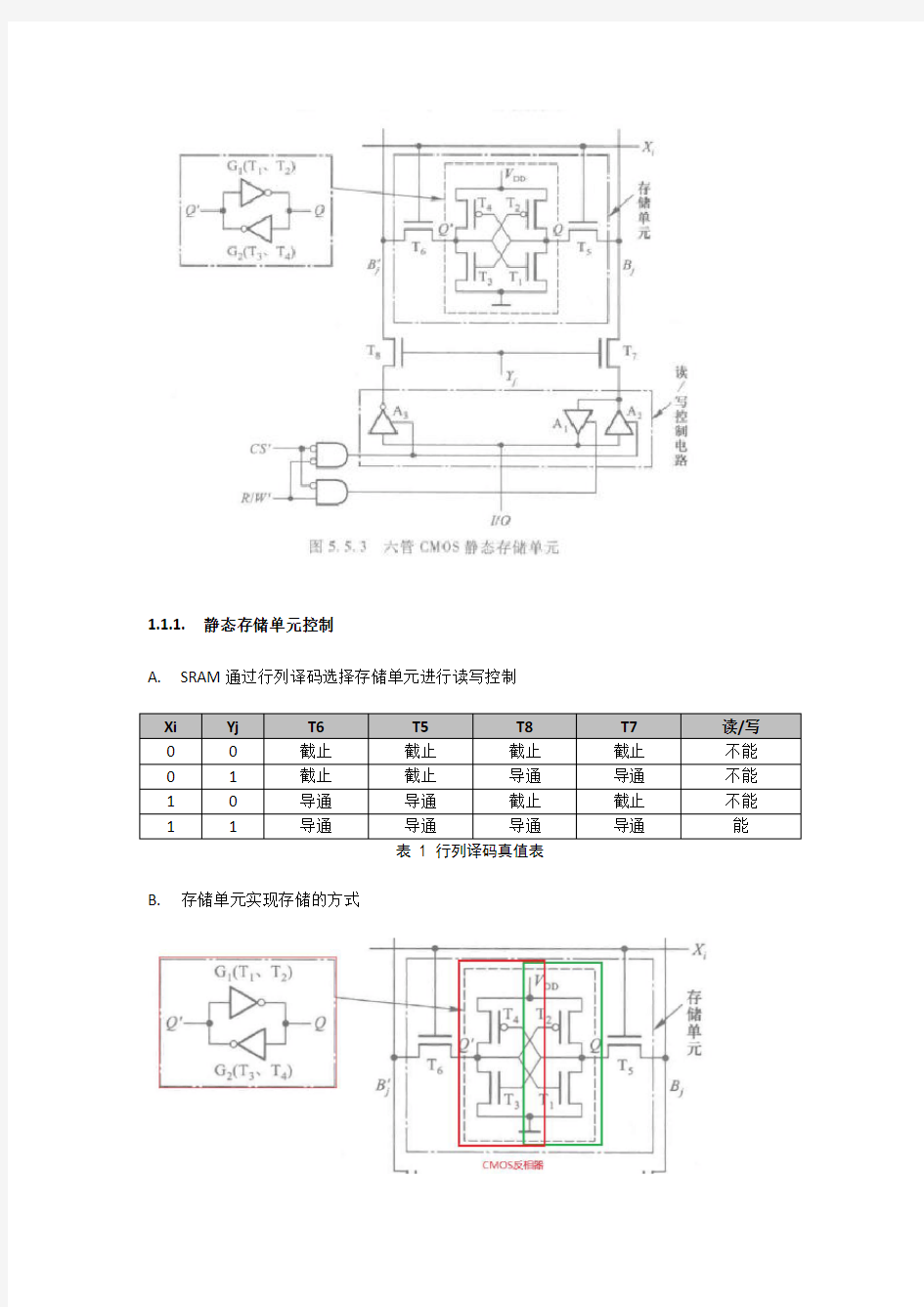

1.1.1.静态存储单元控制

A.SRAM通过行列译码选择存储单元进行读写控制

表 1 行列译码真值表B.存储单元实现存储的方式

靠锁存器来实现,要写入的数据为Q,经过A3的反相之后Q’,此时经过G1输出为Q;

当撤去Q’和Q的外部输入后,G1的输出Q,经过G2到达G1的输入端,状态得以保持C.选择对应的存储单元后,通过CS’和R/W’进行存储单元读写的控制

假设I/O此时输入为Q

表 2 读写控制真值表

1.2. DRAM(Dynamic Random-Access Memory,动态随机存储器)

DRAM其结构大体上与SRAM类似,包括双地址译码,存储矩阵,读写控制

对于DRAM,为了提高集成度减少引脚数目,一般都采用一位输入、一位输出和地址分时输入(地址多路复用)

1.2.1.地址多路复用

这里一个行地址和列地址都是10位的一个DRAM,可以看出他们的行、列地址都是共用的相同的引脚,分为2次分别送入,分别由CAS’和RAS’控制:

首先是行地址输入,行地址到达时,RAS’必须变为低,控制行锁存器锁存输入的行地址

然后是列地址输入,列地址到达时,CAS’必须为低,控制列地址锁存器锁存输入的列地址1.2.2.Mos存储单元结构

DRAM的存储单元是采用mos管加电容的方式实现的,电容有电荷时存放1,无电荷时存放0

A.行地址线为高电平时,相应的mos管导通,电容连接到位线上;此时刷新放大器读取

对应电容上的电压值,将读到的电压转换成逻辑0或1

B.由于在行地址线为高时,一行上所有的电容C都受到了影响,为了在读出数据之后仍

能保持原有的信息,刷新放大器在读取之后会对电容进行重写

C.列地址线为高电平时,相应的mos管导通,位线导通

1.2.3.刷新操作

由于电容存在有漏电流,,保存电荷的时间有限,为了避免存储的数据丢失,必须定时的向电容进行充电,称为刷新

刷新是按照行来操作的,因此不需要列地址,下图中,通过一个刷新计数器,产生10位行地址,来刷新电容

1.2.4.读/写端口

三态门控制,输入还是输出(写还是读)下图是CS’控制

1.3. SRAM与DRAM区别

根据存储方式可以得知,断电后,里面所存储的数据都会丢失

2.ROM(Read-Only Memory,只读存储器)

一般ROM正常情况下只能从里面读取数据

2.1. 掩模ROM

里面的内容已由厂家按要求写在芯片中,不可更改。以4x4的掩模ROM来说明其实现的原理

A1A0字线D3D2D1D0

每个位置都有mos管,这里只是没有画出来而已

通过A0、A1的值,会选择W0--W3中的一条字线输出,以W0字线为例:当A1A0=00时,W0字线为高,其余字线为低

下图中,当W0字线为1,其余字线为0时,可以看出,为0的3个字线,其mos管都是截止的;

W0为1时,只看图中黑色方框,D0中的mos管导通接地,D0=0;D1中的mos管截止,D1连接到Vdd,D1=1.。。。。。

因此输出D3D2D1D0=1010

可以看到,是先选择字线然后再输出位线值,一位位线就是一位输出数据

2.2. PROM(可编程只读存储器)

PROM是使用熔丝加三极管进行编程,一般出厂时都会连接所有的熔丝,里面存入的数据全为1,

下面是一个16x8的一个PROM存储器4位地址线选择要存储的字线,8根输出位线

当字线为高时,三极管导通,此时熔丝连接,位线输出高;当熔丝熔断时,位线连接到地,此时输出为低

另外还有反熔丝型的PROM,其可编程连接元件是一个绝缘连接件(通常用特殊的绝缘材质),未编程似乎所有的连接件均不导通,加电压后,绝缘被永久击穿,导通连接

2.3. 可擦除、可再编程存储器(EPROM,EEROM,Flash)

最开始的可编程ROM是用紫外线照射进行擦除的,被称之为EPROM;

后来又出现了电可擦除的,称之为E2PROM;

再后来出现了快速存储器,称之为Flash;

所有的可擦除、可编程的ROM其连接元件都是基于浮栅mos管

2.3.1.浮栅mos管

浮栅mos管有两个控制栅极,一个为正常的CG极,一个为特殊的FG极

FG中无电荷时,mos管正常工作

当FG中注入负电荷时,CG的开启会被提高,此时会高于W中正常的高电平,相当于将mos 管截止了

因此上图中,假设源极接Vss,位线D接地,FG中无电荷时,存储为1;有负电荷时,存储为0

2.3.2.FLASH

分为NOR和NAND

NOR:小容量,读取速度快

NAND:大容量

3.其他3.1. 三态门

3.2. DRAM时序原理

3.3. 电容漏电

电容介质不可能绝对不导电,会有漏电流,电荷保存时间有限