. 课程设计

. 教学院计算机学院 课程名称计算机组成原理题目4位乘法整列设计专业计算机科学与技术班级2014级计本非师班姓名唐健峰 同组人员黄亚军 指导教师 2016 年10 月 5 日

1 课程设计概述 1.1 课设目的 计算机组成原理是计算机专业的核心专业基础课。课程设计属于设计型实验,不仅锻炼学生简单计算机系统的设计能力,而且通过进行设计及实现,进一步提高分析和解决问题的能力。 同时也巩固了我们对课本知识的掌握,加深了对知识的理解。在设计中我们发现问题,分析问题,到最终的解决问题。凝聚了我们对问题的思考,充分的锻炼了我们的动手能力、团队合作能力、分析解决问题的能力。 1.2 设计任务 设计一个4位的二进制乘法器: 输入信号:4位被乘数A(A1,A2,A3,A4), 4位乘数B(B1,B2,B3,B4), 输出信号:8位乘积q(q1,q2,q3,q4,q5,q6,q7,q8). 1.3 设计要求 根据理论课程所学的至少设计出简单计算机系统的总体方案,结合各单元实验积累和课堂上所学知识,选择适当芯片,设计简单的计算机系统。 (1)制定设计方案: 我们小组做的是4位阵列乘法器,4位阵列乘法器主要由求补器和阵列全加器组成。 (2)客观要求 要掌握电子逻辑学的基本内容能在设计时运用到本课程中,其次是要思维灵活遇到问题能找到合理的解决方案。小组成员要积极配合共同达到目的。

2 实验原理与环境 2.1 1.实验原理 计算机组成原理,数字逻辑,maxplus2是现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 用乘数的每一位去乘被乘数,然后将每一位权值直接去乘被乘数得到部分积,并按位列为一行每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值,将各次部分积求和得到最终的对应数位的权值。 2.2 2.实验环境 2.2.1双击maxplu2II软件图标,启动软件 (1).新建工程,flie->new project ....,出现存储路径的选项框,指定项目保存路径并且为工程命名,第三行设置实体名,保持与工程名一致。点击OK

课程设计任务书 题目基于FPGA的6*6串行乘法器设计起讫日期 学生姓名专业班级通信工程 所在院系电气信息学院 指导教师职称 所在单位通信工程教研室

任务及要求: 1.设计内容和要求(包括设计内容、主要指标与技术参数) 设计内容:设计一个6*6串行乘法器 设计要求: (1)设计语言为Verilog,仿真软件为ISE自带仿真软件iSIM; (2)该设计不要求下载到硬件开发板上,只需给出仿真波形图,但要求能够从波形图 中看出实现了乘法运算 2.原始依据 本设计要求学生应用Xilinx FPGA设计一个6*6串行乘法器,通过设计能够让学生进一步掌握FPGA的基本开发流程,同时提高时序设计能力,学生已学习过EDA课程,掌握硬件描述语言基本知识,通过本次设计可进一步提高学生的动手能力,加强理论联系实际的能力。 3.进度计划 3.4-3.8 查阅相关资料,掌握FPGA基本知识。 3.11-3.15 应用Verilog语言进行程序开发,设计调试。 3.18-3.22 调试验收,撰写专业课程实践训练报告。 4.参考文献 [1] 夏宇闻. Verilog数字系统设计教程[M]. 北京:北京航空航天大学出版社,2008. [2] Snair Palnitkar(美). VerilogHDL数字设计与综合. 夏宇闻等译.(第二版)[M]. 北京:电子工业出版社,2009. [3] Xilinx. UG230 [Z/OL]. https://www.doczj.com/doc/f21177625.html, 指导教师签字: 教研室主任签字:

目录 摘要: (4) 关键词 (4) 一:FPGA (4) 1.1名称 (4) 1.2背景 (4) 1.3工作原理 (4) 1.4芯片结构 (5) 二:Verilog HDL (5) 2.1verilog hdl名称 (5) 2.2verilog hdl用途 (5) 2.3 Ve r i l o g硬件描述语言的主要能力 (6) 三:Spartan3E (7) 四:乘法器 (8) 4.1什么是乘法器 (8) 4.2实现乘法器的方法 (8) 4.3 6*6串行乘法器的设计思路 (9) 4.4 6*6乘法器程序代码 (9) 4.5 6*6乘法器设计仿真图 (11) 4.6结果分析 (12) 四:总结 (12) 参考文献 (12)

课程设计报告 课程设计名称:计算机组成原理课程设计课程设计题目:阵列除法器设计及实现 院(系):计算机学院 专业: 班级: 学号: 姓名: 指导教师: 完成日期:2016年1月12日

目录 第1章总体设计方案0 1.1设计原理0 1.2设计思路2 1.3设计环境3 第2章详细设计方案4 2.1功能模块的设计及实现4 2.1.1细胞模块的设计及实现5 2.1.2除法器模块的设计及实现7 2.2仿真调试9 参考文献11 附录(电路原理图)

1 2

第1章总体设计方案 1.1 设计原理 在原码除法中,原码除法符号位是单独处理的,商符由两数符号位进行异或运算求得,商值由两数绝对值相除求得。原码除法中由于对余数的处理不同,又可分为恢复余数法和不恢复余数法(加减交替法)。在机器操作中通常采用加减交替法,因为加减交替法机器除法时间短,操作规则。 加减交替法的运算规则如下: (1)当余数为正时,上商1,余数左移一位后减去除数得下一 位余数。 (2)当余数为负时,上商0,余数左移一位后加上除数得下一位 余数。 阵列除法器是一种并行运算部件,采用大规模集成电路制造,及早期的串行除法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运算速度。阵列除法器有多种形式,如不恢复余数阵列除法器、补码阵列除法器等等。本实验设计的是加减交替阵列除法器。 本实验利用的细胞单元是一个可控加法/减法CAS单元,利用它组成的流水阵列来实现四位小数的除法。CAS单元有四个输入端、四个输出端。其中有一个控制输入端P,当P=0时,CAS作加法运算;

当P=1时,CAS作减法运算。逻辑结构图如图1.1所示。 图1.1 可控加法/减法(CAS)单元逻辑结构图CAS单元的输入及输出的关系可用如下逻辑方程来表示:Si=Ai⊕(Bi⊕P)⊕Ci Ci+1=(Ai+Ci)(Bi⊕P)+AiCi 当P=0时,CAS单元就是一个全加器,如下: Si=Ai⊕B⊕iCi Ci+1=AiBi+BiCi+AiCi 当P=1时,则得求差公式: Si=Ai⊕B⊕iCi Ci+1=AiBi+BiCi+AiCi

沈阳航空航天大学 课程设计报告 课程设计名称:计算机组成原理课程设计课程设计题目:阵列乘法器的设计与实现 院(系):计算机学院 专业:计算机科学与技术 班级: 学号: 姓名: 指导教师: 完成日期:2014年1月10日

沈阳航空航天大学课程设计报告 _______________________________________________________________________________ 目录 第1章总体设计方案 (1) 1.1设计原理 (1) 1.2设计思路 (2) 1.3设计环境 (3) 第2章详细设计方案 (3) 2.1总体方案的设计与实现 (4) 2.1.1总体方案的逻辑图 (4) 2.1.2器件的选择与引脚锁定 (4) 2.1.3编译、综合、适配 (5) 2.2功能模块的设计与实现 (5) 2.2.1一位全加器的设计与实现 (6) 2.2.2 4位输入端加法器的设计与实现 (7) 2.2.3 阵列乘法器的设计与实现 (10) 第3章硬件测试 (13) 3.1编程下载 (13) 3.2 硬件测试及结果分析 (13) 参考文献 (15) 附录(电路原理图) (16)

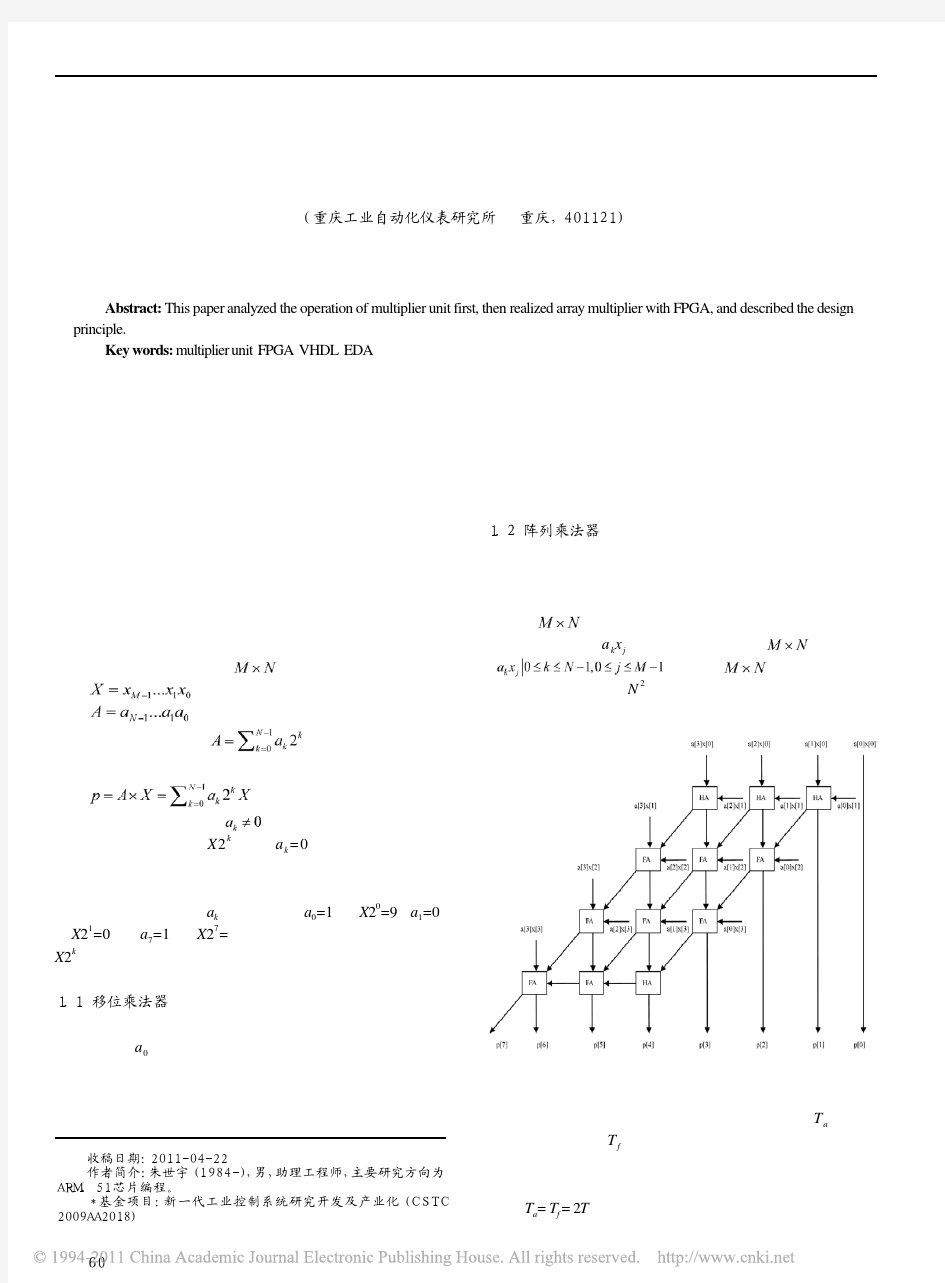

第1章总体设计方案 1.1 设计原理 阵列乘法器采用类似人工计算的方法进行乘法运算。人工计算方法是用乘数的每一位去乘被乘数,然后将每一位权值对应相加得出每一位的最终结果。如图1.1所示,用乘数的每一位直接去乘被乘数得到部分积并按位列为一行,每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值。将各次部分积求和,即将各次部分积的对应数位求和即得到最终乘积的对应数位的权值。 为了进一步提高乘法的运算速度,可采用大规模的阵列乘法器来实现,阵列乘法器的乘数与被乘数都是二进制数。可以通过乘数从最后一位起一个一个和被乘数相与,自第二位起要依次向左移一位,形成一个阵列的形式。这就可将其看成一个全加的过程,将乘数某位与被乘数某位与完的结果加上乘数某位的下一位与被乘数某位的下一位与完的结果再加上前一列的进位进而得出每一位的结果,假设被乘数与乘数的位数均为4位二进制数,即m=n=4,A×B可用如下竖式算出,如图1.1所示。 X 4 X 3 X 2 X 1 =A × Y 4 Y 3 Y 2 Y 1 =B X 4Y 1 X 3 Y 1 X 2 Y 1 X 1 Y 1 X 4Y 2 X 3 Y 2 X 2 Y 2 X 1 Y 2 X 4Y 3 X 3 Y 3 X 2 Y 3 X 1 Y 3 (进位) X4Y4 X3Y4 X2Y4 X1Y4 Z 8 Z 7 Z 6 Z 5 Z 4 Z 3 Z 2 Z 1 图1.1 A×B计算竖式 X 4 ,X 3 ,X 2 ,X 1 ,Y 4 ,Y 3 ,Y 2 ,Y 1 为阵列乘法器的输入端,Z 1 -Z 8 为阵列乘法器 的输出端,该逻辑框图所要完成的功能是实现两个四位二进制既A(X)*B(Y)的 乘法运算,其计算结果为C(Z) (其中A(X)=X 4X 3 X 2 X 1 ,B(Y)=Y 4 Y 3 Y 2 Y 1 , C(Z)=Z 8Z 7 Z 6 Z 5 Z 4 Z 3 Z 2 Z 1 而且输入和输出结果均用二进制表示 )。阵列乘法器的总原 理如图1.2所示。

各种乘法器比较 韦其敏08321050 引言:乘法器频繁地使用在数字信号处理和数字通信的各种算法中,并往往影响着整个系统的运行速度。如何实现快速高效的乘法器关系着整个系统的运算速度和资源效率。本位用如下算法实现乘法运算:并行运算、移位相加、查找表、加法树。并行运算是纯组合逻辑实现乘法器,完全由逻辑门实现;移位相加乘法器将乘法变为加法,通过逐步移位相加实现;查找表乘法器将乘积结果存储于存储器中,将操作数作为地址访问存储器,得到的输出数据就是乘法运算结果;加法树乘法器结合移位相加乘法器和查找表乘法器的优点,增加了芯片耗用,提高运算速度。 注:笔者使用综合软件为Quartus II 9.1,选用器件为EP2C70,选用ModelSim SE 6.1b进行仿真,对于其他的软硬件环境,需视具体情况做对应修改。 汇总的比较: 详细实现过程: 1.并行乘法器 源代码: module Mult1(outcome,a,b); parameter MSB=8; input [MSB:1] a,b; output [2*MSB:1] outcome; assign outcome=a*b; endmodule

资源耗用情况: ModelSim测试激励文件源代码:`timescale 10ns/1ns module Mult1_test(); reg [8:1] a,b; wire [16:1] outcome; Mult1 u1(outcome,a,b); parameter delay=2; initial begin a=1; b=0; end initial forever begin #delay a=a+1; b=b+1; if(outcome>=16'h0FFF) $stop;

收稿日期:2011-09-20;修回日期:2011-11-04 基金项目:国家科技重大专项基金资助项目(2009ZX01030-001-002). 作者简介:曾宪恺(1987-),男,湖北孝感人,硕士,主要研究方向为超大规模集成电路设计自动化(zengxk@vlsi.zju.edu.cn );郑丹丹(1981-),女,博士,主要研究方向为超深亚微米集成电路SOC 设计;严晓浪(1947-),男,教授,主要研究方向为超大规模集成电路设计、VLSI 设计自动化;吕冬明(1981-),男,博士,主要研究方向为集成电路CAD 研究;葛海通(1972-),男,博士,主要研究方向为嵌入式系统设计. 基于标准单元库扩展的快速乘法器设计 * 曾宪恺,郑丹丹,严晓浪,吕冬明,葛海通 (浙江大学超大规模集成电路设计研究所,杭州310027) 摘 要:设计并实现17?17bit 带符号数字乘法器。为了提高乘法器的性能,采用改进的Booth 编码算法、 Wal-lace 树型结构以及基于标准单元库扩展的设计方法。该方法使用逻辑功效模型分析乘法器的关键路径,通过构造驱动能力更为完备的单元以实现关键路径中每一级门功效相等,从而得到最短路径延时。将TSMC 90nm 标准单元库扩展得到扩展单元库, 使用两个单元库版图分别实现数字乘法器,基于扩展单元库实现的乘法器速度提升10.87%。实验结果表明,基于标准单元库扩展的半定制设计方法可以有效提升电路的性能,这种方法尤其适用于电路负载过大的情况。 关键词:乘法器;标准单元库扩展;改进的Booth 编码算法;Wallace 树;逻辑功效中图分类号:TN47 文献标志码:A 文章编号:1001-3695(2012)05-1778-03 doi :10.3969/j.issn.1001-3695.2012.05.047 Design of high-speed multiplier based on standard cell library extension ZENG Xian-kai ,ZHENG Dan-dan ,YAN Xiao-lang ,LV Dong-ming ,GE Hai-tong (Institute of VLSI Design ,Zhejiang University ,Hangzhou 310027,China ) Abstract :This paper proposed a 17?17bit signed digital multiplier.To improve the performance ,the multiplier used modi-fied Booth ’s recoding algorithm ,a Wallace tree structure and design method based on standard cell library extension.It ana-lyzed critical path using logical effort model ,and by constructing cells with different driving capabilities , it implemented equal logical effort in each stage to achieve minimum path delay.Based on TSMC 90nm standard cell library , generated an extended cell library ,and implemented the layouts of multiplier respectively.Compared to standard cell library ,the multiplier imple-mented with extended cell library achieved a performance improvement of 10.87%.Experimental results show that the semi-custom design methodology based on standard cell library extension can improve circuit performance effectively ,which is espe-cially appropriate for designs with large loads. Key words :multiplier ;standard cell library extension ;modified Booth ’s recoding algorithm ;Wallace tree ;logical effort 0引言 乘法器是嵌入式CPU 的重要部件,其运算速度决定了逻 辑运算单元的工作频率,因此高性能乘法器的设计仍然被关注 [1,2] 。同时,市场的需求加速了产品的上市进程,从而要求 设计者尽量缩短设计时间。为了兼顾乘法器的性能和设计时间, 通常使用基于标准单元库的半定制设计方法。但该方法受限于库中标准单元有限的驱动能力,无法实现最短路径延时。为此,本文提出基于标准单元库扩展的乘法器设计方法,消除了传统方法因关键路径优化不足对乘法器性能的影响。基于TSMC 90nm 工艺标准单元库扩展,设计并实现了17?17bit 乘法器模块。该乘法器支持带符号二进制乘法运算, 最差情况下(工作电压0.9V ,温度125℃)工作频率为346MHz 。设计过程中,使用EDA 工具进行了速度优先的逻辑综合以及布局布线;在关键路径的处理中,采用了基于逻辑功效的优化方法。 1乘法器 二进制乘法器实现了二进制数的乘法运算,它将两个二进 制数X 和Y 作为输入,将乘法运算的积Z 作为输出。设被乘数为m 位,记为X m -1X m -2…X 0,乘数为n 位,记为Y n -1Y n -2…Y 0,则积为m +n 位,记为Z m +n -1Z m +n -2…Z 0。将m 位被乘数X 与n 位乘数Y 的每一位进行与运算,可以得到n 项位数为m 的部分积, 用加法器阵列将n 项部分积相加,得到积Z 。乘法器的具体实现分为部分积生成、部分积压缩、最终加法三个步骤。通常,使用与门来产生部分积,用加法器阵列对部分积压缩来构成阵列乘法器。这种架构算法简单,易于实现,并且能够实现规则的版图结构,但是由于部分积个数较多,压缩时间较长,无法得到快速的乘法器。使用改进的Booth 编码算法[3,4] 有效地减少了部分积的个数,使用Wallace 树型结 构 [5] 缩短部分积压缩的时间,其算法较复杂,并且版图结构不 规则, 但可以有效地提升乘法器的性能。第29卷第5期2012年5月计算机应用研究 Application Research of Computers Vol.29No.5May 2012

计算机组成原理专周报告 成都电子机械高等专科学校计算机工程系

` 目录 一、项目名称 (1) 二、实验目的 (1) 三、不恢复余数的阵列除法器介绍 (1) 四、逻辑流程图及原理 (3) 算法流程 (3) 粗框图 (4) CSA逻辑结构图 (4) 原理分析 (5) 五、实例结果及求解过程 (8) 实例结果图 (8) 实例求解过程 (9) 六、心得体会: (10)

计算机组成原理专周报告 一、项目名称 原码阵列除法器 二、实验目的 1)理解原码阵列除法运算的规则。 2)掌握原码阵列除法器设计思想,设计一个原码阵列除法器。 3)熟悉proteus 7 professional软件的使用。 4)复习巩固课堂知识,将所学知识运用于实际,做到学以致用。三、不恢复余数的阵列除法器介绍 阵列式除法器是一种并行运算部件,采用大规模集成电路制造,与早期的串行除法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运算速度。阵列除法器有多种多样形式,如不恢复余数阵列除法器,补码阵列除法器等等。我们所用到的就是不恢复余数的阵列除法器。 设:所有被处理的数都是正的小数(仍以定点小数为例)。不恢复余数的除法也就是加减交替法。在不恢复余数的除法阵列中,每一行所执行的操作究竟是加法还是减法, 取决于前一行输出的符号与

被除数的符号是否一致。当出现不够减时,部分余数相对于被除数来说要改变符号。这时应该产生一个商位“0”,除数首先沿对角线右移,然后加到下一行的部分余数上。当部分余数不改变它的符号时, 即产生商位“1”,下一行的操作应该是减法。图(四)示出了 (4位÷4位)的不恢复余数阵列除法器的逻辑原理图。由图看出,该阵列除法器是用一个可控加法/减法(CAS)单元所组成的流水阵列来实现的。推广到一般情况,一个(n+1)位除(n+1)位的加减交替除法阵列由(n+1)2个CAS单元组成,其中两个操作数(被除数与除数)都是正的。单元之间的互连是用n=3的阵列来表示的。 这里被除数X是一个6位的小数(双倍长度值):X=0.A1A2A3A4A5A6它是由顶部一行和最右边的对角线上的垂直输入线来提供的。 除数Y是一个3位的小数:Y=0.B1B2B3 它沿对角线方向进入这个阵列。这是因为,在除法中所需要的部分余数的左移,可以用下列等效的操作来代替:即让余数保持固定,而将除数沿对角线右移。 商Q是一个3位的小数:Q=0.Q1Q2Q3 它在阵列的左边产生。 余数r是一个6位的小数:r=0.00r0r1r2r3 它在阵列的最下一行产生。

课程设计

教学院计算机学院 课程名称计算机组成原理题目4位乘法整列设计专业计算机科学与技术班级2014级计本非师班姓名唐健峰 同组人员黄亚军 指导教师 2016 年10 月 5 日

1 课程设计概述 1.1 课设目的 计算机组成原理是计算机专业的核心专业基础课。课程设计属于设计型实验,不仅锻炼学生简单计算机系统的设计能力,而且通过进行设计及实现,进一步提高分析和解决问题的能力。 同时也巩固了我们对课本知识的掌握,加深了对知识的理解。在设计中我们发现问题,分析问题,到最终的解决问题。凝聚了我们对问题的思考,充分的锻炼了我们的动手能力、团队合作能力、分析解决问题的能力。 1.2 设计任务 设计一个4位的二进制乘法器: 输入信号:4位被乘数A(A1,A2,A3,A4), 4位乘数B(B1,B2,B3,B4), 输出信号:8位乘积q(q1,q2,q3,q4,q5,q6,q7,q8). 1.3 设计要求 根据理论课程所学的至少设计出简单计算机系统的总体方案,结合各单元实验积累和课堂上所学知识,选择适当芯片,设计简单的计算机系统。 (1)制定设计方案: 我们小组做的是4位阵列乘法器,4位阵列乘法器主要由求补器和阵列全加器组成。 (2)客观要求 要掌握电子逻辑学的基本内容能在设计时运用到本课程中,其次是要思维灵活遇到问题能找到合理的解决方案。小组成员要积极配合共同达到目的。

2 实验原理与环境 2.1 1.实验原理 计算机组成原理,数字逻辑,maxplus2是现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 用乘数的每一位去乘被乘数,然后将每一位权值直接去乘被乘数得到部分积,并按位列为一行每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值,将各次部分积求和得到最终的对应数位的权值。 2.2 2.实验环境 2.2.1双击maxplu2II软件图标,启动软件 (1).新建工程,flie->new project ....,出现存储路径的选项框,指定项目保存路径并且为工程命名,第三行设置实体名,保持与工程名一致。点击OK

流水线乘法器 一般的快速乘法器通常采用逐位并行的迭代阵列结构,将每个操作数的N位都并行地提交给乘法器。但是一般对于FPGA来讲,进位的速度快于加法的速度,这种阵列结构并不是最优的。所以可以采用多级流水线的形式,将相邻的两个部分乘积结果再加到最终的输出乘积上,即排成一个二叉树形式的结构,这样对于N位乘法器需要log2(N)级来实现。一个8位乘法器,如图所示。 module mux_4(mul_a,mul_b,mul_out,clk,rst_n); parameter MUL_WIDTH = 4; parameter MUL_RESULT = 8; input [MUL_WIDTH-1:0] mul_a; input [MUL_WIDTH-1:0] mul_b; input clk; input rst_n; output [MUL_RESULT-1:0] mul_out; reg [MUL_RESULT-1:0] mul_out; reg [MUL_RESULT-1:0] stored0; reg [MUL_RESULT-1:0] stored1; reg [MUL_RESULT-1:0] stored2; reg [MUL_RESULT-1:0] stored3; reg [MUL_RESULT-1:0] add01; reg [MUL_RESULT-1:0] add23; always @(posedge clk or negedge rst_n) begin if(!rst_n) begin mul_out <= 8'b0000_0000;

stored0 <= 8'b0000_0000; stored1 <= 8'b0000_0000; stored2 <= 8'b0000_0000; stored3 <= 8'b0000_0000; add01 <= 8'b0000_0000; add23 <= 8'b0000_0000;; end else begin stored3 <= mul_b[3] ? {1'b0,mul_a,3'b0} : 8'b0; stored2 <= mul_b[2] ? {2'b0,mul_a,2'b0} : 8'b0; stored1 <= mul_b[1] ? {3'b0,mul_a,1'b0} : 8'b0; stored0 <= mul_b[0] ? {4'b0,mul_a} : 8'b0; add01 <= stored1 + stored0; add23 <= stored3 + stored2; mul_out <= add01 + add23; end end endmodule

沈阳航空工业学院 课程设计报告 课程设计名称:计算机组成原理课程设计课程设计题目:阵列除法器的设计 院(系):计算机学院 专业:计算机科学与技术 班级:7401101 学号:200704011004 姓名:刘慧 指导教师:施国君 完成日期:2010年1月15日

沈阳航空工业学院课程设计报告 目录 第1章总体设计方案 (1) 1.1设计原理 (1) 1.2设计思路 (2) 1.3设计环境 (3) 第2章详细设计方案 (6) 2.1顶层方案图的设计与实现 (6) 2.1.1创建顶层图形设计文件 (6) 2.1.2器件的选择与引脚锁定 (7) 2.1.3编译、综合、适配 (8) 2.2功能模块的设计与实现 (8) 2.3仿真调试 (10) 第3章编程下载与硬件测试 (12) 3.1编程下载 (12) 3.2硬件测试及结果分析 (12) 参考文献 (14) 附录(电路原理图) (15)

第1章总体设计方案 1.1 设计原理 阵列除法器的功能是利用一个可控加法/减法(CAS)单元所组成的流水阵列来实现的。它有四个输出端和四个输入端。当输入线P=0时,CAS作加法运算;当P=1时,CAS作减法运算。可控加法/减法(CAS)单元的逻辑电路图如图1.1所示。 图1.1可控加法/减法(CAS)单元的逻辑图 CAS单元的输入与输出关系可用如下一组逻辑方程来表示: S i=A i ⊕(B i ⊕P) ?C C i+1=(A i+C i) ?(B i ⊕P)+A i C i 当P=0时,就得到我们熟悉的一位全加器(FA)的公式: S i=A i ⊕B i ⊕C i C i+1=A i B i+B i C i+A i C i 当P=1时,则得求差公式: S i=A i ?B i '?C i C i+1=A i B i '+B i 'C i+A i C i 其中B i '=B i?1。 称为借位输出。 在减法情况下,输入C i称为借位输入,而C i +1

乘位阵列乘法器设计集团文件版本号:(M928-T898-M248-WU2669-I2896-DQ586-M1988)

课程设计报告课程设计题目: 4乘4位阵列乘法器设计 学生姓名:杨博闻 学号 专业:计算机科学与技术 班级: 1120701 指导教师:汪宇玲 2014年 1月 4日

一、设计目的 1.掌握乘法器的原理及其设计方法。 2 .熟练应用CPLD 设计及 EDA 操作软件。 二、设计设备 1.TDN-CM+或 TDN-CM++教学实验系统一套。 2 ·PC 微机一台。 3·ispDesignEXPERT 软件 模型机数据通路结构框图 三、设计原理 本实验用 CPLD 来设计一个 4 ×4 位乘法器,相对于画电路图输入,用 ABEL 语言描述是比较方便的。其算式如下(其中括号中的数字表示在 ABEL 源程序描述中的功能块调用编号): a3 a2 a1 a0 × b3 b2 b1 b0 ---------------------------------------------------------------------------------------------------------- a3b0(10) a2b0(6) a1b0(3) a0b0(1) a3b1(13) a2b1(9) a1b1(5) a0b1(2)

a3b2(15) a2b2(12) a1b2(8) a0b2(4) + a3b3(16) a2b3(14) a1b3(11) a0b3(7) ----------------------------------------------------------- ------------------------------------------------ p7 p6 p5 p4 p3 p2 p1 p0 四、设计步骤 1.安装EDA 软件 打开计算机电源,进入 Windows 系统,安装上述 ispDesignEXPERT 软件。安装完成后,桌面和开始菜单中则建有 ispDesignEXPERT 软件图 标。 2.用ispDesignEXPERT 软件根据上述乘法的逻辑原理用ABEL 语言 编写功能描述程序。 其在 1032 芯片中对应的管脚如图: 3.编辑、编译和下载 使用 ispDesignEXPERT 软件编辑源程序并进行编译,然后打开实验 系统电源,将生成的 JEDEC 文件下载到 ispLSI1032 中去。 4 .连接实验电路 按下图连接实验电路。 5 .给定操作数,观察乘法器输出 将 SWITCH UNIT 单元中的 SW-B、AR 开关置为低电平状态。在 INPUT DEVICE 单元中的 8 个开关的高 4 位为乘数 A ,低四位为被乘

目录 一、设计题目 (2) 二、设计目的 (2) 三、设计过程 (2) 3.1设计原理 (2) 3.2器件选择 (3) 3.3逻辑原理 (3) 3.4阵列乘法器的逻辑原理 (4) 3.5 时序图 (4) 四、设计心得 (5) 五、参考文献 (6)

4位阵列乘法器 一、设计题目4位阵列乘法器 二、设计目的 计算机组成原理是计算机专业的核心专业基础课。课程设计属于设计型实验,不仅锻炼学生简单计算机系统的设计能力,而且通过进行设计及实现,进一步提高分析和解决问题的能力。 同时也巩固了我们对课本知识的掌握,加深了对知识的理解。在设计中我们发现问题,分析问题,到最终的解决问题。凝聚了我们对问题的思考,充分的锻炼了我们的动手能力、团队合作能力、分析解决问题的能力。 三、设计过程 3.1设计原理 阵列乘法器是类似于人工计算(如图1.1所示)的方法,乘数与被乘数都是二进制数。所以可以通过乘数从最后一位起一个一个和被乘数相与,自第二位起要依次向左移一位,形成一个阵列的形式。这就可将其看成一个全加的过程,将乘数某位与被乘数某位与完的结果加上乘数某位的下一位与被乘数某位的下一位与完的结果再加上前一列的进位进而得出每一位的结果。 一个阵列乘法器要完成X.Y乘法运算(X=X4X3X2X1,Y=Y4Y3Y2Y1)。阵列的每一行送入乘数Y的每一位数位,而各行错开形成的每一斜列则送入被乘数的每一数位。阵列乘法器是由十六个模块组成,每一个模块构包括一个与门和一位全加器。 1 0 1 1 × 1 1 0 1 ________________ 10 1 1 00 0 0 1 0 1 1 1 0 1 1 ___________________________ 1 0 0 0 1 1 1 1 图1人工计算乘法示例

沈阳***** 课程设计报告 课程设计名称:计算机组成原理课程设计课程设计题目:阵列乘法器的设计 院(系):计算机学院 专业:计算机科学与技术 班级: 学号: 姓名: 指导教师: 完成日期:2007年1月7日

目录 第1章总体设计方案 (1) 1.1 设计原理 (1) 1.2 设计思路 (1) 1.3 设计环境 (1) 第二章详细设计方案 (2) 2.1顶层方案图的设计与实现 (2) 2.1.1创建顶层图形设计文件 (2) 2.1.2器件的选择与引脚锁定 (3) 2.1.3编译、综合、适配........................................................................ . (4) 2.2底层的设计与实现........................................................................ (4) 2.2.1阵列乘法器的设计与实现..................................... ................. .......... ................. (4) 2.3功能模块的设计与实现 (6) 2.4 仿真调试.................................................................................. (7) 第3章编程下载与硬件测试 (10) 3.1 编程下载 (10) 3.2 硬件测试及结果分析 (10) 参考文献 (12) 课程设计总结 (13)

1 `timescale1ns/1ps 2 ////////////////////////////////////////////////////////////////////////////////// 3 // Company: 4 // Engineer: 5 // 6 // Create Date: 21:30:18 10/13/2011 7 // Design Name: 8 // Module Name: Add_Tree8 9 // Project Name: 10 // Target Devices: 11 // Tool versions: 12 // Description: 13 // 14 // Dependencies: 15 // 16 // Revision: 17 // Revision 0.01 - File Created 18 // Additional Comments: 19 // 20 ////////////////////////////////////////////////////////////////////////////////// 21 module Add_Tree8(out,a,b,clk 22 ); 23 output[15:0]out; 24 input[7:0]a,b; 25 input clk; 26 27 wire[15:0]out; 28 wire[14:0]out1,c1; 29 wire[12:0]out2; 30 wire[10:0]out3,c2; 31 wire[8:0]out4; 32 33 reg[14:0]atemp; 34 reg[13:0]atemp1; 35 reg[12:0]atemp2; 36 reg[11:0]atemp3; 37 reg[10:0]atemp4; 38 reg[9:0]atemp5; 39 reg[8:0]atemp6; 40 reg[7:0]atemp7; 41 42 assign out1=atemp+atemp1; 43 assign out2=atemp2+atemp3; 44 assign out3=atemp4+atemp5; 45 assign out4=atemp6+atemp7; 46 assign c1=out1+out2; 47 assign c2=out3+out4; 48 assign out=c1+c2;

课程设计报告课程设计题目:4乘4位阵列乘法器设计 学生姓名:杨博闻 学号:201120070115 专业:计算机科学与技术 班级:1120701 指导教师:汪宇玲 2014年1月4日

一、设计目的 1.掌握乘法器的原理及其设计方法。 2 .熟练应用CPLD 设计及EDA 操作软件。 二、设计设备 1.TDN-CM+或TDN-CM++教学实验系统一套。 2 ·PC 微机一台。 3·ispDesignEXPERT 软件 模型机数据通路结构框图 三、设计原理 本实验用CPLD 来设计一个4 ×4 位乘法器,相对于画电路图输入,用ABEL 语言描述是比较方便的。其算式如下(其中括号中的数字表示在ABEL 源程序描述中的功能块调用编号):

a3 a2 a1 a0 ×b3 b2 b1 b0 ---------------------------------------------------------------------------------------------------------- a3b0(10) a2b0(6) a1b0(3) a0b0(1) a3b1(13) a2b1(9) a1b1(5) a0b1(2) a3b2(15) a2b2(12) a1b2(8) a0b2(4) +a3b3(16) a2b3(14) a1b3(11) a0b3(7) ----------------------------------------------------------------------------------------------------------- p7 p6 p5 p4 p3 p2 p1 p0 四、设计步骤 1.安装EDA 软件 打开计算机电源,进入Windows 系统,安装上述ispDesignEXPERT 软件。安装完成后,桌面和开始菜单中则建有ispDesignEXPERT 软件图标。 2.用ispDesignEXPERT 软件根据上述乘法的逻辑原理用ABEL 语言编写功能描述程序。 其在1032 芯片中对应的管脚如图: 3.编辑、编译和下载 使用ispDesignEXPERT 软件编辑源程序并进行编译,然后打开实验系统电源,将生成的JEDEC 文件下载到ispLSI1032 中去。 4 .连接实验电路 按下图连接实验电路。 5 .给定操作数,观察乘法器输出 将SWITCH UNIT 单元中的SW-B、AR 开关置为低电平状态。在INPUT

8位并行乘法器 在数字信号处理中,乘法器的速度对整个芯片以及系统性能有着重要影响。随着超大规模集成电路的发展,高速、低功耗、版图设计规则、占用芯片面积小等是乘法器研究的重点。 串行乘法器,通常是两个N位二进制数x、y的乘积用简单的方法计算就是利用移位操作来实现。但计算一次乘法需要8个周期,这种乘法器的优点是所占用的资源是所有类型乘法器中最少的,在低速的信号处理中有着广泛的应用,但是串行乘法器速度比较慢、时延大。 为了加快运算速度,一般的快速乘法器通常采用逐位并行的迭代阵列结构,将每个操作数的N位都并行地提交给乘法器。但是一般对于FPGA来讲,进位的速度快于加法的速度,这种阵列结构并不是最优的。所以可以采用多级流水线的形式,将相邻的两个部分乘积结果再加到最终的输出乘积上,即排成一个二叉树形式的结构,这样对于N位乘法器需要lb(N)级来实现。 一、VHDL代码 library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.STD_LOGIC_ARITH.all; use IEEE.STD_LOGIC_UNSIGNED.all;

entity chengfa is port( clk :in std_logic; a :in std_logic_VECTOR(7 downto 0); b :in std_logic_VECTOR(7 downto 0); cout:out std_logic_VECTOR(15 downto 0) ); end chengfa; architecture one of chengfa is signal a1,b1:std_logic_vector(3 downto 0); signal a2,b2:std_logic_vector(7 downto 4); signal cout1:std_logic_vector(15 downto 0); signal cout2:std_logic_vector(15 downto 0); signal a1b1,a2b1,a1b2,a2b2:std_logic_vector(15 downto 0); begin process(a,b,clk) begin if clk'event and clk='1' then a1b1<="0000"&(a(5 downto 0) *b(5 downto 0)); a2b1<="00"&(a(7 downto 6)*b(5 downto 0))&"000000"; a1b2<="00"&(a(5 downto 0)*b(7 downto 6))&"000000"; a2b2<=(a(7 downto 6)*b(7 downto 6))&"000000000000"; end if; end process; process(clk) begin if clk'event and clk='1' then cout1<=a1b1+a2b1; cout2<=a1b2+a2b2; end if; end process; process(clk) begin if clk'event and clk='1' then cout<=cout1+cout2; end if; end process; end one;