实验三:八位运算器组成实验

一:实验目的:

1:掌握运算器的组成原理、工作原理;

2: 了解总线数据传输结构;

3:熟悉简单的运算器的数据通路与控制信号的关系;

4:完成给定数据的算术操作、逻辑操作;

二:实验条件:

1:PC机一台;

2:MAX+PLUS软件;

三:实验内容(一)

1:所用到的芯片

74181 :四位算术逻辑运算单元;

74244:收发器(双向的三态缓冲器)

74273:八位D触发器;

74374 :八位D锁存器;

74163:八进制计数器;

7449: 七段译码器

2:实验电路图

(1)运算器电路图

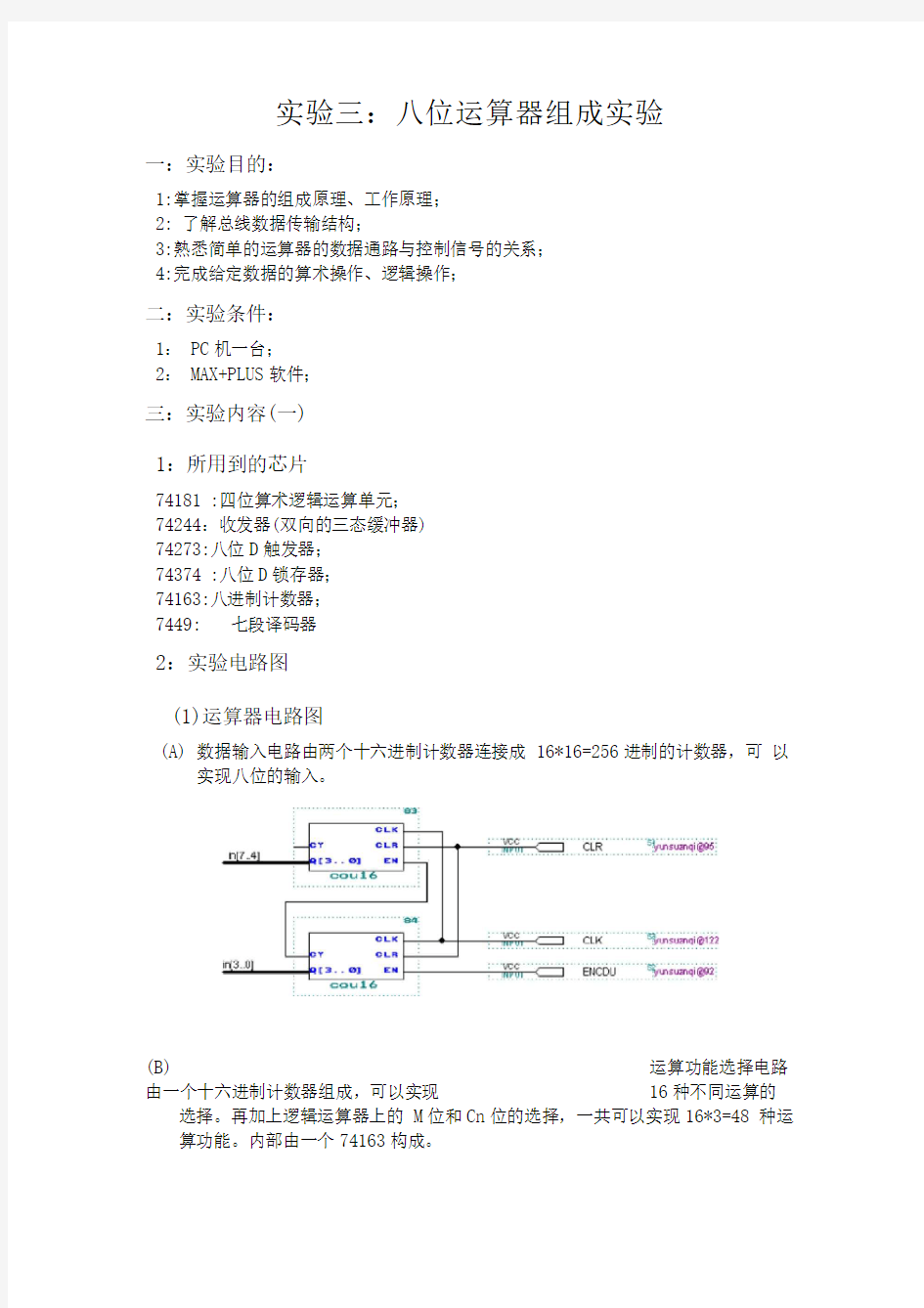

(A)数据输入电路由两个十六进制计数器连接成16*16=256进制的计数器,可以

实现八位的输入。

(B)运算功能选择电路由一个十六进制计数器组成,可以实现16种不同运算的选择。再加上逻辑运算器上的M位和Cn位的选择,一共可以实现16*3=48 种运算功能。内部由一个74163构成。

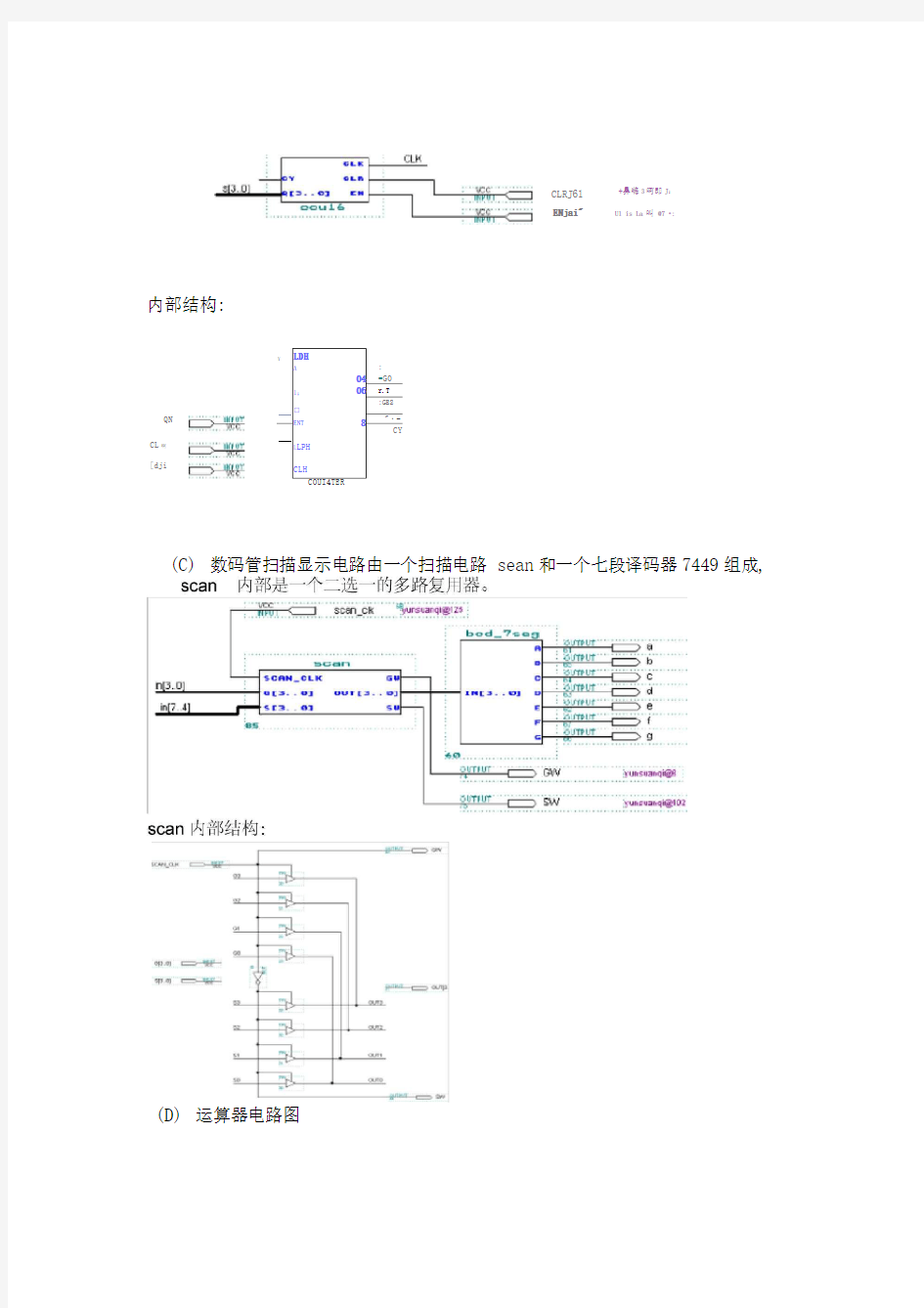

(C) 数码管扫描显示电路由一个扫描电路 sean 和一个七段译码器7449组成,

(D) 运算器电路图

CLRJ61

ENjai"

+鼻嗨3呵即J :

Ul is La 叫 @7 ?:

内部结构:

Y

LDH

A

:

04 =GO 1;

06 r.T

:GE2 — □

ENT

8

"?-

CY

—

L LPH

CLH

QN CL 啊 [dji

COUI4TER

AT. i

■ ^7

机UE

U O' oo o

丿」:.

,

3 " E

H

密

(2)波形仿真图

(A)输入两个数A=05H,B=0AH,O5H DR1,0AH> DR2,并通过经由74181在总线上显示。

10A 3n$

i^-CLK

rn

?ELCDU

Qt)(OllK)[Q3X?*X :S J OS J

0OOD Uli.'「II ;

70C Gn i

an I)in :i W-LDR5 ^R5 BUS ■?—LOOR? "-EN iei CLR.1E31

心 U] rT_a_r^ir^T_rLrLrLn_rLn_rLr^^

=! UUU1

1D1U

P 叩01

H

Lxnr-L^

— LDR4 Rd BUS LDDR1

、R1的猗人打弃]

E*? LDRS

1>-ALU_BJS 港总感输出FS4的蘇朿

X

ROD

l^CLR

—L3U5

一-crj trf-M —uj_iai _CLR_1E1

2 i[

3 0]

忖 nnim

■^CLK

]轻了41利的斬出打开