实验七 8位移位寄存器的设计

- 格式:docx

- 大小:1.22 MB

- 文档页数:8

实验七移位寄存器及其应用一、实验目的1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。

2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。

二、实验原理1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

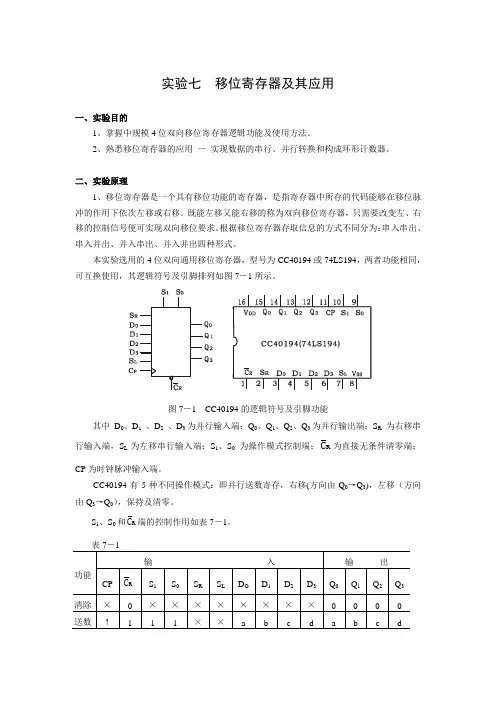

本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图7-1所示。

图7-1 CC40194的逻辑符号及引脚功能其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串C为直接无条件清零端;行输入端,S L为左移串行输入端;S1、S0为操作模式控制端;RCP为时钟脉冲输入端。

CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q0→Q3),左移(方向由Q3→Q0),保持及清零。

S1、S0和R C端的控制作用如表7-1。

2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。

本实验研究移位寄存器用作环形计数器和数据的串、并行转换。

(1)环形计数器把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图7-2所示,把输出端Q3和右移串行输入端S R 相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表7-2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。

图7-2 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。

8位移位寄存器

8位移位寄存器是一种能够存储和移位8位二进制数据的数字逻辑电路,它可以通过输入信号控制数据的输入、输出和移位操作。

一般来说,8位移位寄存器由8个触发器组成,每个触发器能够存储1位二进制数据。

这些触发器按照一定的顺序连接,并通过控制信号控制数据的流动。

8位移位寄存器常用的操作包括:

1. 并行加载(Parallel Load):将8位数据同时加载到寄存器中,可以通过输入信号将数据写入寄存器的每个触发器中。

2. 左移位(Left Shift):将寄存器中的数据向左移位,即每个触发器的输出信号连接到下一个触发器的输入信号。

3. 右移位(Right Shift):将寄存器中的数据向右移位,

即每个触发器的输出信号连接到上一个触发器的输入信号。

4. 输出数据(Output Data):将寄存器中存储的数据输出。

8位移位寄存器常用于串行数据传输、序列生成和控制逻辑等应用领域,可以通过组合逻辑电路实现不同的功能。

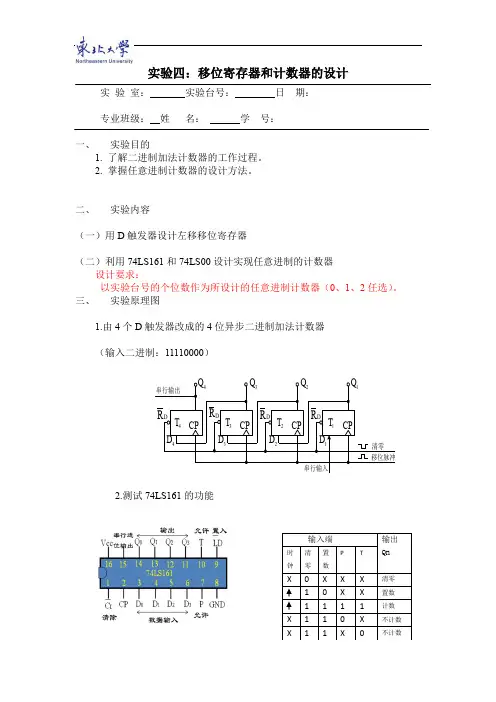

第1篇一、实验目的1. 理解时序电路的基本概念和组成,掌握时序电路的设计方法和分析方法。

2. 掌握计数器、寄存器、移位寄存器等时序电路的应用。

3. 熟悉FPGA开发环境,能够使用Quartus II设计工具进行时序电路的设计和仿真。

二、实验原理时序电路是数字电路中的一种重要电路,它能够根据输入信号的变化,产生一系列有序的输出信号。

时序电路主要由触发器、逻辑门和时钟信号组成。

1. 触发器:触发器是时序电路的基本单元,具有存储一个二进制信息的功能。

常见的触发器有D触发器、JK触发器、T触发器等。

2. 逻辑门:逻辑门用于实现基本的逻辑运算,如与、或、非、异或等。

3. 时钟信号:时钟信号是时序电路的同步信号,用于控制触发器的翻转。

三、实验内容1. 计数器设计(1)设计一个3位同步二进制加计数器。

(2)设计一个3位同步二进制减计数器。

2. 寄存器设计使用74LS74触发器设计一个双向移位寄存器。

3. 移位寄存器设计使用74LS74触发器设计一个单向移位寄存器。

4. 环形计数器设计使用74LS74触发器设计一个环形计数器。

5. 可控分频器设计使用Verilog HDL语言设计一个可控分频器,实现时钟信号的分频功能。

四、实验步骤1. 使用Quartus II设计工具创建工程,并添加所需的设计文件。

2. 根据实验原理,编写时序电路的Verilog HDL代码。

3. 编译代码,并生成测试平台。

4. 在测试平台上进行仿真,验证时序电路的功能。

5. 将设计下载到FPGA,进行硬件实验。

6. 记录实验结果,分析实验现象。

五、实验结果与分析1. 计数器实验结果(1)3位同步二进制加计数器:按照时钟信号的变化,计数器能够从000计数到111。

(2)3位同步二进制减计数器:按照时钟信号的变化,计数器能够从111减到000。

2. 寄存器实验结果使用74LS74触发器设计的双向移位寄存器,能够实现数据的左移和右移功能。

3. 移位寄存器实验结果使用74LS74触发器设计的单向移位寄存器,能够实现数据的左移功能。

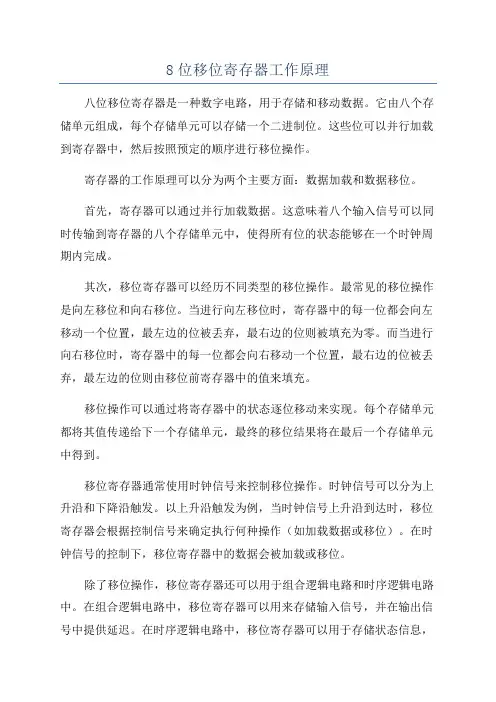

8位移位寄存器工作原理八位移位寄存器是一种数字电路,用于存储和移动数据。

它由八个存储单元组成,每个存储单元可以存储一个二进制位。

这些位可以并行加载到寄存器中,然后按照预定的顺序进行移位操作。

寄存器的工作原理可以分为两个主要方面:数据加载和数据移位。

首先,寄存器可以通过并行加载数据。

这意味着八个输入信号可以同时传输到寄存器的八个存储单元中,使得所有位的状态能够在一个时钟周期内完成。

其次,移位寄存器可以经历不同类型的移位操作。

最常见的移位操作是向左移位和向右移位。

当进行向左移位时,寄存器中的每一位都会向左移动一个位置,最左边的位被丢弃,最右边的位则被填充为零。

而当进行向右移位时,寄存器中的每一位都会向右移动一个位置,最右边的位被丢弃,最左边的位则由移位前寄存器中的值来填充。

移位操作可以通过将寄存器中的状态逐位移动来实现。

每个存储单元都将其值传递给下一个存储单元,最终的移位结果将在最后一个存储单元中得到。

移位寄存器通常使用时钟信号来控制移位操作。

时钟信号可以分为上升沿和下降沿触发。

以上升沿触发为例,当时钟信号上升沿到达时,移位寄存器会根据控制信号来确定执行何种操作(如加载数据或移位)。

在时钟信号的控制下,移位寄存器中的数据会被加载或移位。

除了移位操作,移位寄存器还可以用于组合逻辑电路和时序逻辑电路中。

在组合逻辑电路中,移位寄存器可以用来存储输入信号,并在输出信号中提供延迟。

在时序逻辑电路中,移位寄存器可以用于存储状态信息,并按照预定的时序进行移位操作。

这在时序电路中是非常重要的,因为它可以存储和传递状态信息,使电路能够在不同的时钟周期中正确地工作。

总结起来,八位移位寄存器是一种用于存储和移动数据的数字电路。

它由八个存储单元组成,采用并行加载和移位操作。

移位寄存器可以通过时钟信号来控制数据加载和移位操作,并在组合逻辑电路和时序逻辑电路中起着重要的作用。

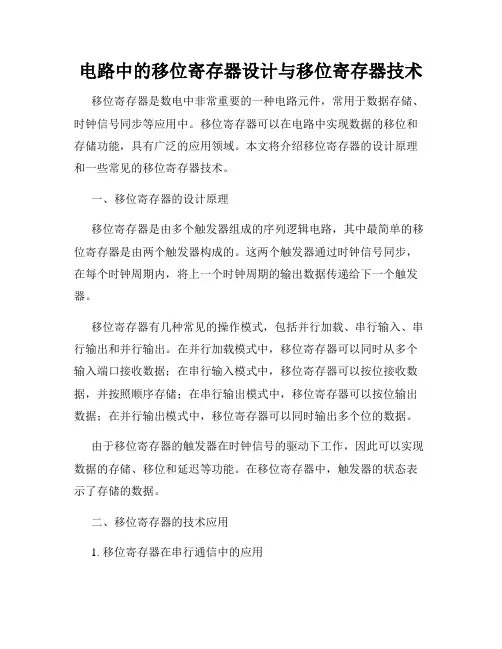

电路中的移位寄存器设计与移位寄存器技术移位寄存器是数电中非常重要的一种电路元件,常用于数据存储、时钟信号同步等应用中。

移位寄存器可以在电路中实现数据的移位和存储功能,具有广泛的应用领域。

本文将介绍移位寄存器的设计原理和一些常见的移位寄存器技术。

一、移位寄存器的设计原理移位寄存器是由多个触发器组成的序列逻辑电路,其中最简单的移位寄存器是由两个触发器构成的。

这两个触发器通过时钟信号同步,在每个时钟周期内,将上一个时钟周期的输出数据传递给下一个触发器。

移位寄存器有几种常见的操作模式,包括并行加载、串行输入、串行输出和并行输出。

在并行加载模式中,移位寄存器可以同时从多个输入端口接收数据;在串行输入模式中,移位寄存器可以按位接收数据,并按照顺序存储;在串行输出模式中,移位寄存器可以按位输出数据;在并行输出模式中,移位寄存器可以同时输出多个位的数据。

由于移位寄存器的触发器在时钟信号的驱动下工作,因此可以实现数据的存储、移位和延迟等功能。

在移位寄存器中,触发器的状态表示了存储的数据。

二、移位寄存器的技术应用1. 移位寄存器在串行通信中的应用在串行通信中,移位寄存器通常用于将并行数据转换为串行数据,或者将串行数据转换为并行数据。

例如,在串行通信中,发送方将并行数据按照顺序输入到移位寄存器中,然后按照位序输出,形成串行数据。

接收方则将串行数据输入移位寄存器,然后按照位序输出,得到并行数据。

2. 移位寄存器在计数器中的应用移位寄存器还可以用于设计计数器电路。

例如,4位移位寄存器可以用来实现二进制计数器,通过移位寄存器中的数据进行加法运算,实现数字的递增。

在计数器电路中,遇到溢出时,可以通过逻辑门电路实现循环计数。

3. 移位寄存器在状态机中的应用状态机是一种用于表示系统状态和状态转移的电路。

移位寄存器可以用来设计状态机中的状态寄存器,用于存储系统的状态。

在状态机中,根据输入信号和当前状态,移位寄存器可以将系统状态切换到下一个状态,并输出相应的控制信号。

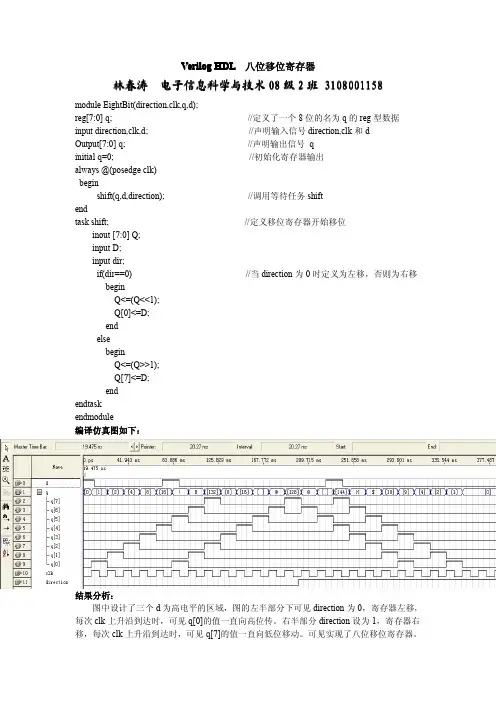

Verilog HDL八位移位寄存器

林春涛电子信息科学与技术08级2班3108001158

module EightBit(direction,clk,q,d);

reg[7:0]q;//定义了一个8位的名为q的reg型数据input direction,clk,d;//声明输入信号direction,clk和d

Output[7:0]q;//声明输出信号q

initial q=0;//初始化寄存器输出

always@(posedge clk)

begin

shift(q,d,direction);//调用等待任务shift

end

task shift;//定义移位寄存器开始移位

inout[7:0]Q;

input D;

input dir;

if(dir==0)//当direction为0时定义为左移,否则为右移

begin

Q<=(Q<<1);

Q[0]<=D;

end

else

begin

Q<=(Q>>1);

Q[7]<=D;

end

endtask

endmodule

编译仿真图如下:

结果分析:

图中设计了三个d为高电平的区域,图的左半部分下可见direction为0,寄存器左移,每次clk上升沿到达时,可见q[0]的值一直向高位传。

右半部分direction设为1,寄存器右移,每次clk上升沿到达时,可见q[7]的值一直向低位移动。

可见实现了八位移位寄存器。

移位寄存器设计范文首先,我们需要确定移位寄存器的移位方向。

移位方向可以是向左或向右。

考虑到数据在计算机系统中的存储方式,大多数情况下,移位方向选择向左移位。

向左移位意味着最左边的比特位将丢失,并在最右边填充一个新的比特位。

其次,我们需要确定移位寄存器的移位位数。

移位位数指的是在一次移位操作中,需要将存储的数据向左或向右移动的比特位数。

移位位数可以是固定的,也可以由外部输入决定。

在移位位数固定的情况下,我们需要确定移位寄存器中的存储单元数目,以满足预定的移位位数需求。

接下来,我们需要设计移位寄存器的输入/输出接口。

输入接口用于将数据加载到移位寄存器中,输出接口用于从移位寄存器中获取移位后的数据。

对于输入接口,可以采用并行输入或串行输入方式。

并行输入方式需要多个输入引脚,每个引脚对应一个比特位。

串行输入方式只需一个输入引脚,输入数据从一个比特位依次输入。

对于输出接口,同样可以采用并行输出或串行输出方式。

最后,我们需要考虑移位寄存器的时序控制。

时序控制指的是对移位操作的时钟信号进行控制。

通常情况下,移位寄存器的移位操作都是在时钟的上升沿或下降沿触发的。

可以通过时钟信号对存储单元进行同步操作,确保移位寄存器能够按照设计要求正确地进行移位操作。

综上所述,设计一个移位寄存器需要考虑移位方向、移位位数、输入/输出接口和时序控制等因素。

通过合理设计这些因素,可以实现一个高效、可靠的移位寄存器,满足各种应用场景中的需求。

寄存器与移位寄存器的设计与应用寄存器是计算机系统中重要的存储器件,用于存储和传输数据。

同时,移位寄存器是寄存器的一种常见类型,它具有特殊的移位功能。

本文将对寄存器和移位寄存器的设计与应用进行探讨。

一、寄存器的设计与功能寄存器是一种用于存储和传输数据的存储器件,常见的寄存器有通用寄存器、程序计数器(PC)、指令寄存器(IR)等。

寄存器通常由触发器(flip-flop)构成,不同位数的寄存器可以存储不同位数的数据。

寄存器的设计与功能需根据具体应用场景进行确定。

例如,通用寄存器一般用于数据传输和运算操作,可以保存中间结果和临时数据。

而PC寄存器用于指示程序执行的位置,IR寄存器则用于存储当前执行的指令。

二、移位寄存器的设计与功能移位寄存器是一种特殊的寄存器,它具有位移(移位)功能。

常见的移位寄存器有移位寄存器、移位寄存器带有并行载入功能的移位寄存器等。

移位寄存器可以向左或向右移动数据位,常用的移位操作有逻辑左移(<<)、逻辑右移(>>)、算术左移(<<<)、算术右移(>>>)等。

移位操作可以用于数据的扩展、压缩、循环移位等场景。

在实际应用中,移位寄存器常用于数据的串行传输、数据的并行/串行转换等信息处理任务。

通过移位寄存器,可以有效地对数据进行处理和操作。

三、寄存器与移位寄存器的应用寄存器和移位寄存器在计算机系统中有广泛的应用。

以下列举几个常见的应用场景。

1. 数据存储和传输寄存器可以作为临时存储器,保存运算结果和中间数据。

通过寄存器的传输功能,可以在处理器和存储器之间进行数据的传递。

2. 状态存储寄存器可以用于存储和切换系统的状态。

例如,标志寄存器(Flag Register)用于存储程序运行的状态标志,如零标志、进位标志等。

3. 数据处理移位寄存器可以用于数据的扩展、压缩和转换。

通过适当的移位操作,可以对数据进行位操作,实现数据的处理和运算。

8位移位寄存器工作原理

8位移位寄存器是由8个触发器组成的寄存器,在每个时钟周期内,输入数据会从最低位依次向左移位,最高位的数据会被丢弃,同时新的数据会从最低位进入。

移位寄存器的工作原理如下:

1. 初始化:将所有触发器的输出设置为0,清除寄存器中的数据。

2. 输入数据:将要存储的数据输入到最低位的触发器。

3. 移位操作:在每个时钟周期内,触发器中的数据依次向左移动一位。

每个触发器的输入会接收相邻右侧触发器的输出,最右侧的触发器接收输入数据。

最左侧的触发器数据会被丢弃。

4. 输出数据:寄存器中最右侧的触发器的输出数据即为最后输入的数据。

通过不断重复移位操作,可以实现将多个数据存储在移位寄存器中,并按照一定顺序输出。

移位寄存器常用于数据的串行传输、并行-串行数据转换、移位操作等场合。

它的工作原理简单且可靠,具有较高的数据传输速率和可扩展性。

实验八移位寄存器逻辑功能测试及应用一、实验目的:1、掌握中规模4位双向移位寄存器逻辑功能及使用方法;2、熟悉移位寄存器的应用一一构成环形计数器和实现数据的串行、并行转换。

二、实验原理:移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

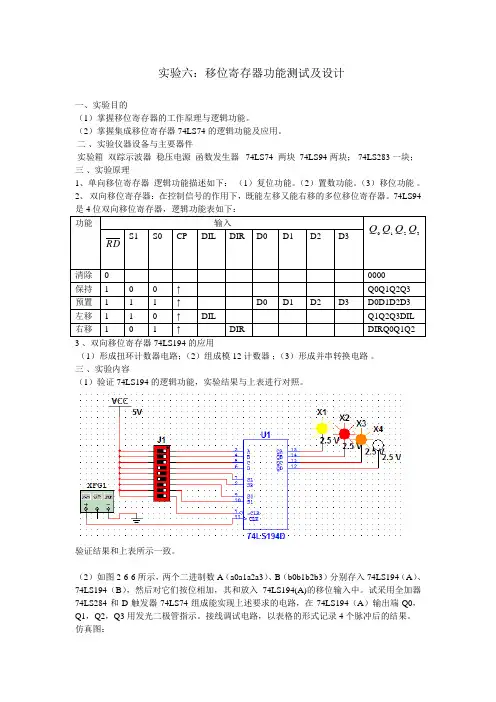

本实验选用的4位双向移位寄存器,型号为74LS194,其引脚排列如图11 —1所示。

移位寄存器不仅可以组成串行一并行数码转换器,还可以方便地组成移位寄存器型计数器、脉冲分配器等电路。

常用的移位寄存器有环行计数器和扭环型计数器。

图11 —1 74LS194引脚排列及功能三、实验仪器及器材:实验仪器设备:DGJ —2型电工技术实验装置(D71 —2数电实验挂箱)集成块:74LS194 74LS04四、实验内容与步骤:1、验证移位寄存器74LS194的逻辑功能:计数脉冲由单次脉冲源提供,清零端上,、工作状态控制端M1 M2、并行数据输入端D 0—D3、DS L为左移串行数据输入端、DS R右移串行数据输入端分别接逻辑电平开关,输出端Q o—Q3均接逻辑电平显示。

按如下逐项测试并判断该集成块的功能是否正常。

(1)异步清零功能:当-I,=o时,这时Q3Q2Q1Q O=OOOO,双向移位寄存器清零。

其它输入信号都不起作用,与CP无关,故称为异步清零。

(2)保持功能:当-上=1,且CP=0或M1 =M2=0时,双向移位寄存器保持状态不变。

(3)同步并行送数功能:当_t.=1,M1 =M2=1时,在CP上升沿操作下,并行输入数据d3 d2 d1 d0 送入寄存器。

(4)右移串行送数功能:当-h=1,M1 =0、M2=1时,在CP上升沿操作下,可依次把加在讣端的数据从时钟触发器行送入寄存器中。

(5)左移串行送数功能:当 -上=1,M1 =1、M2=0时,在CP上升沿操作下,可依次把加在DS L端的数据从时钟触发器串行送入寄存器中。

实验五寄存器电路设计1.画出74ls74构成的4位单向移位寄存器并说明其工作原理。

74ls74是由四个D触发器串联而成的四位单向移位寄存器。

移位寄存器使其中所储存的二进制,在一位脉冲的作用下左右移动;一位触发器可以储存1位二进制代码,存放n位二进制就需要n个触发器构成。

2.8位移位寄存器设计原理图。

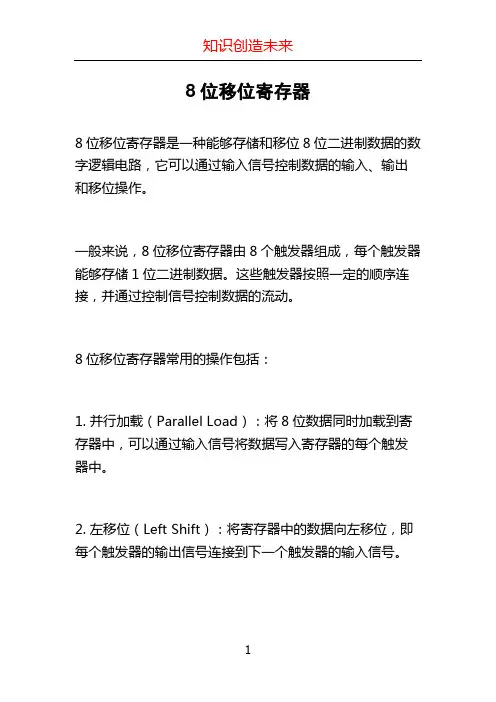

实验五寄存器电路设计一、实验目的l、掌握寄存器的工作原理、测试和分析其工作状态2、掌握集成双向移位寄存器和并行数据锁存器的功能及使用方法3、8位移位寄存器电路设计二、实验内容及步骤1、并行输入/并行输出寄存器功能测试表5.12、移位寄存器功能测试(1)用74LS74构成的4位单向移位寄存器表5.2(2) 74LSl94表5.3S1S0CP Dsr Dsl I3I2I1I0Q3Q2Q1Q0 0X X X X X X X X X00001X X0X X X X X X0000111X X d3d2d1d0d3d2d1d01011X X X X X11111010X X X X X0000110X1X X X X1111110X0X X X X0000100X X X X X X X00003、8D锁存器功能测试表5.4E D7D6D5D4D3D2D1D0Q7Q6Q5Q4Q3Q2Q1Q0 001011011000000000 011011011010110110 00011101100111011 01100010011000100 1X X X X X X X X X00000000注: “个”表示单脉冲上升沿4、8位移位寄存器电路设计(如不够可自行加纸)自制表格:Cr S1 S0 CP Dsr Dsl I3 I2 I1 I0 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q00 X X X X X X X X X 0 0 0 0 0 0 0 01 X X 0 X X X X X X 0 0 0 0 0 0 0 0 1 1 1 ↑X X 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 ↑0 X X X X X 0 0 0 0 0 0 0 0 1 0 1 ↑ 1 X X X X X 1 1 1 1 1 1 1 1 1 1 0 ↑0 X X X X X 0 0 0 0 0 0 0 0 1 1 0 ↑ 1 X X X X X 1 1 1 1 1 1 1 1 1 0 0 X X X X X X X 0 0 0 0 0 0 0 0实验仿真图:实验原理:实验主要用到用两片74LS194芯片构成8位移步寄存器。

技术与应用tougao1@77OCT 2018 NO.19Mixly开源项目设计27:移位寄存器(二)——8位二进制计数器和流水灯隋杰峰 山东省威海市乳山市畅园学校信息技术实验上一期,我们介绍了通过74HC595移位寄存器只用UNO 的3个管脚就可以控制8个LED的亮灭。

本期,我们将进一步介绍74HC595的一些应用,将分别做一个8位二进制计数器和一个流水灯项目。

在元件的使用和电路的连接上,依然沿用上一期的元件和电路。

● 需要的元件(如表1)● 电路连接(如图1)● 程序设计1.8位二进制计数器上一期的文章介绍了在shiftOut模块中输入数值,控制8个LED亮灭的过程,实际上,就是将十进制的数值转换为8位二进制,依次送入移位寄存器,明白了这个过程,就可以设计一个程序,来展现二进制进位了,程序如图2所示。

我们来解释一下这个程序:首先声明一个变量i为整数,并赋值为0;然后是一个for循环模块,让i 依次(步长为1)取从0到255的值,即第一次取值0,第二次取值1,第三次取值2……第256次取值255;接着就是我们熟悉的模块,在上一期,我们用它来控制了8个LED 的亮灭;最后延时200毫秒,作用是让每一次输入数值后,LED亮灭的状态保持200毫秒。

上传程序后,我们就可以看到L E D从全灭到全亮的过程,LED从右往左开始被点亮,它们每200毫秒变化一下,相当于从二进制00000000每次加1,一直加到11111111,再重新开始,如此重复表1图1 电路图图2 程序4(8位二进制计数器程序)技术与应用tougao1@78中国信息技术教育本案例的分享视频将会在以下公众号中陆续登载。

执行。

2.流水灯如果要设计一个流水灯,只需要将下面的二进制数一个个输入即可,为了方便,我们可以将它们转换成十进制或者十六进制放到数组里(如表2)。

以十进制为例,流水灯程序如图3所示。

上面的程序采用了数组,依次取出数组mylist中的8个数值,转换为二进制输入移位寄存器,就实现了流水灯的效果。

实验七 8位移位寄存器的设计

一、实验目的

熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言设计一个8位移位寄存器

二、实验内容

1.用VHDL语言设计由边沿触发式D触发器构成的8位移位寄存器,并进行仿真与分析;

三、实验原理

1.(1)8位移位寄存器逻辑电路的原理:

可以实现串行输出、并行输入,串行输出的功能。

是能暂时存放二进制码的电路,被广泛的应用于各类数字系统和数字计算机中。

寄存器的特点是存数方便。

abcdefgh为8个并行输入端,qa~qh为并行输出端,srsi为右移串行输入端,slsi为左移串行输入端,s1,s0为模式控制端,clrn为异步清零端,clk为时钟脉冲输入端

(2)通过实验实现逻辑的原理:

输入信号输出信

号

clk clrn S1 S0 sl sr abcdef

gh Q_abcde

fgh

↑1 1 1 0 0 000011

11

00001111

↑ 1 1 0 1 0 000011

11

00011111 ↑ 1 1 0 1 0 000111

11

00111111 ↑ 1 1 0 0 0 001111

11

01111110 ↑ 1 1 0 0 0 0111111

11111100 ↑ 1 0 0 0 0 1111110

11111100 ↑ 1 0 1 0 1 1111110

11111110 ↑ 1 0 1 0 1 1111111

11111111 ↑ 1 0 1 0 0 1111111

1

01111111 ↑ 1 0 1 0 0 0111111

1

00111111

↑0 0 0 0 0 001111

11 0000000

四、实验方法与步骤

实验方法:

采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

实验步骤:

1、编写源代码。

打开QuartusⅡ软件平台,点击File中得New建立一

个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件。

VHDL设计源代码如下:

2、按照实验箱上FPGA的芯片名更改编程芯片的设置。

操作是点击Assign/Device,选取芯片的类型“Altera的EPF10K20TI144_4”

3、编译与调试。

确定源代码文件为当前工程文件,点击Complier进行文件编译。

编译结果有错误或警告,则将要调试修改直至文件编译成功。

4、波形仿真及验证。

在编译成功后,点击Waveform开始设计波形。

点击“insert the node”,按照程序所述插入clrn,clk,s0,s1,sl,sr,a,b,c,d,e,f,g,h,qa,qb,qc,qd,qe,qf,qg,qh共22个节点(clrn,clk,s0,s1,sl,sr, a,b,c,d,e,f,g,h为输入节点,qa,qb,qc,qd,qe,qf,qg,qh为输出节点)。

设置s0,s1,sl,sr以不同的信号输入,abcdefgh输入初始数据,clk为时钟信号,点击保存按钮保存。

然后进行功能仿真,选择菜单Processing->Generate Functional Netlist 命令产生功能仿真网表,选择菜单Assignments-->Setting下拉列表中选择Simulator input ,在右侧的Simulation mode下拉列表中选择Functional,完成设置;选择菜单中的Processing->Start Simulation启动功能仿真,然后查看波形报告中的结果

5、时序仿真。

首先进行全编译,编译成功后,点击Assignments 的settings 的simulation mode:Timing,仿真成功后即出带延时的波形图。

6、FPGA芯片编程及验证。

(1)分配管脚:assignment—>Pins在Location中选择合适的输入输出管脚并进行编译。

(2)下载验证:Tools->Programmer进入下载窗口Hardware Setup

—>ByteBlaster->Start->OK

(3)初始化电路,根据设置好的管脚资源擦做实验电路板,完成数据测试。

五、实验结果与分析

1、编译过程

a)编译过程、调试结果

b)结果分析及结论:编译无错误,可进行下一步

2、功能仿真

a)功能仿真过程及仿真结果

b)结果分析及结论:

最开始是清零;

置数:当clrn=1时,S=11,输入01010101,输出01010101;

再清零,

右移:当S=01时,slsr=01时补1,因此输出10000000;

slsr=10时补0,因此输出01000000;

左移:当S=10时,slsr=10时补1,输出为10000001;

slsr=01补0,输出为00000010;

slsr=10时补1,输出为00000101;

3、时序仿真

a)时序仿真过程及仿真结果

b)结果分析及结论:仿真结果与逻辑存在偏差,因为时序仿真存在延迟现象,是正常现象。

4、Programming芯片编程

a)芯片编程过程

b)编程芯片FPGA验证结果

b)结果分析与结论

按图示顺序为

右移补一:

清零:

置数为01010101:

由于没有在代码中加入保持的代码,所以不能抓拍到所有的结果,信号变化的太快。

六、实验结论

1.实验结论:成功参照74198芯片,用VHDL语言设计由边沿触发式D 触发器构成的8位移位寄存器,并进行仿真与分析;根据功能仿真和时序仿真的波形图显示成功,且下载成功。

2.实验心得:移位寄存器通过对数据的移动来储存数据,存数方便,但是范围较小,要弄懂移位寄存器的原理首先要搞懂它的逻辑功能表,如此才能在仿真过程中了解结果的正确与否,然后有一段缺陷是没有在代码中加入保持的功能,在下载时结果变化的太快,导致不能抓拍到所有的变化结果。

下载过程耗费了太多的时间,都是自己不熟悉过程导致的。

以后会多加练习下载这一部分。