JTAG接口引脚定义

- 格式:doc

- 大小:185.00 KB

- 文档页数:3

并口与连接1.并行口基地址:0x0378 新系统通用,通常是LPT1,也可以是LPT2,通常使用中断IRQ70x0278 通常是LPT2,也可以是LPT1,LPT3(只能用此基地址),通常使用中断IRQ5 2.寄存器定义3.状态寄存器(379)和控制寄存器(37A)的定义:5.连接方式a)hybus255与并口的连接是通过74CH541与并口连接LPT D0 Pin 2 and TCK J10 Pin 4LPT D1 Pin 3 and TDI J10 Pin 11LPT D2 Pin 4 and TMS J10 Pin 9LPT Busy Pin 11 and TDO J10 Pin 13b)2410以及44b0连接图TCK---------------->DATA0TDI---------------->DATA1TMS---------------->DATA2TDO---------------->STATUS76.寄存器的读写a)先对控制寄存器(Control)初始化如果禁止中断用out(37A,0x80),如果使用中断用out(37A,0x90)b)写一个寄存器的两条基本指令:out(37B,addr);// 将addr写入用户设备地址寄存器写:out(37C,data);// 将数据data写入addr指向的用户设备空间单元读:in(37C);// 从addr指向的用户设备空间单元中读取数据JTAG接口信息1.TCK:输入移位时钟TMS和TDI的数据在TCK的上升沿被采样数据在时钟的下降沿输出到TDO2.TMS:输入方式选择TMS用于控制TAP状态机3.TDI:输入。

输入到指令寄存器IR或数据寄存器DR的数据出现在TDI输入端在TCK的上升沿被采样4.TDO:TDO输出来自指令寄存器或数据寄存器的数据在时钟的下降沿被移出到TDOTAP状态机*状态机框图中位于箭头旁边的数字表示TCK变高时TMS的逻辑状态JTAG时序1.TAP复位时序在hybus255-Jflash中void test_logic_reset(void){putp(1,1,IGNORE_PORT); // keep TMS set to 1 force a test logic resetputp(1,1,IGNORE_PORT); // no matter where you are in the TAP controller putp(1,1,IGNORE_PORT);putp(1,1,IGNORE_PORT);putp(1,1,IGNORE_PORT);putp(1,1,IGNORE_PORT);}2.IR,DR扫描时序。

AVR单片机JTAG接口的使用方法AVR单片机JTAG(Joint Test Action Group)接口是一种用于单片机的调试和编程工具。

它提供了一种高效的方式来进行硬件调试、固件编程和软件调试。

在本文中,我将详细介绍AVR单片机JTAG接口的使用方法。

1.JTAG接口简介JTAG接口由四条线组成,分别是TCK(时钟线)、TMS(状态线)、TDI(数据输入线)和TDO(数据输出线)。

它是一种串行接口,用于与其他外设进行通信。

JTAG接口能够通过硬件调试、固件编程和软件调试来提高系统调试的效率。

2.JTAG接口的初始化在使用JTAG接口之前,需要对其进行初始化。

首先,需要确定使用的JTAG接口类型,然后根据类型选择与之匹配的调试工具和软件。

接下来,需要连接JTAG接口的四个引脚到单片机的相应引脚上。

通常,这些引脚在单片机的数据手册中有详细的说明。

3.JTAG接口的连接连接JTAG接口的四个引脚到单片机的相应引脚上,确保连接正确无误。

通常,TCK(时钟线)和TMS(状态线)引脚是共享的,它们分别连接到单片机的相应引脚上。

TDI(数据输入线)和TDO(数据输出线)引脚则是分别连接到单片机的相应引脚上。

请务必根据单片机的数据手册正确连接JTAG接口引脚。

4.JTAG接口的编程在使用JTAG接口进行编程之前,需要确保已经安装了合适的调试工具和软件。

这些工具和软件可以帮助我们完成对单片机的编程操作。

通常,这些工具和软件提供了一些简单的命令和接口,用于与单片机进行通信。

通过这些命令和接口,我们可以读取和写入单片机的内部寄存器,从而实现对单片机的编程操作。

5.JTAG接口的调试使用JTAG接口进行调试可以帮助我们找到系统中的错误和问题。

通过读取和写入单片机的内部寄存器,我们可以查看程序的执行状态、输入和输出数据、栈的使用情况等信息。

通过这些信息,我们可以判断程序中的错误和问题,并进行调试操作。

6.JTAG接口的注意事项在使用JTAG接口之前-确保JTAG接口的引脚连接正确无误,避免引脚连接错误导致的通信问题。

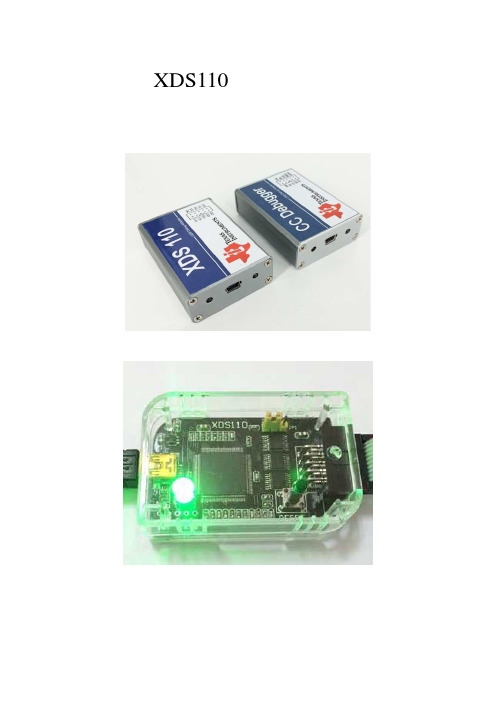

XDS110使用说明书

一、简介

XDS110是XDS100V1/V2/V3的升级版,编程速度比XDS100有很大的提升,并集成了虚拟串口和SWO调试功能,这些都是XDS100没有的。

二、XDS110硬件连接

1、JTAG编辑接口的硬件连接

TI的很多ARM内核芯片都采用JTAG编程接口,采用JTAG编程接口的硬件连接如下图所示:

上图中目标芯片的引脚需要根据具体使用的芯片型号和封装,查找数据手册找到对应的引脚,如CC1310的2个封装的JTAG引脚如下图所示:

CC2630/CC2640/CC2650芯片不同封装的JTAG引脚如下:

2、在程序调试或应用中有时候我们需要用到虚拟串口功能,XDS的虚拟串口连接如下图所示:

XDS110接到电脑有将有2个虚拟的串口号,注意使用串口功能时主要选择XDS110 Class Application/User UART(COMx)这个串口号,如下图所示:

3. XDS110具有SWO调试接口,接线方法如下

注意使用SWO功能时主要选择XDS110 Class Auxiliary Data Port(COMx)这个串口号,如下图所示:

三、使用Flash Programmer 2进行编程

1. 使用Flash Programmer 2软件配合XDS110进行编程如下:

2. IAR使用XDS110进行仿真的设置如下:。

JTAG电路设计规范JTAG(Joint Test Action Group,联合测试动作小组)是一种用于测试和调试电子设备的标准接口。

它提供了一种在生产过程中、产品调试阶段和维护过程中进行测试和调试的标准方法。

为了确保JTAG电路的设计和实施的可靠性和稳定性,有以下设计规范需要遵守:1.电路连接:JTAG端口应直接连接到目标电路中,以避免电路复杂性和信号干扰。

在设计过程中,需要考虑JTAG端口与目标电路之间的物理布局和布线。

2.电路保护:为了防止静电和电磁干扰对JTAG电路造成损害,应采用适当的电路保护措施,如静电保护器、电流限制器等。

3.电源和信号隔离:JTAG电路应与目标电路之间有适当的电源和信号隔离,以保护JTAG电路免受目标电路中的噪声和干扰。

4.信号过滤和补偿:为了降低信号干扰和噪声对JTAG信号的影响,需要在JTAG电路中添加滤波器和补偿电路。

5.时序和时钟管理:在设计JTAG电路时,需要遵守JTAG时序和时钟要求,以确保正确的数据传输和操作。

6.节点连接和映射:在设计JTAG电路时,需要正确配置和映射JTAG 节点和目标电路中的节点,以实现正确的测试和调试功能。

7.信号线长度匹配:为了确保信号传输的准确性和可靠性,需要对JTAG信号线的长度进行匹配和校准。

8.建立和保持时间:在设计JTAG电路时,需要考虑建立和保持时间要求,以确保正确的数据传输和操作。

9.引脚定义和约束:在设计JTAG电路时,需要与目标电路的开发人员和测试人员合作,定义和约束JTAG引脚的功能、命名和使用方法。

10.布局和地面规划:在设计PCB布局时,需要合理安排JTAG电路和地面,以降低电磁干扰和信号串扰。

11.热管理和散热设计:在设计JTAG电路时,需要考虑散热和热管理问题,以确保JTAG电路的稳定性和可靠性。

总的来说,JTAG电路的设计应遵循准确、可靠、稳定和简化的原则。

这需要对电路连接、保护、信号过滤、时序、节点映射、信号线匹配、建立和保持时间、引脚定义、布局和散热等方面进行综合考虑和设计。

JTAG使用说明JTAG使用说明遵循JTAG的器件包含以下几个管脚TCK 测试时钟输入,它和系统时钟不同TDI测试数据输入,通过它数据移位进入器件TDO测试数据输出,通过它数据从器件移出TMS测试模式选择,在JTAG规范中TMS命令选择测试模式TRST测试复位输入,它为TAP控制器提供异步初始化器件的测试支持功能是通过TAP控制器来实现的。

TAP是一个状态机,它控制控制所有相关操作,每种遵循JTAG的器件都有自己的TAP控制器,通过TCK和TMS可以使状态机内部的状态发生变化,从而支持诸如断点、单步、内部观察等调试工作。

本章针对ARM7TDMI介绍调试结构。

ARM的调试体系采用协议转换器来使调试器通过JTAG与ARM核直接通信。

前面JTAG标准中提到的扫描链功能是测试用,这里把它作为调试用:捕获数据总线上的信号并向内核或存储器插入新的信息。

ARM7TDMI-S核内具有EmbeddedICE逻辑,EmbeddedICE逻辑提供对片内调试的支持。

调试指令直接通过扫描链插入ARM内核并执行。

根据插入调试指令的不同,内核可以处于观察、保存或改变状态。

ARM的调试体系可以使程序指令执行速度处于调试速度或全速运行。

在ARM中采用JTAG的特点是:通过JTAG接口可以观察ARM内核状态和系统状态(注意:系统状态包括片内外设,不同于内核状态);不占用额外的目标系统资源;提供传统的断点访问和观察点访问;不再需要另外的UART 端口来和监控程序通信。

围绕ARM内核有两个扫描链:围绕整个内核外围的一个扫描链以及仅仅覆盖数据总线和断点的扫描链。

由于后者的链比较短,从而使调试指令和数据可以快速插入内核,避免了额外的时间ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?下图是JTAG接口的信号排列示意:接口是一个20脚的IDC插座。

1.下载口。

JTAG下载接口,对应下载的文件是SOF文件,速度快,JTAG 将程序直接下载到FPGA中,但是掉电程序丢失,平时学习推荐使用JTAG方式,最后固化程序的时候再通过AS方式将程序下载到配置芯片中即可;AS下载接口,对应下载的是POF文件,速度相对较慢,需要重新上电并且拔掉下载线,才能工作,操作相对麻烦,不推荐学习的时候使用。

2.FPGA引脚作用:(1)VCCINT:这些都是内部逻辑阵列电源电压引脚。

VCCINT还可以给输入缓冲区供电,用于LVPECL,LVDS(常规I / O和CLK引脚),差分HSTL,差分SSTL I/ O标准。

Connect all VCCINT pins to 1.2 V. Decoupling depends on the design decoupling requirementsof the specific board.所有VCCINT引脚连接至1.2 V,去耦依赖于设计脱钩的要求的具体电路板。

(2)VCCIO[1…8]: 这些I / O电源电压引脚银行1至8。

每个组可以支持不同的电压水平。

VCCIO供电到输出缓冲区,所有的I / O标准。

VCCIO供电输入缓冲区用于LVTTL,LVCMOS,1.5-V,1.8 V,2.5 V,3.3 V PCI,和3.3-V PCI-X,差分SSTL。

差分HSTL。

和LVDS lrecular我/ OL I / O标准。

验证VCCIO电压等级连接是与QuartusII软件的引脚连接一致。

去耦取决于设计去耦的具体要求的具体电路板。

(3)VREFB[1..8]N[0..3]: 为每个I / O组的输入参考电压。

这些引脚被用来作电压参考引脚。

如果没有被用,就作为普通的I/O引脚。

(4)VCCA PLL[1..4]: 模拟电源锁相环[1 ..4].将这些引脚连接到1.2 V,即使不使用PLL。

更好的,使用一个孤立的线性电源钳工性能。

10 pin jtag线束定义

10针JTAG线束是一种用于连接JTAG(联合测试行动组)接口的线束,通常用于与嵌入式系统和电子设备进行通信和调试。

这种线束通常由10根导线组成,每根导线都有特定的功能和定义。

以下是10针JTAG线束的常见定义:

1. TCK(测试时钟),用于提供时钟信号,驱动测试操作的时序。

2. TMS(测试模式选择),用于选择JTAG的操作模式,例如移动到下一个状态或者退出测试模式。

3. TDI(测试数据输入),用于输入测试数据或指令到被测设备中。

4. TDO(测试数据输出),用于输出来自被测设备的测试数据或状态信息。

5. TRST(测试复位),可选引脚,用于对被测设备进行复位。

6. 供电引脚(VCC),用于提供电源给被测设备。

7. 地线引脚(GND),用于连接被测设备的地线。

8. 保留引脚,有些10针JTAG线束可能会包含一些保留的引脚,用于未来的扩展或特定功能。

9. 保留引脚,另一个保留的引脚,用于未来的扩展或特定功能。

10. 保留引脚,第三个保留的引脚,同样用于未来的扩展或特

定功能。

这些是10针JTAG线束常见的定义,不同的设备和制造商可能

会有一些差异,但通常遵循类似的标准。

这种线束通常用于连接到JTAG调试器或编程器,以便对目标设备进行调试、测试或编程操作。

jtagulator识别引脚原理理论说明1. 引言1.1 概述本篇长文旨在对JTAGulator识别引脚原理进行详细的理论说明。

随着现代电子设备日益复杂和智能化,许多通信设备和嵌入式系统采用JTAG(Joint Test Action Group)技术来进行测试、调试和编程。

由于安全性的考虑,很多设备会将JTAG接口隐藏或者不公开。

此时,JTAGulator作为一种非侵入式的引脚识别工具应运而生。

它通过扫描目标设备上的引脚,并利用两种方法来识别是否存在隐藏的JTAG接口。

本文将深入探讨JTAG技术概述、JTAGulator工具简介以及其引脚识别原理。

1.2 文章结构文章主要分为五个部分。

首先是引言部分,概述了文章的目的和结构。

其次是“2. JTAGulator识别引脚原理的理论说明”,详细介绍了JTAG技术的背景知识、JTAGulator工具的基本情况以及其引脚识别原理。

第三部分为正文内容,具体展开讲解待定名称的要点,包括待定名称下各个小节内容。

第四部分同样展开讲解待定名称的要点,包括待定名称下各个小节内容。

最后一部分是结论部分,总结文章的主要内容并探讨其研究意义和进一步展望。

1.3 目的本文的目的在于深入理解JTAGulator识别引脚原理,并通过对JTAG技术背景、JTAGulator工具及其引脚识别原理的详细阐述,帮助读者更好地了解该工具在现代电子设备测试、调试和编程中的应用。

同时,通过分析和总结相关知识,揭示该原理背后的核心思想以及未来可能的发展方向。

2. JTAGulator识别引脚原理的理论说明:2.1 JTAG技术概述:JTAG(全称为Joint Test Action Group)是一种用于测试集成电路(IC)的接口标准。

它允许在IC制造过程中和芯片集成到系统中后对其进行测试、调试和编程。

JTAG技术通过访问芯片内部的测试逻辑,使得开发人员可以非常方便地获取芯片的内部状态和应用程序运行数据。

JTag和Jlink的区别JTag和Jlink的区别 JTAG是arm芯⽚的调试协议,诸如Keil/ADS/IAR等IDE集成了JTAG解析功能。

JLink,JTrace都是调试器/仿真器,即在线调试⼯具,他们⽀持从JTAG协议/接⼝转换到USB协议/接⼝。

⼀、⼯作原理 调试ARM,总要遵循ARM的调试接⼝协议吧,jtag就是其中的⼀种吧。

当仿真时,IAR,KEIL,ADS等等都有⼀个公共的调试接⼝,RDI(RDI接⼝是ARM公司提出的调试接⼝标准,主要⽤于ARM芯⽚的JTAG仿真。

) 那么我们如何完成RDI-->arm调试协议(JTAG)的转换呢?如是乎就有两种做法: (1) 在电脑上写⼀个服务程序,把KEIL,ADS,IAR中的RDI命令解析成相关的JTAG协议,然后通后⼀个物理转换接⼝(注意,这个转换只是电⽓物理层上的转换,就像RS232那样的作⽤)发送你的的⽬标板。

H-JTAG就是这样的。

H-JTAG的硬件就仅是⼀个物理电平的转换接⼝,所以很简单。

⽽电脑中装的H-JTAG软件就是前⾯说到的服务程序,负责协议转换的。

(2)另⼀种做法,就是做⼀个板,⽤此板直接接收来⾃KEIL,ADS,IAR等软件的调试命令,由此板做RDI->JTAG协议的转换。

然后与⽬标板通信,这就是jlink的⼯作原理。

(这也就实现了USB转JTAG协议)。

1.JTAG⼯作原理 JTAG(Joint Test AcTIon Group,联合测试⾏动组)是⼀种国际标准测试协议(IEEE 1149.1兼容)。

标准的JTAG接⼝是4线——TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输⼊和数据输出线。

JTAG是最基本的通讯协议之⼀,⼤家可以理解为与RX TX或者USB的道理是⼀样的,只是⼀种通讯⼿段,但与RX TX以及USB有很重⼤的不同,那就是这个JTAG协议是最底层的,说的通俗⼀点,⼀般来说,⼿机⾥边,CPU是⽼⼤,对吧?但在JTAG⾯前,他就不是⽼⼤了,JTAG协议就是⽤来控制CPU的,在JTAG⾯前CPU变成喽啰了。

J-link引脚定义

Pin Name Fuction

1 VCCS VCC Sense

2 NC not connected

3 TRST JTAG Reset

4 GND Common Ground

5 TDI JTAG data input of target CPU

6 GND Common Ground

7 TMS JTAG mode input of target CPU

8 GND Common Ground

9 TCK JTAG clock signal to target CPU

10 GND Common Ground

11 NC not connected

12 GND Common Ground

13 TDO JTAG date ouput from target CPU

14 GND Common Ground

15 RESET target CPU reset signal

16 GND Common Ground

17 NC not connected

18 GND Common Ground

19 VDC +5 VC to target board

20 GND Common ground

标准的JTAG当然是20Pin,但JA TG实际使用的只有4根信号线,再配合电源、地,故又有了很多不同的接口形式,而且现在也渐成标准

1.TCK Programmer JTAG Clock(JTAG管脚中的输入时钟信号,对编程和边界扫

描都需要)

2.GND1 Signal Reference(信号地)

3.TDO Target Board Test Data Output(JTAG管脚中串行的输出数据信号,对编程和

边界扫描都需要)

4.VTref 接开发板电源

5.TMS Programmer Test Mode Select(JTAG管脚中的测试选通信号,对编程和边界

扫描都需要)

6.VJTAG Target Board JTAG Supply V oltage(目标板JTAG电源)

7.VPUMP2 Programmer/Target Board Programming Supply V oltage(目标板JTAG电源)

8.nTRST Programmer JTAG Test Reset (Hi-Z with 10 kΩ pull-down, HIGH, LOW,or

toggling)(JTAG管脚中异步复位信号,对编程和边界扫描都需要,用10K电阻上拉到Vddp)

9.TDI Programmer Test Data Input(JTAG管脚中串行的输入数据信号,对编程和

边界扫描都需要)

10.GND1 Signal Reference(信号地)

Notes:

1. Both GND pins must be connected.(所有的地引脚都要连接)

2. FlashPro3 can provide VPUMP if there is only one device on the target board.(如果目标板只有一个芯片,则VPUMP可以由FlashPro3提供。