第 2 章习题参考答案

1 8086CPU由哪两部分构成它们的主要功能是什么?

答:

8086CPU由两部分组成:指令执行部件 (EU,Execution Unit) 和总线接口部

件 (BIU , Bus Interface Unit)。

指令执行部件( EU)主要由算术逻辑运算单元(ALU)、标志寄存器 FR、通用寄存器组和 EU控制器等 4 个部件组成。其主要功能是执行指令。

总线接口部件 (BIU) 主要由地址加法器、专用寄存器组、指令队列和总线控

制电路等 4 个部件组成。其主要功能是形成访问存储器的物理地址、访问存储

器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参

加 EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?

答:

8086CPU的预取指令队列由6 个字节组成。

按照 8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接

通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部, EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内

存中读取并送到指令队列。

3.8086CPU 中有哪些寄存器?各有什么用途?

答:

CPU有 14 个内部寄存器,可分为 3 大类:通用寄存器、控制寄存器和段寄

存器。

通用寄存器是一种面向寄存器的体系结构,操作数可以直接存放在这些寄

存器中,既可减少访问存储器的次数,又可缩短程序的长度,提高了数据处理

速度,占用内存空间少。指令执行部件(EU)设有 8 个通用寄存器:

AX:累加器,一般用来存放参加运算的数据和结果,在乘、除法运算、

I/O 操作、 BCD数运算中有不可替代的作用

BX:基址寄存器,除可作数据寄存器外,还可放内存的逻辑偏移地址

CX:计数寄存器,既可作数据寄存器,又可在串指令和移位指令中作计数用

DX: DX 除可作通用数据寄存器外,还在乘、除法运算、带符号数的扩展指令中有特殊用途

源变址寄存器SI :多用于存放内存的逻辑偏移地址,隐含的逻辑段地址在 DS寄存器中,也可放数据

目标变址寄存器DI :多用于存放内存的逻辑偏移地址,隐含的逻辑段地址在 DS寄存器中,也可放数据

基址指针BP:用于存放内存的逻辑偏移地址,隐含的逻辑段地址在SS寄存器中

堆栈指针SP:用于存放栈顶的逻辑偏移地址,隐含的逻辑段地址在SS寄存器中

控制寄存器包括指令指针寄存器 IP 和标志寄存器 FLAG: IP 用来指示当前指

令在代码段的偏移位置。 IP 始终存有相对于当前指令段起点偏移量的下一条

指令,即 IP 总是指向下一条待执行的指令, IP 中内容可由 BIU 自动修改; FLAG 用于反映指令执行结果或控制指令执行的形式:

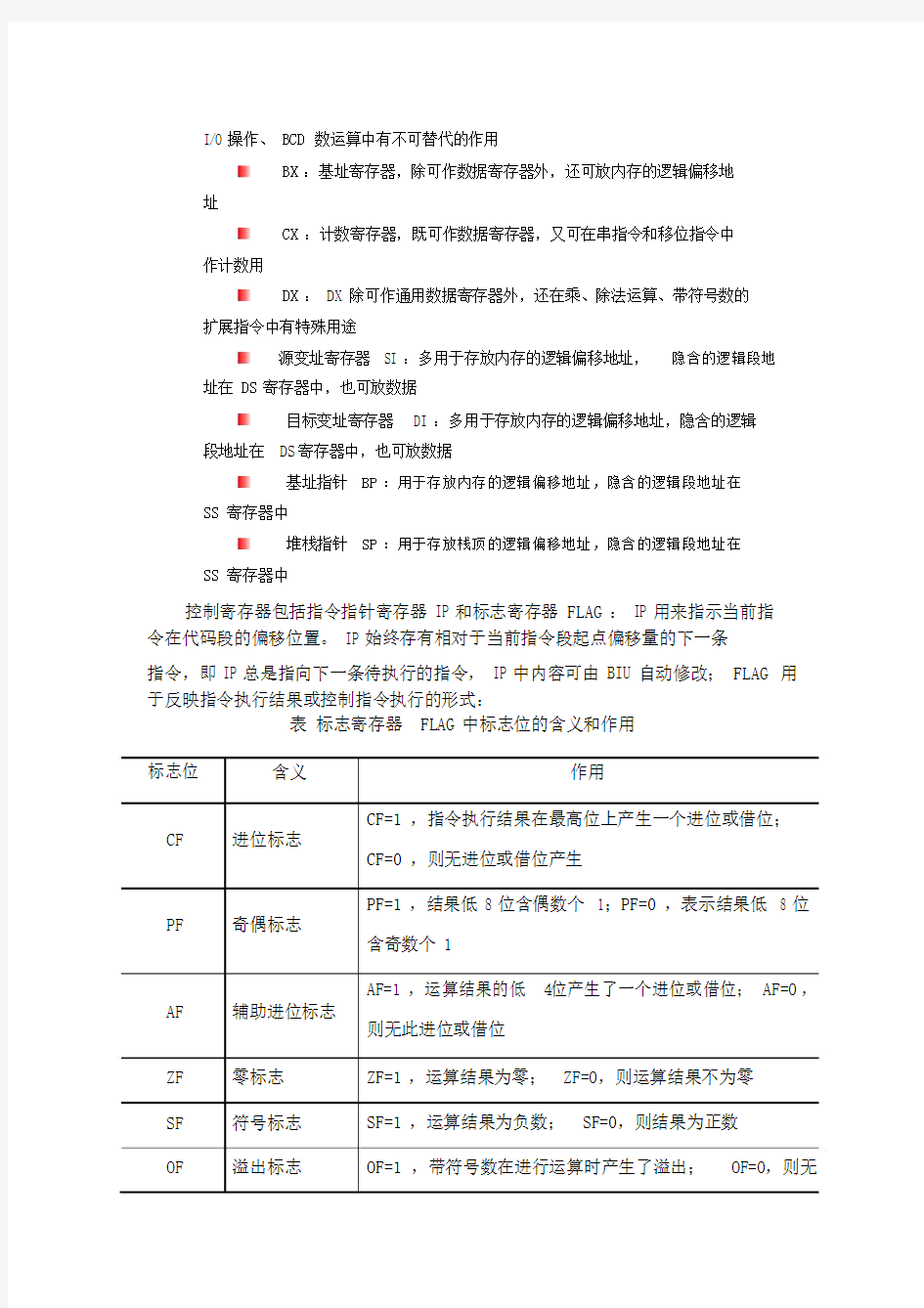

表标志寄存器 FLAG中标志位的含义和作用

标志位含义作用

CF进位标志CF=1,指令执行结果在最高位上产生一个进位或借位;CF=0,则无进位或借位产生

PF奇偶标志

PF=1,结果低 8 位含偶数个 1;PF=0,表示结果低 8 位

含奇数个 1

AF辅助进位标志AF=1,运算结果的低 4 位产生了一个进位或借位; AF=0,则无此进位或借位

ZF零标志ZF=1,运算结果为零; ZF=0,则运算结果不为零

SF符号标志SF=1,运算结果为负数; SF=0,则结果为正数

OF溢出标志OF=1,带符号数在进行运算时产生了溢出; OF=0,则无

溢出

TF=1, 8086CPU处于单步工作方式; TF=0, 8086CPU正TF陷阱标志

常执行程序

IF=1,允许 CPU接受外部从 INTR 引脚上发来的可屏蔽IF中断允许标志

中断请求信号; IF=0 ,则禁止接受可屏蔽中断请求

DF=1,字符串操作指令按递减的顺序对字符串进行处

DF方向标志

理; DF=0,字符串操作指令按递增的顺序进行处理

为了实现寻址 1MB存储器空间, 8086CPU将 1MB的存储空间分成若干个逻

辑段进行管理, 4 个 16 位的段寄存器来存放每一个逻辑段的段起始地址。

CPU规定 4 个段寄存器存放当前可寻址的段基址:

代码段寄存器CS :存放程序代码段起始地址的高16 位

数据段寄存器DS:存放数据段起始地址的高16 位

堆栈段寄存器SS:存放堆栈段起始地址的高16 位

扩展段寄存器ES:存放扩展数据段起始地址的高16 位

5简述 8086 系统中物理地址的形成过程。 8086 系统中的物理地址

最多有多少个?逻辑地址呢?

答:

8086 系统中的物理地址是由20 根地址总线形成的。 8086 系统采用分段并

附以地址偏移量办法形成20 位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部

分构成,都是16 位二进制数。通过一个20 位的地址加法器将这两个地址相加

形成物理地址。具体做法是16 位的段基址左移 4 位 ( 相当于在段基址最低位后

添 4 个“ 0”) ,然后与偏移地址相加获得物理地址。

8086由于8086CPU的地址线是20 根,所以可寻址的存储空间为1M字节,

即

系统的物理地址空间是1MB。逻辑地址由段基址和偏移地址两部分构成,都是无

符号的16 位二进制数。程序设计时采用逻辑地址,也是1MB。

6.8086 系统中的存储器为什么要采用分段结构?有什么好处?

答:

8086CPU中的寄存器都是 16 位的,16 位的地址只能访问64KB的内存。8086系统中的物理地址是由20 根地址总线形成的,要做到对20 位地址空间进行访问,就需要两部分地址。

采用段基址和偏移地址方式组成物理地址的优点是:满足对 8086 系统的 1MB 存储空间的访问,同时在大部分指令中只要提供16 位的偏移地址即可。

8.8086 工作在最小模式和最大模式系统中的主要区别是什么?和

有什么主要特点?

【解答】

两种模式的主要区别是:

8086 工作在最小模式时,系统只有一个微处理器,且系统所有的控制信号

全部由8086 CPU 提供;在最大模式时,系统由多个微处理器/ 协处理器构成的多机系统,控制信号通过总线控制器产生,且系统资源由各处理器共享。

8086CPU工作在哪种模式下通过CPU的第33 条引脚MN/MX来控制:MN/MX =1,系统就处于最小工作模式;MN/MX =0,系统处于最大工作模式。

9 在某系统中已知当前SS=2360H,SP=0800H,那么该堆栈段在存储器中的物理地址范围是什么?若往堆栈中存入20 个字节数据,那么 SP的内容为什么值?

答:

SS×10H+SP=23600H+0800H=23E00H

堆栈段在存储器中的物理地址范围是:23600H~23E00H

若往堆栈中存入20 个字节数据那么SP的内容为:0800H-14H=07ECH。20的十六进制为14H。

10 已知当前数据段位于存储器的B4000H到 C3FFFH范围内,则段寄存器 DS的内容为多少?

答:

段寄存器 DS的内容为 B400H。

118086 系统中为什么一定要有地址锁存器?需要锁存哪些信息?

答:

由于 8086CPU受芯片封装的限制,只有40 个管脚,所以地址线和数据线只

能采用复用的方式共同使用某些管脚。

对存储器进行访问时,在读取数据或写入数据时,存储器芯片要求在这个

过程中地址信息必须稳定提供给存储器,而由于8086CPU地址线和数据线是复用的,就不可能在同一时刻具有地址和数据的两种功能。这就需要在CPU提供地址信息时,将地址锁存起来,以保证下一个时刻当这些复用的管脚起着数据

线的功能时,存储器有正确的地址信息。

要锁存的信息包括这些复用管脚的地址和BHE等信号。

12.8086 读/ 写总线周期各包括最少几个时钟周期?什么情况下需要

插入等待周期 TW?插入多少个TW取决于什么因素?

答:

8086CPU经外部总线对存储器或 I/O 端口进行一次信息的输入或输出过程所

需要的时间,称为总线周期。

8086CPU的读 / 写总线周期通常包括T1、T2、 T3、T4 状态 4 个时钟周期。

在高速的 CPU与慢速的存储器或I/O 接口交换信息时,为了防止丢失数据,

会由存储器或外设通过READY信号线,在总线周期的T3 和 T4 之间插入 1 个或多个必要的等待状态TW,用来进行必要的时间补偿。

在 BIU 不执行任何操作的两个总线周期之间会出现空闲状态TI 。

显然,插入的等待周期TW的个数取决于外设或存储器的取出或写入时间。

13若已知当前(DS)=7F06H,在偏移地址为 0075H开始的存储器中连续存放 6 个字节的数据,分别为 11H,22H,33H,44H,55H和 66H。请指出这些数据在存储器中的物理地址,如果要从存储器中读出这些

数据,需要设备访问几次存储器?各读出哪些数据?

答:

物理地址 7F06FH×10H+0075H=7F0D5H,故从 7F0D5H起 6 个地址数据在存器中的地址。最少要四次,第一次11。第二次 3322。第三次 5544。第四

次 66。

14.某程序在当前数据段中存有两个数据字 0ABCDH和 1234H 它们对应的物理地址分别为 3FF85H和 40AFEH。若已知当前( DS)=3FB0H,请说明这两个数据的偏移地址,并用图说明它们在存储器中的存放格式。

答:

3FF85H偏移地址: 3FF85H - ( DS)*10H=3FF85H-3FB00H=0485H

40AFEH偏移地址: 40AFEH -( DS)*10H=40AFE H-3FB00H=0FFEH

3FB0H:0000H

?

3FB0H:0485H0CDH

3FB0H:0486H0ABH

?

3FB0H:0FFEH34H

3FB0H:0FFFH12H