. .. .

实验二指令流水线相关性分析

·实验目的

通过使用WINDLX模拟器,对程序中的三种相关现象进行观察,并对使用专用通路,增加运算部件等技术对性能的影响进行考察,加深对流水线和RISC 处理器的特点的理解。

·实验原理:

指令流水线中主要有结构相关、数据相关、控制相关。相关影响流水线性能。·实验步骤

一.使用WinDLX模拟器,对Fact.s做如下分析:

(1)观察程序中出现的数据/控制/结构相关。指出程序中出现上述现象的指令组合。

(2)考察增加浮点运算部件对性能的影响。

(3)考察增加forward部件对性能的影响。

(4)观察转移指令在转移成功和转移不成功时候的流水线开销。

·实验过程

一.使用WinDLX模拟器,对Fact.s做如下分析:

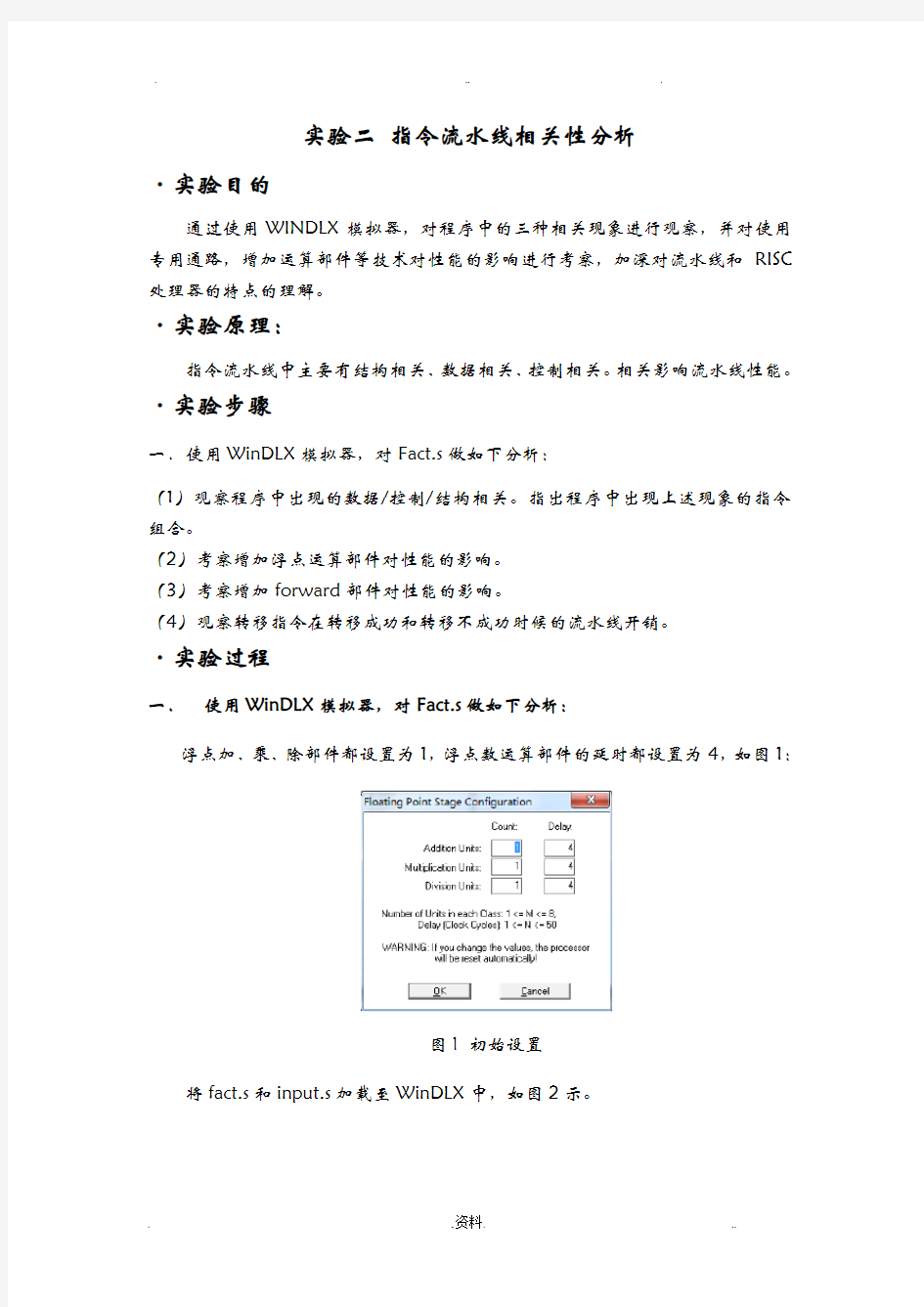

浮点加、乘、除部件都设置为1,浮点数运算部件的延时都设置为4,如图1:

图1 初始设置

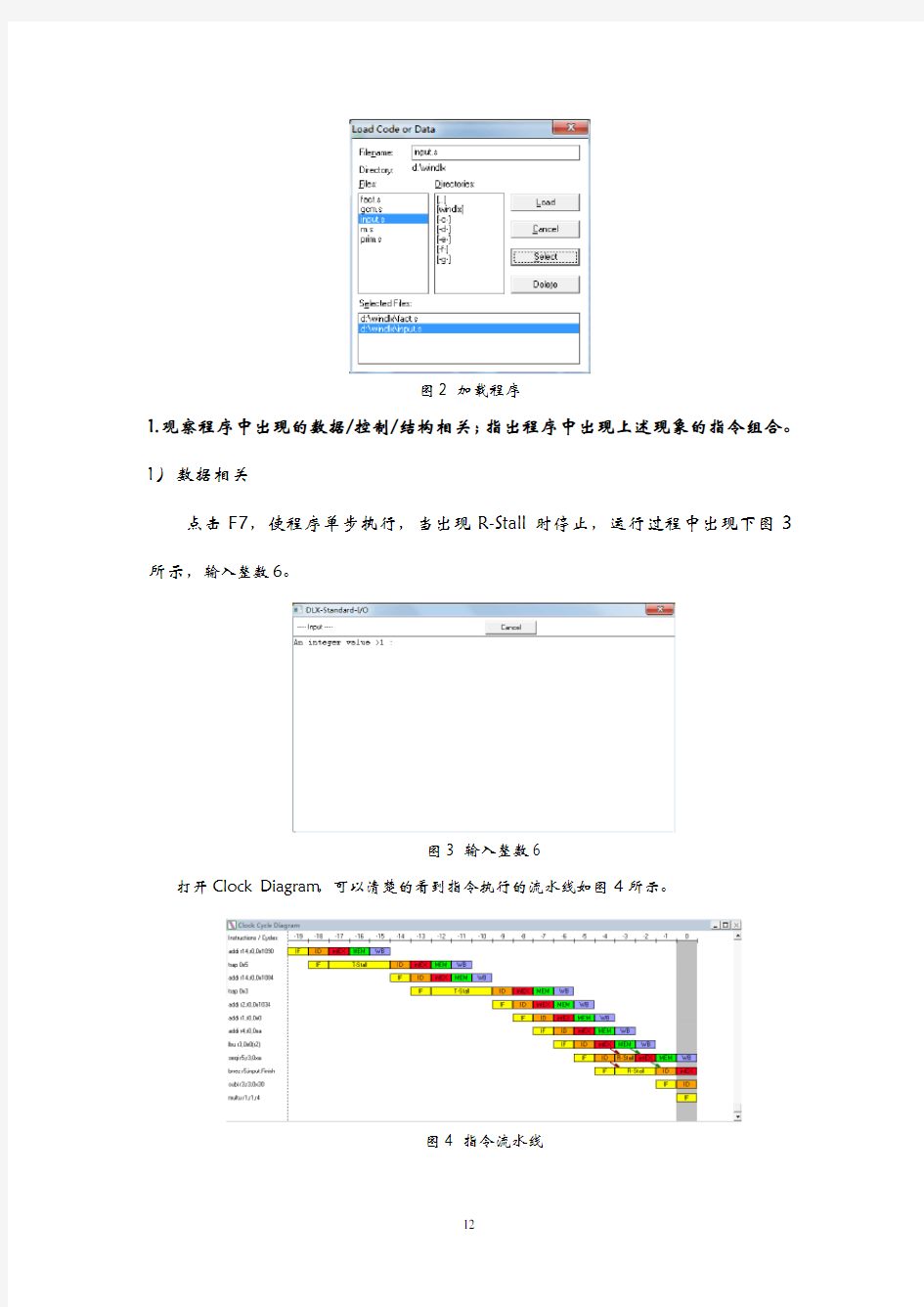

将fact.s和input.s加载至WinDLX中,如图2示。

图2 加载程序

1.观察程序中出现的数据/控制/结构相关;指出程序中出现上述现象的指令组合。1)数据相关

点击F7,使程序单步执行,当出现R-Stall时停止,运行过程中出现下图3所示,输入整数6。

图3 输入整数6

打开Clock Diagram,可以清楚的看到指令执行的流水线如图4所示。

图4 指令流水线

双击第一次出现R-Stall的指令行,如图5所示。

图5 指令详细信息

对以上出现的情况分析如下:

程序发生了数据相关,R-Stall(R-暂停)表示引起暂停的原因是RAW。

lbu r3,0×0(r2)

要在WB周期写回r3中的数据;而下一条指令

seqi r5,r3,0×a

要在intEX周期中读取r3中的数据。

上述过程发生了WR冲突,即写读相关。为了避免此类冲突,

seq r5,r4,0×a的intEX指令延迟了一个周期进行。

由此,相关指令为:

2)控制相关

由图6可以看出,在第4时钟周期:第一条指令处于MEM段,第二条命令

处于intEX段,第三条指令出于aborted状态,第四条命令处于IF段。

图6 指令流水线

以上情况原因分析:

在窗口中,模拟处于第四时钟周期,第3条命令指示为:“aborted”。原因是:第二条命令jal InputUnsigned是无条件分支指令,在第4个时钟周期,jal指令执行intEX周期之后才知道转移的位置,下一条指令应该执行sw SaveR2(r0),r2指令。但之前jal InputUnsigned的下一条命令movi2fp f10.r1已经取出,所以需要将该指令流水清空,即movi2fp的执行应被取消,在流水线中留下气泡。

3)结构相关

首先,我们先来看一下执行过控制相关的时空图和Pipeline,如下图7所示。

图7 控制相关

图8 控制相关的Pipeline

当我们点击Pipeline中IF所对应的框框可以看到详细的该指令执行情况,如下图9所示。

图9 指令详情

图9表明了addi r2,r2,0×1的详细信息。该指令与它前一条指令add r1,r1,r3发生了结构相关。并且由于此处的冲突,需要暂停2个周期。在ID段暂停后,则开始进图intEX段。所以这条指令(addi r2,r2,0×1)你不能进入ID流水段,译码部分占用,发生了结构相关。该部分的指令为:

1.考察增加浮点运算部件对性能的影响。

该实验取N=6

首先通过Configuration,点击Floating Point Stage Configuration来设置浮点运算部件的配置。实验要求所有浮点运算部件的延时都请设定为4个周期,所以我们将Delay这一栏改成4,而Count可以任意,为了对比,我们第一次浮点运算部件取全部为1,第二次浮点运算部件取全部为2。如下图所示:

运行50个cycles之后,可以看到他们数据的对比:

由此可见,浮点运算部件的增减对效率无影响。比较各个数据,发现没有变化。无论怎么增加浮点运算部件,统计结果都一样。原因在于此程序中浮点计算指令没有重叠,所以并行度没有增加,性能没有提高。

3.考察增加forward部件对性能的影响。

为了对比有无forward部件的性能。需要在Configuration中勾选enable forwarding,以及不勾选enable configuration来看性能数据的对比,不使用forward部件和使用forward部件:

从上面的数据我们可以看出增加forward部件后RAW由原来占总时钟周期的26%减少至18%,RAW个数由原来的13减少至9。增加forward部件使得控制相关比例增加了。即,使用forward部件后,总的时钟周期减少,数据相关减少,流水线的性能得到一定的改善。

4.观察转移指令在转移成功和转移不成功时候的流水线开销。

我们假设,浮点部件设置Count=1,Delay=4;N=6。执行50个cycles完毕后,查看条件转移分支,如下图所示:

由上图可知,转移指令一共2条,成功转移1条(占50%),不成功为1条。

所以,静态指令调度算法只能解决数据相关,条件转移结果与原来相比没有变化。即,若转移不成功,对流水线的执行无影响,流水线的吞吐率和效率没有降低;若转移成功,则要废弃预先读入的指令,重新从转移成功处读入指令,执行效率会下降。

·实验总结

通过本次试验,不仅更加熟悉了WinDLX模拟器的使用以及对其基础功能的认识,而且通过单步执行程序,观察三种相关的出现,以及思考出现的原因,是我更加深入了解了流水线。