第25卷 第1期2010年2月

液 晶 与 显 示

Chinese Jour nal of Liquid Cryst als and Displays

Vol 125,No 11Feb.,2010

文章编号:100722780(2010)0120130204

FPGA 实现的视频图像缩放显示

孙红进

(南京工业大学信息科学与工程学院,江苏南京 210009,E 2mail:s unhjin @https://www.doczj.com/doc/e44808264.html,)

摘 要:对几种常用的图像缩放算法进行了比较,在权衡了算法复杂度、缩放效果和FPGA 逻辑资源等3大因素后,选择了双线性插值算法来实现图像缩放。重点介绍了双线性插值算法和该方法的F PGA 硬件实现方法,包括图像数据缓冲单元、插值系数生成单元以及插值计算单元等。应用结果表明,双线性插值算法及其硬件实现模块达到了预期的效果。关 键 词:图像缩放;FP GA;双线性插值中图分类号:T P301.6 文献标识码:A

FPGA Realization of Video Image Zooming Display

SUN H ong 2jin

(College of I nf ormation Science and Eng ineering ,N anj ing University of T echnolog y ,

Nanj ing 210009,Ch ina,E 2mail:sunhjin @y https://www.doczj.com/doc/e44808264.html,)

Abstr act:Some commonly used image scaling algorithms were introduced,as well as a com 2parison among sever al algor ithms.After weighing the algorithm complexity,zoom effects

and FPGA logic resources,etc.,the bilinear interpolation algor ithm was chosen to achieve image scaling.This work focused on the bilinear interpolation algor ithm and the method of FPGA hardware implementation,including image data buffer unit,interpolation coefficient generating unit,as well as the interpolation calculation unit.The realized results show that the bilinear inter polation algorithm and its hardware realizing modules achieve the desired results.

Key words:image scaling;FPGA;bilinear interpolation

收稿日期:2009206226;修订日期:2009207216

作者简介:孙红进(1985-),男,江苏南京人,硕士研究生,主要研究方向为数字信号处理、显示技术。

1 引 言

图像是人类感知世界的视觉基础,是人类获取信息、表达信息的重要手段。现在研究较多的是数字图像,它是由连续函数或离散函数生成的抽象图像,能直接被计算机处理。图像缩放是数字图像处理的重要一环,在实际应用中经常要将图像进行放大或缩小。例如,等离子电视、液晶电视和发光二极管(LED)显示屏等显示器需将接收到的图像分辨率进行缩放,使之与显示器的物理

分辨率一致,才能在显示器上完整地显示视频图像。视频图像处理的详细内容请见参考文献[1,2]。目前,市场上有数字视频后处理芯片,这些芯片大都是从欧美、日、韩等地的公司进口的,国内最早进行视频处理芯片研究的是西安交通大学[3],但这些芯片主要应用于高复杂度的系统,应用在低复杂度的系统则显得不合适,比如应用在需要单纯进行图像缩放的场合,则显得浪费,还可能带来不必要的麻烦。本文要实现的图像缩放是视频图像的实时缩放,而不是仅实现某个缩放比例

第1期孙红进:F PGA 实现的视频图像缩放显示131

的图像缩放,适合于低复杂度的系统,成本较低。2 算法原理

2.1 算法选择

图像缩放算法种类较多,几乎都是通过插值算法实现的,传统的插值算法有:最近邻插值、双线性插值和立方卷积插值等。最简单的插值方法是最近邻插值,与其他两种插值算法相比,最近邻插值具有简单快速的特点,但是对于近邻像素点的灰度值有较大改变,细微结构是粗糙的。双线性插值方法具有低通滤波器性质,使高频信息受损,图像轮廓模糊,但边缘处的过渡比较自然。与最近邻插值相比,它的计算量较大,但缩放后的图像质量高,不会出现像素值不连续的情况,在对图像边缘质量要求不是非常高的情况下,这种方法是完全可以接受的。立方卷积法计算量要比双线性插值大很多,但精度高,能保持较好的图像边缘细节。实际应用中,因为FPGA 内的逻辑资源有限,而算法越复杂占用的逻辑资源就越多,对FPGA 完成图像的实时缩放有重要影响

[428]

,所以

实际应用中应选择合适的算法,并非精度越高越好。综上所述,本文选用双线性插值算法来实现图像缩放。

2.2 双线性插值算法

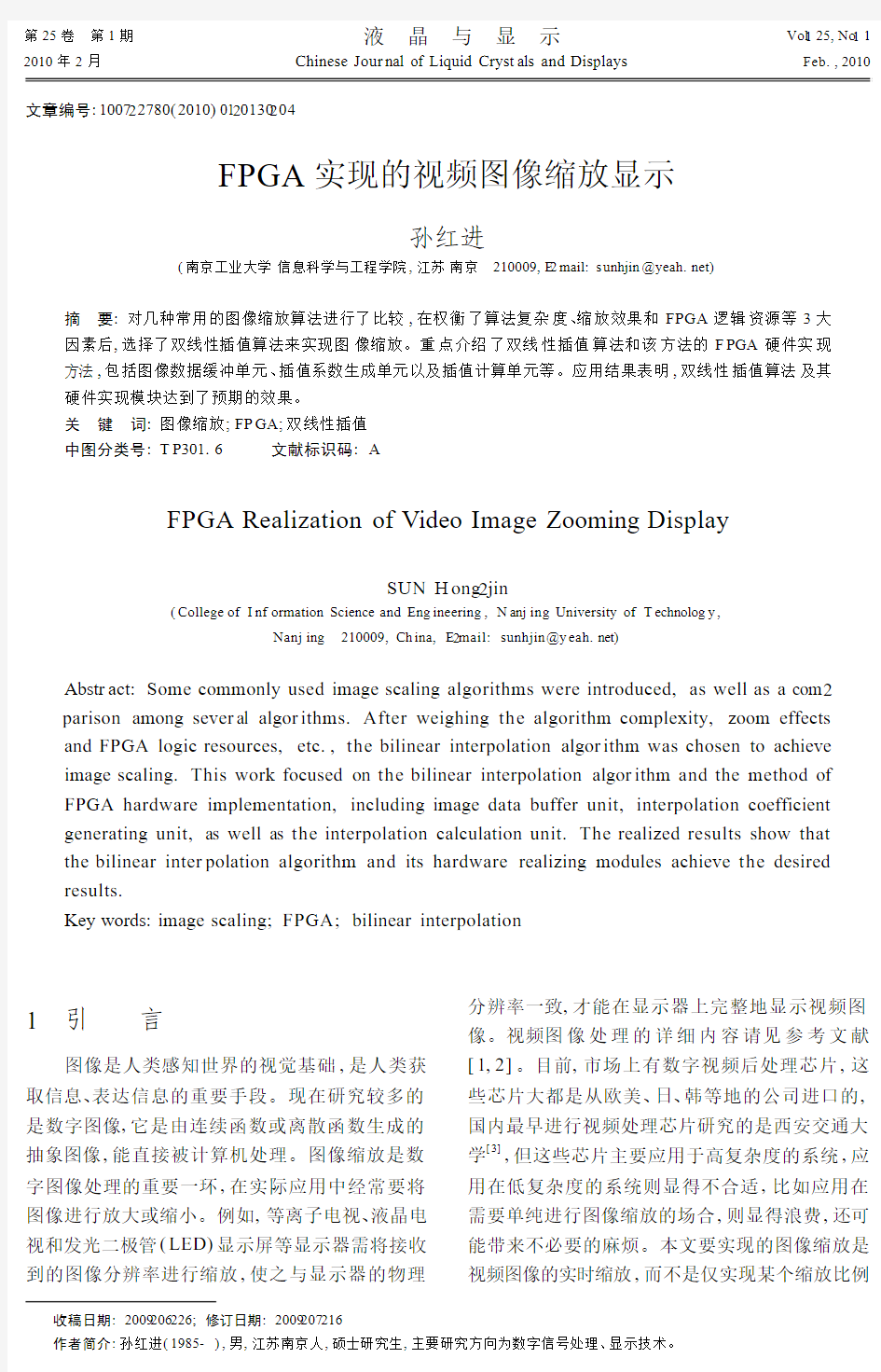

在双线性插值中,新创建的图像的像素值是由原图像位置在它附近的(2@2)个邻近像素的值通过加权平均计算得出的,然后由新图像的某个像素(x,y)映射到原始图像(x c ,y c )处,对x c 、y c 取整得到(u,v)并得到(u +1,v)、(u,v +1)和(u +1,v +1)的值,利用双线性插值得到像素点(x,y)的值并写回新图像[6,7]

。图1为双线性插

值的原理图。

设原始图像中相邻两行中相邻两列的4个像素点为p l 、p 2、p 3、p 4,

水平和垂直两个方向点距为

图1 双线性插值原理图

Fig.1 Pr inciple diagram of bilinear inter polation

单位长度l 。4点坐标分别为p l (x,y)、p 2(x +l,y)、p 3(x,y +l)、p 4(x +l,y +l ),目标像素点的坐标为A(x +d x ,y +d y),d x 、d y 分别是目标像素点与原始图像中邻近点的水平和垂直坐标方向上的两个增量。那么,采用双线性插值法得到目标插值像素点A 的灰度值为:

A(x +d x ,y +d y)=(1-d x)(1-d y)p 1+d x(1-d y)p 2+(1-d x)d yp 3+d x d yp 4 考虑以FPGA 来实现插值运算时,共需要8个乘法器、2个减法器和4个加法器,占用了较多的逻辑资源[5]

,所以将它改写为:

A(x +d x,y +d y)=p 1+d x(p 2-p 1)+d y(p 3-p 1)+d x d y(p 1-p 2-p 3+p 4)=

p 1+(p 2-p 1)d x +(p 3-p 1)d y +[(p 4-p 3)-(p 2-p 1)]d x d y

(1)

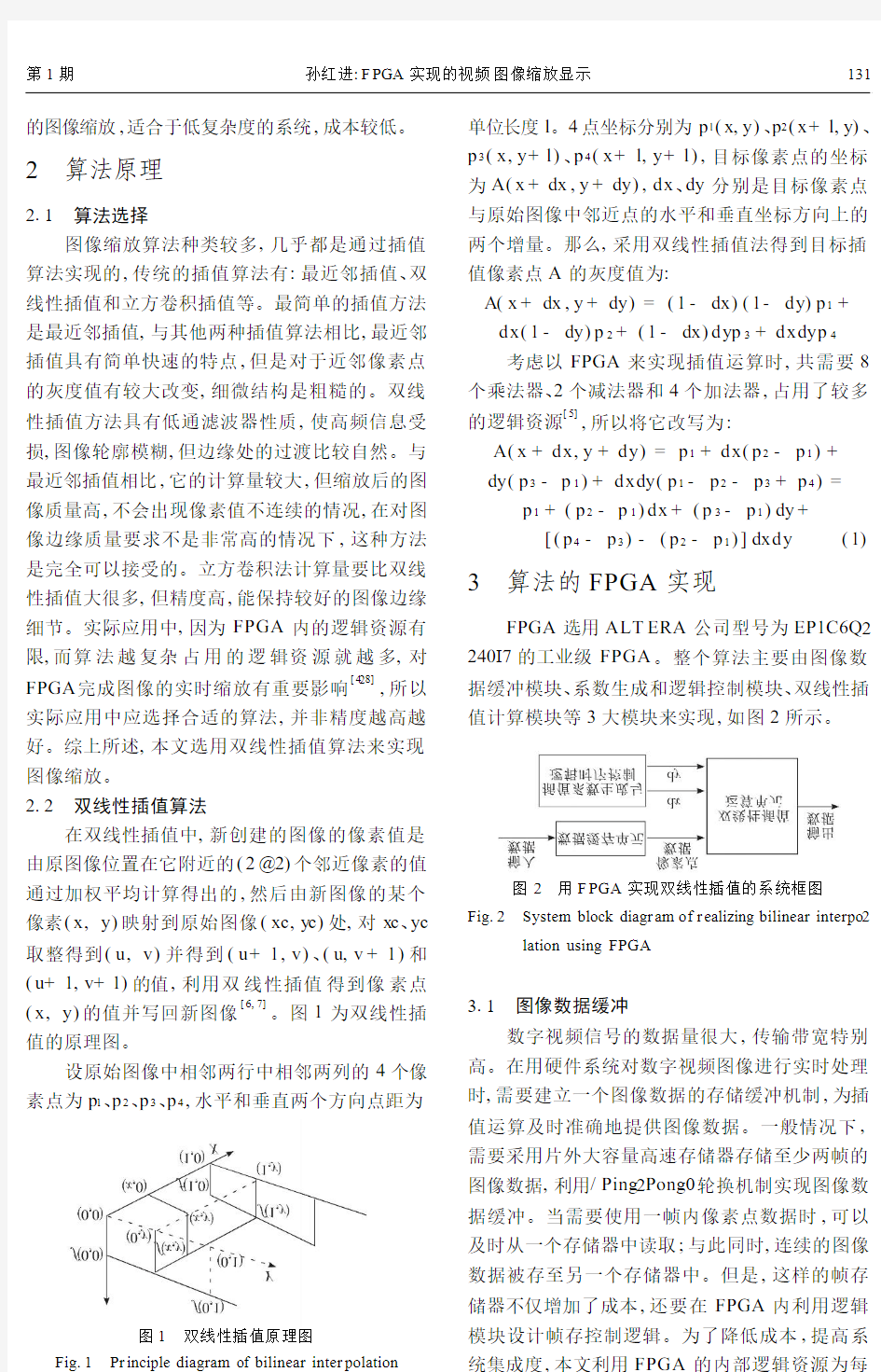

3 算法的FPGA 实现

FPGA 选用ALT ERA 公司型号为EP1C6Q 2240I7的工业级FPGA 。整个算法主要由图像数据缓冲模块、系数生成和逻辑控制模块、双线性插值计算模块等3大模块来实现,如图2

所示。

图2 用F PGA 实现双线性插值的系统框图Fig.2 System block diagr am of r ealizing bilinear interpo 2

lation using FPGA

3.1 图像数据缓冲

数字视频信号的数据量很大,传输带宽特别高。在用硬件系统对数字视频图像进行实时处理时,需要建立一个图像数据的存储缓冲机制,为插值运算及时准确地提供图像数据。一般情况下,需要采用片外大容量高速存储器存储至少两帧的图像数据,利用/Ping 2Pong 0轮换机制实现图像数据缓冲。当需要使用一帧内像素点数据时,可以及时从一个存储器中读取;与此同时,连续的图像数据被存至另一个存储器中。但是,这样的帧存储器不仅增加了成本,还要在FPGA 内利用逻辑

模块设计帧存控制逻辑。为了降低成本,提高系统集成度,本文利用FPGA 的内部逻辑资源为每

132 液 晶 与 显 示第25卷

一彩色通道设计了一组由3个双端口RAM (DPRAM)组成的图像数据缓冲阵列,并将这样一个缓冲阵列称为行缓冲器[5,9]

。

3.2 插值系数生成

根据双线性插值运算公式及二维图像插值的FPGA 实现方法,两个运算系数d x 和d y 需要准确及时地求出,提供给插值运算单元,并且只有当生成的系数在时序节拍上与图像数据存储、插值计算单元的时序配合一致时,才能有效地完成整幅图像的插值运算。因此,在生成系数的同时,必须能够给出系数在原图像中对应邻近像素点的坐标信息,即在DPRAM 中的存储地址,以便图像数据缓冲模块可以同步地取出参与运算的4个图像数据[5]。

首先需要确定缩放因子S 。对于以单位长度/10来表示相邻两个像素点的距离的模型进行缩放时,以S 为间隔形成一个新采样格栅,重新对原图像在水平和垂直两个方向上进行重采样,新图像的像素点距离即为S 。如果把分辨率为640@480的图像转化为800@600的图像,就需要放大

1.25倍,则缩放因子为:

S =l /1.25=0.8

如果把分辨率为1024@768的图像转化为800@600,将图像缩小0.78125倍时,缩放因子为:

S =l /0.78125=1.28

上述两种情况下,目标图像在水平和垂直两个方向的缩放比例是一样的。若在水平和垂直两个方向上的缩放比例不一致,则缩放因子也就不相同,分别定义为S _x 和S _y 。那么,对应于新图像中坐标为(m,n)的像素点,系数d x 和d y 可以由公式(2)得到:

d x =m @S _x -[m @S _x]d y =m @S _y -[m @S _y ]

(2)

式(2)中,[]表示下取整。

4 双线性插值运算单元

在获取插值像素点相邻4点的图像数据和插值系数后,就可以进行双线性插值运算了。依据插值公式(1),设计了一种具有流水线特性的运算逻辑结构,如图3

。

图3 双线性插值运算单元

Fig.3 Comput ing unit of bilinear inter polation

图中,p 1、p 2、p 3和p 4由DPRAM 实时输出,d x 和d y 则由系数生成单元提供。逻辑实现过程中,要特别注意时序节拍的控制,力求时序同步。当某个运算步骤输出数据与其他运算的输出值在某个时钟不能同步到达下一个运算器时,在数据线上插入延时单元,使它们能达到同步,并且适当增加乘法器和加法器等的流水线延时。

5 功能实现

设计中,选用ALTERA 公司型号为EP1C6Q 2240I7的工业级FPGA ,采用VH DL 语言对各逻辑模块进行设计,在开发环境Quartus II 8.0下完成了时序仿真和功能验证。此外,整个硬件模块在像素间距为20mm 的发光二极管(LED)显示屏中得到了成功应用,虽然从理论上讲,利用双

第1期孙红进:F PGA 实现的视频图像缩放显示133

线性插值算法实现图像缩放存在边缘高频分量的损失,但从LED 显示屏的显示效果来看,人眼完

全可以接受,所采用的算法适合于这一工程应用。显示效果如图4中的(a)、(b)、(c)

所示。

图4 图像缩放显示.(a)100%显示;(b)放大1.5倍显示;(c)缩小0.7倍显示.

Fig.4 Image zoom displa y.(a)Display with 100%;(b)Display wit h enlar ging by 150%;(c)Display with nar rowing

by 70%.

6 结 论

介绍了一些常用的图像缩放算法并对几种算法进行了比较,在权衡算法复杂度、缩放效果和FPGA 逻辑资源等3大因素后,选择了双线性插值算法来实现图像缩放。从实现结果看,本算法

以及硬件实现模块达到了预期的效果。虽然该算法在理论上会造成被缩放图像边缘高频分量的损失,使图像边缘模糊,但在很多对图像质量要求不是很严格的场合,比如在LED 显示屏上播放视频图像,所获得的图像质量是人眼完全可以接受的,效果良好,适合工程应用。

参 考 文 献:

[1]许录平,编著.数字图像处理[M].北京:科学出版社,2007.

[2]Castleman Kenneth R[美].Dig ital I ma ge P r ocessing [M ].北京:电子工业出版社,2008.

[3]葛晨阳,郑南宁,任鹏举,等.平板电视数字视频后处理芯片的设计与实现[J].西安交通大学学报,2008,42(10):

529.

[4]吴均,朱重光.带锐度保持的斜投影B2样条图像缩放[J].遥感学报,2002,6(2):1082112.

[5]盛磊.面向特种LCD 图像处理方法与FPGA 实现研究[D].合肥:合肥工业大学博士论文,2005:26240.

[6]蔡希昌,翟林培,周九飞,等.基于FP GA 的非XGA 标准图像显示控制器的设计[J].液晶与显示,2008,23(3):

3012306.

[7]徐伯庆,孙国强,陈离.数字图像缩放的原理与硬件实现[J].上海理工大学学报,2002,24(3):2232225.[8]Hear n Donald,Baker M P.计算机图形学[M].蔡士杰,宋继强,蔡敏,译.北京:电子工业出版社,2007.

[9]Feng Tao,Xie Wenlu,Yang Lianxing.An ar chit ecture and implementation of image scaling conver sion[C]//T he 4th

I nter na tiona l Conf erence on ASI C P r oceedings,Shanghia,China:IEEE,2001:4092410.

基于FPGA的快速图像处理系统的设计 摘要 我们评估、改进硬件、软件架构的性能,目的是为了适应各种不同的图像处理任务。这个系统架构采用基于现场可编程门阵列(FPGA)和主机电脑。PC端安装Lab VIEW应用程序,用于控制图像采集和工业相机的视频捕获。通过USB2.0传输协议执行传输。FPGA控制器是基于ALTERA的Cyclone II 芯片,其作用是作为一个系统级可编程芯片(SOPC)嵌入NIOSII内核。该SOPC集成了CPU,片内、外部内存,传输信道,和图像数据处理系统。采用标准的传输协议和通过软硬件逻辑来调整各种帧的大小。与其他解决方案作比较,对其一系列的应用进行讨论。 关键词:软件/硬件联合设计;图像处理;FPGA;嵌入式

毕业设计(论文)原创性声明和使用授权说明 原创性声明 本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。 作者签名:日期: 指导教师签名:日期: 使用授权说明 本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。

基于FPGA的图像压缩传输与解码 硬件设计部分 一、硬件完成的功能定义 1.使用FPGA普通端口作为GPIO使用。 2.使用FPGA开发板的50MHZ时钟分频后25MHZ作为VGA输出时钟。 3.时钟频率25MHZ完成行扫描信号计数。 4.时钟频率25MHZ完成祯扫描信号计数,并完成祯计数。 5.在行,场信号有效范围内进行VGA数据输出。 二、顶层模块划分 1.顶层的输入输出定义

2.顶层模块输入、输出之间的时序关系: vag输入时钟50mhz,分频产生25mhz,作为vga输出时钟,PLL倍频,200mhz作为cpu时钟,UART接收来自串口数据。软件读取数据,处理 后,输出数据。 软件设计部分 一、软件功能定义1 获取发送数据, 二:软件设计的总体设计及结构图

三:软件详细设计 1:用matlab取图像的reb值,将取出的rgb值写入文件。 2:读取rbg值,将十六进制数表示的rgb值转化为以该asc||值对应的字符(减少信息传输量),将转化后的的字 符写入文件中。 3:对转化后的文件数据进行压缩,发送目标文件格式为,文件头信息,发送文件的起始信息,用来判定开始发 送数据,用三个字节,信息数据为GCL,一个字节表示 最后一个字节的有效位,最后一个字节有效位为0bit- 8bit之间,一个字节表示文件中rgb的种类,0-255,四字节,表示整个压缩文件的大小,其后数据格式为, 字符及字符对应的出现次数,即字符频度信息,字符 频度之后对应的是压缩信息。

4:具体软件的实现: 1.Matlab取图片rgb值,写入rgb.txt文件中,处理得到 对应字符文件,读取文件统计rgb值得种类及每种rgb 值出现的次数。 2.根据统计rgb值得种类及次数,生成huffman树。 3.由生成的huffman树,递归生成huffmancode。 4.根据reb.txt文件内容和huffmancode生成压缩信。 四、软件功能测试 1:手工构造最简单的huffman树,huffmancode,compress code。 2:显示软件统计字符及频度与最小模型是否一样。 3:显示软件生成的huffmantab与最小模型huffmantab是否一样。 4:显示软件递归生成的huffmantab code与最小模型huffmantab code是否一样。 5显示软件递归生成compresse code与最小模型compress code 是否一样。 一:软件功能定义2 UART串口发射接收。该模块主要用于数据发送与接收,UART_RXD作为接收端,UART_TXD作为发射端, 二:软件设计的总体设计及结构图 三:软件详细设计 1:初始化UART,将UART设置为单字节触发模, UART->STATUS.BITS.RRDY = 0; UART->SIATUS.BITS.TRDY =0 ; UART->DIVISOR.WORD=(unsigned int)(ALT_CPU_FREQ/baudrate+0.5);

基于FPGA的图像预处理系统 由于获取图像的工具或手段的影响,使获取图像无法完全体现原始图像的全部信息。因此,对图像进行预处理就显得非常重要。预处理的目的是改善图像数据,抑制不需要的变形或者增强某些对于后续处理来说比较重要的图像特征。 通常根据预处理目的的不同,把预处理技术归为图像增强技术和图像分割技术两类。图像对比度处理是空间域图像增强的一种方法。由于图像灰度范围狭窄会使图像的对比度不理想,可用对比度增强技术来调整图像灰度值的动态范围。 图像处理通常采用软件或者DSP(数字信号处理器)来实现。如果利用软件实现,运行时会耗费较多的PC资源,而且算法越复杂时耗费的资源就越多,对于需要高速处理的情况就不适用了;而如果采用DSP来实现,提高并行性的同时指令执行速度必然会提高,较高的指令速度可能导致系统设计复杂化,并增加功耗和成本。新一代的FPGA集成了CPU或DSP 内核,可以在一片FPGA上进行软硬件协同设计,为实现SOPC提供了强大的硬件支持。本文介绍的是利用FPGA并行处理和计算能力,以Altera FPGA Stratix EP1S40为系统控制的核心实现的SOPC。 系统硬件平台 采用基于PCI总线的FPGA开发平台,结构如图1所示。板上主要硬件资源有:PCI 桥、FPGA、SRAM和SDRAM等其他外设。 图1 基于PCI总线的FPGA开发平台 PCI桥采用PCI9656桥接芯片实现,用来连接PCI总线与32位/50MHz的板级局部总线;FPGA包括41 250个逻辑单元,14个DSP模块,112个嵌入式乘法器,4个增强型PLL(锁相环)和4个快速型PLL等逻辑资源;SDRAM用来存储图像数据。Avalon总线模块完成整个片上可编程系统组件之间的互连。Avalon总线是SOPC设计中连接片上处理器和其他IP 模块的一种简单总线协议,规定了主、从构件之间的端口连接以及通信时序关系,SOPC Builder来完成整个系统(包括Avalon)模块的生成和集成。丰富的板级资源可以满足图像的高速预处理需求。 系统工作原理 设计采用DMA方式快速传输图像数据,这样数据的传输和处理可以并行起来,使得系统的运行效率大为提高。PC与PCI板卡之间建立软件环境,在该环境下利用DMA通道把图像数据从主机通过PCI总线、PCI桥、板级局部总线和Avalon总线传到SDRAM存储起来,然后送入算法逻辑模块进行处理,处理完成后再把图像数据存储到SDRAM中,最后再用DMA通道把图像处理结果传送回主机。 建立片上系统中的关键模块

龙源期刊网 https://www.doczj.com/doc/e44808264.html, 基于FPGA的数字图像处理 作者:李科唐波张玉 来源:《科技资讯》2012年第02期 摘要:随着数字多媒体技术的不断发展,数字图像处理技术被广泛应用于航空航天、通信、医学及工业生产等领域中。图像处理系统一般包括两个部分:图像采集部分和图像处理部分。图像采集部分由专用的视频处理器,图像缓存和控制接口电路组成。图像处理部分可以是计算机,也可以是专用图像处理器件,或者是两者的结合。由于底层图像处理的数据量很大,要求处理速度快,但运算结果相对比较简单,以(FPGA作为主要处理芯片的图像处理系统非常适合于对图像进行处理。 关键词:FPGA数字图像数据处理 中图分类号:TP2文献标识码:A文章编号:1672-3791(2012)01(b)-0032-01 数字图像处理的特点是处理的数据量大,处理非常耗时,本文研究了在FPGA上用硬件描述语言实现图像处理算法,通过功能模块的硬件化,解决了视频图像处理的速度问题。随着微电子技术的高速发展,FPGA为数字图像信号处理在算法、系统结构上带来了新的方法和思路。 图像处理系统的发展大致分为三个阶段。 第一阶段大体上是20世纪60年代末到20世纪80年代中期,当时的代表产品是美国和英国的一些公司推出的各种图像计算机以及图像分析系统。 第二阶段是从20世纪80年代中期到20世纪90年代初期,该阶段的特点是小型化,外部结构不再是机箱式而是插卡式。 第三阶段是从20世纪90年代初开始,这阶段的产品出现两大类,一种仍是采用插卡式,随着PCI,总线技术的成熟,采用PCI,总线的产品逐步取代采用ISA总线接口的产品。 随着近些年来多媒体技术的发展,人们对视频信息的需求愈来愈强烈,图像采集与处理显得越来越重要。依托计算机技术、通信技术和网络条件的发展以及数字信号处理的快速发展,图像处理系统出现以下发展趋势。 (1)随着硬件的发展,图像处理系统的性能会越来越高,价格会逐步降低。 (2)图像处理系统的功能都会集成在一个便于携带使用方便的电子设备上,不需要PC和各种辅助设备。

基于FPGA的图像处理现状分析 摘要:本文首先介绍了现场可编程门阵列(FPGA)的基本特点和设计流程。针对图像处理中处理速度的瓶颈问题,本文回顾了基于FPGA的图像处理算法,包括图像的采集和压缩存储、预处理、图像检测、视频图像的实时处理和显示等。这些实现算法,在提高图像的处理速度上都有明显的效果,在图像的实时处理方面具有现实的意义。 关键字:FPGA,图像处理,实时,硬件设计. 1引言 随着数字多媒体技术的不断发展,数字图像处理技术被广泛应用于航空航天、通信、医学及工业生产等领域中,新开发的产品在图像存储容量、图像质量、图像处理速度等方面有了新的要求。数字图像处理,一般是通过对像素的一些运算提高图像质量,在图像处理过程中,虽然处理算法简单,但参与运算的数据量大,数据需多次重复使用,因此,图像处理往往是图像处理系统中最为耗时的环节,对整个系统速度影响较大。在当前图像处理算法研究已经很成熟的背景下,提高图像处理的时效性有很大的应用前景。随着微电子技术的高速发展,FPGA 为数字图像信号处理在算法、系统结构上带来了新的方法和思路。由于图像中的所有元素均可施以同样的操作,存在固有的并行性,非常适合于映射到FPGA架构中由硬件算法实现,使得图像的处理速度大大加快。对于数字图像处理,底层图像处理的数据量很大,要求处理速度快,但运算结果相对比较简单,以FPGA作为主要处理芯片的图像处理系统非常适合于对图像进行处理。 2现场可编程门阵列(FPGA)概述 FPGA(Field Programmable Gate Array)是一类高集成度的可编程逻辑器件,起源于美国的XILINX公司,该公司于1985年推出了世界上第一块FPGA芯片。FPGA技术结合了微电子技术、电路技术、EDA技术,使设计者可以集中精力进行所需逻辑功能的设计。与专用集成电路ASCI(Application Specific Integrated Circuit)相比,FPGA具有灵活性高、设计周期短、成本低、风险小等优势,因而得到了广泛应用。 随着工艺的发展和市场需求的扩大,超大规模、高速、低功耗的新型FPGA不断推陈出新。新一代的FPGA甚至集成了中央处理器(CPU)或数字处理器(DSP)内核[1],在一片FPGA开发板上进行软硬件协同设计,为实现片上可编程系统提供了强大的硬件支持。 目前,FPGA的主要发展动向是实现片上可编程系统,芯片朝着高密度、低电压、低功耗方向发展,实现在速度和集成方面的进一步提高。迄今为止,FPGA的品种繁多,主要有XILINX公司的Spartan、vertex、Atrix-7、Kintex-7系列,以及ALTERA公司的FIEX系列等。根据FPGA基本结构的不同,可以将其分为基于乘积项技术的FPGA和基于查找表技术的FPGA 两种。 FPGA主要有6个部分组成:可编程输入/输出单元、基本可编程逻辑单元、完整的时钟管理、内嵌SRAM、丰富的布线单元、底层嵌入功能单元和内嵌专用单硬件模块等。基于FPGA

基于FPGA的图像差分处理 1背景知识 差分图像在许多领域得到了广泛的应用,比如:视频压缩,生物医学诊断,天文学,遥感,人脸识别等。 2 matlab仿真MATLAB源码:Main.mI = imread(flower.bmp); figure, imshow(I);I_gray = rgb2gray(I);figure,imshow(I_gray);Id = mipcentraldiff(I_gray,dx); figure, imshow(Id);Mipcentraldiff.mfunction dimg = mipcentraldiff(img,direction)% MIPCENTRALDIFF Finite difference calculations %% DIMG = MIPCENTRALDIFF(IMG,DIRECTION)%% Calculates the central-difference for?a given direction% IMG : input image% DIRECTION : dx?or dy% DIMG : resultant image%% See also MIPFORWARDDIFF MIPBACKWARDDIFF MIPSECONDDERIV% MIPSECONDPARTIALDERIV% Omer Demirkaya, Musa Asyali, Prasana Shaoo, ... % Medical Image Processing Toolboximg = padarray(img,[1 1],symmetric,both);[row,col] = size(img);dimg = zeros(row,col);switch(direction)casedx,dimg(:,2:col-1) = (img(:,3:col)-img(:,1:col-2))/2;casedy,dimg(2:row-1,:) = (img(3:row,:)-img(1:row-2,:))/2;otherwise,disp(Direction is unknown);enddimg = dimg(2:end-1,2:end-1);仿真结果: 图1 RGB原图 图2 gray 图3 central_diff 3 FPGA设计 图4 基于串口传图的中心差分 如图4所示,我们将RGB565格式转化为Ycbcr格式,Y通道进入中心差分模块,完成中心差分算法。

基于FPGA的高速图像处理系统的设计 摘要: 在本文中,设计了一个高速图像处理系统,是为了解决这样的问题,如出现在车载计算机图像处理中的低系统集成,低速的处理过程。通过配置Nios II软核CPU和一些基于主要硬件FPGA的图像预处理,处理和显示的功能模块和设计的系统软件,使得该系统实现了图像的采集,记忆和重叠功能。由于采用可编程芯片和并行处理技术,该系统集成度高,好维修,图像处理速度快、实时性强。 关键词:图像处理,FPGA,Nios II CPU。 I.介绍 近年来,车载计算机中存在的主要问题集中在两个方面。首先,在使用低功率损耗的PowerPC CPU的状态下,对于图像的采集和显示,一个集成板是必需的。其次,随着视频图像和红外热像仪的广泛使用,还有电子一体化的发展,应该设计出一个高速的图像处理系统。 为了解决这两个主要的问题,作者设计了一个基于FPGA的高速图像处理系统用来识别重叠的多通道图像信息。功能模块,比如图像采集,处理和显示,都可以在一个单一的FPGA芯片上实现,它减少了外围电路,提高整个系统的性能。因为并行处理技术,处理速度和实时性都大大的提高。

II.图像处理算法分析 A.基于双线性插值的图像放大 基于像素的放大倍率的方法原理简单、快速,但它只是复制原始像素的邻域。随着放大系数增大,图像会出现明显的块锯齿,不能保留原始图像的边缘信息。这个问题是可以通过双线性插值来解决。双线性插值可以消除锯齿,保留原始图像的边缘信息和获得更好的视觉效果。 图1.原始图像(略) 图2.放大图像(略) 图1是原始图像,其中f ij,f i,j+1,f i+1,j,f i+1,j+1是相邻的像素块。图2是在水平方向上放大K倍,在垂直方向放大L倍的图像。f ij,f i,j+1,f i+1,j,f i+1,j+1在放大图像中只改变位置但像素值保持不变。因此,我们可以得到以下方程:

基于FPGA的VGA图像显示 1、VGA显示原理 VGA标准是一种计算机显示标准,最初是由IBM公司在1987 年提出的,分辨率是640*480。VGA 接口也叫做D_Sub 接口,是显卡上输出模拟信号的接口。目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的D/A 转换器转变为R、G、B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。 常见的彩色显示器一般由阴极射线管(CRT) 构成,彩色由GRB(Green Red Blue) 基色组成。显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生 GRB 基色,合成一个彩色像素。扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。 要实现VGA显示就要解决数据来源、数据存储、时序实现等问题,其中关键还是如何实现VGA时序。VGA的标准参考显示时序如图1所示。行时序和帧时序都需要产生同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序段(Display interval c)和显示前沿(Front porch d)四个部分。 2、方案设计 由VGA的显示原理可知,该任务的关键是VGA时序控制部分和汉字图形显示部分: (1)VGA时序控制部分,采用FPGA本地50MHz时钟,根据所需时序要求,经Verilog 语言编写的计数模块分频而得到,该部分十分重要,如果产生的时序有偏差,那么就会使汉字图形无法显示或显示结果混乱;

基于FPGA的数字CMOS摄像机图像采集 一、数据采集系统概述 数据采集是指将以各种形式输入的被测信号,包括语音信号、温度信号、湿度信号、图像信号等经过适当处理,成为计算机可以识别的数字信号,从而送入计算机进行存储处理的过程,数据采集卡就是典型的基于数据采集系统原理的集成计算机扩展卡。如图1所示,在数据采集过程中主要有几个关键部分:(1)输入信号的幅度较小或者过大,需要经过放大器单元将输入信号幅度放大或者缩小;(2)输入信号带有较大的噪声,需要经过一个硬件的模拟滤波单元,将信号滤波整形;(3)将信号送到AD进行模数转换;(4)将信号传输到计算机;(5)存储记录和处理数据。 图1数据采集过程 通常认为如果数字逻辑电路的频率超过50MHz,而且工作在这个频率之上的电路已经 占到了整个电路系统的三分之一以上,就称为高速电路。相应的,对于并行采样系统,如果采样频率达到50MHZ,数据量并行8bit以上;对于串行采样系统,如果采样频率达到200MHz,一般将这种采样系统也称为高速数据采集。目前高速数据采集使用较多的采样频率一般在 50M~100MHz之间。采集系统分模拟系统和数字系统,大多数字采集系统中,CMOS图像 传感器是系统的成像部件,它是系统的“眼睛”,能够捕获高速运动物体的图像,此模块是将采集的模拟图像转化为数字信号输出;图像处理模块是系统的中间缓存处理部分,此模块为了消除或降低前期采集携带噪声的影响,提高图像质量,将庞大的数据量进行压缩,以减小对存储介质容量的要求;数据传输模块是系统与外设搭建的桥梁,此模块是将实时采集的数据高速传输,给外设提供信息。 二、总体方案设计 方案1: 图像数据的传输通过USB总线技术完成系统的初始化以及将最终的传输信号准确无误 地传送到上位机上。USB技术具有简单化、通用性、可靠性、热插拔、传输速率高等优点,随之带来的是应用USB技术的复杂程度高、总线传输协议需要协调等问题。 方案2: 利用两片SDRAM进行图像数据的短时间存储并快速传输,SDRAM是多Bank结构,

摘要:许多关于图像中比较重要的信息都在图像的边缘包含着,图像边缘检测作为图像处理的重要组成部分,在许多领域有着重要的应用。图像边缘检测在很大程度上减少了数据的量,并且除去了一些并不是特别相关的信息,但是却保留了对于图像来说重要的结构属性,数据量大,重复度高是边缘检测算法最主要的特点。由于FPGA的算法在硬件处理中速度快、而且可以用来直接编程、可重配置等各种特点,因此它在图像处理中占有很重要的位置,为此文章提出了运用FPGA实现边缘检测的方法,并且根据FPGA的特性,对Sobel算子进行了FPGA设计与实现以及仿真,并且对几种边缘检测算子进行了比较。仿真中通过改变程序中的阈值可以得到不同的处理效果,这也是利用FPGA的优点,方便容易、速度也得到了提高,并且可编程、可重配置,使得FPGA在数字图像处理方面显得非常优越。 关键词:边缘检测;FPGA;图像处理;Sobel算子;Prewitt算子 The design of image edge detection technology based on FPGA Abstract:Many important information about the image is contained at the edge of the image,Image edge detection is an important part of image processing,It is important in many fields .Image edge detection greatly reduces the amount of data,And removed some information that is not particularly relevant,But it preserves the structural attributes that are important to the image,Large amount of data,High repetition is the most important feature of edge detection algorithm.Because the FPGA algorithm is fast in hardware processing、And can be used for direct programming, reconfiguration and other characteristics,Therefore, it plays an important role in image processing,For this reason, a method of edge detection using FPGA is proposed,And according to the characteristics of FPGA,FPGA design, implementation and Simulation of Sobel operator are carried out,And several edge detection operators are compared.In simulation, different processing results can be obtained by changing the thresholds in the program,This is also the advantage of using FPGA, which is convenient, easy and fast,And programmable and reconfigurable, enabling FPGA to be very good in digital image processing.

基于FPGA的VGA彩条图像显示 1. 设计的任务及内容 在电子电路领域中,设计自动化工具已经被广大电子工程师所接受,它必将取代人工设计方法并成为主要的设计手段。目前,Verilog语言已经成为各家EDA工具和集成电路厂商认同和共同推广的标准化硬件描述语言,随着科学技术的迅猛发展,电子工业界经历了巨大的飞跃。集成电路的设计正朝着速度快、性能高、容量大、体积小和微功耗的方向发展,这种发展必将导致集成电路的设计规模日益增大。 该实训的设计是用Verilog语言硬件描述语言设计出一个VGA图象显示控制器,用Verilog 硬件描述语言进行编程,把Verilog语言描述的VGA图象显示控制器所需的程序在QuartusⅡ软件环境下进行模拟仿真,以此来验证所设计的结果是否满足设计的要求。在结果符合要求的情况下把Verilog程序下载到FPGA器件上,利用FPGA器件内部存储器存储所需要的数据,再通过VGA接口输出到显示器上,从而达到设计的要求。 VGA显示器因为其输出信息量大,输出形式多样等特点已经成为现在大多数设计的常用输出设备,FPGA以其结构的优势可以使用很少的资源产生VGA的各种控制信号。 CRT显示器作为一种通用型显示设备,如今已广泛应用于我们的工作和生活中。与嵌入式系统中常用的显示器件相比,它具有显示面积大、色彩丰富、承载信息量大、接口简单等优点,如果将其应用到嵌入式系统中,可以显著提升产品的视觉效果。如今随着液晶显示器的出现,越来越多的数字产品开始使用液晶作为显示终端。但基于VGA标准的显示器仍是目前普及率最高的显示器[1]。若驱动此类显示器,需要很高的扫面频率,以及极短的处理时间,正是由于这些特点,所以可以用FPGA来实现对VGA显示器的驱动。本次专业课程设计即选用FPGA 来实现VGA的显示。 随着FPGA的不断发展及其价格的不断下降,FPGA的可编程逻辑设计的应用优势逐渐显现出来。现在,越来越多的嵌入式系统选择了基于FPGA的设计方案。在基于FPGA的大规模嵌入式系统设计中,为实现VGA显示功能,既可以使用专用的VGA接口芯片如SPX7111A等,也可以设计和使用基于FPGA的VGA接口软核。虽然使用VGA专用芯片具有更稳定的VGA时序和更多的显示模式可供选择等优点,但设计和使用VGA接口软核更具有以下优势:(1)使用芯片更少,节省板上资源,减小布线难度;(2)当进行高速数据传输时,具有更小的高频噪声干扰;(3) FPGA(现场可编程门阵列)设计VGA接口可以将要显示的数据直接送到显示器,节省了计算机的处理过程,加快了数据的处理速度,节约了硬件成本。 1.1 FPGA简介 FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分[9]。FPGA的基本特点主要有: 1)采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。 2)FPGA可做其它全定制或半定制ASIC电路的中试样片。 3)FPGA内部有丰富的触发器和I/O引脚。 4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。 5) FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。 1

基于FPGA的图像处理的研究 图像处理是用计算机对图像进行分析,以达到所需的结果的一种技术,又称为影像处理。它是对图像进行操作从而得到自己想要的结果,它是一个非常广义的概念,包含图像增强、图像复原、图像重建、图像分析、模式识别、计算机视觉等N多个应用方向。这些应用技术有许多在本质上是相通的,但是不同应用领域的关注点往往是不同的。 FPGA做图像处理的优势 用FPGA做图像处理最关键的一点优势就是:FPGA能进行实时流水线运算,能达到最高的实时性。因此在一些对实时性要求非常高的应用领域,做图像处理基本就只能用FPGA。例如在某些分选设备中图像处理基本上用的都是FPGA,因为在相机中从看到物料图像到给出执行指令之间的延时大概只有几毫秒,这就要求图像处理必须很快且延时固定,只有FPGA进行的实时流水线运算才能满足这一要求。

要了解FPGA进行图像处理的优势就必须理解FPGA所能进行的实时流水线运算和DSP,GPU等进行的图像处理运算有何不同: DSP,GPU,CPU对图像的处理基本是以帧为单位的,从相机采集到的图像数据会先存在内存中,然后GPU会读取内存中的图像数据进行处理。假如采集图像的帧率是30帧,那么DSP,GPU要是能在1/30秒内完成一帧图像的处理,那基本上就能算是实时处理。 而FPGA对图像进行实时流水线运算是以行为单位的。FPGA可以直接和图像传感器芯片连接采集图像数据流,如果是RAW格式的还可以通过差值来获得RGB图像数据。FPGA能进行实时流水线处理的关键是它可以用内部的Block Ram缓存若干行的图像数据。Block Ram可以说是类似于CPU里面的Cache,但Cache不是你能完全控制的,而Block Ram是完全可控的,可以用它实现各种灵活的运算处理。这样FPGA通过缓存若干行图像数据就可以对图像进行实时处理,数据就这样一边流过就一边处理好了,不需要送入DDR缓存了之后再读出来处理。 FPGA图像处理之路,从此开始 用FPGA做图像处理相关的开发时,往往我们首先要考虑的是FPGA处理板的性能,因为做图像处理是一个十分消耗资源的事情。从网上可以搜索到很多图像处理FPGA开发板,有些开发板上的资源十分丰富,可以满足我们前期试验的需求。 FPGA在图像处理方面的主要应用于图像的预处理阶段。

基于FPGA的图像采集系统设计 前言 随着科技社会的发展,图像采集系统在日常生活、工业生产、国家安全等众多领域得到广泛的应用,具有广阔的应用前景和研究价值。采用FPGA进行设计的图像采集系统有良好的扩展性能和相对稳定的硬件结构。主要工作如下: 1)分析图像采集和图像处理的原理和特点,设计硬件电路的原理图,完成系统PCB板图的设计。 2)针对FPGA进行内部功能模块的划分,使用Verilog HDL硬件描述语言进行设计。 3)利用SOPC Builder 完成NIOS处理器软核及其外设的创建和配置。 4)根据FPGA内部硬件电路的特点,选择适合FPGA的算法,并对算法进行优化。 5)在NIOS II IDE环境下用Verilog HDL语言编写图像传感器控制、图像采集、SRAM读写控制、图像显示等程序,实现完整的图像采集系统功能。 1课题分析 1.1 选题背景(含国内外相关研究综述及评价)与意义 EDA技术的发展和应用普及性越来越高,已经涉及到现代电子产品设计的各个系统、各个领域中。之所以有这样的广泛应用,主要得益于可编程逻辑器件的长足发展和日益成熟,可编程逻辑器件(Programmable Logic Device, PLD)是一种半定制集成电路,在其内部集成了大量的门和触发器等基本逻辑单元电路,通过用户编程来改变PLD内部电路的逻辑关系或连线,从而得到所需要的电路设计功能。这种新型逻辑器件,不仅速度快、集成度高,能够完成用户定义的逻辑功能,还可以加密和重新定义编程,其允许编程次数可以达到上万次。可编程逻辑器件的出现,大大改变了传统数字系统设计方法,简化了硬件系统、降低成本、提高系统的可靠性、灵活性。因此,自20世纪70年代问世以后,PLD受到广大工程师的青睐,被广泛应用于工业控制、通信设备、仪器仪表和医疗电子仪器等众多领域,为EDA技术开创了广阔的发展空间。 VGA作为一种标准的显示接口,在视频和计算机领域得到了广泛的应用。VGA图像信号发生器是电视台、电视机生产企业、电视维修人员常用的仪器,其主要功能就是产生标准的图像测试信号。对VGA而言,其主要应用在工业控制领域,通过VGA接口实现将信息、图像、文字等内容显示各种VGA显示器上,为客户提供一种完美的显示界面,也是目前重要的显示终端。本次实验设计主要是基于FPGA芯片为处理器,利用硬件描述语言完成VGA的时序控制,并利用相应的实验平台,进行设计验证,基本实现了VGA 的彩条信号和图像显示效果,达到了整个设计目标和要求。

2015年暑期实践报告 ——基于FPGA的视频图像处理技术1 课题背景 人类接收的信息中约有70%来自视觉,周围景物在人眼视网膜上的映射是人类最有效、最重要的信息交流方式。视频具有确切、直观、具体生动、真实和高效的特点。随着计算机软硬件技术和电子技术的飞速发展,视频图像技术也得到了迅速的发展。视频图像在商业、工业、军用以及民用领域内得到了广泛的应用,例如,监控系统、电视会议、多媒体通信、数字娱乐、可视电话等。 在视频应用系统的各个环节中,如采集、传送、转换和显示等,不可避免的造成图像质量的下降。例如,在摄影时由于外界环境的影响如光照过强或不足,将会使图像过亮或过暗;光学系统由于电子设备等各种原因产生的失真、大气的流动等将会使图像变得模糊;信道的传输以及系统的硬件将会引入不同种类的噪声等。这些问题不仅影响我们的视觉效果,而且对后续的处理带来了麻烦,如视频图像的存储、传输、跟踪与识别等。因此图像处理技术相应产生了,对图像进行相应的处理和加工来满足人们的视觉要求和后续的应用需求。 由于视频图像处理技术要求对图像进行实时的数据采集、压缩处理、可靠传输和显示,整个过程对实时性的要求提到了一个很高的水平。再者,视频图像往往数据量很大,对其进行处理会占用很多系统资源,如果处理器处理能力差会对图像的实时性传输造成很大影响,并且也会影响图像的质量。为此,整个系统对处理器运算能力和数据的实时性优先考虑。当前,DSP(数字信号处理器)或者FPGA(现场可编程门阵列)常作为视频图像处理的核心处理单元。但是由于DSP 本身的一些特性,使其不宜在此视频图像处理上得到广泛应用。这包括DSP的指令执行采用速度相对较慢的串行通信形式,并且相对固定化的运算操作模块很难完全满足如此全面的需求。因此在设计时选取了运行速度更快、设计更加灵活的FPGA控制芯片。除此之外FPGA还具有开发周期相对较短,系统维护和扩展容易,对信号实时处理能力强,这些特征都可显著提高视频图像数据处理的速度,满足对系统实时性的要求。所以,设计中优先选择了FPGA芯片作为系统的核心处理芯片。 在机载座舱中,由于使用环境的特殊性和复杂性,机载任务处理机给出的视频图像信号在最终输出显示前,需要进行一定的处理,以满足飞行员在不同环境下的观察需要,同时机载显示器对画面显示的实时性有着较高的要求。基于FPGA硬件平台的图像处理方式不仅能够获得良好的处理效果,而且处理速度也