基于FPGA的LCD驱动显示电路的设计与实现

- 格式:doc

- 大小:627.00 KB

- 文档页数:22

基于FPGA的MIPI CSI-2图像采集系统设计赵清壮【摘要】This paper elaborates a design of MIPI CSI-2 high-definition camera interface image acquisition system based on FPGA. Now, MIPI high-definition CCD is used widely, this design uses FPGA to achieve MIPI high-definition CCD collect and provides two outputs of LCD screen and USB, the data transmission is stable and reliable, it make MIPI interface camera applied widely by the other circuit systems, accelerates system development and saves cost.%阐述一种基于FPGA的MIPI CSI-2接口高清摄像头图像采集系统设计,该设计用FPGA实现当前应用广泛的MIPI高清CCD采集,并提供LCD屏、USB两路输出,数据传输稳定可靠,把MIPI接口摄像头应用到更广泛的其他电路系统中,加快系统开发,节省成本。

【期刊名称】《价值工程》【年(卷),期】2015(000)029【总页数】2页(P84-85)【关键词】MIPI;CSI-2;图像采集;FPGA【作者】赵清壮【作者单位】广州飒特红外特股份有限公司,广州510000【正文语种】中文【中图分类】TP302.10 引言CSI(Camera Serial Interface)是由MIPI(Mobile Industry Processor Interface)联盟下Camera工作组制定的接口标准,是MIPI联盟发起的为移动应用处理器制定的开放标准,MIPI联盟由ARM、诺基亚、意法半导体和德州仪器发起成立,作为移动行业领导者的合作组织,MIPI联盟旨在确定并推动移动应用处理器接口的开放性标准。

基于STM32单片机FSMC接口驱动LCD的配置与分析概述:STM32单片机是一款高性能、低功耗的32位ARM Cortex-M系列微控制器。

它具有丰富的外设接口,其中包括FSMC(Flexible Static Memory Controller)接口,用于连接外部存储器,例如LCD显示器。

本文将详细介绍如何配置和驱动LCD显示器,以及分析FSMC接口的工作原理。

一、LCD驱动接口配置1. 在STM32的标准外设库中,FSMC的配置函数位于STM32F10x_stdperiph_driver库的stm32f10x_fsmc.c和stm32f10x_fsmc.h文件中。

通过这些函数,可以配置FSMC接口的参数,以使它能够连接和驱动LCD。

2.首先,需要配置FSMC的时钟预分频值。

根据LCD的要求以及系统时钟频率,选择适当的预分频值。

这可以通过设置FSMC_BCRx寄存器中的MBKEN和PS字段来实现。

3.然后,需要配置FSMC的存储芯片选择使能信号(CSEN)和片选信号(ALE)。

这可以通过设置FSMC_BCRx寄存器中的CSEN和ALEN字段来实现。

4.接下来,需要配置FSMC的读写延迟、数据宽度、存储器类型等参数。

这可以通过设置FSMC_BTRx和FSMC_BWTRx寄存器来实现。

5.最后,需要配置FSMC的地址线、数据线和控制线的映射关系。

这可以通过设置FSMC_BCRx寄存器中的MWID、MTYP、MUXEN、MWID和NWID 字段来实现。

二、FSMC接口工作原理1.FSMC接口是一种高速并行接口,它通过多路复用来连接不同的外部存储器。

它具有独立的读/写数据线和地址线,以及控制线,用于选择读/写操作和片选信号。

2. FSMC接口支持不同类型的存储器,例如SRAM、NOR Flash、NAND Flash和LCD。

每种存储器都有不同的时序和接口要求。

3.FSMC接口的时序参数主要包括时钟预分频值、读/写延迟、数据宽度和地址线宽度等。

基于FPGA的LVDS学习报告讲解FPGA(Field Programmable Gate Array)是一种基于可编程逻辑门阵列的可重构数字电路集成电路。

LVDS(Low Voltage Differential Signaling)是一种低压差分信号传输技术,常用于高速数据传输。

本文将介绍基于FPGA的LVDS技术,并讲解其原理和应用。

首先,我们来看一下LVDS的原理。

LVDS技术通过在传输线上同时传输正向和反向的差分信号来传输数据。

这种方式能有效地抑制噪声和串扰,提供更高的传输速率和更低的功耗。

LVDS技术通常使用一个驱动器和一个接收器对数据进行发送和接收。

在FPGA中,我们可以使用LVDS技术实现高速数据传输。

FPGA通常具有多个I/O引脚,可以配置为差分信号输入和输出。

通过将这些引脚与LVDS驱动器和接收器连接起来,可以实现高速数据传输。

FPGA还可以根据需要对LVDS信号进行配置和控制。

LVDS技术在许多应用中发挥着重要的作用。

例如,在高速通信中,LVDS可以用于将数据从传感器传输到处理器。

在图像处理中,LVDS可以用于将图像数据从摄像头传输到FPGA进行处理。

此外,LVDS还可以用于高速数据存储和传输,例如在存储器和计算机之间。

除了上述应用,LVDS技术还广泛应用于显示器接口。

例如,LVDS可以用于将图形数据从图像处理器传输到LCD显示器。

由于LVDS技术具有高速传输和抗干扰能力,因此能够提供高质量的图像显示效果。

需要注意的是,LVDS技术的配置和控制需要一定的专业知识和技术。

首先,需要对FPGA进行编程和配置,以正确地设置LVDS引脚的功能和性能参数。

其次,需要使用适当的连接线缆和接插件将LVDS驱动器和接收器与FPGA和其他设备连接起来。

最后,需要进行测试和调试,以确保LVDS系统的正常运行。

总之,基于FPGA的LVDS技术是一种高速数据传输技术,具有抗干扰能力强、传输速率高和功耗低的优点。

基于FPGA的实用多功能信号发生器的设计与制作基于FPGA的实用多功能信号发生器的设计与制作摘要多功能信号发生器已成为现代测试领域应用最为广泛的通用仪器之一,代表了信号源的发展方向。

直接数字频率合成(DDS)是二十世纪七十年代初提出的一种全数字的频率合成技术,其查表合成波形的方法可以满足产生任意波形的要求。

由于现场可编程门阵列(FPGA)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS技术,极大的提高函数发生器的性能,降低生产成本。

本文首先介绍了函数信号发生器的研究背景和DDS的理论。

然后详尽地叙述了利用Verilog HDL描述DDS模块的设计过程,以及设计过程中应注意的问题。

文中详细地介绍了多种信号的发生理论、实现方法、实现过程、部分Verilog HDL代码以及利用Modelsim仿真的结果。

文中还介绍了Altera公司的DE2多媒体开发平台的部分功能及使用,并最终利用DE2平台完成了多功能信号发生器的大部分功能。

包括由LCD显示和按键输入构成的人机界面和多种信号的发生。

数字模拟转换器是BURR-BROWN 公司生产的DAC902。

该信号发生器能输出8种不同的信号,并且能对输出信号的频率、相位以及调制信号的频率进行修改设定。

关键词:信号发生器;DDS;FPGA;DE2Practical FPGA-based multi function signal generatordesign and productionAbstractMulti function signal generator has become the most widely used in modern testing field of general instrument, and has represented one of the development direction of the source. Direct digital frequency synthesis (DDS) is a totaly digital frequency synthesis technology, which been put forward in the early 1970s. Using a look-up table method to synthetic waveform, it can satisfy any requirement of waveform produce. Due to the field programmable gates array (FPGA) with high integrity, high speed, and large storage properties, it can realize the DDS technology effectively, increase signal generator’s performance and reduce production costs.Firstly, this article introduced the function signal generator of the research background and DDS theory. Then, it described how to design a DDS module by Verilog HDL, and introduced various signal occurs theory, method and the implementation process, Verilog HDL code and simulation results.This paper also introduces the function of DE2 multimedia development platform, and completed most of the functions of multi-function signal generator on DE2 platform finally. Including the occurrence of multiple signal and the man-machine interface which composed by LCD display and key input. Digital-to-analog converters is DAC902, which produced by company BURR-BROWN.This signal generator can output eight different kinds of signals, and the frequency of the output signal, phase and modulation frequency signal also can be modifyed.Key Words: Signal generator; DDS; FPGA; DE2目录论文总页数:34页1 引言 (1)1.1课题背景 (1)1.2国内外波形发生器的发展现状 (1)1.3本文研究的主要内容 (2)2 信号发生器原理 (2)2.1直接数字频率合成技术的基本原理 (2)2.2相位偏移控制 (3)2.3多种信号的发生 (3)2.3.1方波的发生 (3)2.3.2三角波发生 (4)2.2.3锯齿波发生 (4)2.3.4 PWM信号发生 (4)2.3.5 SPWM信号发生 (5)2.3.6 AM信号发生 (5)2.3.7 FM信号发生 (6)2.4DDS的特点 (7)2.4.1 DDS 的优点 (7)2.4.2 DDS 系统的缺点 (7)3 系统整体设计 (8)3.1硬件部分 (8)3.1.1 DE2实验板 (8)3.1.2 LCD模块 (9)3.1.2 DAC902 (11)3.2基于VERILOG的FPGA设计 (12)3.3软件工具 (12)3.3.1 Modelsim (12)3.3.2 Quartus (12)3.4系统设计 (13)3.4.1 系统初始化模块 (13)3.4.2按键模块和LCD模块 (13)3.4.3 RAM模块 (14)3.4.4数据转换模块 (15)3.4.5 DAC驱动模块 (15)3.4.6系统的运行 (15)4 VERILOG HDL代码实现与仿真 (15)4.1信号发生器模块 (15)4.1.1频率控制字和相位累加器 (15)4.1.2 相位偏移控制 (16)4.1.3正弦波发生模块 (17)4.1.4 方波发生模块 (17)4.1.5 三角波发生模块 (18)4.1.6 锯齿波发生模块 (18)4.1.7 PWM信号发生模块 (19)4.1.8 SPWM信号发生模块 (19)4.1.9 AM信号发生模块 (20)4.1.10 FM信号发生模块 (21)4.2按键输入模块 (22)4.3LCD显示模块 (23)4.4RAM模块 (24)4.5数据转换模块 (25)5 系统测试 (26)5.1控制及显示部分测试 (27)5.2输出频率测试 (27)5.3信号发生测试 (28)5.3.1 正弦波、方波、三角波、锯齿波测试 (28)5.3.2 PWM信号测试 (29)5.3.3 SPWM信号测试 (29)5.3.4 AM信号测试 (29)5.3.5 FM信号测试 (30)结论 (31)参考文献 (32)致谢...................................................... 错误!未定义书签。

电子电路设计与方案0 前言现场可编程门阵列具有运行速度快,修改灵活方便,并自带大量的输入输出端口等优点,通过FPGA实现该信号发生器的核心部件DDS模块,可以灵活地对信号发生器的参数进行调整,另外通过单片机的配合实现对其他外设电路的控制,实现信号发生器显示、参数调节等辅助的功能,通过数模转换电路和波形处理电路实现所需信号波形的输出。

本设计的主要指标为:(1)频率范围:0~1MHz,可通过键盘任意设置频率,步进1Hz。

(2)频率精度:±1%。

(3)幅值范围:±5V,可通过键盘任意设置幅度,步进100mV。

(4)幅值精度:±5%。

(5)用液晶显示所选波形名称,频率,幅值。

1 系统硬件结构该信号发生器主要是由FPGA构成其最小系统,通过编程实现信号发生器的主要功能部件数字频率合成功能模块,并对其信号进行控制和处理,使得输出波形更加平滑、符合要求。

当然为了使电路能够实现人机对话、参数设置等功能,并设计了由单片机和外围电路构成的控制电路部分,实现对显示电路、输入电路的控制。

本系统通过单片机来识别按键所输入的指令,并根据其该指令,产生输出波形的参数要求,并将该数据送入FPGA 的ROM中,再由FPGA完成DDS数据处理功能(频率控制、移相等),将波形数据送入D/A转换器,并将波形参数(如频率、幅值等)送入到显示电路中显示,最后通过低通滤波电路滤波使输出的波形平滑。

系统硬件结构如图1所示。

本设计未采用专用DDS芯片,而是通Verilog HDL语言编程在目标芯片上来实现信号源的主要功能,可以根据实际设计的要求来增删DDS的功能,具有灵活、方便等特点,同时该DDS模块中的参数及子模块根据所用目标器件稍加调整,完全可用于其他需要DDS技术的应用场合,有很好的通用性。

图1 系统硬件结构图2 单元电路的设计整个硬件系统以FPGA为核心,配合外围电路控制参数实现波形的模拟输出。

外围电路主要包括控制电路及信号处理电路两部分。

第 38 卷第 11 期2023 年 11 月Vol.38 No.11Nov. 2023液晶与显示Chinese Journal of Liquid Crystals and Displays基于FPGA的Winograd算法卷积神经网络加速器设计与实现牛朝旭1,2,孙海江1,2*(1.中国科学院长春光学精密机械与物理研究所,吉林长春 130033;2.中国科学院大学,北京 100049)摘要:为实现卷积神经网络在低功耗、边缘计算等场景中的加速计算,设计了一种基于现场可编程门阵列(FPGA)的Winograd算法卷积神经网络加速器。

首先,将图像数据和权重数据量化为8位定点数,并设计了硬件卷积计算过程中的量化流程,提升了数据传输速度和计算速度。

接着,设计了输入数据缓存复用模块,将多输入通道数据融合后传输,复用了行重叠数据。

然后设计了Winograd流水线卷积模块,实现列数据的组合复用,从而最大化重用了片上数据,降低了片上数据存储的占用和带宽压力。

最后将加速器在Xilinx的ZCU104开发板上部署。

经过实验验证,加速器的卷积层计算性能达到354.5 GOPS,片上DSP计算效率达到0.69,与相关研究相比,实现了1.6倍以上的提升。

该加速器能够以高能效比完成基于VGG-16网络的遥感图像分类任务。

关键词:卷积神经网络;现场可编程门阵列;Winograd算法;流水线;并行计算中图分类号:TP332 文献标识码:A doi:10.37188/CJLCD.2023-0013Design and implementation of convolution neural network accelerator for Winograd algorithm based on FPGANIU Zhao-xu1,2,SUN Hai-jiang1,2*(1.Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences,Changchun 130033, China;2.University of Chinese Academy of Sciences, Beijing 100049, China)Abstract: In order to realize the acceleration of convolutional neural network in low-power, edge computing and other scenarios, a Winograd algorithm convolutional neural network accelerator based on field programmable gate array (FPGA) is designed. Firstly, the image data and weight data are quantized into 8-bit fixed-point numbers, and the quantization process in the hardware convolution calculation process is designed to improve data transmission speed and calculation speed.Secondly,the input data buffer multiplexing module is designed, which fuses the data of multiple input channels and transmits them, reusing the row overlapping data.Then,the Winograd pipeline convolution module is designed to realize the combined reuse of 文章编号:1007-2780(2023)11-1521-10收稿日期:2023-01-13;修订日期:2023-02-04.基金项目:吉林省科技发展计划(No.20200404155YY)Supported by Jilin Province Science and Technology Development Plan (No.20200404155YY)*通信联系人,E-mail:sunhaijing@第 38 卷液晶与显示column data, so as to maximize the reuse of data on chip and reduce the occupation of data storage on chip and bandwidth pressure. Finally, the accelerator is deployed on the ZCU104 development board of Xilinx. Experimental verification shows that the convolution layer computing performance of accelerator reaches to 354.5 GOPS, and the on-chip DSP computing efficiency reaches to 0.69, which is more than 1.6 times higher than relevant research. The accelerator can complete remote sensing image classification task based on VGG-16 network with high energy efficiency ratio.Key words: convolution neural network;field programmable gate array;winograd algorithm;assembly line; parallel computing1 引言卷积神经网络被广泛应用于许多深度学习系统中,并在全息图像重建[1]、光学计量[2]和自动驾驶[3]等多种计算机视觉任务中取得了显著的成效。

摘要高速数字化采样技术和FPGA技术的发展,已经开始对传统测试仪器,包括现有的数字化仪器发展产生着深刻的影响,对传统仪器体系结构,传统测量方法,传统仪器的定义和分类等都将产生深刻的变革。

近几年来,数字仪器通常采用DSP或FPGA结构,从信息处理技术的发展上看,以FPGA为基础的软件硬件化是其重要的发展方向,本文设计的基于FPGA的数字示波器,是由单片机和FPGA相结合的方式组成,即用单片机完成人机界面,系统调控,用FPGA完成数据采集,数据处理等功能。

由通道输入调整,数据采集,数据处理,波形显示和操作界面等功能模块组成,系统中的数据采集及数据处理模块,采用了FPGA 内制的RAM IP核,使系统的工作频率基本不受外围器件影响。

设计中采用了自顶向下的方法,将系统按逻辑功能划分模块,各模块使用VHDL语言进行设计,在ISE中完成软件的设计和仿真关键词:FPGA 数字示波器数字采样AbstractHigh-speed digital sampling and FPGA technology has begun to influnence the development of traditional test equipment, including existing digital instruments , the architecture of traditional instruments, traditional measurement methods, definition and classification of traditional instruments and so will produce profound changes.In recent years, independent instrument is made up of DSP or FPGA structure, from the point of information processing technology development, to FPGA based hardware of software is an important direction of development, the paper design FPGA-based digital oscilloscope, which combines a single chip and FPGA , namely, with a microcontroller for interface and system control, with the FPGA for data acquisition, data processing and other functions. It is made up of adjustable channel input, data acquisition, data processing,waveform display and user interface features such as modules, the system of data collection and data processing module, using the FPGA within the system RAM IP core, which make a great significance on the data processing speed and real-time entry requirements. Using top-down approach, the system is logical and functional modules, each module is designed using the VHDL language, completed in the ISE software .Keywords: FPGA,Digital Oscilloscope,Digital Sampling目录摘要 (1)第一章绪论 (5)1.1研究概况与意义 (5)1.2 主要工作 (6)第二章数字示波器的工作原理 (8)2.1 工作原理框图 (8)2.1.1 数字示波器系统框图 (8)2.2 采样定理 (9)2.3 频率测量 (10)2.3.1高频双计数器测量方法 (10)2.3.2大范围双计数器测量法 (11)2.3.3 等精度测量法 (11)2.4扫描速度 (12)第三章硬件电路 (13)3.1 系统组成结构 (13)3.2放大电路 (14)3.2.1程控衰减放大器电路 (15)3.2.2 ADS830的应用 (16)3.2.3 放大器AD603介绍 (17)3.3整形电路 (20)3.3.1信号整形电路设计 (20)3.4采样与保持电路 (21)3.4.1 随机采样 (21)3.4.2 采样与保持电路设计 (22)3.5 数据采集电路 (22)3.5.1 FIFO的选择 (23)3.5.2 随机采样展宽电路 (23)3.6 电路的保护及滤波处理 (24)第四章 FPGA软件设计及仿真 (25)4.1分频电路及产生A/D转换器的控制信号 (25)4.2 FIFO功能单元设计 (26)4.3双口RAM (27)4.4液晶显示及键盘模块 (27)4.5系统软件住程序设计 (28)第五章实验结果 (29)5. 1 垂直灵敏度测试 (29)5. 2 水平扫描速度的测试 (29)总结 (30)参考文献 (31)第一章绪论与传统模拟示波器相比,数字示波器不仅具有可存储波形、体积小、功耗低,使用方便等优点,而且还具有强大的信号实时处理分析功能。

基于FPGA数字电压表设计目录1系统设计 (3)1.1 控制模块方案的比较 (3)1.2 A/D转换方案的比较 (4)1.3 显示方案的比较 (4)1.4 总体方案设计 (5)1.5 系统的基本原理 (5)2 单元电路设计 (6)2.1 A/D转换部分 (6)2.1.1 ADC0809工作原理 (6)2.1.2 ADC0809工作时序 (7)2.1.3 档位控制电路 (8)2.2 FPGA功能模块的设计 (8)2.2.1 码制变换模块 (8)2.2.2 显示控制及驱动模块 (9)3 软件设计 (9)3.1 开发软件及编程语言简介 (9)3.2 程序流程图 (9)4 系统测试 (10)4.1 测试仪器清单 (10)4.2 测试及误差计算 (10)参考文献 (11)附录1 程序清单 (11)1 系统设计1.1控制模块方案的比较方案一:采用3位半数字电压表。

采用此方案电路结构简单,易于实现且易于维护。

它的核心器件是一个双积分式A/D转换,双积分式DVM属于V—T变换式,其基本原理是在一个测量周期内,首先将被测电压UX加到积分器的输入端,在确定的时间内进行积分,也称定时积分;然后切断UX,在积分器的输入端加与UX极性相反的电压UR,由于UR一定,所以称为定值积分,但积分方向相反,直到积分输出达到起始电平为止,从而将UX转换成时间间隔进行测量。

只要用计数器累计时间间隔内的脉冲数,即为UX之值。

其原理方框图如图1.1.1所示。

图1.1.1 3位半电压表原理图方案二:采用单片机为控制核心。

目前单片机技术比较成熟,功能也比较强大,配合一定的外围电路可实现数字电压表,原理图如图1.1.2所示。

输入信号经AD转换器转换后送到单片机进行数据处理,系统根据不同电压信号计算出不同的数值,并将其显示出来。

采用这种方案优点是呆以依赖地成熟的单片机技术、运算功能较强、软件编程灵活、自由度大、设计成本也较低,能较准确地测量输入电压。

毕业论文--数字电路课程设计报告--基于1602液晶屏的数字万年历Verilog版基于1602液晶屏的数字万年历(Verilog版)课程名称:数字电路课程设计专业:集成电路设计与集成系统基于1602液晶屏的数字万年历(Verilog版)一.设计要求1.基本功能设计一个数字钟,能够显示当前时间,分别用6个数码管显示小时、分钟、秒钟的时间,秒针的计数频率为1Hz,可由系统脉冲分频得到。

在整点进行提示,可通过LED闪烁实现,闪烁频率及花型可自己设计。

能够调整小时和分钟的时间,调整的形式为通过按键进行累加。

具有闹钟功能,闹钟时间可以任意设定(设定的形式同样为通过按键累加),并且在设定的时间能够进行提示,提示同样可以由LED闪烁实现。

2.扩展功能设计模式选择计数器,通过计数器来控制各个功能之间转换。

调整当前时间以及闹钟时间,在按键累加的功能不变的基础上,增加一个功能,即当按住累加键超过3秒,时间能够以4Hz的频率累加。

用LCD液晶屏来显示当前时间及功能模式。

二.设计分析及系统方案设计1.要求分析:基于FPGA实际并发处理的特点,对于实现数字万历年系统,相比于任何嵌入式处理器而言,其特点和优势将得以更加全面体现。

数字万年历中所有模块都将基于基准时钟源进行处理,结合FPGA本身的特点,在时钟源下可进行精确计数,可轻易而产生十分精确的万年历时间。

基础部分:万年历可包括以下时间处理模块:基于秒时钟计数器进行判断处理。

①秒,分,时。

②星期,上/下午。

③日,月,年。

④闹钟功能部分:①时间设定:使用四个按键进行控制,分别是:设置复位按键,设置移位键,功能“加”键,功能“减”键。

②整点报时部分:使用7个绿色LED作为提示灯。

③闹钟提示部分:使用16个红色LED作为闹钟报时提示。

显示部分:使用LCD1602液晶显示屏作为万年历的主显示屏,闹钟显示部分使用6个7段数码管。

2.方案设计基于FPGA的特点以及本万年历系统自身功能特点的实现方式。

第1章绪论1.1 系统背景随着科技的不断发展,电子技术获得了飞速的发展,有力的推动了生产力的发展和社会信息化程度的提高,电子行业也经历着日新月异的变化。

90年代后期,出现了以高级语言描述、系统级仿真和综合技术为特征的第三代EDA工具,极大地提高了系统设计的效率,使广大的电子设计师开始实现“概念驱动工程”的梦想。

设计师们摆脱了大量的具体设计工作,而把精力集中于创造性的方案与概念构思上,从而极大地提高了设计效率,缩短了产品的研制周期。

现场可编程逻辑门阵列FPGA,与PAL、GAL器件相比,他的优点是可以实时地对外加或内置得RAM或EPROM编程,实施地改变迄今功能,实现现场可编程(基于EPROM型)或在线重配置(基于RAM型)。

是科学试验、演技研制、小批量产品生产的最佳选择其间。

自上世纪70年代单片机问世以来,它以其体积小、控制功能齐全、价格低廉等特点赢得了广泛的好评与应用。

由单片机构成的应用系统有有体积小、功耗低控制功能强的特点,它用利于产品的小型化、多功能化和智能化,还有助与提高仪表的精度和准确度,简化结构、减小体积与重量,便于携带与使用,降低成本,增强抗干扰能力,便于增加显示、报警和诊断功能。

因而许多现代仪器仪表都用到了单片机。

1.2 选题目的及其意义信号发生器它最原始的功能是能够产生多种波形,比如说它可以产生方波、三角波、正弦波、锯齿波等等。

但随着科技的发展,它的功能也得到了增强,成为最普通、最基本的,也是应用最广泛的电子仪器之一,几乎所有的电参量的测量都需要用到多功能信号发生器。

不论是在生产还是在科研与教学上,多功能信号源发生器都是电子工程师信号仿真实验的最佳工具。

它除此之外还有许多的用途,它已经被广泛地应用于工业、教学、医学,科学研究等领域。

目前大部分信号发生器的设计是以微控制器为核心进行的,它与纯硬件设计的信号发生器相比,具有高精度、高可靠性、操作方便、价格便宜、智能化等特点,是智能化仪器的一个发展方向,具有一定的实用价值。

– 42 – 2012年第11卷第3期引言信息化社会的到来,促进了现代信息显示技术的发展,信息传播具有越来越重要的地位,同时受众对视觉媒体的要求也愈来愈高,要求传播媒体反映迅速、现实(实时性)、醒目(色彩丰富、栩栩如生)。

而随着微电子技术、自动化技术、计算机技术的迅速发展,随着LED材料技术和工艺水平提高,LED显示屏以突出的优势成为平板显示的主流产品之一。

而为了满足日益复杂的需求,LED 显示屏控制系统要具有足够的灵活性和可靠性[1]。

本文提出一种嵌入式LED显示屏控制系统的设计方案。

该方案的主控单元采用ARM9芯片,扫描控制单元采用FPGA芯片,以达到简化电路结构,提高整个控制系统的灵活性和可靠性的目的[2]。

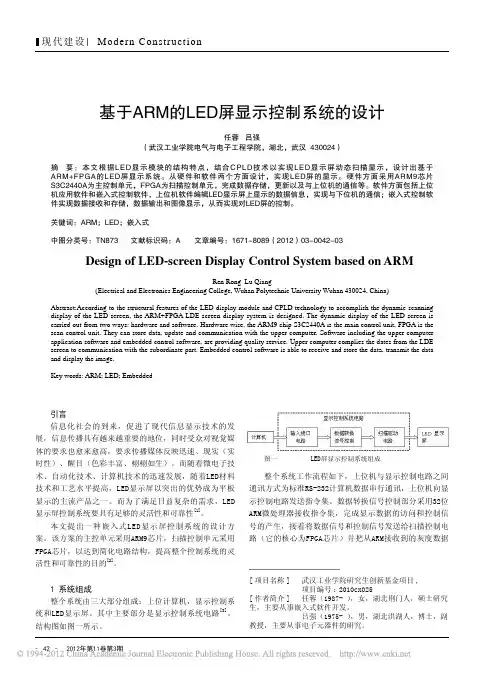

1 系统组成整个系统由三大部分组成:上位计算机,显示控制系统和LED显示屏。

其中主要部分是显示控制系统电路[3]。

结构图如图一所示。

图一 LED屏显示控制系统组成整个系统工作流程如下,上位机与显示控制电路之间通讯方式为标准RS-232计算机数据串行通讯,上位机向显示控制电路发送指令集。

数据转换信号控制部分采用32位ARM微处理器接收指令集,完成显示数据的访问和控制信号的产生,接着将数据信号和控制信号发送给扫描控制电路(它的核心为FPGA芯片)并把从ARM接收到的灰度数据基于ARM的LED屏显示控制系统的设计任蓉 吕强(武汉工业学院电气与电子工程学院,湖北,武汉 430024)摘 要:本文根据LED显示模块的结构特点,结合CPLD技术以实现LED显示屏动态扫描显示,设计出基于ARM+FPGA的LED屏显示系统。

从硬件和软件两个方面设计,实现LED屏的显示。

硬件方面采用ARM9芯片S3C2440A为主控制单元,FPGA为扫描控制单元,完成数据存储,更新以及与上位机的通信等。

软件方面包括上位机应用软件和嵌入式控制软件,上位机软件编辑LED显示屏上显示的数据信息,实现与下位机的通信;嵌入式控制软件实现数据接收和存储,数据输出和图像显示,从而实现对LED屏的控制。

基于FPGA车牌识别系统的设计与实现摘要:本文对传统的以通用数字信号处理器(dsp)为核心的车牌识别系统进行了改进,介绍了一种新的基于fpga车牌识别系统。

该系统主要通过摄像头采集汽车车牌图像,经过fpga核心处理器对图像进行处理,识别出车牌号,并通过 lcd 显示。

经过调试运行,该系统实现了车牌识别的功能,可运用于工程实践。

关键词:fpga;车牌识别;图像预处理;模板匹配【abstract】based on the traditional dsp, measurement was improved. the article mainly studies the design and realization of vlpr based on fpga. the system acquisitions the auto plate image through ccd and processes it in the fpga chip, then recognizes the plate and displays on the lcd. it realizes the function of vlpr after being debugged, and this can be used in the engineering projects.【key words】fpga; vlpr; image processing; module match 0 引言智能交通系统已成为当前交通管理发展的重要方向,而车辆牌照识别是计算机视觉与模式识别在智能交通领域应用的重要研究课题之一,有着广泛的实际应用前景[1]。

传统的车辆牌照识别大多以pc平台上的纯软件算法或dsp处理器为核心来实现。

由pc机构建的系统非小型化,在系统实时性的方面存在不足,主要用于前期算法的研究;而以通用的数字信号处理器(dsp)为核心的车牌识别系统外围电路设计复杂,开发调试困难,系统的可扩展性和升级性较差。

大连理工大学硕士学位论文LED显示屏接口电路设计姓名:刘庆申请学位级别:硕士专业:电子与通信工程指导教师:马灵芝20061210IED显示屏接口电路设计图5.3DVI接口Fig.5。

3InterfaceofDVI这样一来,Dv工接口就可以被分为只包含24针数字接口的Dv工一D,以及上面的数字、模拟兼顾的Dv工一工。

至于只有模拟接口的DV工一A,至今官方还没有发布此标准。

而现在显卡使用广泛的还是DVI一接口。

5,3.2叫I数字接口的应用随着计算机技术的飞速发展,一些与之相关的产业取得了长足的进步,显示器行业就是其中之一。

目前,显示器业正在由传统CRT一统天下的局面转变为ClOT,LCD等显示器百家争鸣的“春秋时代”,新兴的平面显示器、液晶显示器来势汹汹,并向传统CRT显示器的霸主地位发起挑战。

在这些形形色色的显示器中,液晶显示器被公认为今后显示器发展的主流,市场前景非常看好。

数字接口的LCD将是未来显示器接入的新标准。

众所周知,CRT显示器和LCD显示器之『自j的重要区别是前者需要用模拟信号来产生图像,而后者要求的是数字信号。

然而,目前市场上的LCD多为模拟接口,这就需要一个由模拟信号向数字信号的转换过程。

模拟接口的LCD最大的弱点是在显示的时候会出现像素闪烁的现象,这种现象出现的原因是时钟频率与输入的模拟信号不能100%同步,造成少数像素点的闪烁。

这在显示字符和线条的时候比较明显。

液晶显示器可以通过两种接口与显卡相连,一种就是传统显示器所采用的D型模拟接口,另一种就是新型的数字接口。

从理论上来说,要想发挥液晶显示器的真正性能,我们应当优先选择采用数字接1:3的液晶显示器。

采用数字接口(如目前的DVI接1:3是主流1可以有效地减少信号的损耗和干扰,是最适合液晶显示器的。

不过目前提供DVI接口的显卡和视频输出设备并不多见,所以大多数液晶显示器仍然使用模拟信号接口。

但随着DVI接口的显卡和视频输出设备越来越多,液晶显示器采用数字接口也将成为必然。

基于数字信号处理的 FPGA实现摘要:高速通信接口设计FPGA可用于高速信号处理。

一般来说,在AD采样率较高并且数据速率也较高的情况下,就需要对数据、处理信号、发送信号、存储数据进行处理,例如处理数据、过滤数据、减少数据速率等。

数字信号处理包含图像处理、雷达信号处理、医疗信号处理等,其优点在于良好的实时性能。

通过面积换高速,可以获得比CPU更快、更大的并行度。

关键词:数字信号;数字信号处理;FPGA实现;前言:通过使用FPGA设计ASIC电路,可以在不进行芯片制造的情况下获得适当的芯片。

FPGA可以用作其他全色或半定制ASIC电路的中间采样芯片。

FPGA 有很多触发器和输入输出销,其中FPGA是具有最短设计周期、最低开发成本以及ASIC电路最低风险的设备之一,并且FPGA采用低功耗、高速chmos技术,与cmos和ttl电平兼容。

1.FPGA应用的三个主要方向1.1第一个方向第一个方向被用于以往通信装置的高速接口电路的设计。

设计者需要理解高速接口电路设计和高速数字电路板水平设计,在解决高速收发机过程中的信号完整性问题。

FPGA最初在通信领域被广泛使用,而且距离很远。

另一方面,通信领域需要高速的通信协议处理方法,但是通信协议总是被变更,不适合制作特殊芯片,因此能够灵活变更功能的FPGA是第一选择。

迄今为止,应用FPGA的一半以上也存在于通信行业。

1.2第二个方向第二个方向也可以被称为数字信号处理方向或数学计算方向,这是因为其自身大大超出了信号处理的范围。

例如,最早在2006年,报道美国使用FPGA分析财务数据,并且在此基础之上,FPGA设计者需要具备一个恒定的数学基础,并且可以理解和改进相对复杂的数学算法,并使用FPGA内部的各种资源将其转化为实际的运算电路。

然而,最近在欧洲和美国等地区,人们发现许多电子和计算机系统已经进入金融业,以更好地发展金融信号处理。

随着传输数量的增加,FPGA其他领域的数学计算功能将得到更好地展示。

基于FPGA 的CameraLink 接口设计摘要院阐述一种基于FPGA 的Camera Link 接口设计,该接口设计用于替换原来发送端的并转串驱动器芯片SN75LVDS83B。

系统将原来芯片实现的功能集成到FPGA 中,既降低了功耗,也节省了产品的成本。

本设计利于产品的集成化,小型化。

通过该设计实现了芯片的功能,同时将数字图像数据成功的传输到液晶屏上进行显示。

Abstract: This article elaborates a kind of Camera Link interface design based on FPGA. The interface is designed to replace theoriginal sender of the parallel and serial driver chip SN75LVDS83B. The system will achieve the original chip functionality intothe FPGA,which reduces power consumption, but also saves the cost of the product. This design is conducive to integration, small productsminiaturized. The function of the chip is designed and implemented by the design, while the successful transmission of digital image data tobe displayed on the LCD screen.关键词院Camera Link;FPGA;图像传输Key words: Camera Link;FPGA;image transmission中图分类号院TN946 文献标识码院A 文章编号院1006-4311(2014)16-0218-02 0引言Camera Link 是一种基于视频应用发展而来的通信接口,是在Channel Link 技术基础上发展出来的[1]。

基于FPGA车牌识别系统的设计与实现摘要:本文对传统的以通用数字信号处理器(dsp)为核心的车牌识别系统进行了改进,介绍了一种新的基于fpga车牌识别系统。

该系统主要通过摄像头采集汽车车牌图像,经过fpga核心处理器对图像进行处理,识别出车牌号,并通过 lcd 显示。

经过调试运行,该系统实现了车牌识别的功能,可运用于工程实践。

关键词:fpga;车牌识别;图像预处理;模板匹配【abstract】based on the traditional dsp, measurement was improved. the article mainly studies the design and realization of vlpr based on fpga. the system acquisitions the auto plate image through ccd and processes it in the fpga chip, then recognizes the plate and displays on the lcd. it realizes the function of vlpr after being debugged, and this can be used in the engineering projects.【key words】fpga; vlpr; image processing; module match 0 引言智能交通系统已成为当前交通管理发展的重要方向,而车辆牌照识别是计算机视觉与模式识别在智能交通领域应用的重要研究课题之一,有着广泛的实际应用前景[1]。

传统的车辆牌照识别大多以pc平台上的纯软件算法或dsp处理器为核心来实现。

由pc机构建的系统非小型化,在系统实时性的方面存在不足,主要用于前期算法的研究;而以通用的数字信号处理器(dsp)为核心的车牌识别系统外围电路设计复杂,开发调试困难,系统的可扩展性和升级性较差。

目录1. 设计概述 (1)2. 设计目标 (2)3. 设计思想 (3)4. 系统结构 (4)4.1系统硬件结构框图 (4)4.2系统软件结构框图 (5)5. 系统单元电路的设计 (5)5.1ADC采样模块设计 (5)5.1.1 WM7831芯片简介 (5)5.1.2 WM8731芯片控制 (6)5.1.3 ADC单元硬件电路 (7)5.2FFT模块的设计 (9)5.2.1 FFT算法 (9)5.2.2 FFT算法的FPGA实现整体结构 (10)5.3中断的实现 (11)5.4液晶显示模块的设计 (11)5.4.1 方案论证 (12)5.4.2 方案设计过程 (12)5.5VGA显示模块的设计 (18)5.5.1 VGA显示原理及时序 (18)5.5.2 方案论证 (19)5.5.3 方案设计过程 (20)5.6音频前置放大器的设计 (22)5.7音频输出 (22)6. 系统实验结果分析 (23)6.1分辨率实验 (23)6.2频率的测量范围实验 (24)6.3M ATLAB对正弦波进行频谱分析的仿真结果 (25)6.4音频信号的相关实验 (26)6.5系统运算速度测试 (26)6.6实验结果分析 (26)6.7系统资源使用情况 (26)7. 设计特点与不足 (27)7.1设计特点 (27)7.2设计不足 (27)8. 设计过程中出现的问题及解决 (28)9.总结 (28)参考文献 (29)数字频谱分析仪Digital Spectrum Analyzer(陕西科技大学王鹏,李明艳,刘波指导教师:马令坤)摘要:随着科学技术的发展,频谱分析作为近代的信号分析方法在各个学科研究中已经广泛应用,是从事各种电子产品研发、生产、检验的重要依据。

高分辨率、宽频带实时的数字频谱分析的方法和实现一直是该领域的研究热点,我们设计了一种基于NIOS II的嵌入式频谱分析仪。

充分利用NIOSII强的运算能力和FPGA易于系统集成的特点,实现了硬件开销小、实时性较强和分辨率高的语音频谱分析仪。

学号:********** 河南大学民生学院

毕 业 论 文 ( 2014 届)

年 级 2010级 专 业 班 级 电子信息科学与技术 学 生 姓 名 指导教师姓名 指导教师职称 讲师 论文完成时间 2014年5月10日 河南大学民生学院本科毕业论文

1 目 录 摘 要: ........................................................................................................................ 2 1 绪论 ............................................................................................................................ 3 1.1 选题背景 ........................................................................................................... 3 1.2 LCD发展 .......................................................................................................... 3 1.3 选题目的 ........................................................................................................... 4 2 关键技术 .................................................................................................................... 4 2.1 FPGA简介 .......................................................................................................... 4 2.2 LCD简介 ............................................................................................................ 5 3 系统分析 .................................................................................................................... 7 3.1 FPGA的设计方法 .............................................................................................. 7 3.2 Verilog HDL ..................................................................................................... 8 3.3 TC1602液晶模块工作方式 .............................................................................. 8 3.4 系统开发环境 ................................................................................................. 12 4 系统设计与验证 ...................................................................................................... 12 4.1 系统概述 ......................................................................................................... 12 4.2 功能结构设计 ................................................................................................. 12 4.3 设计流程图与状态的设计 ............................................................................. 12 4.4 系统实现 ......................................................................................................... 15 4.5 部分程序代码 ................................................................................................. 16 5 系统测试 .................................................................................................................. 20 5.1 仿真波形 ......................................................................................................... 20 5.2 对TC1602液晶显示器验证 ........................................................................... 20 6 结论 .......................................................................................................................... 20 参考文献 ...................................................................................................................... 21 河南大学民生学院本科毕业论文

2 基于FPGA的LCD驱动显示电路的设计与实现

(河南大学民生学院,河南 开封,475004) 摘 要: 本课题主要任务是设计基于FPGA的LCD驱动电路的设计和实现,兼顾好程序的易用性,以方便之后模块的移植和应用。控制器部分采用Verilog语言编写,主体程序采用了状态机作为主要控制方式。最后实现使用FPGA在LCD上显示任意的英文字符和阿拉伯数字,另外要能根据输入数据的变化同步变化LCD上显示的内容。同时要能将储存模块中的数据正常地显示在LCD上。 本文中对FPGA,LCD,Quartus II,硬件设计工具等进行了简单的介绍,对其功能进行了简单的描述,并了解了LCD液晶显示器的发展历史,日常应用以及相对比于其他种类显示器的优缺点,并对基于FPGA的LCD液晶显示器驱动电路未来的发展趋势进行了展望。

关键词: FPGA LCD Verilog 状态机

Design and Implementation of LCD Drive Display Circuit based on FPGA Abstract: In this project, the main object is to design a LCD controller based on FPGA, and at the same time emphasize on the convenience for the later application and migration.The program of the controller is written by Verilog language, and the main body of the program used state machine as the primary control method. displayed picture which was put earlier. In this project, FPGA, LCD, Quartus II, I hardware design tools simply introduces its functions were a simple description, and understanding the LCD monitor the development history, and relative everyday applications than in other types of monitor based on FPGA advantages and disadvantages, and the LCD monitor driver circuit future development trends are discussed. Key words:

FPGA, LCD, Verilog, State Machine