C a m e r a L i n k接口

1.CameraLink接口简介

1.1CameraLink标准概述

Camera Link 技术标准是基于 National Semiconductor 公司的 Channel Link 标准发展而来的,而 Channel Link 标准是一种多路并行 LVDS 传输接口标准。

低压差分信号( LVDS )是一种低摆幅的差分信号技术,电压摆幅在 350mV 左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在。 90 年代美国国家半导体公司( National Semiconductor )为了找到平板显示技术的解决方案,开发了基于 LVDS 物理层平台的 Channel Link 技术。此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用。

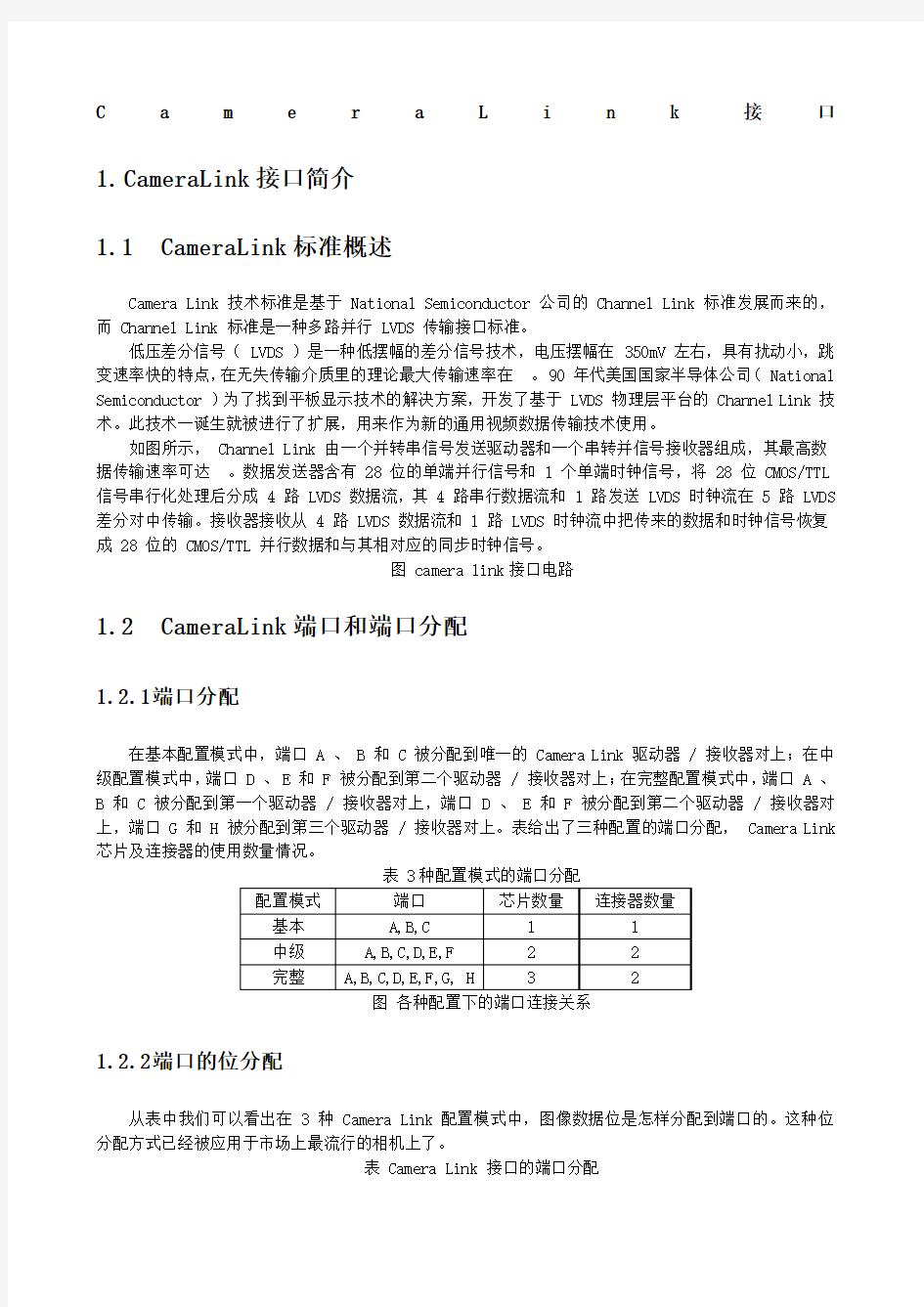

如图所示, Channel Link 由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达。数据发送器含有 28 位的单端并行信号和 1 个单端时钟信号,将 28 位 CMOS/TTL 信号串行化处理后分成 4 路 LVDS 数据流,其 4 路串行数据流和 1 路发送 LVDS 时钟流在 5 路 LVDS 差分对中传输。接收器接收从 4 路 LVDS 数据流和 1 路 LVDS 时钟流中把传来的数据和时钟信号恢复成 28 位的 CMOS/TTL 并行数据和与其相对应的同步时钟信号。

图 camera link接口电路

1.2CameraLink端口和端口分配

1.2.1端口分配

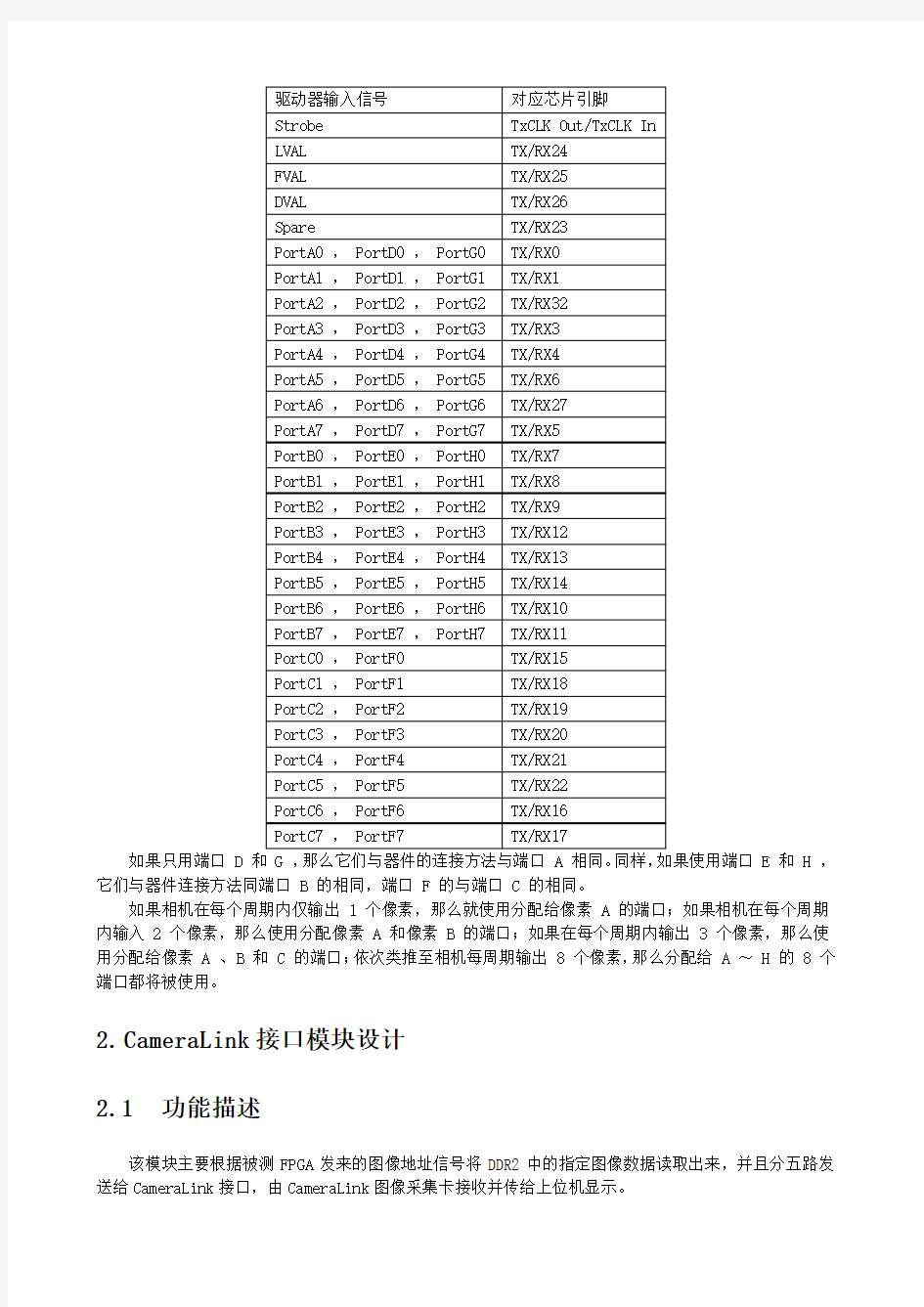

在基本配置模式中,端口 A 、 B 和 C 被分配到唯一的 Camera Link 驱动器 / 接收器对上;在中级配置模式中,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上;在完整配置模式中,端口 A 、B 和 C 被分配到第一个驱动器 / 接收器对上,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上,端口 G 和 H 被分配到第三个驱动器 / 接收器对上。表给出了三种配置的端口分配, Camera Link 芯片及连接器的使用数量情况。

表 3种配置模式的端口分配

图各种配置下的端口连接关系

1.2.2端口的位分配

从表中我们可以看出在 3 种 Camera Link 配置模式中,图像数据位是怎样分配到端口的。这种位分配方式已经被应用于市场上最流行的相机上了。

表 Camera Link 接口的端口分配

如果只用端口 D 和 G ,那么它们与器件的连接方法与端口 A 相同。同样,如果使用端口 E 和 H ,它们与器件连接方法同端口 B 的相同,端口 F 的与端口 C 的相同。

如果相机在每个周期内仅输出 1 个像素,那么就使用分配给像素 A 的端口;如果相机在每个周期内输入 2 个像素,那么使用分配像素 A 和像素 B 的端口;如果在每个周期内输出 3 个像素,那么使用分配给像素 A 、 B 和 C 的端口;依次类推至相机每周期输出 8 个像素,那么分配给 A ~ H 的 8 个端口都将被使用。

2.CameraLink接口模块设计

2.1功能描述

该模块主要根据被测FPGA发来的图像地址信号将DDR2中的指定图像数据读取出来,并且分五路发送给CameraLink接口,由CameraLink图像采集卡接收并传给上位机显示。

2.2接口描述

CameraLink图像采集端口模块的接口信号如图所示:

图 CameraLink图像采集端口示意图

表各端口的接口定义

CameraLink接口信号时序如图所示:

图 CameraLink图像采集电路的时序图

2.3功能实现

Cameralink图像采集接口电路主要包含两个子模块,如图所示,数据读取分发模块负责从DDR2中读取处理好的CMOS图像,并按指定的数据编排要求分发给5路CAMERALINK数据缓冲输出模块,数据缓冲输出模块完成5路CAMERALINK数据的缓冲,并按指定时序要求发送给DS90CR287。

图 CameraLink图像采集软件流程框图

2.3.1数据读取分发模块

数据读取分发模块负责在帧行同步信号的控制下,按照地址使能和地址信号从DDR2中读取处理好的CMOS图像数据,并按指定的数据编排要求发送给cameralink数据缓冲输出模块。

该模块也分为两个子模块:地址映射模块和读取DDR模块。地址映射模块的主要功能是根据被测

FPGA给的行地址转化成对应DDR的行起始地址,转化完成后把DDR地址发给DDR读取模块,DDR读取模块负责把该行的10240个像素(12bit)全部读取到五路缓冲模块中。

2.3.2数据缓冲输出模块

缓冲模块总共有五路,把一行图像数据平均分到五路缓冲后输出。每路CameraLink缓冲模块包括2个双口RAM,采用乒乓读写的工作模式,一个双口RAM读DDR数据的同时另一个双口RAM发送数据。双口RAM配置为两端口独立时钟模式,以隔离DDR时钟和CamerLink 数据域的时钟。另外,两端口可以配置为不同的数据位宽,以方便实现DDR2数据位宽64位到16位数据位宽的变换。由于CamerLink输出时12位的,因此在款冲模块处还要有一个16位位宽转换位12位位宽的子模块来完成位宽的转换。

2.4modelsim仿真结果

图 modelsim仿真结果

如图,被测FPGA每来一个行同步,CameraLink模块获取行地址后读取DDR2中的数据写入缓存模块,等到下一个行同步来的时候把所读的数据从缓存模块中输出。实际要求的是每个行同步来后要读取一行数据,大小为2048x12bit,为了缩小仿真时间,仿真时没一行的数据长度为:80x12bit。

图五路CameraLink仿真输出

如图,当下个行同步来的时候缓存数据输出,输出的数据时连续的。

J S-D K系列L E D全彩控制器 使用说明书(V1.2) J S-D K-T1a_1024(L E D全彩单通道同步控制器) J S-D K-T2a_1024(L E D全彩双通道同步控制器) J S-D K-T4a_1024(L E D全彩四通道同步控制器) J S-D K-T8a_1024(L E D全彩八通道同步控制器) J S-D K-T1b_512(L E D全彩单通道单机控制器) J S-D K-T1b_1024(L E D全彩双通道单机控制器) J S-D K-T2b_1024(L E D全彩四通道单机控制器) J S-D K-T4b_1024(L E D全彩四通道单机控制器) J S-D K-T8b_1024(L E D全彩八通道单机控制器)

一、概述 J S-D K系列L E D全彩控制器目前上市九款:包括J S-D K-T1a_1024、J S-D K-T2a_1024、J S-D K-T4a_1024、J S-D K-T8a_1024、J S-D K-T1b_512、J S-D K-T1b_1024、J S-D K-T2b_1024、J S-D K-T4b_1024、J S-D K-T8a_1024。L E D全彩同步控制器通过交流220V市电进行同步播放,可以多台联合使用。L E D全彩灯单机控制器D C+5~+24V控制,只能单机使用。 L E D全彩同步控制器主要适用于:L E D模组、全彩穿孔灯、外控护栏管、灯条、全彩点光源等。 二、技术参数 输入电压:同步控制器(交流220V,50H z市电) 单机控制器(直流+5V~直流+24V) 控制路数:J S-D K-T1a_1024(1路)、J S-D K-T2a_1024(2路)、J S-D K-T4a_1024(4路)、 J S-D K-T8a_1024(8路)、 J S-D K-T1b_512(1路)、J S-D K-T1b_1024(1路)、 J S-D K-T2b_1024(2路)、J S-D K-T4b_1024(4路)、J S-D K-T8b_1024(8路)同步模式:自动检测50H工频信号(同步控制器)。 驱动芯片:三线芯片,四线芯片。 三、产品特点 l智能化软件设计支持自动布线、手动布线,大大提高工作效率。 l便捷化软件设计10分钟学会软件设计、布线操作,简单实用。 l数据文件U盘导入,方便灵活,适应性强。 l软件24位伽马校正,展现绚丽画面。 l白光全亮测试,迅速排查接线及电源供电问题。 l经过严格电磁兼容性测试,防静电、抗干扰、防谐波,坚实可靠! 四、产品说明 (图一)

Camera Link接口数字相机图像显示装置(技术)摘要:由于目前基于CameraLink接口的各种相机都不能直接显示,因此本文基于Xilinx公司的Spartan3系列FPGA XC3S1000-6FG456I设计了一套实时显示系统,该系统可以在不通过系统机的情况下,完成对相机CameraLink信号的接收、缓存、读取并显示。系统采用两片SDRAM作为帧缓存,将输入的CameraLink信号转换成帧频为75Hz,分辨率为1,024×768的XGA格式信号,并采用ADV7123JST芯片实现数模转换,将芯片输出的信号送到VGA接口,通过VGA显示器显示出来。设计的系统可以应用于各种基于CameraLink接口的相机输出信号的实时显示。 关键词:CameraLink; FPGA; SDRAM控制器;实时显示 Research on the Real-time Display Technology Based on CameraLink Abstract: All cameras based on the CameraLink interface cannot be displayed directly at present. Therefore, we designed a real-time display system based on the Xilinx Spartan3 FPGA XC3S1000-6FG456I.Our system could receive, store, read and display the CameraLink signal without the system computer. Two SDRAMs were used as frame storage. Input CameraLink signal was converted to XGA signal with 1024×768 pixles/frame at 75 frame/s. The ADV7123JST was used as D/A convertor. Its output signal was transmitted to the VGA interface and displayed on the screen of the VGA monitor. Our system could display the output signal of all cameras based on the CameraLink interface. Keywords: CameraLink; FPGA; SDRAM controller; real-time display

一、填空题 1. 基本RS触发器,当R、S都接高电平时,该触发器具有____ ___功能。2.D 触发器的特性方程为___ ;J-K 触发器的特性方程为______。 3.T触发器的特性方程为。 4.仅具有“置0”、“置1”功能的触发器叫。 5.时钟有效边沿到来时,输出状态和输入信号相同的触发器叫____ _____。 6. 若D触发器的D端连在Q端上,经100 个脉冲作用后,其次态为0,则现态应为。 7.JK触发器J与K相接作为一个输入时相当于触发器。 8. 触发器有个稳定状态,它可以记录位二进制码,存储8 位二进制信息需要个触发器。 9.时序电路的次态输出不仅与即时输入有关,而且还与有关。 10. 时序逻辑电路一般由和两部分组成的。 11. 计数器按内部各触发器的动作步调,可分为___ ___计数器和____ __计数器。 12. 按进位体制的不同,计数器可分为计数器和计数器两类;按计数过程中数字增减趋势的不同,计数器可分为计数器、计数器和计数器。13.要构成五进制计数器,至少需要级触发器。 14.设集成十进制(默认为8421码)加法计数器的初态为Q4Q3Q2Q1=1001,则经过5个CP脉冲以后计数器的状态为。 15.将某时钟频率为32MHz的CP变为4MHz的CP,需要个二进制计数器。 16. 在各种寄存器中,存放N位二进制数码需要个触发器。 17. 有一个移位寄存器,高位在左,低位在右,欲将存放在该移位寄存器中的二进制数乘上十进制数4,则需将该移位寄存器中的数移位,需要个移位脉冲。 18.某单稳态触发器在无外触发信号时输出为0态,在外加触发信号时,输出跳变为1态,因此其稳态为态,暂稳态为态。 19.单稳态触发器有___ _个稳定状态,多谐振荡器有_ ___个稳定状态。20.单稳态触发器在外加触发信号作用下能够由状态翻转到状态。21.集成单稳态触发器的暂稳维持时间取决于。 22. 多谐振荡器的振荡周期为T=tw1+tw2,其中tw1为正脉冲宽度,tw2为负脉冲宽度,则占空比应为_______。 23.施密特触发器有____个阈值电压,分别称作___ _____ 和___ _____ 。24.触发器能将缓慢变化的非矩形脉冲变换成边沿陡峭的矩形脉冲。25.施密特触发器常用于波形的与。 二、选择题 1. R-S型触发器不具有( )功能。 A. 保持 B. 翻转 C. 置1 D. 置0 2. 触发器的空翻现象是指() A.一个时钟脉冲期间,触发器没有翻转 B.一个时钟脉冲期间,触发器只翻转一次 C.一个时钟脉冲期间,触发器发生多次翻转 D.每来2个时钟脉冲,触发器才翻转一次 3. 欲得到D触发器的功能,以下诸图中唯有图(A)是正确的。

电源时序器能够按照由前级设备到后级设备逐个顺序启动电源,关闭供电电源时则由后级到前级地顺序关闭各类用电设备,这样就能有效地统一管理和控制各类用电设备,避免了人为地失误操作,同时又可减低用电设备在开关瞬间对供电电网地冲击,也避免了感生电流对设备地冲击,确保了整个用电系统地稳定. 产品使用说明 .备用电源开关:可以用来防止控制器因某些原因而失去控制,关掉此开关,可同时连接所有插座电源; .输出插座指示灯:当每个指示灯亮相对应插座将连通电源; .电源指示灯:打开此电源控制器后,指示灯就会显示已经启动地控制信号; .电源开关:打开此电源开关时,就会自动按照:顺序把电源输入插座中.关掉此电源,就会自动按照:此顺序把电源切断;个人收集整理勿做商业用途 .电源输入电缆; .电源输出插座. 功能与使用 .此电源开关打开时,控制器可以按顺序连接到每一个插座.相反地,关掉此电源开关,控制器可以反顺序切断每一个插座上地电源.个人收集整理勿做商业用途 .此装置可以用作会议中心,电脑机房,电视播放系统与其他电源系统,都需要按照顺序地打开设备. 技术规格 . 每一路输出电流; . 控制电源:通道; 串口控制 (脚接收,脚信号地) (脚,脚) 波特率数据位停止位校验位 每接收正确地串口命令,电源指示灯闪烁三次,频率为秒次. 是修改()地址码.是固定公共地址码,例如是指令是个人收集整理勿做商业用途 各路开关例如:第一路开: 关: 第二路开: 关: 第三路开: 关: 第十路开: 关: 第十一路开: 关: 第十二路开: 关: 全开: 全关: 各路上锁与解锁指令:(是上锁对应路开关,不受开关锁控制) 如:第一路上锁: 解锁:

第12章时序逻辑电路 自测题 一、填空题 1.时序逻辑电路按状态转换情况可分为时序电路和时序电路两大类。 2.按计数进制的不同,可将计数器分为、和N进制计数器等类型。 3.用来累计和寄存输入脉冲个数的电路称为。 4.时序逻辑电路在结构方面的特点是:由具有控制作用的电路和具记忆作用电路组成。、 5.、寄存器的作用是用于、、数码指令等信息。 6.按计数过程中数值的增减来分,可将计数器分为为、和三种。 二、选择题 1.如题图12.1所示电路为某寄存器的一位,该寄存器为 。 A、单拍接收数码寄存器; B、双拍接收数码寄存器; C、单向移位寄存器; D、双向移位寄存器。 2.下列电路不属于时序逻辑电路的是。 A、数码寄存器; B、编码器; C、触发器; D、可逆计数器。 3.下列逻辑电路不具有记忆功能的是。 A、译码器; B、RS触发器; C、寄存器; D、计数器。 4.时序逻辑电路特点中,下列叙述正确的是。 A、电路任一时刻的输出只与当时输入信号有关; B、电路任一时刻的输出只与电路原来状态有关; C、电路任一时刻的输出与输入信号和电路原来状态均有关; D、电路任一时刻的输出与输入信号和电路原来状态均无关。 5.具有记忆功能的逻辑电路是。 A、加法器; B、显示器; C、译码器; D、计数器。 6.数码寄存器采用的输入输出方式为。 A、并行输入、并行输出; B、串行输入、串行输出; C、并行输入、串行输出; D、并行输出、串行输入。 三、判断下面说法是否正确,用“√"或“×"表示在括号 1.寄存器具有存储数码和信号的功能。( ) 2.构成计数电路的器件必须有记忆能力。( ) 3.移位寄存器只能串行输出。( ) 4.移位寄存器就是数码寄存器,它们没有区别。( ) 5.同步时序电路的工作速度高于异步时序电路。( ) 6.移位寄存器有接收、暂存、清除和数码移位等作用。() 思考与练习题 12.1.1 时序逻辑电路的特点是什么? 12.1.2 时序逻辑电路与组合电路有何区别? 12.3.1 在图12.1电路作用下,数码寄存器的原始状态Q3Q2Q1Q0=1001,而输入数码

第七章 几种常用的时序逻辑电路 一、填空题 1.(9-1易)与组合逻辑电路不同,时序逻辑电路的特点是:任何时刻的输出信号不仅与____________有关,还与____________有关,是______(a.有记忆性b.无记忆性)逻辑电路。 2.(9-1易)触发器是数字电路中______(a.有记忆b.非记忆)的基本逻辑单元。 3.(9-1易)在外加输入信号作用下,触发器可从一种稳定状态转换为另一种稳定状态,信号终止,稳态_________(a.不能保持下去 b. 仍能保持下去)。 4.(9-1中)JK 触发器是________(a.CP 为1有效b.CP 边沿有效)。 5.(9-1易)1n n n Q JQ KQ +=+是_______触发器的特性方程。 6.(9-1中)1n n Q S RQ +=+是________触发器的特性方程,其约束条件为___________。 7.(9-1易)1n n n Q TQ TQ +=+是_____触发器的特征方程。 8. (9-1中)在T 触发器中,若使T=____,则每输入一个CP ,触发器状态就翻转一次,这种具有翻转功能的触发器称为'T 触发器,它的特征方程是________________。 9.(9-1难)我们可以用JK 触发器转换成其他逻辑功能触发器,令 __________________,即转换成T 触发器;令_______________, 即转换为'T 触发器;令________________,即转换成D 触发器。 10.(9-1难)我们可以用D 触发器转换成其他逻辑功能触发器,令 __________________,即转换成T 触发器;令_______________, 即转换为'T 触发器。

jgd280同步控制器使用说明 使用说明 2009-08-21 15:39 阅读58 评论0 字号:大中小 JGD系列同步控制器是本公司在原生产的单一型号基础上推出的成系列同步控制装置,内部采用计算机为核心的全数字化设计,每台控制器能同时控制四台或八台电机的运转,使用非常灵活、简便。JG D系列同步控制器拥有完善的功能,在技术上处于国内领先水平,在性能上可与国外同类产品相媲美。广泛适用于由多台调速系统组成的各种机械设备上,如电力、钢铁、造纸、纺织、印染、电缆光纤、塑料等行业。可对线速度、位移、张力、距离等进行控制,是机器设备的最佳选择。 一、型号说明 1.主要特点 A、数字化 JGD系列控制器采用单片计算机控制,可通过对控制器进行多种参数设置,设置参数时通过数码显示。本控制器内有记忆体,断电后能自动保留用户设置的参数。 B、功能强大 1)JGD系列控制器每台有三种给定输入方式(内部给定、外部电压给定、外部电流给定)。 2)JGD-280控制器每台可控制八个独立单元有八路输出(V01~V08)。 3)每个控制单元的输出可作为另外控制单元的输入(单元串、并联使用)。可将一台控制器作为 二台或三台独立控制器使用。 4)具有缓起动、停车功能,时间可设置(0~100秒)。 5)具有故障报警及起动信号继电器输出,其驱动能力达5A。 C、高精度 本系列控制器输入、输出模拟信号采用高分辨率的A/D、D/A转换器,其分辨率可达0.1%。 D、通用性 外部给定输入采用标准的0~10V或4~20mA,控制输出0~10V,可与各种调速控制器相匹配。 E、使用简便 1)用户修改控制参数可在控制器起动状态下进行,便于用户调试设备。

C a m e r a L i n k接口时序 控制 This manuscript was revised by the office on December 10, 2020.

CameraLink接口 1.CameraLink接口简介 1.1CameraLink标准概述 Camera Link 技术标准是基于 National Semiconductor 公司的 Channel Link 标准发展而来的,而 Channel Link 标准是一种多路并行 LVDS 传输接口标准。 低压差分信号( LVDS )是一种低摆幅的差分信号技术,电压摆幅在 350mV 左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在 1.923Gbps 。 90 年代美国国家半导体公司( National Semiconductor )为了找到平板显示技术的解决方案,开发了基于 LVDS 物理层平台的 Channel Link 技术。此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用。 如图1.1所示, Channel Link 由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达 2.38G 。数据发送器含有 28 位的单端并行信号和 1 个单端时钟信号,将 28 位 CMOS/TTL 信号串行化处理后分成 4 路 LVDS 数据流,其 4 路串行数据流和 1 路发送 LVDS 时钟流在 5 路LVDS 差分对中传输。接收器接收从 4 路 LVDS 数据流和 1 路 LVDS 时钟流中把传来的数据和时钟信号恢复成 28 位的 CMOS/TTL 并行数据和与其相对应的同步时钟信号。 图1.1 camera link接口电路 1.2CameraLink端口和端口分配 1.2.1端口分配 在基本配置模式中,端口 A 、 B 和 C 被分配到唯一的 Camera Link 驱动器 / 接收器对上;在中级配置模式中,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上;在完整配置模式中,端口 A 、 B 和 C 被分配到第一个驱动器 / 接收器对上,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上,端口 G 和 H 被分配到第三个驱动器 / 接收器对上。表1.1给出了三种配置的端口分配, Camera Link 芯片及连接器的使用数量情况。

第5章时序逻辑电路 5.1 时序逻辑电路的基本概念 1.时序逻辑电路的结构及特点 时序逻辑电路在任何时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关,触发器就是最简单的时序逻辑电路,时序逻辑电路中必须含有存储电路。时序电路的基本结构如图 5.1 所示,它由组合电路和存储电路两部分组成。 图5.1 时序逻辑电路框图 时序逻辑电路具有以下特点: (1)时序逻辑电路通常包含组合电路和存储电路两个组成部分,而存储电路要记忆给定时刻前的输入输出信号,是必不可少的。 (2)时序逻辑电路中存在反馈,存储电路的输出状态必须反馈到组合电路的输入端,与输入信号一起,共同决定组合逻辑电路的输出。 2.时序逻辑电路的分类 (1)按时钟输入方式 时序电路按照时钟输入方式分为同步时序电路和异步时序电路两大类。同步时序电路中,各触发器受同一时钟控制,其状态转换与所加的时钟脉冲信号都是同步的;异步时序电路中,各触发器的时钟不同,电路状态的转换有先有后。同步时序电路较复杂,其速度高于异步时序电路。 (2)按输出信号的特点 根据输出信号的特点可将时序电路分为米里(Mealy)型和摩尔(Moore)型两类。米里型电路的外部输出Z既与触发器的状态Q n有关,又与外部输入X有

关。而摩尔型电路的外部输出Z仅与触发器的状态Q n有关,而与外部输入X无关。 (3)按逻辑功能 时序逻辑电路按逻辑功能可划分为寄存器、锁存器、移位寄存器、计数器和节拍发生器等。 3.时序逻辑电路的逻辑功能描述方法 描述一个时序电路的逻辑功能可以采用逻辑方程组(驱动方程、输出方程、状态方程)、状态表、状态图、时序图等方法。这些方法可以相互转换,而且都是分析和设计时序电路的基本工具。 5.2 时序逻辑电路的分析方法和设计方法 1.时序逻辑电路的分析步骤 (1)首先确定是同步还是异步。若是异步,须写出各触发器的时钟方程。(2)写驱动方程。 (3)写状态方程(或次态方程)。 (4)写输出方程。若电路由外部输出,要写出这些输出的逻辑表达式,即输出方程。 (5)列状态表 (6)画状态图和时序图。 (7)检查电路能否自启动并说明其逻辑功能。 5.2.1 同步时序逻辑电路的设计方法 1.同步时序逻辑电路的设计步骤 设计同步时序电路的一般过程如图5.10所示。 图5.10 同步时序电路的设计过程

盤面型 RSC-406 使用說明書 浙江麗水謙勝機電有限公司浙江麗水水閣工業區綠穀大道306-2號 TEL: FAX:068

目錄1.前言 ~1~ 1.前言... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... .... ... ... . (2) 2.產品特點介紹... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... .... ... .... (3) 3.產品檢 查 … … ..3 3-1 數位式同步控制器外 觀... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ....... (3) 3-2 控制器外觀尺 (4) 3-3 控制器面板顯示及操作說 明... ... ... ... ... ... ... ... ... ... .... ... ... ... ..... ... (4) 3-3-1 LED 燈號說 明… … … … … … … … … … … … … … … … … … … … … … .5 3-3-2 按鍵操作說 ...5首先感謝您選用由本公司所開發的 RSC-406 數位式比例同步控制器。 為了充分地發揮RSC-406 的功能,及確保使用者的安全,請詳閱本操作手 冊。當您使用中出現任何疑點而本手冊無法提供您解決方案時,請您與本公司 連絡,我們將竭誠為您服務。並請您繼續采用本公司的產品。 4.安裝… … … … … … … … … … … … … … … … … … … … … … … … … … .… … .....6!注意 4-1 使用環 境… … … … … … … … … … … … … … … … … … … … … … .... ... .. (6) 4-2 控制器後端護弓,端子安裝方式及盤面安裝尺 寸... ... ... ... ... ... ... ... .. (6) 5.配線… … … … … … … … … … … … … … … … … … … … … … … … … … … ..… ...75-1 端子功能說明… … … … … … … … … … … … … … … … … … … … … … ..... .7 5-2 標准配線圖… … … … … … … … … … … … … … … … … … … … … … … … ..8 5-3 控制回路配線圖… … … … … … … … … … … … … … … … … … … … … .

CameraLink 图像采集接口电路 1.Camera Link标准概述 Camera Link 技术标准是基于 National Semiconductor 公司的 Channel Link 标准发展而来的,而 Channel Link 标准是一种多路并行 LVDS 传输接口标准。 低压差分信号( LVDS )是一种低摆幅的差分信号技术,电压摆幅在 350mV 左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在 1.923Gbps 。 90 年代美国国家半导体公司( National Semiconductor )为了找到平板显示技术的解决方案,开发了基于 LVDS 物理层平台的 Channel Link 技术。此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用。 如图1 所示, Channel Link 由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达 2.38G 。数据发送器含有 28 位的单端并行信号和 1 个单端时钟信号,将 28 位 CMOS/TTL 信号串行化处理后分成 4 路 LVDS 数据流,其 4 路串行数据流和 1 路发送 LVDS 时钟流在 5 路 LVDS 差分对中传输。接收器接收从 4 路 LVDS 数据流和 1 路 LVDS 时钟流中把传来的数据和时钟信号恢复成 28 位的 CMOS/TTL 并行数据和与其相对应的同步时钟信号。 图1 camera link接口电路 2.Channel Link标准的端口和端口分配 2.1 .端口定义 一个端口定义为一个 8 位的字,在这个 8 位的字中,最低的 1 位( LSB )是 bit0 ,最高的 1 位( MSB )是 bit7 。 Camera Link 标准使用 8 个端口,即端口 A 至端口 H 。

《电子技术基础》复习题 时序逻辑电路 一、填空题: 1.具有“置0”、“置1”、“保持”和“计数功能”的触发器是() 2.触发器有门电路构成,但它不同门电路功能,主要特点是:() 型触发器的直接置0端Rd、置1端Sd的正确用法是() 4.按触发方式双稳态触发器分为:() 5.时序电路可以由()组成 6.时序电路输出状态的改变() 7.通常寄存器应具有()功能 8.通常计数器应具有()功能 9. M进制计数器的状态转换的特点是设初态后,每来()个CP时,计数器又重回初态。 10.欲构成能记最大十进制数为999的计数器,至少需要()个双稳触发器。 11. 同步时序逻辑电路中所有触发器的时钟端应()。 二、选择题: 1.计数器在电路组成上的特点是() a)有CP输入端,无数码输入端 b) 有CP输入端和数码输入端 c) 无CP输入端,有数码输 入端 2.按各触发器的状态转换与CP的关系分类,计数器可分为()计数器。 a)加法、减法和加减可逆 b)同步和异步 c)二、十和M进制 3. 按计数器的状态变换的规律分类,计数器可分为()计数器。 a)加法、减法和加减可逆 b)同步和异步 c)二、十和M进制 4 按计数器的进位制分类,计数器可分为()计数器。 a)加法、减法和加减可逆 b)同步和异步 c)二、十和M进制 5. n位二进制加法计数器有()个状态,最大计数值是()。 a)2n-1 b)2n c)2n-1 6.分析时序逻辑电路的状态表,可知它是一只()。 (a) 二进制计数器(b)六进制计数(c) 五进制计数器 7. 分析如图所示计数器的波形图,可知它是一只()。 (a) 六进制计数器(b) 七进制计数器(c) 八进制计数器

JGD280同步控制器使用说明书 默认分类 2007-07-13 22:05:27 阅读822 评论0 字号:大中小订阅 JGD系列同步控制器是本公司在原生产的单一型号基础上推出的成系列同步控制装置,内部采用计算机为核心的全数字化设计,每台控制器能同时控制四台或八台电机的运转,使用非常灵活、简便。JGD系列同步控制器拥有完善的功能,在技术上处于国内领先水平,在性能上可与国外同类产品相媲美。广泛适用于由多台调速系统组成的各种机械设备上,如电力、钢铁、造纸、纺织、印染、电缆光纤、塑料等行业。可对线速度、位移、张力、距离等进行控制,是机器设备的最佳选择。 一、型号说明 1.主要特点 A、数字化 JGD系列控制器采用单片计算机控制,可通过对控制器进行多种参数设置,设置参数时通过数码显示。本控制器内有记忆体,断电后能自动保留用户设置的参数。 B、功能强大 1)JGD系列控制器每台有三种给定输入方式(内部给定、外部电压给定、外部电流给定)。 2)JGD-280控制器每台可控制八个独立单元有八路输出(V01~V08)。 3)每个控制单元的输出可作为另外控制单元的输入(单元串、并联使用)。可将一台控制器作为二台或三台独立控制器使用。 4)具有缓起动、停车功能,时间可设置(0~100秒)。 5)具有故障报警及起动信号继电器输出,其驱动能力达5A。 C、高精度 本系列控制器输入、输出模拟信号采用高分辨率的A/D、D/A转换器,其分辨率可达0.1%。 D、通用性

外部给定输入采用标准的0~10V或4~20mA,控制输出0~10V,可与各种调速控制器相匹配。 E、使用简便 1)用户修改控制参数可在控制器起动状态下进行,便于用户调试设备。 2)具有对设定的参数进行锁定的功能,能避免其他人员误动。 3)外部连线少,简化用户设计及调试设备工作,大量节省用户的人力、物力、财力。 F、工作可靠 JGD系列同步控制器经过精心设计制造,内部工作电源采用开关电源。具有抗干扰能力强,工作电压范围宽,能保证在电网电压波动范围大的地方均能正常工作,其工作电压在150~300VAC。 2.主要技术指标 A、控制电压输出 ·输出电压分辨率0.01V ·输出电压驱动能力≤5mA ·输出电压稳定度≤0.2% B、给定、反馈信号输入 ·给定、反馈电压输入分辨率0.01V ·外部给定电压输入精度≤0.8% ·反馈电压输入精度≤5±0.01V C、内部电源输出负载能力 ·+24V电源最大输出电流≤200mA ·+10V电源最大输出电流≤10mA ·5V电源最大输出电流≤100mA 3.使用条件 工作电压(交流):220V±30%50~60Hz 工作环境温度:0~50℃ 相对环境湿度:<90% 不结露 海拔高度:<1000m 周围无腐蚀、粉尘气体及易燃易爆之危险品

系统电源控制设备

前面板 1.面板电源输出插座 输出电流10A,此插座默认为直通插座,可根据需要更改为受控插座. 2.电源电压指示(2U) 误差小于1V. 3..直通按键 按下此开关会强制开启所有输出。此开关为隐藏式设计,以防误操作。 锁定键和状态指示 长按锁定按键,可以锁定/解锁-按键。指示灯在电平控制、开关 控制状态下常亮,在RS232数据控制状态下闪亮,-设置延时闪亮一次,取消延时闪亮次;锁 定/解锁时,该指示灯闪亮次。 时序开启钥匙 钥匙处于ON时打开时序,处于OFF时关闭时序。 4(2U)5.八路控制按键(2U)及状态指示 亮灯时表示该路有输出,按一次按键转换一次开关状态。长 按某一个按键,可以将该路设置成关的时候延时10分钟(第七路为10秒)。同时按下5和6按键, 可以将机器恢复出厂设置。此8个按键可以被第九个按键锁定,被锁定后,8个按键无效。6.(2U)181824(4)(仅限于2U )第一和第二路(后板下排1-6插座)带20A 双重净化功能,符合欧洲CISPR 和美国FCC 规范.对需要高品质电源的设备,如音响系统的周边设备(调音台、 均衡器、效果器、无线话筒、DVD 等),医疗设备,精密仪器等,建议使用此六个 插座。电源净化功能,对于消除系统间电磁干扰,提高音视频设备的信噪比, 保证系统稳定性,有明显的作用。

后面板 L N 1.级联输入和级联输出口 2.RS232控制输入接口 3.5V输入控制口和短路输入控制口 4.通道1输出插座(共3个,带净化) 5.通道2输出插座(共3个,带净化) 6.通道3-8输出插座 7.接地端子 8.空气开关火线和零线接入端子10.RS232控制输入接口11.四位凤凰接线端子 包含短路触发,5V输入触发, 5V输出触发接口12.1-8路输出插座13.电源输入电缆 1.接入电源 由具备电工上岗资质人员进行操作。 从配电箱取电,根据实际功率要求使用相应线径,推荐使用6平方纯铜电线。 注意:要按照标示,正确接入各电极,不能接错。本产品为I类电器,务必接地,确保安全。 2.手动控制 开启空气开关,通过机器面板的时序开关(或者钥匙),开启时序电源输出和关闭时序电源输出。 (仅限2U设备)可单独按动1-8按键,控制该路的输出;该路灯亮表示有输出,灯灭表示没输出。 (仅限2U设备)在特殊情况下,按下面板上隐藏的"bypass"按键,可以强制打开1-8通道输出. 3.级联控制 当输出路数不够时,可通过级联扩展,本机可级联2台。 将电脑通过RS232连接到级联主机,在PC软件上将第7路打钩(2U机器可长按面板第7按键)。 PC PC 1U连接图2U连接图软件控制界面

CameraLink接口 1.CameraLink接口简介 1.1CameraLink标准概述 Camera Link 技术标准是基于 National Semiconductor 公司的 Channel Link 标准发展而来的,而 Channel Link 标准是一种多路并行 LVDS 传输接口标准。 低压差分信号( LVDS )是一种低摆幅的差分信号技术,电压摆幅在 350mV 左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在 1.923Gbps 。 90 年代美国国家半导体公司( National Semiconductor )为了找 到平板显示技术的解决方案,开发了基于 LVDS 物理层平台的 Channel Link 技术。此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用。 如图1.1所示, Channel Link 由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达 2.38G 。数据发送器含有 28 位的单端并行信号和 1 个单端时钟信号,将 28 位 CMOS/TTL 信号串行化处理后分成 4 路 LVDS 数据流,其 4 路串行数据流和 1 路发送 LVDS 时钟流在 5 路 LVDS 差分对中传输。接收器接收从 4 路 LVDS 数据流和 1 路 LVDS 时钟流中把传来的数据和时钟信号 恢复成 28 位的 CMOS/TTL 并行数据和与其相对应的同步时钟信号。 图1.1 camera link接口电路

1.2CameraLink端口和端口分配 1.2.1端口分配 在基本配置模式中,端口 A 、 B 和 C 被分配到唯一的 Camera Link 驱动器 / 接收器对上;在中级配置模式中,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上;在完整配置模式中,端口 A 、 B 和 C 被分配到第一个驱动器 / 接收器对上,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上,端口 G 和 H 被分配到第三个驱动器 / 接收器对上。表1.1给出了三种配置的端口分配, Camera Link 芯片及连接器的使用数量情况。 表1.1 3种配置模式的端口分配 图1.2 各种配置下的端口连接关系

实验三时序逻辑电路 学习目标: 1、掌握时序逻辑电路的一般设计过程 2、掌握时序逻辑电路的时延分析方法,了解时序电路对时钟信号相关参数的基本要求 3、掌握时序逻辑电路的基本调试方法 4、熟练使用示波器和逻辑分析仪观察波形图 实验内容: 1、广告流水灯(第 9 周课内验收)用触发器、组合函数器件和门电路设计一个广告流水灯,该流水灯由 8 个 LED 组成,工作时始终为 1 暗 7 亮,且这一个暗灯循环右移。 (1) 写出设计过程,画出设计的逻辑电路图,按图搭接电路 (2) 将单脉冲加到系统时钟端,静态验证实验电路 (3) 将 TTL 连续脉冲信号加到系统时钟端,用示波器观察并记录时钟脉冲 CP、触发器的输出端 Q2、Q1、 Q0 和 8 个 LED 上的波形。 2、序列发生器(第 10 周课内实物验收计数器方案)分别用 MSI 计数器和移位寄存器设计一个具有自启动功能的 01011 序列信号发生器 (1) 写出设计过程,画出电路逻辑图 (2) 搭接电路,并用单脉冲静态验证实验结果 (3) 加入 TTL 连续脉冲,用示波器观察观察并记录时钟脉冲 CLK、序列输出端的波形。 3、4 位并行输入-串行输出曼切斯特编码电路(第10周课内验收,基础要求占70%,扩展要求占30%) 在电信与数据存储中, 曼彻斯特编码(Manchester coding),又称自同步码、相位编码(phase encoding,PE),它能够用信号的变化来保持发送设备和接收设备之间的同步,在以太网中,被物理层使用来编码一个同步位流的时钟和数据。曼彻斯特编码用电压的变化来分辨 0 和 1,从高电平到低电平的跳变代表 0,而从低电平到高电平的跳变代表 1。信号的保持不会超过一个比特位的时间间隔。即使是 0 或 1 的序列,信号也将在每个时间间隔的中间发生跳变。这种跳变将允许接收设备的时钟与发送设备的时钟保持一致,图 3.1 为曼切斯特编码的例子。 设计一个电路,它能自动加载 4 位并行数据,并将这4位数据逐个串行输出(高位在前),每个串行输出位都被编码成曼切斯特码,当 4 位数据全部传输完成后,重新加载新数据,继续传输,如图 3.2 所示。

盤面型RSC-406 使用說明書 浙江麗水謙勝機電有限公司浙江麗水水閣工業區綠穀大道306-2號 TEL: FAX:068

目錄1.前言 ~1~ 1.前言... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... .... ... ... . (2) 2.產品特點介紹... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... .... ... .... (3) 3.產品檢 查 … … ..3 3-1 數位式同步控制器外 觀... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ....... (3) 3-2 控制器外觀尺 (4) 3-3 控制器面板顯示及操作說 明... ... ... ... ... ... ... ... ... ... .... ... ... ... ..... ... (4) 3-3-1 LED 燈號說 明… … … … … … … … … … … … … … … … … … … … … … .5 3-3-2 按鍵操作說 ...5 首先感謝您選用由本公司所開發的 RSC-406 數位式比例同步控制器。 為了充分地發揮RSC-406 的功能,及確保使用者的安全,請詳閱本操作手 冊。當您使用中出現任何疑點而本手冊無法提供您解決方案時,請您與本公司連絡,我們將竭誠為您服務。並請您繼續采用本公司的產品。 4.安裝... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... .... ... .. (6) !注意 4-1 使用環境... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ....... ... .. (6) 4-2 控制器後端護弓,端子安裝方式及盤面安裝尺寸... ... ... ... ... ... ... ... .. (6) 5.配線... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ...... ... ... ... ..... (7) 5-1 端子功能說 明… … … … … … … … … … … … … … … … … … … … … … .....

电源时序器 电源时序器能够按照由前级设备到后级设备逐个顺序启动电源,关闭供电电源时则由后级到前级的顺序关闭各类用电设备,这样就能有效的统一管理和控制各类用电设备,避免了人为的失误操作,同时又可减低用电设备在开关瞬间对供电电网的冲击,也避免了感生电流对设备的冲击,确保了整个用电系统的稳定。 1 产品使用说明 ● 1.备用电源开关:可以用来防止控制器因某些原因而失去控 制,关掉此开关,可同时连接所有插座电源; ● 2.输出插座指示灯:当每个指示灯亮相对应插座将连通电源; ● 3.电源指示灯:打开此电源控制器后,指示灯就会显示已经启 动的控制信号; ● 4.电源开关:打开此电源开关时,就会自动按照:1~8顺序把 电源输入插座中。关掉此电源,就会自动按照:8~1此顺序 把电源切断; ● 5.电源输入电缆; ● 6.电源输出插座。 2 功能与使用 1.此电源开关打开时,控制器可以按顺序连接到每一个插座。相

反地,关掉此电源开关,控制器可以反顺序切断每一个插座上 的电源。 2.此装置可以用作会议中心,电脑机房,电视播放系统与其他电源系统,都需要按照顺序的打开设备。 3 技术规格 1. 每一路输出电流15A; 2. 控制电源:8通道; 4 RS232/RS485串口控制 RS232 (3脚接收,5脚信号地) RS485 (3脚B,5脚A) ●波特率9600 数据位8 停止位1 校验位None ●每接收正确的串口命令,电源指示灯闪烁三次,频率为0.5 秒/次。 ●A0是修改ID(00)地址码。00是固定公共地址码,例如ID 是01指令是CA 20 00 A0 01 AC ●A1各路开关例如:第一路开:CA 20 00 A1 11 AC 关:CA 20 00 A1 10 AC 第二路开:CA 20 00 A1 21 AC 关:CA 20 00 A1 20 AC 第三路开:CA 20 00 A1 31 AC 关:CA 20 00 A1 30 AC

控制器操作说明书 控制器有四个按键,分别是设定键、上升键、下降键、输入键。 显示数码管分为两行,上排为四位数码管,显示为参数和数值,下排为两位数码管,显示为当前的工作通道。 开始 1:按住设定键3秒以上,上排显示LU(通道设定,本控制器为自动检测输出路数,此参数可不必改动,如果改动,在下次上电即会被改回实际输出路数),按下输入键后,(以下的描述适用于其它的参数改动)上排显示通道设定值。此时可点按上升键或下岗键即可改变设定通道值。改动完后按下输入键,即可保存。如果不想保存可直接按下设定键。上排显示会显示下一参数的名称。 2:上排显示T-E(脉冲间隔时间的分钟参数),按下输入键后,操作同上。参数范围为0分到99分。 3:上排显示T-S(脉冲间隔时间的秒参数),按下输入键后,操作同上。参数范围为1秒到99秒。 4:上排显示S-H(停止时间的小时参数),按下输入键后,操作同上。参数范围为0小时到99小时。 5:上排显示S-E(停止时间的分钟参数),按下输入键后,操作同上。参数范围为0分钟到99分钟。 6:上排显示P-S(脉冲时间参数),按下输入键后,操作同上。参数范围为0.01秒到9.99秒。 7:上排显示SL(级联标志),按下输入键后,上排显示OFF或ON。按下上升键或下降键改变显示,改动完后按下输入键,即可保存。如果不想保存可直接按下设定键。上排显示会显示下一参数的名称。参数范围为OFF(关闭)和ON(打开)。 8:上排显示STAR(级联的主机标志),按下输入键后,上排显示OFF或ON。按下上升键或下降键改变显示,改动完后按下输入键,即可保存。如果不想保存可直接按下设定键。上排显示会显示下一参数的名称。参数范围为OFF(关闭)和ON(打开)。 9:上排显示RST(出厂值恢复标志),按下输入键后,上排显示OFF或ON。按下上升键或下降键改变显示,改动完后按下输入键,即可保存。如果不想保存可直接按下设定键。上排显示会显示下一参数的名称。参数范围为OFF(关闭)和ON(打开)。 10:上排显示LU01---LU12(通道使能标志),按下输入键后,上排显示OFF或ON。按下上升键或下降键改变显示,改动完后按下输入键,即可保存。如果不想保存可直接按下设定键。上排显示会显示下一参数的名称。参数范围为OFF(关闭)和ON(打开)。 11:退出参数设定状态。(如果在没有按动任何按键的12秒时,亦自动退出参数设定状态)。结束 控制器手动控制输出操作方法: 在控制器工作状态下,按住输入键不放,点按一下下降键,上排显示HAND,下排显示第几通道数值,此时按下上升键或下降键改动要测试输出的通道,点按输入键时即可输出电压。