实验四用VHDL设计多功能信号发生器

一、设计任务

基于《VHDL语言》,通过给定的仪器(EDA6000试验箱)设计一个多功能信号发生器,要求:

(1)能产生周期性正弦波、方波、三角波、锯齿波以及用户自己编辑的特定波形(选作);

(2)输出信号的频率范围为100Hz~200KHz,且输出频率可以调节;

(3)具有显示输出波形、频率的功能。(选作)

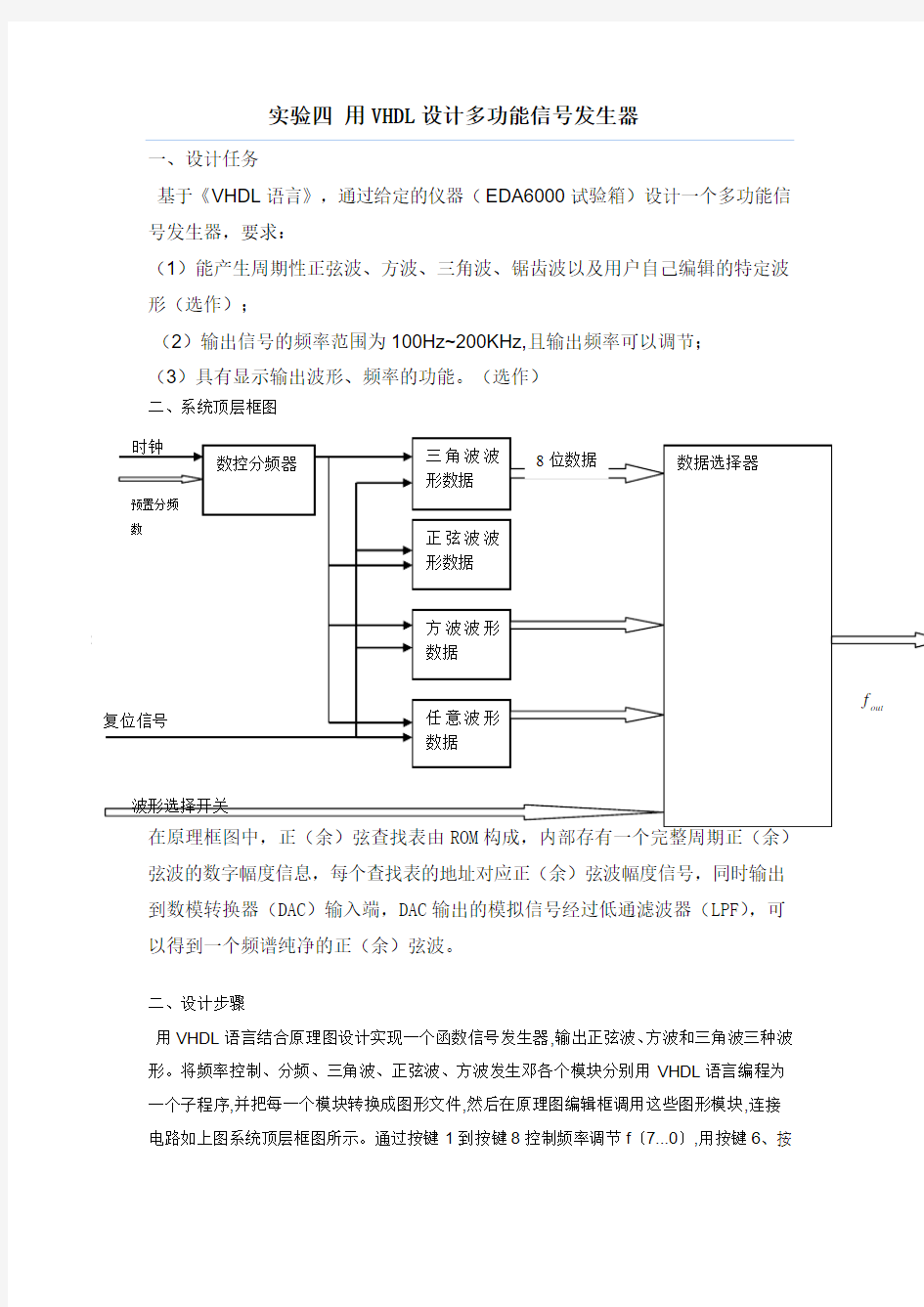

二、系统顶层框图

弦波的数字幅度信息,每个查找表的地址对应正(余)弦波幅度信号,同时输出到数模转换器(DAC)输入端,DAC输出的模拟信号经过低通滤波器(LPF),可以得到一个频谱纯净的正(余)弦波。

二、设计步骤

用VHDL语言结合原理图设计实现一个函数信号发生器,输出正弦波、方波和三角波三种波形。将频率控制、分频、三角波、正弦波、方波发生邓各个模块分别用VHDL语言编程为一个子程序,并把每一个模块转换成图形文件,然后在原理图编辑框调用这些图形模块,连接电路如上图系统顶层框图所示。通过按键1到按键8控制频率调节f〔7...0〕,用按键6、按

键7、按键8控制dlt 、sin 、sqr 波形选通,最后把八位输出接DAC0832通过D/A 转换,从示波器上就能看到波形输出。按下不同的按键输出不同的波形及频率。

三、系统设计

(1)数控分频器模块

在时钟的作用下,通过预置分频数DIN ,来改变输出频率。假如分频系数为N ,波形存储模块存储一个周期的波形,实验里按照一个周期波形采样64个点存储在波形存储模块里。则输出频率N f f clk

out .64=

(2).数据存储模块 (存储波形数据)

数据存储模块主要存的是正弦波、三角波、锯齿波等一个周期的采样点。

三角波模块可设计一个可逆计数器实现,设计时设置一变量作为工作状态标志,在此变量为0时,当检测到时钟的上升沿进行加同一个数操作;为1时,进行减同一个数操作。DA 转换采用的DA0832,输入有8个数据端,范围是0到255;而且设置64个时钟周期为一个三角波周期,所有每次加、减为8.

锯齿波的存储数据与三角波类似。

方波可以通过交替输出全0和全1,并给以32个周期的延时来实现。

正弦波:要通过波形变换实现把a sin 变换成5.127*)1(cos +a 的形式进行采样,然后变换成8位二进制码,存储在波形存储器里。

(3)数据选择器模块

在波形开关的控制下,选择相应的波形输出。可以用3个按键来控制波形选择(4).LED 显示模块 (选作)

LED 显示模块主要是完成频率控制字的显示,由于本次实验采用八位的由键盘输入的频率控制字,累计寻址,读取8位地址长度256点的一个周期波形的数字幅度信息,所以频率控制字控制着频率的大小,而恰好此时的频率控制字就是系统输出波形的频率,所以,LED 显示的也是波形的频率。此模块主要的功能是将外部键盘的8位二进制数转换成三位BCD 码。

四、实验内容

设计程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity Vhdl1 is

port(clk,sel :in std_logic;

pout: out integer range 255 downto 0);

end;

architecture dacc of Vhdl1 is

signal q: integer range 63 downto 0;

signal q1: integer range 2 downto 0;

signal d: integer range 255 downto 0;

begin

process(clk)

begin

if clk'event and clk='1' then

if q<63 then q<=q+1;

else q<=0;

end if;

end if;

end process;

process(sel)

begin

if sel'event and sel='1' then

if q1<3 then q1<=q1+1;

else q1<=0;

end if;

end if;

end process;

process(q,q1)

begin

case q1 is

when 0=> 正弦波

case q is

when 00=>d<=255; when 01=>d<=254; when 02=>d<=252; when 03=>d<=249; when 04=>d<=245; when 05=>d<=239; when 06=>d<=233; when 07=>d<=225; when 08=>d<=217; when 09=>d<=207; when 10=>d<=197; when 11=>d<=186; when 12=>d<=174; when 13=>d<=162; when 14=>d<=150; when 15=>d<=137; when 16=>d<=124; when 17=>d<=112; when 18=>d<=99; when 19=>d<=87; when 20=>d<=75; when 21=>d<=64; when 22=>d<=53; when 23=>d<=43; when 24=>d<=34; when 25=>d<=26; when 26=>d<=19; when 27=>d<=13; when 28=>d<=8; when 29=>d<=4; when 30=>d<=1; when 31=>d<=0;

when 63=>d<=255; when 62=>d<=254; when 61=>d<=252; when 60=>d<=249; when 59=>d<=245; when 58=>d<=239; when 57=>d<=233; when 56=>d<=225; when 55=>d<=217; when 54=>d<=207; when 53=>d<=197; when 52=>d<=186; when 51=>d<=174; when 50=>d<=162; when 49=>d<=150; when 48=>d<=137; when 47=>d<=124; when 46=>d<=112; when 45=>d<=99; when 44=>d<=87; when 43=>d<=75; when 42=>d<=64; when 41=>d<=53; when 40=>d<=43; when 39=>d<=34; when 38=>d<=26; when 37=>d<=19; when 36=>d<=13;

when 35=>d<=8; when 34=>d<=4; when 33=>d<=1; when 32=>d<=0;

when others=>null;

end case;

when 1=> 方波

case q is

when 00=>d<=255; when 01=>d<=255; when 02=>d<=255; when 03=>d<=255; when 04=>d<=255; when 05=>d<=255; when 06=>d<=255; when 07=>d<=225; when 08=>d<=255; when 09=>d<=255; when 10=>d<=255; when 11=>d<=255; when 12=>d<=255; when 13=>d<=255; when 14=>d<=255; when 15=>d<=255; when 16=>d<=255; when 17=>d<=255; when 18=>d<=255; when 19=>d<=255; when 20=>d<=255; when 21=>d<=255; when 22=>d<=255; when 23=>d<=255; when 24=>d<=255; when 25=>d<=255; when 26=>d<=255; when 27=>d<=255; when 28=>d<=255; when 29=>d<=255; when 30=>d<=255; when 31=>d<=255;

when 63=>d<=0; when 62=>d<=0; when 61=>d<=0; when 60=>d<=0;

when 59=>d<=0; when 58=>d<=0; when 57=>d<=0; when 56=>d<=0;

when 55=>d<=0; when 54=>d<=0; when 53=>d<=0; when 52=>d<=0;

when 51=>d<=0; when 50=>d<=0; when 49=>d<=0; when 48=>d<=0;

when 47=>d<=0; when 46=>d<=0; when 45=>d<=0; when 44=>d<=0;

when 43=>d<=0; when 42=>d<=0; when 41=>d<=0; when 40=>d<=0;

when 39=>d<=0; when 38=>d<=0; when 37=>d<=0; when 36=>d<=0;

when 35=>d<=0; when 34=>d<=0; when 33=>d<=0; when 32=>d<=0;

when others=>null;

end case;

when 2=> 三角波

case q is

when 00=>d<=0; when 01=>d<=1; when 02=>d<=2; when 03=>d<=3;

when 04=>d<=4; when 05=>d<=5; when 06=>d<=6; when 07=>d<=7;

when 08=>d<=8; when 09=>d<=9; when 10=>d<=10; when 11=>d<=11;

when 12=>d<=12; when 13=>d<=13; when 14=>d<=14; when 15=>d<=15;

when 16=>d<=16; when 17=>d<=17; when 18=>d<=18; when 19=>d<=19;

when 20=>d<=20; when 21=>d<=21; when 22=>d<=22; when 23=>d<=23; when 24=>d<=24; when 25=>d<=25; when 26=>d<=26; when 27=>d<=27;

when 28=>d<=28; when 29=>d<=29; when 30=>d<=30; when 31=>d<=31;

when 62=>d<=0; when 61=>d<=1; when 60=>d<=2;

when 59=>d<=3; when 58=>d<=4; when 57=>d<=5; when 56=>d<=6;

when 55=>d<=7; when 54=>d<=8; when 53=>d<=9; when 52=>d<=10;

when 51=>d<=11; when 50=>d<=12; when 49=>d<=13; when 48=>d<=14; when 47=>d<=15; when 46=>d<=16; when 45=>d<=17; when 44=>d<=18; when 43=>d<=19; when 42=>d<=20; when 41=>d<=21; when 40=>d<=22; when 39=>d<=23; when 38=>d<=24; when 37=>d<=25; when 36=>d<=26; when 35=>d<=27; when 34=>d<=28; when 33=>d<=29; when 32=>d<=30; when others=>null;

end case;

when 2=> 锯齿波

case q is

when 00=>d<=0; when 01=>d<=3; when 02=>d<=6; when 03=>d<=9;

when 04=>d<=12; when 05=>d<=15; when 06=>d<=18; when 07=>d<=21; when 08=>d<=24; when 09=>d<=27; when 10=>d<=30; when 11=>d<=33; when 12=>d<=36; when 13=>d<=39; when 14=>d<=42; when 15=>d<=45; when 16=>d<=44; when 17=>d<=43; when 18=>d<=42; when 19=>d<=41; when 20=>d<=40; when 21=>d<=39; when 22=>d<=38; when 23=>d<=37; when 24=>d<=36; when 25=>d<=35; when 26=>d<=34; when 27=>d<=33; when 28=>d<=32; when 29=>d<=31; when 30=>d<=30; when 31=>d<=29;

when 62=>d<=28; when 61=>d<=27; when 60=>d<=26;

when 59=>d<=25; when 58=>d<=24; when 57=>d<=23; when 56=>d<=22; when 55=>d<=21; when 54=>d<=20; when 53=>d<=19; when 52=>d<=18; when 51=>d<=17; when 50=>d<=16; when 49=>d<=15; when 48=>d<=14; when 47=>d<=13; when 46=>d<=12; when 45=>d<=11; when 44=>d<=10; when 43=>d<=9; when 42=>d<=8; when 41=>d<=7; when 40=>d<=6; when 39=>d<=5; when 38=>d<=4; when 37=>d<=3; when 36=>d<=2;

when 35=>d<=1; when 34=>d<=0; when 33=>d<=0; when 32=>d<=0; when others=>null;

end case;

end case;

end process;

pout<=d;

end;

五、实验结果

当a=0时,显示正弦波当a=0时,显示方波

当a=0时,显示三角波当a=0时,显示锯齿波

六、参考资料

《EDA技术实用教程》科学出版社

《创新实验》实验报告 —基于VHDL的编程和硬件实现

一、实验目的 1.熟悉和掌握硬件描述语言VHDL的基本语法及编写; 2.掌握软件Xilinx ISE 10.1的使用; 3.熟悉SDZ-6电子技术实验箱的使用; 4.了解节拍脉冲发生器等基本电路的实现; 5.了解八位二进制计数器的功能与设计; 6.学习键盘和七段数码管显示的控制和设计。 二、实验内容 1.Xilinx ISE 10.1软件的使用; 2.节拍脉冲发生器等基本电路的实现; 3.八位二进制计数器的实现 4.键盘扫描及显示的实现 三、实验器材 1、PC机 2、SDZ-6电子技术实验箱 3、正负5V电源 4、I/O接口线 四、软件的使用 在安装Xilinx10.1软件时,需要一个ID号,其实这个ID号是可以重复使用的,几个同学在官网注册后就可以共享ID号了。 安装完成之后就可以使用这个软件编写相应的VHDL的程序。 1.新建工程 File—>New Project 弹出下面的对话框 输入工程名后单击Next。然后根据本实验的实验箱进行以下设置。

以后的步骤一般都是单击Next(有些资料上会介绍有些这些步骤的具体功能,但对于本实验不必用到),最后单击Finish,完成新建一个工程。在窗口的左边会出现刚刚新建的工程,如下: 2.新建一个VHDL的源文件。 在上图中,右击工程选择New Source ,弹出如下对话框。

在对画框的左边选择VHDL Module,输入文件的名字(改名字最好是你定义的实体的名字)。单击Next。出现下面的对话框。 该对话框主要是对外部端口的编辑。可以直接跳过,即单击Next,在源文件上编辑端口。然后在接下来的对话框中单击Finish。完成建立一个源文件。窗口右边就会出现刚才编辑的源文件。 3.编写和编译代码 将事先编好的代码复制到源文件里,然后保存文件。 选中左边的文件名,在窗体的左边出现如下编辑文档内容。

实验报告 课程名称网络技术基础实验项目TCP/IP协议配置实验仪器计算机 系别 专业 班级/学号 学生姓名 实验日期 成绩 指导教师

实验一 TCP/IP协议配置 一、实验目的(标题黑体小四) 1.熟练掌握模板的用法。 2.掌握CSS的用法。 3.掌握网站发布的方法。 二、实验内容 1. 创建和使用模板。 2. css的创建和使用。 3. 发布网站。 三、实验课时 4课时 四、实验步骤 创建网站 1、创建一个站点,并创建 images 文件夹存放图片。将示例图片拷贝至images 目录下 2、创建 CSS 文件,名称为 style.css,将其保存至 style文件夹。 3、创建模板文件 tpl.dwt,并保存。结果如下: (1) 给 tpl.dwt 附加样式表 style.css。 在 tpl.dwt 的空白处点击鼠标右键,选择“附加样式表”: 选择 style.css 文件: 完成后,在 tpl.dwt 的 head标签里有如下的代码: (2) 设置模板的背景颜色。打开 CSS 面板,为 style.css 新建一条 css 规则。过程如 下:

将背景颜色设为#ff1e70: 在 style.css 生成如下的代码: body { background-color: #ff1e70? } 3) 制作布局。插入一 2 行 2 列的表格。表格的宽度=316+634=950,其他的设置:让表格居中对齐。 (4) 消除表格两边的空隙。展开 CSS 样式表,双击 body: 双击 body后,打开“body的 CSS 规则定义”对话框,按照下面的方式设置:Style.css 的代码变为: body { background-color: #ff1e70? margin: 0px? }

课程设计报告 实践课题:VHDL与数字系统课程设计 学生:XXX 指导老师:XXX、XXX 系别:电子信息与电气工程系 专业:电子科学与技术 班级:XXX 学号:XXX

一、设计任务 用VHDL设计一个简单的处理器,并完成相关的仿真测试。 .设计要求: 图1是一个处理器的原理图,它包含了一定数量的寄存器、一个复用器、一个加法/减法器(Addsub),一个计数器和一个控制单元。 图1 简单处理器的电路图 数据传输实现过程:16位数据从DIN输入到系统中,可以通过复用器分配给R0~R7和A,复用器也允许数据从一个寄存器传通过Bus送到另外一个寄存器。 加法和减法的实现过程:复用器先将一个数据通过总线放到寄存器A中,然后将另一个数据放到总线上,加法/减法器对这两个数据进行运算,运算结果存入寄存器G中,G中的数据又可根据要求通过复用器转存到其他寄存器中。 1)Rx ←[Ry] :将寄存器Ry中的内容复制到Rx; 2)Mvi Rx,#D :将立即数存入寄存器Rx中去。 所有指令都按9位编码(取自DIN的高9位)存储在指令存储器IR中,编编码规则为IIIXXXYYY,III表示指令,XXX表示Rx寄存器,YYY表示Ry寄存器。立即数#D是在mvi指令存储到IR中之后,通过16位DIN输入

的。 有一些指令,如加法指令和减法指令,需要在总线上多次传输数据,因此需要多个时钟周期才能完成。控制单元使用了一个两位计数器来区分这些指令执行的每一个阶段。当Run信号置位时,处理器开始执行DIN输 时间 指令 T0T1T2T3 (mv):I0 (mvi):I1 (add):I2 (sub):I3 IR in IR in IR in IR in RY out,RX in,Done DIN out,RX in,Done RX out,A in RX out,A in ---- ---- RY out,G in,Addsub RY out,G in,Addsub ---- ---- G out,RX in,Done G out,RX in,Done 二、实现功能说明 2.1 mv Rx,Ry 实现的功能:将寄存器Rx的值赋给寄存器Ry(以mv R0, R5为例) (1 )计数器为“00”时,指令寄存器的置位控制信号输入端IRin=1有效,将DIN输入的数据的高9位锁存。 置位的控制信号如图3加粗黑线所示。 图3 (2)计数器为“01”时,首先控制单元根据设计器为“00”时输入的指令,向复用器发出选通控制信号,复用器根据该控制信号让R5的值输出到总线上,然后控制单元控制寄存器R0将总线上的值锁存,完成整个寄存器对寄存器的赋值过程。置位的控制信号和数据流如图4加粗黑线所示。 图4

VHDL课程设计-PS2键盘

目录 一、课程设计的目的与任务 (3) 二、课程设计题目 (3) 1、指定题目: (3) 2、自选题目: (3) 三、课程设计的内容与要求 (3) 1、设计内容 (4) 2、设计要求 (4) 四、实验仪器设备 (4) 五、设计方案 (4) 1、PS2解码 (4) 2、设计思路 (6) 3、模块设计 (7) 4、各模块分析 (8) (1)PS2时钟检测模块 8 (2)PS2解码模块 10 (3)PS2组合模块 12 (4)控制LED模块 14 (5)PS2总的组合模块 16 六、综合与仿真 (17) 1、综合 (17) 2、仿真 (18) (1)电平检测模块仿真 (18) (2)LED灯控制模块仿真 (18)

(3)PS2_module总模块仿真 (19) 七、硬件下载 (23) 八、心得体会 (24) 九、参考文献 (24) 一、课程设计的目的与任务 (1)熟练掌握EDA工具软件QuartusII的使用; (2)熟练用VHDL硬件描述语言描述数字电路; (3)学会使用VHDL进行大规模集成电路设计; (4)学会用CPLD\FPGA使用系统硬件验证电路设计的正确性; (5)初步掌握EDA技术并具备一定的可编程逻辑芯片的开发能力; 二、课程设计题目 1、指定题目: 0 :多功能计数器;1 :数字秒表;2 :简易数字钟;3 :简易频率计; 4 :彩灯控制器; 5 :交通灯控制器; 6 :四路智力竞赛抢答器; 7 :简易微波炉控制器;8 :表决器;9 :数字密码锁; 我的的学号尾数是2,所以我要做的题目是简易数字钟。由于我之前已经学过Verilog HDL和VHDL,所以简易数字钟相对于我比较简单,我完成了简易数字钟并验收后,再选择了另一个自选题目来完成。 简易数字钟:设计一个以“秒”为基准信号的简易数字钟,显示时、分、秒,同时可实现整点报时和清零(我已经完成,而且已经验收了)。 2、自选题目: 在完成了数字钟的设计后,我选择了另一个设计的题目,那就是PS2键盘扫描。所以这次课程设计我的报告主要详细写的是PS2键盘扫描的程序,而不是简易数字钟。 PS键盘扫描:设计一个PS键盘扫描程序,能接受键盘的输入时钟和数据,区别哪一个键输入,同时解译通码和断码,使用LED灯来显示收到的数据。三、课程设计的内容与要求

VHDL实验报告 60 庄炜旭实验三. 4位可逆计数器,4位可逆二进制代码-格雷码转换器设计 一.实验目的 学习时序电路的设计,仿真和硬件测试,进一步熟悉VHDL设计技术 1. 学习4位可逆计数器的设计 2. 学习4位可逆二进制代码-格雷码转换器设计 二.实验内容 设计4位可逆计数器,及4位可逆二进制代码-格雷码转换器,并仿真,下载。 [具体要求] 1.4位可逆计数器 a)使用CLOCK_50作为输入时钟,其频率为50MHz(对于频率大于50Hz的闪烁, 人眼会看到连续的光),因而,对其进行225的分频后,再用于时钟控制。(可 利用实验一) b)使用拨码开关SW17作为模式控制,置‘1’时为加法计数器,置‘0’时为减 法计数器,同时使用LEDR17显示SW17的值。 c)使用KEY3作为异步复位开关(按下时为0,不按为1),当为加法计数器时, 置“0000”,当为减法计数器时,置“1111”。 d)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高 位,LEDR0为低位。 2.4位可逆二进制代码――格雷码转换器 a)使用拨码开关SW17作为模式控制,置‘1’时为二进制代码―>格雷码转换, 置‘0’时为格雷码―>二进制代码,同时使用LEDR17显示SW17的值。 b)使用拨码开关SW3, SW2, SW1, SW0作为输入的被转换数,SW3为高位,SW0 为低位。 c)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高 位,LEDR0为低位。 三.管脚设定 SW[0]PIN_N25 SW[1]PIN_N26 SW[2]PIN_P25 SW[3] PIN_AE14 SW[17] PIN_V2 LEDR[0] PIN_AE23 LEDR[1] PIN_AF23 LEDR[2] PIN_AB21 LEDR[3] PIN_AC22 LEDR[17] PIN_AD12 KEY[3] PIN_W26

WEB系统开发 综合实验报告 题目红尘客栈网上订房页面 专业计算机科学与技术(信息技术及应用) 班级计信2班 学生蒋波涛 重庆交通大学 2013年

目录 一、设计目的 (3) 二、设计题目 (3) 三、结构设计 (3) 四、技术分析 (4) 五、设计过程 (7) 六、实验心得 (10) 七、实验总结 (11)

一、设计目的 在Internet飞速发展的今天,互联网成为人们快速获取、发布和传递信息的重要渠道,它在人们政治、经济、生活等各个方面发挥着重要的作用。因此网站建设在Internet 应用上的地位显而易见,它已成为政府、企事业单位信息化建设中的重要组成部分,从而倍受人们的重视。我们当代大学生更是离不开网络给我们带来的好处与便利.但是,我们成天浏览的网站网页到底是如何制作的呢?我想这一点很多同学都没有去深究过.所以,这学期我选择了”web网页设计”这门课, 本课程的设计目的是通过实践使同学们经历网页制作的全过程. 通过设计达到掌握网页设计、制作的技巧。 了解和熟悉网页设计的基础知识和实现技巧。根据题目的要求,给出网页设计方案,可以按要求,利用合适图文素材设计制作符合要求的网页设计作品。 熟练掌握Photoshop cs3、Dreamweaver cs等软件的的操作和应用。增强动手实践能力,进一步加强自身综合素质。学会和团队配合,逐渐培养做一个完整项目的能力。 二、设计题目 《红尘客栈》 三、结构设计 选定主题,确定题目之后,在做整个网站之前对网站进行需求分析。首先,做好需求调研。调研方式主要是上网查阅资料,在图书馆里翻阅相关书籍。 然后,调研结束之后对整个网站进行功能描述,并对网站进行总体规划,接着逐步细化。 我们选做的主题是个人主页,并且选定题目为“红尘客栈”,其目的是做一个简单的网站,介绍酒店概况,提供一定的资讯信息。 四、技术分析 (一)建立布局 在这次的网页设计中用到大量的布局,所以怎么样建立布局是关键。Dreamweaver cs3是大多数人设计网页的称手兵器,也是众多入门者的捷径。特别是其在布局方面的出色表现,更受青睐。大家都知道,没有表格的帮助,很难组织出一个协调合理的页面。 1.点击“ALT+F6”键,进入布局模式,插入布局表格。建立一个大概的布局。 2.使用背景图片:选中该项,按浏览可以插入一幅准备好的图片作为表格的背景,因为图片是以平铺的形式作为表格背景,所以表格大小和图片尺寸都要控制好。 (二)网页中的图像

湖南人文科技学院 课程设计报告课程名称: VHDL语言与EDA课程设计 ~ 设计题目:出租车自动计价器设计 系别: 专业: 班级: 学生姓名: 学号: 起止日期: 2011年6月13日~2011年6月26日 $ 指导教师: 教研室主任:

摘要 随着我国社会经济的全面发展,各大中小城市的出租车营运事业发展迅速,出租车已经成为人们日常出行选择较为普遍的交通工具。出租车计价器是出租车营运收费的专用智能化仪表,是出租车市场规范化、标准化以及减少司机与乘客之间发生纠纷的重要设备。一种功能完备、简单易用、计量准确的出租车计价器是加强出租车行业管理、提高服务质量的必备品。根据预定的设计要求和设计思路,我们使用VHDL硬件描述语言设计了一个实际的基于Altera FPGA芯片的出租车自动计价器系统,介绍了该系统的电路结构和程序设计。通过在软件中编译和下载测试,得到了仿真波形和关键的设计结果。经过在实验箱上进行硬件测试,证明该出租车计价系统具有实用出租车计价器的基本功能,如能进一步完善,将可以实用化和市场化。 关键词:出租车自动计价器;VHDL; FPGA ;

目录 设计要求 (1) 1、方案论证与对比 (1) 方案一 (1) 方案二 (2) 两种方案的对比 (2) 2、实验步骤和设计过程 (2) 计程模块 (2) 等待计时模块 (2) 计费模块 (3) 3、调试与操作说明 (3) 中的VHDL程序 (3) 程序的编译与及仿真波形 (6) 程序的下载与功能的测试 (7) 4、课程设计心得体会 (9) 5、元器件及仪器设备明细 (10) 6、参考文献 (11) 7、致谢 (12)

目录 一、课程设计的目的与任务 (1)熟练掌握EDA工具软件QuartusII的使用;

(2)熟练用VHDL硬件描述语言描述数字电路; (3)学会使用VHDL进行大规模集成电路设计; (4)学会用CPLD\FPGA使用系统硬件验证电路设计的正确性; (5)初步掌握EDA技术并具备一定的可编程逻辑芯片的开发能力; 二、课程设计题目 1、指定题目: 0 :多功能计数器; 1 :数字秒表; 2 :简易数字钟; 3 :简易频率计; 4 :彩灯控制器; 5 :交通灯控制器; 6 :四路智力竞赛抢答器; 7 :简易微波炉控制器; 8 :表决器;9 :数字密码锁; 我的的学号尾数是2,所以我要做的题目是简易数字钟。由于我之前已经学过Verilog HDL和VHDL,所以简易数字钟相对于我比较简单,我完成了简易数字钟并验收后,再选择了另一个自选题目来完成。 简易数字钟:设计一个以“秒”为基准信号的简易数字钟,显示时、分、秒,同时可实现整点报时和清零(我已经完成,而且已经验收了)。 2、自选题目: 在完成了数字钟的设计后,我选择了另一个设计的题目,那就是PS2键盘扫描。所以这次课程设计我的报告主要详细写的是PS2键盘扫描的程序,而不是简易数字钟。 PS键盘扫描:设计一个PS键盘扫描程序,能接受键盘的输入时钟和数据,区别哪一个键输入,同时解译通码和断码,使用LED灯来显示收到的数据。 三、课程设计的内容与要求 1、设计内容 (1)系统功能的分析; (2)实现系统功能的实际方案; (3)编写各功能模块的VHDL语言程序; (4)对各功能模块进行编译、综合、仿真、分析; (5)顶层文件设计 (6)对整个系统进行编译、综合、仿真、分析; (7)在CPLD\FPGA实验开发系统试验箱上进行硬件验证; (8)写实验报告;

《大学计算机基础》 实验报告 专业名称: 电子商务2班 学号: xxxxxxxxxxx 姓名: x x 指导教师: x x 2011年12月24日

目录 第一章网站主题设计说明 (1) 1.1 主题内容 (1) 1.2 设计思路 (1) 第二章网站内容设计 (2) 1.1 链接1标题 (2) 1.2 链接2标题 (2) 1.3 flash制作说明 (2) 第三章网站技术难点 (3) 第四章心得体会..................................... ..... ......................... (4)

第一章网站主题设计说明 1.1 主题内容 (1) 网站主题为“四季の花”,包括春夏秋冬四个季节的比较典型的花朵及有关花的诗句,色彩缤纷,十分艳丽夺目。 1.2 设计思路 (2) 大多网站都设计的关于音乐,影视,购物等非常热门的东西,本站设计的主题是花,能让人们在闲下来的时候看看花,品品诗歌,所以做有关花的网页是个不错的选择。同时,让人们分清楚春夏秋冬都各有什么典型的花。

第二章网站内容设计 1.1链接1标题:春の花 春天是生命的季节,在这个季节里,万物复苏。所以就找了虞美人,桃花,牡丹,以及海棠花来作为春天的代表。同时配有与这些花有关的诗句。 1.2 链接2标题:夏の花 夏天充满了激情与阳光,我找了兰花,荷花,百合花等来代表这个季节,色彩艳丽,十分醒目夺人。 1.3 链接3标题:秋の花 大丽花,菊花,月季和牡丹花都竞相出现在本网页,色彩缤纷,赏心悦目。 1.4 链接4标题:冬の花 蝴蝶兰,水仙,迎春花,梅花是冬季的代表,他们刻画了一副傲立冬天的坚强的姿态。

跑马灯VHDL课程设计 一、设计任务 控制8个led进行花式显示,设计四种显示模式: 1.从左到右逐个点亮led; 2.从右到左逐个点亮led; 3.从两边到中间逐个点亮led; 4.从中间到两边逐个点亮led; 四种模式循环切换,由复位键rst控制系统的运行与停止. 二、设计过程 根据系统设计要求,采用状态机进行设计,状态机具有四种状态,每种状态完成一种显示模式四种状态间使用case语句进行切换. 程序如下: library ieee; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_1164.all; entity pmd is port( clk, rst: in std_logic; y: buffer std_logic_vector(7 downto 0)); end pmd; architecture behave of pmd is type states is (state0, state1, state2, state3); signal state: states;

begin process (clk, rst) begin if rst='1' then y<="00000000" ; state <= state0; elsif (clk'event and clk='1') then case state is when state0 => if y="00000000" then y<="10000000";state <= state0; elsif y="10000000" then y<="01000000";state <= state0; elsif y="01000000" then y<="00100000";state <= state0; elsif y="00100000" then y<="00010000";state <= state0; elsif y="00010000" then y<="00001000";state <= state0; elsif y="00001000" then y<="00000100";state <= state0; elsif y="00000100" then y<="00000010";state <= state0; elsif y="00000010" then y<="00000001";state <= state1; end if; when state1 => if y="00000001" then y<="00000010";state <= state1; elsif y="00000010" then y<="00000100";state <= state1; elsif y="00000100" then y<="00001000";state <= state1; elsif y="00001000" then y<="00010000";state <= state1; elsif y="00010000" then y<="00100000";state <= state1; elsif y="00100000" then y<="01000000";state <= state1;

湖南科技大学 信息与电气工程学院 课程设计任务书 20 —20 学年第学期 专业:学号:姓名: 课程设计名称: 设计题目: 完成期限:自年月日至年月日共周设计依据、要求及主要内容(可另加附页): 指导教师(签字): 批准日期:年月日

目录 一、摘要 二、VHDL语言介绍 三、设计的目的 四、设计内容 五、电路工作原理 六、主要程序及仿真结果 七、对本次设计的体会和建议 八、参考文献

一、摘要 人类社会已进入到高度发达的信息化社会。信息化社会的发展离不开电子信息产品开发技术、产品品质的提高和进步。电子信息产品随着科学技术的进步,其电子器件和设计方法更新换代的速度日新月异。实现这种进步的主要原因就是电子设计技术和电子制造技术的发展,其核心就是电子设计自动化(EDA,Electronics Design Automation)技术,EDA技术的发展和推广应用又极大地推动了电子信息产业的发展。为保证电子系统设计的速度和质量,适应“第一时间推出产品”的设计要求,EDA技术正逐渐成为不可缺少的一项先进技术和重要工具。目前,在国内电子技术教学和产业界的技术推广中已形成“EDA热”,完全可以说,掌握EDA技术是电子信息类专业学生、工程技术人员所必备的基本能力和技能。EDA技术在电子系统设计领域越来越普及,本设计主要利用VHDL语言设计一个电子数字钟,它的计时周期为24小时,显示满刻度为24时59分59秒。总的程序由几个各具不同功能的单元模块程序拼接而成,其中包括分频程序模块、时分秒计数和设置程序模块、比较器程序模块、三输入数据选择器程序模块、译码显示程序模块和拼接程序模块。并且使用软件进行电路波形仿真。 关键词:数字钟EDA VHDL语言 二、VHDL语言介绍 1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言。自IEEE公布了VHDL的标准版本,IEEE-1076(简称87版)之后,各EDA公司相继推出了自己的VHDL 设计环境,或宣布自己的设计工具可以和VHDL接口。此后VHDL在电子设计领域得到了广泛的接受,并逐步取代了原有的非标准的硬件描述语言。1993年,IEEE对VHDL进行了修订,从更高的抽象层次和系统描述能力上扩展VHDL的内容,公布了新版本的VHDL,即IEEE标准的1076-1993版本,(简称93版)。现在,VHDL和Verilog作为IEEE的工业标准硬件描述语言,又得到众多EDA公司的支持,在电子工程领域,已成为事实上的通用硬件描述语言。有专家认为,在新的世纪中,VHDL于Verilog语言将承担起大部分的数字系统设计任务。VHDL主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可是部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。 三、设计的目的 本项实验通过六十进制计数器和数字钟的设计与仿真,学习VHDL语言及VHDL文本输入设计方法,编写六十进制计数器和数字钟源程序,应用VMAX+plusII软件进HDL文本输入设计与波形仿真。熟练地运用数字系统的设计方法进行数字系统设计,能进行较复杂的数字系统设计,按要求设计一个数字钟。 四、设计内容 1、60进制计数器计数器 60进制计数器计数器是一个用以实现计数功能的时序部件,它不仅可用来及脉冲数,还常用作数子系统的定时、分频和执行数字运算以及其它特定的逻辑功能。计数器种类很多。按

EDA 实验报告 ——多功能电子钟 姓名:张红义 班级:10级电科五班 学号:1008101143 指导老师:贾树恒

电子钟包括:主控模块,计时模块,闹钟模块,辅控模块,显示模块,蜂鸣器模块,分频器模块。 1.主控模块: 主要功能:控制整个系统,输出现在的状态,以及按键信息。 源代码: libraryieee; use ieee.std_logic_1164.all; useieee.std_logic_arith.all; useieee.std_logic_unsigned.all; entity mc is port(functionswitch,k,set,lightkey: in std_logic; chose21,setout: out std_logic; lightswitch:bufferstd_logic; modeout,kmodeout : out std_logic_vector(1 downto 0); setcs,setcm,setch,setas,setam,setah:outstd_logic); end mc; architecture work of mc is signalmode,kmode:std_logic_vector(1 downto 0); signal light,chose21buf:std_logic; signalsetcount:std_logic_vector(5 downto 0); begin process(functionswitch,k,set,lightkey) begin iffunctionswitch'event and functionswitch='1' then mode<=mode+'1'; end if; iflightkey'event and lightkey='1' then lightswitch<=not lightswitch; end if; if mode="01" thenchose21buf<='0'; else chose21buf<='1'; end if; ifk'event and k='1' then if mode="01" or mode="11" then kmode<=kmode+'1'; end if;end if; if set='1' then if mode = "01" then ifkmode="01" then setcount<="000001"; elsifkmode="10" thensetcount<="000010"; elsifkmode="11" then setcount<="000100";

网页制作实验报告 页制作实验报告 实验一:站点设置 一、实验目的及要求 本实例是经过“站点定义为”对话框中的“高级”选项卡创建一具新站点。 二、仪器用具 1、生均一台多媒体电脑,组建内部局域,同时接入国际互联。 2、安装windows xp操作系统;建立iis服务器环境,支持asp。 3、安装页三剑客(dreamweaver mx;flash mx;fireworks mx)等页设计软件; 三、实验原理 经过“站点定义为”对话框中的“高级”选项卡创建一具新站点。 四、实验办法与步骤 1)执行“站点\治理站点”命令,在弹出的“治理站点”对话框中单击“新建”按钮,在弹出的快捷菜单中挑选“站点”命令。 2)在弹出的“站点定义为”对话框中单击“高级”选项卡。 3)在“站点名称”文本框中输入站点名称,在“默认文件夹”文本框中挑选所创建的站点文件夹。在“默认图象文件夹”文本框中挑选存放图象的文件夹,完成后单击“确定”按钮,返回“治理站点”对话框。 4)在“治理站点”对话框中单击“完成”按钮,站点创建完毕。 五、实验结果 六、讨论与结论 实验开始之前要先建立一具根文件夹,在实验的过程中把站点存在自己建的文件夹里,如此才干使实验条理化,别至于在实验后寻别到自己的站点。在实验过程中会浮现一些选项,计算机普通会有默认的挑选,最后别要去更改,假如要更改要先充分了解清晰该选项的含义,以及它会造成的效果,否则会使实验的结果失真。实验前先熟悉好操作软件是做好该实验的关键。 实验二:页面图像设置 一、实验目的及要求: 本实例的目的是设置页面的背景图像,并创建鼠标经过图像。 二、仪器用具 1、生均一台多媒体电脑,组建内部局域,同时接入国际互联。 2、安装windows xp操作系统;建立iis服务器环境,支持asp。 3、安装页三剑客(dreamweaver mx;flash mx;fireworks mx)等页设计软件; 4、安装acdsee、photoshop等图形处理与制作软件; 5、其他一些动画与图形处理或制作软件。 三、实验原理 设置页面的背景图像,并创建鼠标经过图像。 四、实验办法与步骤 1) 在“页面属性”对话框中设置页面的背景图像。 2) 在页面文档中单击“”插入鼠标经过图像。 五、实验结果

本科实验报告 实验名称:数字系统设计与实验(软件部分)

实验一 QuartusII9.1软件的使用 一、实验目的: 1、通过实现书上的例子,掌握QUARTUSII9.1软件的使用. 2、编程实现3-8译码电路以掌握VHDL组合逻辑的设计以及QUARTUSII9.1软件的使用。 二、实验内容 1.十进制加法计数器的VHDL文本及仿真 功能图: VHDL文本: library IEEE; use IEEE.std_logic_1164.all; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity count10 is port(clk,load,en:in std_logic; data_in:in std_logic_vector(3 downto 0); seg:out std_logic_vector(6 downto 0)); end count10; architecture beha of count10 is signal qout:std_logic_vector(3 downto 0); signal q_temp:std_logic_vector(3 downto 0); begin process(clk,load) begin if(load='1')then q_temp<=data_in; elsif(clk'event and clk='1')then

if(en='0')then qout<=qout; elsif(qout="1001")then qout<="0000"; else qout<=qout+1; end if; q_temp<=qout; end if; end process; process(q_temp) begin case q_temp is when"0000"=>seg<="1000000"; when"0001"=>seg<="1111001"; when"0010"=>seg<="0100100"; when"0011"=>seg<="0110000"; when"0100"=>seg<="0011001"; when"0101"=>seg<="0010010"; when"0110"=>seg<="0000010"; when"0111"=>seg<="1111000"; when"1000"=>seg<="0000000"; when"1001"=>seg<="0010000"; when others=>seg<="0001000"; end case; end process; end beha; 功能仿真流程及结果: 全编译通过后,进行仿真 新建波形文件,在其中添加所需节点。将clk设置为时钟信号,将en设置为高电平,将load 设置为低电平,将data_in设置为想要预置的数值。 运行Generate Functional Simulation Nest List命令产生能仿真的网标文件。点击Start Simulation开始模拟仿真 仿真结果:

专用集成电路实验报告 13050Z01 1305024237 刘德文

实验一开发平台软件安装与认知实验 实验内容 1、本实验以三线八线译码器(LS74138)为例,在Xilinx ISE 9.2软件平台上完成设计 电路的VHDL文本输入、语法检查、编译、仿真、管脚分配和编程下载等操作。下载芯片选择Xilinx公司的CoolRunner II系列XC2C256-7PQ208作为目标仿真芯片。 2、用1中所设计的的三线八线译码器(LS74138)生成一个LS74138元件,在Xilinx ISE 9.2软件原理图设计平台上完成LS74138元件的调用,用原理图的方法设计三线八线译 码器(LS74138),实现编译,仿真,管脚分配和编程下载等操作。 源程序: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; -- Uncomment the following lines to use the declarations that are -- provided for instantiating Xilinx primitive components. --library UNISIM; --use UNISIM.VComponents.all; entity ls74138 is Port ( g1 : in std_logic; g2 : in std_logic; inp : in std_logic_vector(2 downto 0); y : out std_logic_vector(7 downto 0)); end ls74138; architecture Behavioral of ls74138 is begin process(g1,g2,inp) begin if((g1 and g2)='1') then case inp is when "000"=>y<="00000001"; when "001"=>y<="00000010";

北京理工大学珠海学院课程设计说明书 _2013_—_2014_学年第_1_学期 题目: 《Web应用开发课程设计》 学院:计算机学院 专业班级: 11级软件工程3班 学号: 110202031031 学生姓名:蒋征 指导教师:魏志军 成绩: 时间: 2014/1/5 2014年 1 月 5 日

摘要 本次作品是一个IT技术交流论坛,实现论坛的基本功能,注册、登录、发帖、浏览和回帖。 论坛分三个分板块,网页、C#和JA V A,纵向层次也是三层,主页、板块页和帖子页。网站使用JavaScript实现动态页面。 关键词:计算机技术交流社区JavaScript 网页 I

目录 摘要 ............................................. I 目录 ............................................. II 1 网站结构和布局 (1) 1.1 网站结构 (1) 1.1.1 总体结构 (1) 1.1.2 横向链接结构 (2) 1.2 页面布局 (3) 1.2.1 主页 (3) 1.2.2 分版页面 (6) 1.2.3 帖子页面 (6) 2 技术应用 (8) 2.1 逻辑设计 (8) 2.1.1 HTML和CSS设计 (8) 2.1.2 JavaScript设计 (10) 参考文献 (13) 心得体会 (14) I

教师评语 (15) 成绩评定表 (16) 课程设计答辩记录表 (17) II

1 网站结构 1.1主体结构 1.1.1总结构 网站是以技术交流社区为主题的论坛型网站。 这个网站是按树形结构设计如图1-1-1,页面种类共分三层,分别是主页,分主题页还有就是内容页。 主页连向三个分主题分区页面,分别是MTHL板块,C#板块还有就是JAVA 板块。 主题分区页面下面是内容帖子。 图1-1-1网页关系 1

课程设计 课程名称:交通灯设计. 学院:电气工程学院专业:测仪姓名:学号: 年级:级任课教师: 2012年 1月12日

电气工程学院 课程设计任务书 课题名称:交通灯控制器的设计 专业、班级:测控技术与仪器测仪班 指导教师: 20 年1 月2 日至20 年1 月13 日共2周 指导教师签名: 教研室主任签名: 分管院长签名:

一、课程设计内容 1.学习ALTERA公司的FPGA/CPLD的结构、特点和性能。 2.学习集成开发软件MAX+plus II/Quartus II的使用及设计过程。 3.熟悉EDA工具设计数字电路设计方法,掌握VHDL硬件描述语言设计方法。 4.根据给定题目设计数字电路,来加深对可编程逻辑器件的理解和掌握。 二、课程设计应完成的工作 1.在所选择器件内完成交通灯控制器的设计,要求设计完成后芯片具有交通灯控制器的全部功能、包括显示和操作接口。 2.交通灯控制器要求控制十字路口两道路的交通灯,两道路交替通行,每次通行时间可设定20——60秒之间,每个路口要求有前行、禁止、人行灯。 (根据实际设计进度考虑可以增加左右转向灯,等待和通行时间显示等)。 3.撰写设计说明书一份(不少于2000字),阐述系统的工作原理,软、硬件设计方法,重点阐述软件思路。说明书应包括封面、任务书、目录、摘要、正文、参考文献(资料)等内容,以及硬件电路综合图和软件程序清单等材料。 注:设计说明书题目字体用小三,黑体,正文字体用五号字,宋体,小标题用四号及小四,宋体,并用A4纸打印。 三、课程设计进程安排

四、设计资料及参考文献 1.康华光主编,《电子技术基础-数字部分》,高等教育出版社,1998。2.谭会生等主编,《EDA技术及应用》,西安电子科技大学出版社,2001 3.潘松等主编,《EDA技术实用教程》,科学出版社,2006 4.雷伏容主编,《VHDL电路设计》,清华大学出版社,2006 5.Charles H.Roth等著,《数字系统设计与VHDL》,电子工业出版社,2008 五、成绩评定综合以下因素: (1) 说明书及设计图纸的质量(占50%)。 (2) 独立工作能力及设计过程的表现(占30%)。 (3) 回答问题的情况(占20%)。 说明书和图纸部分评分分值分布如下:

EDA综合课程设计实验报告 题目:设计一个全双工UART电路院系:XXXX学院 学号:XXXXX 姓名:严XX 教师:林XX 时间:2012.06.02

1 课程设计的摘要原理 (2) 2 设计一个全双工UART电路,具体要求如下: (6) 3.UART设计 (7) 3.1 UART结构 (7) 3.2 UART的帧格式 (8) 4 UART的Verilog HDL语言设计 (9) 4.1 UART分频器 (9) 4.2UART发送模块 (10) 4.3 UART的接收模块 (14) 4.4 UART的硬件测试 (18) 5 课程设计总结 (19)

1摘要 UART协议是数据通信及控制系统中广泛使用的一种全双工串行数据传输协议,在实际工业生产中有时并不使用UART的全部功能。只需将其核心功能集成即可。波特率发生器、接收器和发送器是UART的三个核心功能模块,利用Vefilog-HDL语言对这三个功能模块进行描述并加以整合UART(即Universal AsynchronousReceiver Transmitter 通用异步收发器)是广泛使用的串行数据传输协议。UART允许在串行链路上进行全双工的通信。串行外设用到RS232-C异步串行接口,一般采用专用的集成电路即UART实现。如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL或Veriolog -HDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。 实际应用上,有时我们不需要使用完整的UART的功能和这些辅助功能。使用Verilog-HDL将所需要的UART的核心功能集成到FPGA/CPLD内部,就可以实现紧凑、稳定且可靠的UART数据传输。这样,既可以满足实际的应用,实现所要求的简单的通信和控制,又能够去除更多不需要的繁杂复杂的功能实现。 一、UART的原理 串行通信是指外部设备和计算机间使用一根数据线(另外需要地线,可能还需要控制线)进行数据传输的方式。数据在一根数据线上一位一位传输,每一位数据都占据一个固定的时间长度。与并行通信方式相比,串行通信方式的传输速度较慢,但这种通信方式使用的数据线少,在远距离通信中可以节约通信成本,因此得到了广泛的应用。 基本的UART只需要发送和接收两条数据线就可以完成数据的全双工通信,其基本功能是在发送端将控制器通过总线传过来的并行数据,以设定的格式,设定的频率串行地传输出去,并同时在接收端将串行接收到的数据,转换成相应的并行数据发送出去。UART的基本帧格式如图1所示。其中,起始位总是逻辑O状态,停止位总是逻辑l状态,其持续时间可选为1位、1.5位或2位,其数据位可为5、6、7、8位,校验位可根据需要选择奇校验位,偶校验位或无校验位。