嵌入式系统原理与设计

- 格式:docx

- 大小:22.31 KB

- 文档页数:16

学习并使用固件编程和嵌入式系统固件编程和嵌入式系统在现代科技社会中扮演着重要的角色。

从智能手机到智能家居设备再到汽车控制系统,固件编程和嵌入式系统无处不在。

本文将详细介绍固件编程和嵌入式系统的概念、原理、应用场景以及如何学习和使用这些技术。

一、固件编程和嵌入式系统概念1.1固件编程固件是嵌入在硬件设备中的软件,通常用于控制设备的操作。

固件编程是指为嵌入式系统开发和编写固件的过程。

固件可以是一系列的指令、程序或者数据,用于启动和运行硬件设备。

1.2嵌入式系统嵌入式系统是一种特殊的计算机系统,被嵌入到各种设备和系统中,用于控制设备的操作。

嵌入式系统通常包括一个或多个处理器、存储器和各种外设设备,可以是一个独立的系统或者是作为其他系统的一个组成部分。

嵌入式系统通常运行在实时操作系统上,能够对外界的实时事件做出快速反应。

二、固件编程和嵌入式系统原理2.1固件编程原理固件编程的实质是为特定的嵌入式硬件设计和编写软件,使得硬件能够按照设计要求进行工作。

固件编程通常需要了解硬件的架构和规格,以及掌握一定的编程技巧和知识。

固件编程可以使用各种编程语言,如C、C++、汇编语言等。

2.2嵌入式系统原理嵌入式系统是一种特殊的计算机系统,它需要具备以下基本原理:实时性、稳定性、高效性和可靠性。

嵌入式系统的设计需要考虑到硬件资源和功耗的限制,通常需要进行裁剪和优化。

嵌入式系统通常需要对外部的实时事件做出快速反应,因此需要使用实时操作系统,并具备良好的中断处理机制。

三、固件编程和嵌入式系统应用场景3.1智能手机智能手机是典型的嵌入式系统,它包含了各种传感器、通信设备和处理器,能够满足人们日常生活中的通信、娱乐和工作需求。

智能手机上的固件包括操作系统、驱动程序和应用程序,这些软件能够控制硬件设备的工作,实现各种功能。

3.2智能家居设备智能家居设备包括智能灯泡、智能插座、智能门锁等,它们通常采用嵌入式系统来控制和管理设备的操作。

嵌入式系统教案李震一、教案概述本教案旨在为广大嵌入式系统学习者提供一个全面、系统的学习路线,通过讲解基本概念、原理及实际应用,使学习者能够熟练掌握嵌入式系统的基本知识,具备实际项目开发能力。

本教案适用于嵌入式系统及相关专业的本科生、研究生和从业人员。

二、教学目标1. 理解嵌入式系统的概念、特点和应用领域;2. 掌握嵌入式系统硬件平台的基本组成;3. 熟悉嵌入式操作系统的基本原理及常用嵌入式操作系统;4. 学会嵌入式系统软件开发的基本方法;5. 能够运用所学知识分析和解决实际嵌入式系统问题。

三、教学内容第一章:嵌入式系统概述1.1 嵌入式系统的定义及特点1.2 嵌入式系统的应用领域1.3 嵌入式系统的发展趋势第二章:嵌入式系统硬件平台2.1 嵌入式处理器2.2 存储器2.3 输入输出接口2.4 嵌入式系统硬件设计方法第三章:嵌入式操作系统3.1 嵌入式操作系统的基本原理3.2 常用嵌入式操作系统简介3.3 嵌入式操作系统的选择与评估第四章:嵌入式系统软件开发4.1 嵌入式软件开发流程4.2 嵌入式编程语言4.3 嵌入式软件调试与测试第五章:嵌入式系统项目实践5.1 嵌入式系统项目开发流程5.2 基于嵌入式系统的应用案例分析5.3 项目实践案例讲解四、教学方法1. 采用讲授、讨论、实验相结合的方式进行教学;2. 使用实际案例进行分析,使学生更好地理解嵌入式系统的应用;3. 鼓励学生进行项目实践,提高实际动手能力;4. 定期进行课后作业和测试,检查学生学习效果。

五、教学资源1. 教材:《嵌入式系统原理与应用》等;2. 实验设备:嵌入式开发板、编程器、仿真器等;3. 网络资源:相关技术博客、论坛、学术论文等。

六、课程评估1. 课后作业:考察学生对课堂所学知识的理解和运用;2. 实验报告:评估学生在实验过程中的动手能力和问题解决能力;3. 课程论文:考察学生对嵌入式系统某一领域的深入研究;4. 期末考试:全面测试学生对本门课程的掌握程度。

单片机嵌入式系统原理及应用课后答案【篇一:单片机原理及嵌入式系统设计第一次作业习题】1、用8位二进制数表示出下列十进制数的补码:+65 、—115[+65]补:0100 0001[-115]补:1100 11012 、写出十进制数12.4用的bcd码和二进制数:bcd码:0001 0010.0100 二进制数:1100.0110011001100110(结果保留16位小数) 3 、当采用奇校验时,ascii码1000100和1000110的校验位d7应为何值?这2个代码所代表的字符是什么?答:分别为0和1,代表字符分别是d和f4、计算机由(运算器、控制器、存储器、输入设备、输出设备)五部分组成。

5、画出微机的组成框图,说明三总线的作用。

数据总线db:在控制总线的配合下传递cpu的输入/输出数地址总线ab:选择芯片或选择芯片中的单元,以便cpu通过控制总线让数据总线与该单元之间单独传输信息控制总线cb:配合数据总线与地址总线起作用,负责传递数据总线或地址总线的有效时刻和数据总线的传输方向等信息6、8位微机所表示的无符号数、带符号数、bcd码的范围分别是多少?答:8位微机所表示的无符号数范围:0~255带符号数范围:-128~+127bcd码范围:0~997、1001001b分别被看作补码、无符号数、ascii码、bcd码时,它所表示的十进制数或字符是什么?答:分别是补码73,无符号数73,bcd码498、举例说出单片机的用途。

答:比如马路上红路灯的时间控制;洗衣机的洗涤、甩干过程的自动控制等9、举例说明cpu执行指令的过程。

答:计算机每执行一条指令都可分为三个阶段进行。

即取指令、分析指令、执行指令。

根据程序计数器pc中的值从程序存储器读出现行指令,送到指令寄存器。

将指令寄存器中的指令操作码取出后进行译码,分析其指令性质。

如指令要求操作数,则寻找操作数地址。

计算机执行程序的过程实际上就是逐条指令地重复上述操作过程,直至遇到停机指令可循环等待指令。

嵌入式系统原理与应用实验指导书南航金城学院2013.2目录目录 (1)第一部分试验箱硬件结构 (2)第二部分实验 (11)实验一ADS1.2集成开发环境练习 (11)实验二汇编指令实验1 (17)实验三汇编指令实验2 (20)实验四汇编指令实验3 (23)实验五ARM微控制器工作模式实验 (28)实验六 C语言程序实验 (33)实验七 C语言调用汇编程序实验 (36)实验八GPIO输出控制实验 (39)实验九GPIO输入实验 (46)实验十外部中断实验 (50)实验十一UART通讯实验 (56)实验十二I2C接口实验 (64)实验十三定时器实验 (75)实验十四PWM DAC实验 (81)实验十五ADC实验 (87)实验十六RTC实验 (94)实验十七步进电机控制实验 (101)实验十八直流电机控制实验 (105)附录1 DeviceARM2410 专用工程模板 ..................................................... 错误!未定义书签。

第一部分试验箱硬件结构MagicARM2410教学实验开发平台是一款可使用μC/OS-II、Linux和WinCE操作系统、支持QT、MiniGUI图形系统、集众多功能于一身的ARM9教学实验开发平台。

采用Samsung公司的ARM920T内核的S3C2410A微处理器,扩展有充足的存储资源和众多典型的嵌入式系统接口。

MagicARM2410实验箱参考如图1.1所示。

图1.1 MagicARM2410实验箱外观图MagicARM2410实验箱功能框图如图1.2所示。

图1.2 MagicARM2410实验箱功能框图1.1 S3C2410A芯片简介S3C2410A是Samsung公司推出的16/32位RISC处理器(ARM920T内核),适用于手持设备、POS机、数字多媒体播放设备等等,具有低价格、低功耗、高性能等特点。

嵌入式系统原理与应用教学大纲与实现大纲嵌入式系统原理与应用教学大纲与实现大纲一、教学大纲(一)课程简介嵌入式系统是集计算机、微电子、通信和自动化控制等技术于一体的综合系统,广泛应用于航空航天、汽车电子、消费电子、工业控制等领域。

本课程旨在让学生了解嵌入式系统的基本原理、硬件架构、软件编程和实际应用,培养学生掌握嵌入式系统的设计和开发技能。

(二)教学目标1、掌握嵌入式系统的基本概念和原理,了解嵌入式系统的历史和发展趋势。

2、熟悉嵌入式系统的硬件组成,包括处理器、存储器、输入输出接口等,掌握嵌入式系统的硬件设计方法。

3、掌握嵌入式系统的软件编程,包括汇编语言、C语言等编程语言,了解嵌入式系统的启动过程和运行机制。

4、了解嵌入式系统的实际应用,包括工业控制、汽车电子、消费电子等领域,掌握嵌入式系统的应用设计和开发技能。

(三)教学内容1、嵌入式系统概述,包括基本概念、发展历史和发展趋势等。

2、嵌入式系统硬件组成,包括处理器、存储器、输入输出接口等。

3、嵌入式系统软件编程,包括汇编语言、C语言等编程语言,了解嵌入式系统的启动过程和运行机制。

4、嵌入式系统的实际应用,包括工业控制、汽车电子、消费电子等领域。

(四)教学方法1、理论教学:通过课堂讲解、案例分析等方式,让学生了解嵌入式系统的基本原理和应用。

2、实验教学:通过实验操作、编程实践等方式,让学生掌握嵌入式系统的硬件设计和软件编程技能。

3、项目实践:通过分组实践、项目开发等方式,让学生了解嵌入式系统的实际应用和开发过程。

(五)评估方式1、平时作业:布置相关作业,包括论文阅读、编程实践、实验报告等,以评估学生的学习情况和掌握程度。

2、期中考试:通过试卷或实操等方式,测试学生对课程内容的掌握情况。

3、期末考试:通过试卷或实操等方式,测试学生对课程整体的学习效果和掌握程度。

二、实现大纲(一)硬件设计1、选择合适的处理器,根据应用需求进行选型。

2、设计存储器,包括RAM和ROM,考虑容量和速度的需求。

嵌入式操作系统原理一、嵌入式操作系统的概念嵌入式操作系统是一种运行在嵌入式系统上的操作系统,其主要功能是管理和控制硬件资源,提供给应用程序一个良好的运行环境。

嵌入式操作系统通常包含任务调度、内存管理、设备驱动、文件系统等功能模块,以提供各种系统服务。

与一般计算机操作系统相比,嵌入式操作系统有着更高的实时性和可靠性需求。

二、嵌入式操作系统的特点1.高度实时性:嵌入式设备通常需要对外部环境做出及时响应,因此嵌入式操作系统需要具备高度实时性,能够准确响应和处理各种事件。

2.可嵌入性:嵌入式操作系统需要能够方便地移植到不同的硬件平台上,因此具备可嵌入性非常重要。

3.低功耗:嵌入式设备通常具有较低的功耗要求,嵌入式操作系统需要通过各种优化手段来降低系统的功耗。

4.小尺寸:嵌入式设备通常具有较小的存储容量,嵌入式操作系统需要具备小尺寸的特点,以节约存储空间。

三、嵌入式操作系统的功能模块1.任务调度:嵌入式操作系统需要具备任务调度的功能,能够合理分配系统资源,保证系统的实时性和可靠性。

常见的任务调度算法有优先级调度、轮询调度和抢占式调度等。

2.内存管理:嵌入式操作系统需要具备内存管理的功能,能够有效地管理系统的内存资源,包括动态内存分配和回收、内存保护和内存映射等。

3.设备驱动:嵌入式操作系统需要具备设备驱动的功能,能够管理和控制各种外部设备,包括传感器、执行器、通信接口等。

4.文件系统:嵌入式操作系统通常会包含文件系统的功能,能够提供对外部存储设备的读写访问,方便应用程序管理数据和配置文件。

5.网络支持:嵌入式操作系统通常需要具备网络支持的功能,能够提供网络通信的能力,包括TCP/IP协议栈、网络接口驱动等。

四、嵌入式操作系统的工作原理1.初始化:系统启动时,嵌入式操作系统会对硬件进行初始化,并设置系统的各种参数和配置,准备好系统运行的环境。

2.任务调度:嵌入式操作系统会根据任务的优先级和调度算法,决定将哪个任务分配给CPU执行,并根据实时性要求进行任务切换和调度。

一、 "嵌入式系统设计与应用" 作者:郁松该书主要介绍了嵌入式系统的基本原理和设计方法,涵盖了嵌入式系统的硬件设计、软件开发以及系统调试等方面。

书中以STM32为例,详细介绍了STM32的架构特点和应用实例,并结合具体的案例进行了深入讲解,对于STM32课程的开发与设计提供了丰富的参考资料。

二、 "STM32F4xx系列微控制器手册" 作者:STMicroelectronics 该手册是STMicroelectronics冠方出版的STM32F4xx系列微控制器的详细技术手册,内容涵盖了微控制器的基本特性、外设功能、时钟控制、中断管理、低功耗模式等方面的技术细节。

对于想要深入学习STM32F4系列微控制器的同学来说,这本手册是一本不可多得的参考书。

三、 "STM32单片机应用开发实战详解" 作者:刘炳勇该书是一本介绍STM32单片机应用开发的实战指南,书中涵盖了STM32的基本原理、应用实例、开发工具以及调试技巧等内容。

通过大量的实例和案例,帮助读者快速掌握STM32单片机的开发技术,并且对于学习STM32课程的同学来说,这本书是一个非常有用的参考资料。

四、 "基于STM32的嵌入式系统设计与开发" 作者:王明明该书是一本专门介绍基于STM32的嵌入式系统设计与开发的著作,内容包括了嵌入式系统的基本概念、硬件设计、嵌入式操作系统、外设驱动开发、通信接口、数据存储和网络连接等方面,对于想要系统地学习STM32课程设计与开发的同学来说,这本书是一个很好的参考书籍。

五、 "STM32单片机开发指南" 作者:孙苏民该书详细介绍了STM32单片机的各种外设和应用实例,内容涵盖了时钟控制、定时器、串口通信、中断控制、ADC/DAC、PWM输出、FLASH存储等方面。

通过多个实例的讲解,帮助读者深入理解STM32单片机的开发技术,并且对于STM32课程的设计与开发提供了丰富的参考案例。

1.嵌入式系统的定义:一般都认为嵌入式系统是以应用为中心,以计算机技术为根底,并且软硬件可裁剪,可满足应用系统对功能、可靠性、本钱、体积和功能有严格要求的专用计算机系统。

2.嵌入式系统的特征:〔1〕通常是面向特定应用的。

具有功耗低、体积小和集成度高等特点。

〔2〕硬件和软件都必须高效率地设计,量体裁衣,力争在同样的硅片面积上实现更高的性能,这样才能满足功能、可靠性和功耗的苛刻要求。

〔3〕实时系统操作支持。

〔4〕嵌入式系统与具体应用有机结合在一起,升级换代也同步进展。

〔5〕为了提高运行速度和系统可靠性,嵌入式系统中的软件一般固化在存储器芯片中。

3.ARM嵌入式微系统的应用:工业控制、网络系统、成像和平安产品、无线通信、消费类电子产品。

4.ARM嵌入式微处理器的特点:〔1〕体积小、低功耗、低本钱、高性能。

〔2〕支持Thumb〔16位〕/ARM〔32位〕双指令集,兼容8位/16位器件。

〔3〕使用单周期指令,指令简洁规整。

〔4〕大量使用存放器,大多数数据都在存放器中完成,只有加载/存储指令可以存储器,以提高指令的执行效率。

〔5〕寻址方式简单灵活,执行效率高。

〔6〕固定长度的指令格式。

5.嵌入式系统一般由嵌入式微处理器、外围硬件设备、嵌入式操作系统、用户软件构成。

2.哈佛体系构造的主要特点是将程序和数据存储在不同的存储空间。

3.嵌入式处理器主要有四种嵌入式微处理器〔EMPU〕、嵌入式微控制器〔MCU〕、嵌入式数字信号处理器〔DSP〕、嵌入式片上系统〔SoC)4.ARM7采用3级流水线构造,采用·诺依曼体系构造;ARM9采用5级流水线构造,采用哈佛体系构造。

5.ARM处理器共有37个32bit存放器,包括31个通用存放器和6个状态存放器。

6.ARM体系构造可以用2种方法存储字数据,即大端格式和小端格式。

7.ARM处理器既支持32位的ARM指令集又支持16位的THCMB指令集。

8.ARM处理器有7种工作模式,他们分为两大类特权模式、非特权模式。

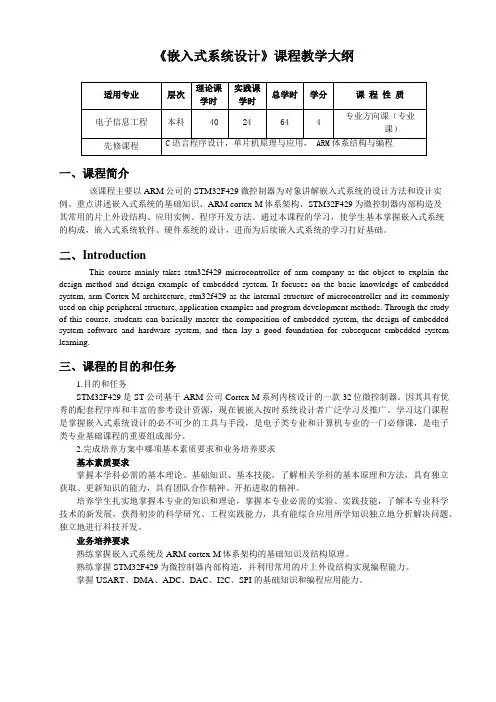

《嵌入式系统设计》课程教学大纲一、课程简介该课程主要以ARM公司的STM32F429微控制器为对象讲解嵌入式系统的设计方法和设计实例。

重点讲述嵌入式系统的基础知识、ARM cortex-M体系架构、STM32F429为微控制器内部构造及其常用的片上外设结构、应用实例、程序开发方法。

通过本课程的学习,使学生基本掌握嵌入式系统的构成,嵌入式系统软件、硬件系统的设计,进而为后续嵌入式系统的学习打好基础。

二、IntroductionThis course mainly takes stm32f429 microcontroller of arm company as the object to explain the design method and design example of embedded system. It focuses on the basic knowledge of embedded system, arm Cortex-M architecture, stm32f429 as the internal structure of microcontroller and its commonly used on-chip peripheral structure, application examples and program development methods. Through the study of this course, students can basically master the composition of embedded system, the design of embedded system software and hardware system, and then lay a good foundation for subsequent embedded system learning.三、课程的目的和任务1.目的和任务STM32F429是ST公司基于ARM公司Cortex-M系列内核设计的一款32位微控制器。

嵌入式系统原理及应用pdf嵌入式系统是一种特殊的计算机系统,它被设计用于控制特定的硬件设备或执行特定的任务。

随着技术的不断发展,嵌入式系统的应用范围也越来越广泛,如智能家居、医疗设备、汽车电子等领域。

为了更好地掌握嵌入式系统的原理和应用,学习《嵌入式系统原理及应用pdf》十分重要。

第一步:了解嵌入式系统的基础知识首先,嵌入式系统必须具备实时性、可靠性和可扩展性高等特点。

其次,嵌入式系统的应用需要根据不同的需求进行定制化设计。

此外,了解嵌入式系统中常见的单片机、处理器和操作系统架构等也是很有必要的。

第二步:了解嵌入式系统的设计流程嵌入式系统的设计流程一般分为需求分析、硬件设计、软件设计、系统测试和系统维护等步骤。

其中,需求分析是整个设计流程中最重要的一步,它需要充分考虑用户需求和系统的各种限制因素。

硬件设计则要对系统的各种硬件模块进行设计和测试,软件设计则需要根据硬件模块的需求进行软件开发。

最后,进行系统测试和维护等步骤,确保系统的稳定性和可靠性。

第三步:掌握嵌入式系统的编程语言和开发工具大多数嵌入式系统的编程语言是C/C++,而且其语法与普通的C/C++有所不同,需要进行一定的学习和了解。

此外,嵌入式系统的开发工具也有很多,如Keil、IAR、Eclipse等,需要根据实际需求选择合适的开发工具。

第四步:了解嵌入式系统的连接与通信技术连接是嵌入式系统最重要的一部分,它需要实现与外部设备的连接和数据通信。

通信技术则是指嵌入式系统之间进行通信所需要的技术,如CAN、TCP/IP等。

综上所述,学习《嵌入式系统原理及应用pdf》能够更好地了解嵌入式系统的基础知识、设计流程、编程语言和开发工具以及连接与通信技术等方面。

对于嵌入式系统的应用和开发有着非常实用的帮助。

《基于嵌入式系统的人脸考勤机的设计》篇一基于嵌入式系统的人脸考勤机设计一、引言随着科技的不断进步和人脸识别技术的发展,嵌入式系统的人脸考勤机作为一种新兴的生物识别技术已广泛应用于各种领域。

本篇文章旨在介绍基于嵌入式系统的人脸考勤机的设计原理、设计方法以及其在实际应用中的优势。

二、设计原理基于嵌入式系统的人脸考勤机主要依赖于人脸识别技术,通过摄像头捕捉到的人脸图像与数据库中的人脸信息进行比对,从而实现考勤功能。

其设计原理主要包括以下几个部分:1. 硬件部分:硬件部分主要包括嵌入式处理器、摄像头、存储器等。

嵌入式处理器负责运行系统程序,处理各种运算和指令;摄像头用于捕捉人脸图像;存储器用于存储人脸数据和其他相关信息。

2. 软件部分:软件部分包括人脸识别算法、操作系统、应用程序等。

人脸识别算法是实现人脸识别功能的核心,操作系统负责管理硬件资源和软件资源,应用程序则负责实现各种功能。

三、设计方法基于嵌入式系统的人脸考勤机的设计方法主要包括以下几个步骤:1. 需求分析:根据实际需求,确定人脸考勤机的功能、性能等要求。

2. 硬件设计:根据需求分析结果,选择合适的嵌入式处理器、摄像头、存储器等硬件设备,并设计电路原理图和PCB板图。

3. 软件设计:编写人脸识别算法、操作系统和应用程序等软件程序,并进行调试和优化。

4. 系统集成:将硬件和软件进行集成,进行系统测试和性能评估。

5. 实际应用:将设计好的人脸考勤机应用于实际场景中,进行实际测试和验证。

四、优势分析基于嵌入式系统的人脸考勤机具有以下优势:1. 高效性:人脸考勤机可以快速准确地识别员工身份,提高考勤效率。

2. 便捷性:员工无需携带任何证件,只需在摄像头前站立片刻即可完成考勤。

3. 安全性:采用生物识别技术,可以有效防止代打卡等作弊行为。

4. 可扩展性:可以与其他系统进行集成,实现更多的功能。

5. 维护方便:嵌入式系统具有较高的稳定性和可靠性,维护成本较低。

嵌入式系统原理与设计第一章嵌入式处理器1. 嵌入式系统概念,组成定义:以应用为主, 以计算机技术为基础, 软硬件可裁剪, 满足系统对功能 .. 、性能、可靠性、体积和功耗.. 有严格要求的计算机... 系统。

组成:硬件:处理器、存储器、 I / O设备、传感器软件:①系统软件②应用软件2. 嵌入式处理器分类,特点;嵌入式处理器与通用处理器区别;哈佛体系结构与风诺依曼体系结构;大端存储方式与小端存储方式。

分类:① MPU 微处理器。

一块芯片,没有集成外设接口。

内部主要由运算器,控制器,寄存器组成。

② MCU 微控制器(单片机) 。

一块芯片集成整个计算机系统。

③ EDSP 数字信号处理器。

特点:运算速度快,擅长于大量重复数据处理嵌入式处理器与通用计算机处理器的区别 :①嵌入式处理器种类繁多,功能多样②嵌入式处理器能力相对较弱,功耗低③嵌入式系统提供灵活的地址空间寻址能力④嵌入式系统集成了外设接口指令的存储结构①哈佛体系结构 :指令和数据分开存储————————(嵌入式存储结构)特征:在同一机器周期内指令和数据同时传输② 冯·诺依曼体系结构 :指令和数据共用一个存储器——(通用式存数结构)数据存储结构(多字节)例题:一个十六进制数 12345678(h ) ,在存储器中使用大端方式格式为(B ) 使用小端方式格式为(A )小端方式(A )大端方式 :低地址存高位小端方式 :低地址存低位处理器决定存储方式通用计算机(代表:X86系列处理器)采用小端方式存储嵌入式计算机(代表:ARM 系列处理器)两者皆可,需设置3. ARM 指令集的命名; ARM 内核的命名(包括命名规则) ARM 指令集命名:V1~V8ARM 内核命名:ARM7, ARM920T , XSCALE (Intel ) , Strog ARM, Cortex-A15 命名规则:ARM {x }{y }{z }{T }{D }{M }{I }{E }{J }{F }{S }{x }——系列(版本){y }——当数值为“ 2”时,表示 MMU (内存管理单元) {z }——当数值为“ 0”时,表示缓存 Cache {T }——支持 16位 Thumb 指令集 {D }——支持片上 Debug (调试) {M }——内嵌硬件乘法器大端方式(B ){I }——内嵌 ICE (在线仿真器)——支持片上断点及调试点{E }——支持 DSP 指令{J }——支持 Jazzle 技术{F }——支持硬件浮点{S }——可综合版本4. JTAG 的概念及作用。

概念:(Joint Test Action Group)联合测试行动小组→检测 PCB 和 IC 芯片标准。

作用:(1)硬件基本功能测试读写(读写处理器内部寄存器 /读写处理器外部存储单元 /设置 GPIO 引脚状态)(2)软件下载:将运行代码下载到目标机 RAM 中(3)软件调试:设置断点和调试点(4) FLASH 烧写:将运行最终代码烧写到 FLASH 存储器中。

5. 什么是 GPIO , S3C2410/2440 GPIO的分组及个数; GPxCON 寄存器, GPxDAT 寄存器, GPxUP 寄存器的功能, 各位含义和用法; 什么是上拉电阻和下拉电阻; 例:使 4个 LED 小灯的 LED1亮起来(会画电路图) ;例:使用按键控制 LED (会画电路图) 。

GPIO 概念:(General Purpose I/O Ports)通用输入 /输出接口,即处理器引脚。

S3C2410共有 117个引脚, 可分成 A —— H 共 8个组, (GPA , GPB , … GPH 组) S3C2440共有 130个引脚,可分成 A —— J 共 9个组, (GPA ,GPB , … , GPH , GPJ 组)① GPxCON 寄存器(控制寄存器)——设置引脚功能→ GPACON (A 组有 23根引脚,一位对应一个引脚,共 32位,拿出 0~22位,其余没用)(若某一位是) 0:(代表该位的引脚是一个)输出引脚1:地址引脚→ GPBCON —— GPH/JCON(用法一致,两位设置一个引脚)00:输入引脚01:输出引脚10:特殊引脚11:保留不用GPBCON 31 1 0② GPxDAT 寄存器(数据寄存器)——设置引脚状态及读取引脚状态若某一位对应的是输出引脚,写此寄存器相应位可令引脚输出高 /低电平。

若某一位对应的是输入引脚,读取此寄存器可知相应引脚电平状态。

GPBDAT31 1③ GpxUP ——上拉电阻寄存器0:相应引脚使用内部上拉电阻 1:相应引脚不适用内部上拉电阻上拉电阻:加在引脚和高电位间的电阻。

下拉电阻:加在引脚和接地间的电阻。

上拉电阻Vcc (高电平) 接地端(S3C2410大部分配有上拉电阻,可使用,也可不使用) ① 例:使 4个 LED 小灯中的 LED1发亮GPBCON : 31 17 16 15 14 13 12 11 10 … 3 2 1 0…GPB8 GPB7 GPB6 GPB5GPB1GPB0GPBDAT : 31 8 7 6 5 … 3 2 1 0…GPB8 GPB7 GPB6 GPB5GPBUP : 不使用上拉电阻程序:#define GPBCON(*(Volatile unsigned long *)0x56000010) #define GPBDAT(*(Volatile unsigned long *)0x56000014) #define GPB5_OUT(1<<(5*2)) #define GPB6_OUT(1<<(6*2)) #define GPB7_OUT(1<<(7*2)) #defineGPB8_OUT(1<<(8*2))int main(){GPBCON&=~(0x0003FC00) ;GPBCON|=0x00015400;GPBDAT&=~(0x000001E0) ;GPBDAT|=0x000001C0;return 0;}②使用按键控制 LEDK1闭合, GPB11低电平K1断开, GPB11高电平GPGDAT11位,当 GPB11为 0时,低电平;当 GPG11为 1时,高电平。

考试肯定考的 20分编程题! ! !S3C2410#define GPBCON(*(volatile unsigned long*)0x56000010) #define GPBDAT(*(volatile unsigned long*)0x56000014) #define GPGCON(*(volatile unsigned long*)0x56000050) #define GPGDAT(*(volatile unsignedlong*)0x56000054) #define GPFCON(*(volatile unsigned long*)0x56000060) #define GPFDAT(*(volatile unsigned long*)0x56000064) #define GPB5_OUT1<<(5*2) #define GPB6_OUT 1<<(6*2) #define GPB7_OUT 1<<(7*2) #define GPB8_OUT 1<<(8*2)K4#define GPG11_IN ~(3<<(11*2))#define GPG3_IN ~(3<<(3*2))#define GPF2_IN ~(3<<(2*2))#define GPF0_IN ~(3<<(0*2))int main(){unsigned long dwDat;GPBCON&=~(0x0003FC00) ;GPBCON|=0x00015400;GPGCON&=~(0x00C000C0) ;GPGCON|=0x00000000;GPFCON&=~(0x00000033);GPFCON|=0x00000000;while(1){dwDat=GPGDAT;if(dwDat&(1<<11)) //如果表达式为真值, 表示 K1没被按下, 与 GPG11相连GPBDAT|=(1<<5); //LED1熄灭elseGPBDAT&=~(1<<5); //LED1点亮if(dwDat&(1<<3)) //如果表达式为真值,表示 K2没被按下 , 与 GPG3相连GPBDAT|=(1<<6); //LED2熄灭elseGPBDAT&=~(1<<6); //LED2点亮if(dwDat&(1<<2)) //如果表达式为真值,表示 K3没被按下 , 与 GPF2相连GPBDAT|=(1<<7); //LED3熄灭elseGPBDAT&=~(1<<7); //LED3点亮if(dwDat&(1<<0)) //如果表达式为真值,表示 K4没被按下 , 与 GPF0相连GPBDAT|=(1<<8); //LED4熄灭 elseGPBDAT&=~(1<<8); //LED4点亮 } return 0;}第二章嵌入式存储器1. 嵌入式存储器的分类,特点。

2.SRAM 位存储电路的存储原理; DRAM 位存储电路的存储原理; DRAM 的优缺点; SDRAM 芯片按 BANK 划分的优点; SDRAM 读写操作; SDRAM 突发传输作用;根据 CL , BL 的值绘制突发传输时序图。

SRAM 存储电路:写数据 :选通信号为高电平, T 5, T6导通如果写 1, D 发出高电平, D#发低电平当选通信号失效, T 1截止, T 2导通, T 3, T 4做负载使用一、分类SRAM :静态随即存储器 (cache ) 存取速度会计, 容量小,造价高,不需刷新DRAM :动态随即存储器(内存) 造价低,存取速度稍慢,存储单元需刷新SDRAM :同步动态随机存储器步时钟 (上升沿或下降沿存取数据)DDR SDRAM:(Dual Data Rate 双倍速率) (上升沿和下降沿都可以读取数据) FLASH :闪存(外存) 速度慢,容量大,造价低NAND FLASH:与非闪存东芝数据NOR FLASH:或非闪存Intel 代码T 4的内阻 >>T2内阻T 3的内阻 >>T1内阻Q 为高电平,由 Vcc 提供Q#为低电平,由接地端提供写 1以及读取同理。