数控增益放大器

一、设计任务和功能要求

1、任务

选用合适的D/A转换器设计一个数控增益放大器电路。

2、设计要求

1. 所设计的数控放大器增益调节范围:8~16,相对误差小于1%;

2. 数控增益放大器所需要的控制数字量由单片机产生,五按键控制电路

由不带锁按键产生五路负脉冲;

3. 设计四路高低电平信号指示电路,电路留有相应的信号输入接口;

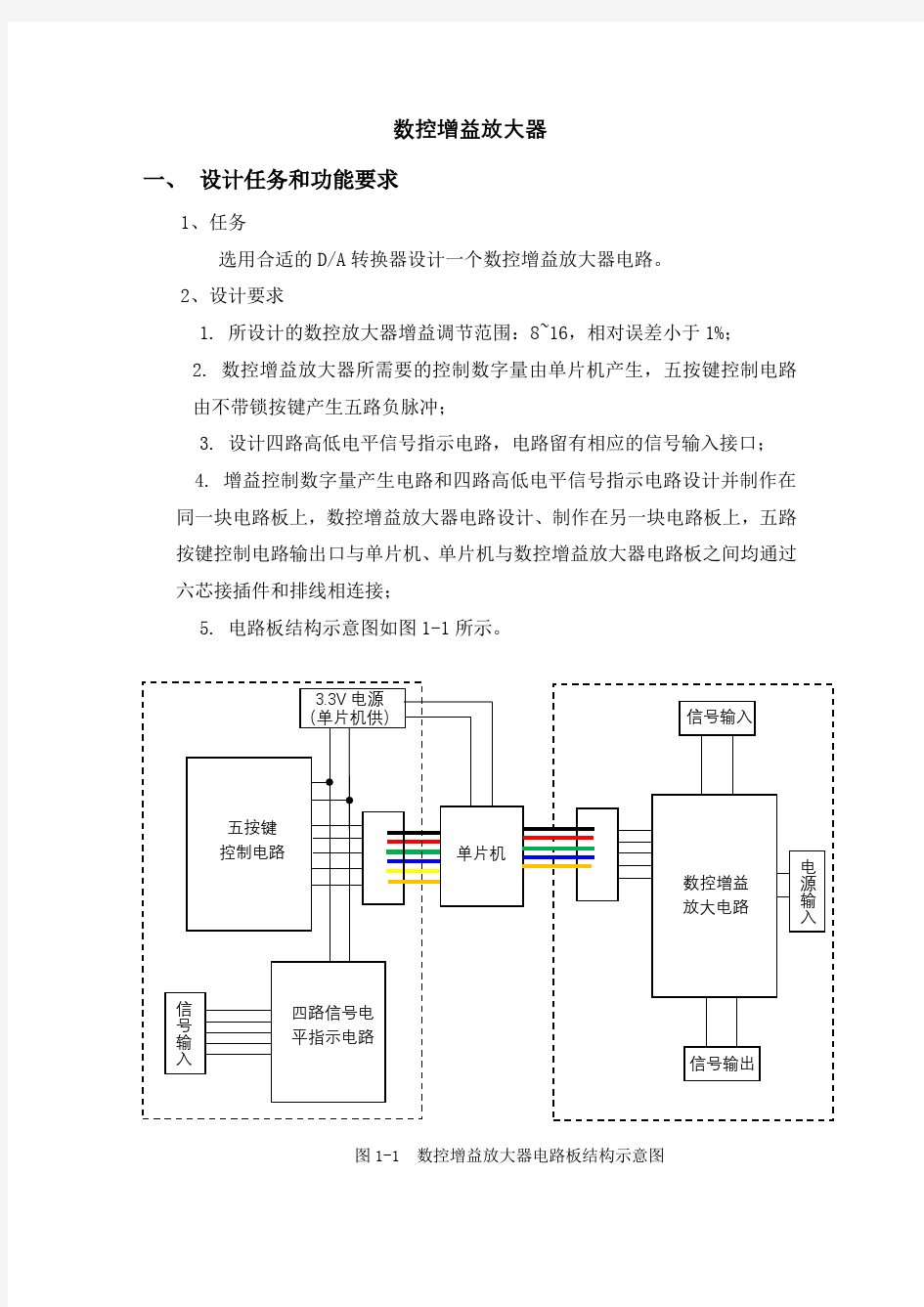

4. 增益控制数字量产生电路和四路高低电平信号指示电路设计并制作在

同一块电路板上,数控增益放大器电路设计、制作在另一块电路板上,五路按键控制电路输出口与单片机、单片机与数控增益放大器电路板之间均通过六芯接插件和排线相连接;

5. 电路板结构示意图如图1-1所示。

图1-1 数控增益放大器电路板结构示意图

二、摘要

数控增益放大器是集计算机技术、电子技术、数控技术为一体的机电一体化高科技产品,具有安全性高,使用方便等优点。

关键词:程控放大器、单片机、DAC0832、增益放大。

三、设计原理概述

数控增益放大器所需要的控制数字量由单片机产生,五按键控制电路由不带锁按键产生五路负脉冲提供给单片机,使单片机输出信号给DAC0832来控制数控增益放大电路的放大倍数。其系统框图如图3-1。

图3-1 数控增益放大器系统框图

四、电路方案论证

1、数控增益放大电路

方案1:如图4-1.1,使用DAC0832转换器,该电路特点:DAC0832采用二次缓冲方式,这样可以在输出的同时采集下一个数据,从而提高转换速度,更重要的是能够在多个转换器同时工作时实现多通道D/A的同时转换。

图4-1.1 DAC0832转换器

方案2:如图4-1.2,采用AD7533转换器,此电路特点:电路中AD7533内部的反馈电阻R为放大电路的输入电阻,而由数字量控制的T形电阻网络是它的反馈电阻。当输入数字量变化时,倒T形电阻网络的等效电阻也随之变化。这样,在输入电阻一定的情况下,随着电阻网络等效电阻变化,反相比例放大器的的增益也就随之改变。

图4-1.2 AD7533转换器

综上所述,采用DAC0832转换器做为增益放大电路。

五、系统原理总图

图5-2 四路指示电路

图5-3 程控放大电路

5%

六、单片机程序与测试

1、单片机程序:

#include

void main(void)

{

WDTCTL = WDTPW + WDTHOLD;

P1DIR &= 0x00 ;

P2DIR |= 0xFF ;

P2OUT &= 0x00 ;

P1IN |= 0xFF;

while(1)

{

if((P1IN&BIT1)==0)

{

__delay_cycles(500000);

if(P1IN&BIT1)

P2OUT ^=BIT1;

}

if((P1IN&BIT2)==0)

{

__delay_cycles(500000);

if(P1IN&BIT2)

P2OUT ^=BIT2;

}

if((P1IN&BIT3)==0)

{

__delay_cycles(500000);

if(P1IN&BIT3)

P2OUT ^=BIT3;

}

if((P1IN&BIT4)==0)

{

__delay_cycles(500000);

if(P1IN&BIT4)

P2OUT ^=BIT4;

}

}

}

2测试

表2-1 输入峰峰值:100mV

图6-1 输入信号

图6-2

图6-3

图6-4

七、元器件清单

八、参考文献

1、康华光;电子技术基础模拟部分;华中科技大学电子技术课程组编;第六版; 北京;高等教育出版社;2013.12

2、康华光;电子技术基础数字部分;华中科技大学电子技术课程组编;第六版; 北京;高等教育出版社;2013.12

目录 1. 设计指标 (1) 2. 运算放大器主体结构的选择 (1) 3. 共模反馈电路(CMFB)的选择 (1) 4. 运算放大器设计策略 (2) 5. 手工设计过程 (2) 5.1 运算放大器参数的确定 (2) 5.1.1 补偿电容Cc和调零电阻的确定 (2) 5.1.2 确定输入级尾电流I0的大小和M0的宽长比 (3) 5.1.3 确定M1和M2的宽长比 (3) 5.1.4确定M5、M6的宽长比 (3) 5.1.5 确定M7、M8、M9和M10宽长比 (3) 5.1.6 确定M3和M4宽长比 (3) 5.1.7 确定M11、M12、M13和M14的宽长比 (4) 5.1.8 确定偏置电压 (4) 5.2 CMFB参数的确定 (4) 6. HSPICE仿真 (5) 6.1 直流参数仿真 (5) 6.1.1共模输入电压范围(ICMR) (5) 6.1.2 输出电压范围测试 (6) 6.2 交流参数仿真 (6) 6.2.1 开环增益、增益带宽积、相位裕度、增益裕度的仿真 (6) 6.2.2 共模抑制比(CMRR)的仿真 (7) 6.2.3电源抑制比(PSRR)的仿真 (8) 6.2.4输出阻抗仿真 (9) 6.3瞬态参数仿真 (10) 6.3.1 转换速率(SR) (10) 6.3.2 输入正弦信号的仿真 (11) 7. 设计总结 (11) 附录(整体电路的网表文件) (12)

采用折叠式结构的两级全差分运算放大器的设计 1. 设计指标 5000/ 2.5 2.551010/21~22v DD SS L out dias A V V V V V V GB MHz C pF SR V s V V ICMR V P mW μ>==?== >=±=?≤的范围 2. 运算放大器主体结构的选择 图1 折叠式共源共栅两级运算放大器 运算放大器有很多种结构,按照不同的标准有不同的分类。从电路结构来看, 有套筒 式共源共栅、折叠式共源共栅、增益提高式和一般的两级运算放大器等。本设计采用的是如图1所示的折叠式共源共栅两级运算放大器,采用折叠式结构可以获得很高的共模输入电压范围,与套筒式的结构相比,可以获得更大的输出电压摆幅。 由于折叠式共源共栅放大器输出电压增益没有套筒式结构电压增益那么高,因此为了得到更高的增益,本设计采用了两级运放结构,第一级由M0-M10构成折叠式共源共栅结构,第二级由M11-M14构成共源级结构,既可以提高电压的增益,又可以获得比第一级更高的输出电压摆幅。 为了保证运放在闭环状态下能稳定的工作,本设计通过米勒补偿电容Cc 和调零电阻Rz 对运放进行补偿,提高相位裕量! 另外,本文设计的是全差分运算放大器,与单端输出的运算放大器相比较,可以获得更高的共模抑制比,避免镜像极点及输出电压摆幅。 3. 共模反馈电路(CMFB )的选择 由于采用的是高增益的全差分结构,输出共模电平对器件的特性和失配相当敏感,而且不能通过差动反馈来达到稳定,因此,必须增加共模反馈电路(CMFB )来检测两个输出端

新型多路数控增益放大器 信息来源: 维库开发网发布时间:2009年12月30日 在数字与模拟接口电路中,通常采用放大器和多路开关来完成信号的放大与通道的选择,常用芯片有LF147、CA3140等,多通道选择开关有AD7501等。目前尚没有具有多路放大的专用模拟接口芯片。采用传统的技术方案用做A/D转换器前端接口电路,需要对放大器电路进行增益调节,改变增益控制电阻的阻值达到放大量的变化,当遇到具有+/-极性的输入信号时,处理起来更加繁锁。另外,在小信号的状态下,如采用常用的8位A/D转换器,一个5 V(满量程)的输入信号的分辨率为1/256,一个2.5 V输入信号通过放大至满量程后,它的分辨率将提高1倍,一个小于1/256信号如直接采用A/D转换器,该信号则已无分辨率可言。这样必需通过放大器进行预放大。 开发研制的基于微组装工艺的集成化高精度多路数控增益放大器(型号为 DG8256),是用MCM(多芯片组装)技术实现的。在极性处理方面采用绝对值电路使得输出信号为正值,采用8位A/D转换器时,对小信号均可通过数字控制的方法进行256级增益控制,从而实现了高精度的连续放大。低频高精度A/D转换器的理想前级,放大器具有8个通道的信号输入。基于MCM技术的多路数控增益放大器体积小、重量轻,适用于小型微机处理系统中模拟接口电路,而且放大器具有良好的温度特性,适用于军事、商业、工业、民用领域。 1主要技术参数 开发该接口模块源于某雷达发射设备的控制与保护电路的研制。电路需要模拟接口电路,与以往的雷达发射机控制与保护电路不同的是对体积要求更高,要求在很小的体积下完成复杂的信号采样与控制。这就启发了我们开发研制该模块。模块具备8个通道信号输入,每个通道的信号具有正负信号输入能力,模块末级输出为正值输出,通道选择采用TTL信号控制,信号具有增益可控的能力,增益控制采用TTL电平控制。模块的主要技术参数如下: a)供电电源:±12 V; b)输入信号幅度:-5 V~+5 V; c)输入通道数:3位数控(S0~S2),8通道信号输入(Vin0~Vin7); d)输出信号幅度:0~+5 V; e)输入信号频率:i≥5 kHz; f)放大可控增益:-16 dB~+16 dB; g)放大器线性度:≤2%; h)增益调节:8位数控(G0~G7),256级线性; i)输入阻抗:≥510 kΩ; j)输出电流:≥2 mA; k)工作温度:-55℃~+85 ℃; 1)封装:DIP(双列直插式封装)24脚; m)外型尺寸:长×宽×高为33 mm×21 mm×6.0 mm: n)镀金引脚:引脚长5 mm。 2功能特性与电路原理 2.1功能特性

全差分运算放大器设计 岳生生(200403020126) 一、设计指标 以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下: ?直流增益:>80dB ?单位增益带宽:>50MHz ?负载电容:=5pF ?相位裕量:>60度 ?增益裕量:>12dB ?差分压摆率:>200V/us ?共模电压:2.5V (VDD=5V) ?差分输入摆幅:>±4V 二、运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT N V 之和小于0.5V ,输出端的所有PMOS 管的,DSAT P V 之和也必须小于0.5V 。对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该 要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 三、性能指标分析 1、 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 11 1357 113 51 3 57 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=-+ 第二级增益 9 2 2 9112 9 9 11 ()m o o o m m o o g g G A R r r g g =-=-=- + 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r = = ≥++ 2、 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR :

一.差分信号的特点: 图1 差分信号 1.差分信号是一对幅度相同,相位相反的信号。差分信号会以一个共模信号 V ocm 为中心,如图1所示。差分信号包含差模信号和公模信号两个部分, 差模与公模的定义分别为:Vdiff=(V out+-V out- )/2,Vocm=(V out+ +V out- )/2。 2.差分信号的摆幅是单端信号的两倍。如图1,绿色表示的是单端信号的摆 幅,而蓝色表示的是差分信号的摆幅。所以在同样电源电压供电条件下,使用差分信号增大了系统的动态范围。 3.差分信号可以抑制共模噪声,提高系统的信噪比。In a differential system, keeping the transport wires as close as possible to one another makes the noise coupled into the conductors appear as a common-mode voltage. Noise that is common to the power supplies will also appear as a common-mode voltage. Since the differential amplifier rejects common-mode voltages, the system is more immune to external noise. 4.差分信号可以抑制偶次谐波,提高系统的总谐波失真性能。 Differential systems provide increased immunity to external noise, reduced even-order harmonics, and twice the dynamic range when compared to signal-ended system. 二.分析差分放大器电路 图2.差分放大器电路分析图

程控放大器的设计与实现 摘要 本文介绍了一种可通过程序改变增益的放大器。它与ADC相配合,可以自动适应大范围变化的模拟信号电平。系统以89S51单片机作微处理器,运用NE5532芯片组成运放电路,采用CD4052芯片担任增益切换开关,通过软件控制开关的闭合或断开来达到改变电路的增益。 文章首先对系统方案进行论证,然后对硬件电路和软件设计进行了说明,最后重点阐述了系统的调试过程,并且对调试过程中遇到的问题以及解决方案进行了详细说明。该系统设计达到了预期要求,实现了最大放大60db的目的。 关键词 程控放大器;运算器放大器;单片机;增益 The Design and Realization of Program-Controll Amplifier Abstract This article introduces a amplifier which changes the gain through the software. It coordinates with ADC and adapts the simulated signal level with wide range change automatically. The system uses the 89s51 SCM as the core. The NE5532 chip composes the operational circuit and the CD4052 chip composes the gain switch. The gain of the circuit is changed by software which can control switch closed or disconnect. The article first demonstrates the system plan, then introduces the hardware and the software, finally explains the debugging process of the system with emphasis. It also especially analogizes the problem in the debugging process and the resolutions. This system design has achieved anticipative request and realized enlarged 60db most greatly the goal. Key words Program-controlled amplifier; operational Amplifier; SCM; gain

增益可控射频放大器 一、系统方案 1、方案分析与比较 方案1:以高增益精度的压控VGA芯片AD603作为核心放大器,但频率再高时,效果很不理想,并且在级联时,很容易产生自激现象。 方案2:采用宽带可变增益FET放大电路,其缺点是增益步进控制难以实现,高频时频率的稳定性不好,在75MHz~108MHZ增益起伏较大,不能满足要求。 方案3:采用射频放大器AD8321+衰减器HMC472+放大器AD809的形式。第一级为AD8321三级级联,使增益倍数达到52dB。考虑到输入信号为高频信号,随着频率增加,幅度衰减增大,所以第二级加上可设置分贝衰减器,衰减器随着频率升高衰减效果明显,通过这样的方式使输出幅度稳定。但考虑实际拟合后,增益会稍微下降,最后通过第三级放大器将增益值稳定至输入增益。AD8321是一款低成本、数字控制式可变增益放大器,所需输出增益由8比特串行字决定,方便STM32程控,输出增益范围为-27.4dB~26dB,增益变化为0.75 dB/LSB。具有极低输出噪声电平,上行带宽高达235 MHz(最小增益),符合题目200MHz要求。 综上考虑,AD8321具有频带宽、噪声低、增益可编程,易于与STM32进行串行通信等优点,选用方案3。 2、系统整体设计 根据题目要求,本系统主要由:键盘控制,液晶显示、语音播报模块,三级AD8321级联,衰减器,第二级放大模块,滤波器电路,电压转换电路组成。总体设计框图如图一所示:

图一 二、理论分析与计算 1、射频放大器设计 按照本设计要求,带宽为40MHz~200MHz ,电压增益为52dB 。所以采用AD8321三级级联的方式。8321最大增益为26dB ,理论上总增益=26+26+26=78dB ,符合设计要求。并且阻抗之间已经匹配,级联时无需额外电阻网络。为了防止高频走线间干扰,采用贴片式电路,原理图是根据器件手册的应用电路来设计。 2、频带内增益起伏控制 造成通频带内增益起伏的原因有很多,包括带内波动、运放幅频响应不平坦及供电电源电压不稳等,为了降低增益波动,在三级放大输出加上衰减器,利用衰减器HMC472随着频率增高衰减效果明显的特性,使频带内增益起伏得到控制。对幅度衰减特性进行补偿,最后再加一级AD809,将增益稳定。 3、射频放大器稳定性 由于本系统的处理对象是高频信号,所以整个系统对噪声的处理要求很高才能保证射频放大器的稳定性。噪声来源包括:电源、外界环境、级间干扰,以及走线间相互干扰等。针对不同的噪声,采用了不同的处理措施: (1)电源干扰:使用电感、电容构成滤波电路,能有效滤除纹波。在每个运放的电源引脚并联去耦电容。 (2)外界环境干扰,为了防止外界干扰,可以将电源线和地线加宽,并且在制PCB 板时加以覆铜;对自动增益级及功率放大级增加屏蔽罩,提高其抗干扰性能。 (3)级间干扰,各级之间,采用了高低频电容来滤除高低频噪声。 DC-DC (9V ) DC-DC (5V ) AD8321 AD8321 AD8321 STM32 液晶显示 键盘 直流稳压电源 输入 输出 语音播报 AD809 滤波器 衰减器

通用可变增益放大器(B题) 摘要 本着简单、准确、可靠、通用的原则,采用了分级设计匹配互连的思想。本放大器系统分为前级放大部分、增益放大与控制电路部分、档位控制部分、后级稳压输出部分四部分。全系统采用单一的模拟电路方式,通过前级放大部分获得所需输入电压、输入阻抗等重要参数;通过拨码开关连接的反馈电阻进行精密全局控制,获得20dB至40dB之间分辨力不低于0.1%的可变增益范围;通过档位控制部分电路实现四个档位增益值转换,在衰减电路的作用下得到三个档位的增益值,即—20dB至0、0至20dB、20dB至40dB;最后通过后级稳压输出部分获得输出幅度不低于±8V的输出电压,此部分电路包括抑制零点漂移的调零电路。通过验证,本系统可以对输出电压数值的漂移,零点漂移等不良影响进行有效地抑制和降低。通过全面的调试和测量,使得本系统基本满足题目的基本部分和发挥部分的要求并融入了自己的创新思想,设计出了一个可控范围大、输出幅度高、稳定性好、抗干扰能力强、幅频特性好的通用可变增益放大器。

目录 摘要 (2) 目录 (3) 一、方案论证与比较 (4) 1、前级放大部分 (4) 2、增益放大与衰减控制电路 (4) 3、后级电压输出 (5) 二、系统设计 (5) 1、总体设计思路 (5) 2、主要电路原理分析与计算 (6) 2.1、前级放大电路 (6) 2.2、增益放大与控制电路 (6) 2.3、档位控制电路 (7) 2.4、电压输出电路 (7) 三、系统测试方法与测试数据 (8) 1、测试仪器 (8) 2、测试方法与测试数据 (8) 2.1、测前级放大电路 (8) 2.2、测增益放大与控制电路 (8) 2.3、各级电路调节好后,进行测量和详细记录 (8) 3、测试结果分析 (9) 3.1、测试结果分析 (9) 3.2、误差分析 (9) 3.3、测试心得 (10) 四、总结 (10)

全差分套筒式运算放大器设计 1、设计内容 本设计基于经典的全差分套筒式结构设计了一个高增益运算放大器,采用镜像电流源作为偏置。为了获得更大的输出摆幅及差模增益,电路采用了共模反馈及二级放大电路。 本设计所用到的器件均采用SMIC 0.18μm的工艺库。 2、设计要求及工艺参数 本设计要实现的各项指标和相关的工艺参数如表1和表2所示:

3、放大器设计 3.1 全差分套筒式放大器拓扑结构与实际电路 图1 全差分套筒式放大器拓扑结构 图2 最终电路图

3.2 设计过程 在图1中,Mb1和M9组成的恒流源为差放提供恒流源偏置,且M1,M2完全一样,即两管子所有参数均相同。Mb2、M7和M8构成了镜像电流源,M5、M6和M7、M8构成了共源共栅电流源,M1、M2、M3、M4构成了共源共栅结构,可以显著提高输出阻抗,提高放大倍数(把M3的输出阻抗提高至原来的(gm3 + gmb3)ro2倍。但同时降低了输出电压摆幅。为了提高摆幅,控制增益,在套筒式差分放大器输出端增加二级放大。 本设计中功率上限为10mW,可以给一级放大电路分配3mA的电流。设计要求摆幅为3V,所以图1中M1、M3、M5、M9的过驱动电压之和不大于1.8-3/2=0.3V。我们可以平均分配每个管子的过驱动电压。根据漏电计算流公式(1)(考虑沟道长度调制效应),可以计算出每个管子的宽长比。 I D=1 2μn C ox W L (V GS?V TH)2(1+λV DS)(1) 其中,C ox等于ε/t ox,μn和t ox可以从工艺库中查找。 4、仿真结果 经过调试优化之后的仿真结果如以下各图所示: 图3 增益及相位裕度 从图中可以看出,本设计的低频增益达到了74.25dB,达到了预期要求。3dB 带宽为35kHz左右,比较小,可见设计还有改进的余地。 当CL为2pF时,相位裕度: PM=180°+∠βH(ω)=180°?125.5°=54.5° 电源电压为1.8V时,输出摆幅如下图所示,达到了3V。

全差分运算放大器设计 岳生生(0126) 一、设计指标 以上华CMOS 工艺设计一个全差分运算放大器,设计指标如下: 直流增益:>80dB 单位增益带宽:>50MHz 负载电容:=5pF 相位裕量:>60度 增益裕量:>12dB 差分压摆率:>200V/us 共模电压:(VDD=5V) 差分输入摆幅:>±4V 运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的 ,DSAT N V 之和小于,输出端的所有PMOS 管的 ,DSAT P V 之和也必须小于。对于单 级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 性能指标分析 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 1 1 1 3 5 7 1 1 3 5 1 3 5 7 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=- +P 第二级增益9 2 2 9 11 2 9 9 11 ()m o o o m m o o g g G A R r r g g =-=-=-+P 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r == ≥++ 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR : 1)、输入级: max 1max |2| Cc out DS C C d SR dt I v I C C = = = 单位增益带宽1m u C g C ω= ,可以得到 1m C u g C ω =

辽宁工业大学 模拟电子技术基础课程设计(论文) 题目:程控增益放大器 院(系): 专业班级: 学号: 学生姓名: 指导教师:(签字) 起止时间:2013.7.1—2013.7.12

课程设计(论文)任务及评语 院(系):教研室:Array 注:成绩:平时20% 论文质量60% 答辩20% 以百分制计算

摘要 本文设计是程控增益放大器。说明了程控增益放大器的结构和功能及其主要的特点。最后举出了实用电路。 放大器是应用最广泛的一类电子线路。它的功能是将输入信号进行不失真地放大。在广播,通信,自动控制,电子测量等各种电子设备中,放大器是必不可少的组成部分。在各类电子仪器和设备所采用的电子线路中,集成运算放大器是应用最普遍的模拟电子器件。集成运放配上不同的反馈网络和采用不同的反馈方式,就可以构成功能和特性完全不同的各种集成运放电子电路,简称运放电路。这些运放电路是各种电子电路中的最基本的组成环节。 本系统能够实现增益由程序控制,能够满足各项技术指标,测量准确,工作可靠,性能价格比较高。 关键词:运算放大器;多路转换开关;程控;增益放大

目录 第1章程控增益放大器方案论证 (1) 1.1程控增益放大器的意义 (1) 1.2程控增益放大器的设计要求和技术指标 (1) 1.2.1设计要求: (1) 1.2.2技术指标 (2) 1.3总体设计方案 (2) 第2章程控增益放大器各单元电路设计 (4) 2.1模拟开关 (4) 2.2集成电路运算放大器设计 (4) 2.2.1集成电路运算放大器中的电流源 (4) 2.2.2偏置电路 (5) 2.2.3输入级 (6) 2.2.4中间级 (7) 2.2.5输出级 (7) 2.3反馈电阻网络 (7) 2.4增益调整电路设计 (8) 第3章程控增益放大器整体电路设计 (9) 3.1整体电路图及工作原理 (9) 3.2电路参数计算与选择 (10) 3.3电路仿真结果 (10) 第4章设计总结 (13) 参考文献 (14) 附录I 总体电路图 (15) 附录II 元器件清单 (16)

设计课题 设计一个具有恒流偏置的单端输入-单端输出差分放大器。 学校:延安大学

一: 已知条件 正负电源电压V V V V EE cc 12,12-=-+=+;负载Ω=k R L 20; 输入差模信号mV V id 20=。 二:性能指标要求 差模输入电阻Ω>k R id 10;差模电压增益15≥vd A ;共模抑制 比dB K CMR 50>。 三:方案设计及论证 方案一:

方案二

方案论证: 在放大电路中,任何元件参数的变化,都将产生输出电压的漂移,由温度变化所引起的半导体参数的变化是产生零点漂移的主要原因。采用特性相同的管子使它们产生的温漂相互抵消,故构成差分放大电路。差分放大电路的基本性能是放大差模信号,抑制共模信号好,采用恒流源代替稳流电阻,从而尽可能的提高共模抑制比。 论证方案一:用电阻R6来抑制温漂 ?优点:R6 越大抑制温漂的能力越强; ?缺点:<1>在集成电路中难以制作大电阻; <2> R6的增大也会导致Vee的增大(实际中Vee不

可能随意变化) 论证方案二 优点:(1)引入恒流源来代替R6,理想的恒流源内阻趋于无穷,直流压降不会太高,符合实际情况; (2)电路中恒流源部分增加了两个电位器,其中47R的用来调整电路对称性,10K的用来控制Ic的大小,从而调节静态工作点。 通过分析最终选择方案二。 四:实验工作原理及元器件参数确定 ?静态分析:当输入信号为0时, ?I EQ≈(Vee-U BEQ)/2Re ?I BQ= I EQ /(1+β) ?U CEQ=U CQ-U EQ≈Vcc-I CQ Rc+U BEQ 动态分析 ?已知:R1=R4,R2=R3

全差分运算放大器设计 岳生生(6) 一、设计指标 以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下: ?直流增益:>80dB ?单位增益带宽:>50MHz ?负载电容:=5pF ?相位裕量:>60度 ?增益裕量:>12dB ?差分压摆率:>200V/us ?共模电压:2.5V (VDD=5V) ?差分输入摆幅:>±4V 二、运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT N V 之和小于0.5V ,输出端的所有PMOS 管的 ,DSAT P V 之和也必须小于0.5V 。对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该 要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 三、性能指标分析 1、 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 11135711 3 5 1 3 5 7 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=- +P 第二级增益 9 2 291129 9 11 ()m o o o m m o o g g G A R r r g g =-=-=- +P 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r == ≥++ 2、 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR :

福州大学 《电子技术综合实验》 课题:数控增益放大器 姓名:张全宇 学号:011100938 学院:电气工程与自动化学院2011级9班 指导老师:张选利 实验时间:2013年6月28-30日 目录

一、实验任务 (3) 二、实验目的 (3) 三、实验设计 (3) 四、实验内容 (5) 五、元件清单 (5) 六、心得体会 (5) 七、参考文献 (5) 一、实验任务 设计一个数字控制增益的放大器,要求在控制按键的作用下,放大器的增益依次在1~8之间转换,同时用LED数码管显示放大器的增益。 二、实验目的

通过本实验,熟悉运算放大器、计数器、数据选择器、加法器、译码/显示电路的用法。 三、实验设计 按照要求,放大器的增益应在1~8之间,因此,可选择图1-1所示的同相比例放大器,其电压增益为 2 1 1uf R A R =+ 图1-1 同相输入比例放大器 如果取R1=10k Ω,则可以通过改变R2实现增益的改变,当R2=0时,Auf=1;R2=10 k Ω时,Auf=2;R2=20 k Ω时,Auf=3;依次类推,当R2=70 k Ω时,Auf=8。为达到放大器增益数字控制的目的,可由数据选择器和电阻构成数控电阻网络,代替图中的R2,通过改变数据选择器的地址编码,实现数控电阻的目的,由此设计出图1-2所示的电路。图中用74LS160构成八进制计数器,计数器的Q2、Q1、Q0作为数据选择器CC4051的地址输入。每按动一下按键S1,计数器加1,数控电阻网络的等效电阻发生变化,由此控制放大器的增益在1~8之间变化。 为了直观地显示放大器的增益,译码/显示电路如下图所示。图中74LS283为二进制加法器,通过加一运算,将计数器的值转化为电压放大倍数。

对于全差分放大器,一般可以得到更大的swing (由于差分信号),同时可以实现对共模干扰、噪声以及偶数阶的非线性的抑制;但其需要有两个匹配的反馈网络,以及共模反馈电路 顺便提一下,对于全差分的折叠共源共栅(folded cascode)放大器,需要注意 转换速率(正向与负向)对输入对差分对的尾电流源和cascode电流源的考虑 非主极点的位置–输入对管的drain节点(注意全差分没有镜像极点的问题..),如果考虑PMOS输入的结构,将会折叠到n管的cascode,从而减小此节点阻抗,提高此非主极点的频率;但是P输入结构亦有其问题,如直流增益和cmfb电路的速度(考虑cmfb控制的为cascode的pmos电流源) 关于共模反馈CMFB 从反馈环路来看,共模的稳定问题来源于闭环的共模增益:由于输入差分对的尾电流源的local-feedback,通常共模增益较小,导致运放无法控制其输出共模点;通过CMFB共模反馈电路,可以提高共模反馈环路的增益,以稳定共模信号。 设计CMFB需考虑补偿以减小环路的稳定时间(settling time)和提高稳定性。 从性能上,我们希望共模反馈的单位增益带宽足够大,但由于cmfb的环路相较于差模通路可能有更多高频极点,故此在一定的功耗要求下其UGB一般比较难做的高,有书中提到可以将其设计为差模UGB 的1/3 一般共模反馈的方法是控制放大器的电流源,这里如果是folded-cascode的结构,可以考虑用cmfb控制cascode的电流源而不是输入差分对的电流源—-因其在共模环路中有较少的节点–>更容易补偿等..(另一种考虑是控制尾电流源可能导致共模增益的问题) 另外,对于cmfb控制的尾电流源,常见将尾电流源分为两半,其中之一由cmfb控制,另一半接恒定偏置电流;这种结构的具体分析可见Gray书12.4.2节的内容,简单来说,single-stage的opamp中控制尾电流源的cmfb结构,其UGB主要为gmt/CL, 其中gmt为尾电流源的跨导,这里拆分尾电流源来减半cmc共模控制的部分,这样UGB减小,即缩减带宽来提升共模反馈环路的相位裕度,当然cmfb的增益相应也减小了;另外恒定偏置部分也可帮助共模电压的初始建立,减小cmfb大的扰动。 具体的,共模反馈可以分为连续时间和开关电容两类 连续时间的共模反馈 一般的问题是信号幅度的限制和共模信号干扰,具体的共模反馈的方法: 1.电阻分压resistive-divider (如下左图) 电阻和cm-sense amplifier的输入电容会引入一个极点,可以通过在电阻上并联电容的方法,引入一个左半平面零点,来减小高频极点的影响

一、设计目的 1、了解并掌握电子电路的一般设计方法,具备初步的独立设计能力。 2、通过查阅手册和文献资料,进一步熟悉常用电子器件的类型和特性,并掌握合理选用的原则;进一步掌握电子仪器的正确使用方法。 3、学会使用EDA软件Multisim对电子电路进行仿真设计。 4、初步掌握普通电子电路的安装、布线、调试等基本技能。 5、提高综合运用所学的理论知识独立分析和解决问题的能力,学会撰写课程设计总结报告;培养严肃认真的工作作风和严谨的科学态度。 二、设计内容及要求 1、任务 设计并制作1个数控增益放大器。 2、基本要求 1)设计一个数字控制增益的放大器,要求在控制按键的作用下,放大器的增益依次在1~ 8之间转换。 2)用LED数码管显示放大器的增益。 3、主要元器件 包括:74LS283,74LS48,74LS160,74LS04,LF412,CC4051。 三、设计方案 可选择同相输入比例放大器,其电压增益为 R2?1?A uf R1RRRA=1时,=0如果取Ω=10k,则可以通过改变;当实现增益的改变,当uf212RAR AR A=8。;依次类推,当,=3Ω=70k,Ω=2 Ω=l0k,=;当20k ufufuf222为达到放大器增益数字控制的目的,可由数据选择器和电阻构成数控电阻网络,R,通过改变数据选择器的地址编码,实现数控电阻的目的。代替图中的2 :设计原理图(包括电路各部分的功

能). 根据数控增益放大器功能要求,最终设计方案将电路分为以下几部分: (1)信号产生及观测部分:实现信号的输入与增益的观测 (2)放大电路部分:实现信号的增益放大功能 (3)放大倍数输入及控制部分:实现增益放大倍数的手动自由控制 (4)放大倍数显示部分:实现放大倍数的显示 在实际电路接线中,由于异步计数器芯片的缺乏,采用一个同步计数器来代替,实现放大倍数0~7的显示。 四、本人负责的部分 (1)设计电路实现增益放大倍数的输入、控制与显示。 (2)实际接线中设计、检查74161同步计数器与其他部分的接线;调试过程中部分问题的发现与排除。 设计过程及遇到的问题: 整个设计过程我先后使用了以下三套设计方案, (1)最初确定使用74LS283四位加法器实现放大倍数的显示比输入到模拟,如图+1开关的数值

摘要 本文设计是程控增益放大器。说明了程控增益放大器的结构和功能及其主要的特点。最后举出了实用电路。 本系统以MCS-51单片机及其扩展,多路转换开关,数控增益放大器等构成了实用性较强的硬件电路。放大器是应用最广泛的一类电子线路。它的功能是将输入信号进行不失真地放大。在广播,通信,自动控制,电子测量等各种电子设备中,放大器是必不可少的组成部分。在各类电子仪器和设备所采用的电子线路中,集成运算放大器是应用最普遍的模拟电子器件。集成运放配上不同的反馈网络和采用不同的反馈方式,就可以构成功能和特性完全不同的各种集成运放电子电路,简称运放电路。这些运放电路是各种电子电路中的最基本的组成环节。 本系统能够实现增益由程序控制,能够满足各项技术指标,测量准确,工作可靠,性能价格比较高。 关键词:放大器,多路转换开关,MCS-51单片机

Summary This text design is a distance to control to increase benefit enlarger.Elucidation the distance control structure and function of increase the benefit enlarger and it be main of characteristics.The end enumerated practical electric circuit This system with the MCS-51 list slice machine and it expand, many road conversion switch, number control to increase benefit enlarger etc. constitute the function stronger hardware electric circuit.Enlarger is application the extensive electronics circuit.It of the function carry on importation signal not to lose to really enlarge.At the broadcasting, correspondence, auto control, the electronics measure etc. various electronics equipments in, the enlarger be a constitute of essential to have part.In every variety the electronics circuit for adopt of electronics instrument and equipments, integration operation enlarger is application the most widespread of imitate electronics spare part.Integration the luck put to go together with up the feedback way of the feedback network and adoption dissimilarity of dissimilarity, can constitute function and characteristic be various totally different integration luck turn on electricity sub- electric circuit, brief name luck turn on electricity road.These lucks' turning on electricity road is in various electronics electric circuit of most basically constitute link. This system can realization increase a benefit from the procedure control, can satisfy each item technique index sign, measure accurate, work credibility, function price more Gao. Keyword:Enlarger, many road conversion switch, MCS-51 list slice machine

《IC课程设计》报告——模拟部分电流镜负载的差分放大器设计

摘要 在对单极放大器与差动放大器的电路中,电流源起一个大电阻的作用,但不消耗过多的电压余度。而且,工作在包河区的MOS器件可以当作一个电流源。 在模拟电路中,电流源的设计是基于对基准电流的“复制”,前提是已经存在一个精确的电流源可以利用。但是,这一方法可能引起一个无休止的循环。一个相对比较复杂的电路被用来产生一个稳定的基准电流,这个基准电流再被复制,从而得到系统中很多电流源。而电流镜的作用就是精确地复制电流而不收工艺和温度的影响。在典型的电流镜中差动对的尾电流源通过一个NMOS镜像来偏置,负载电流源通过一个PMOS镜像来偏置。电流镜中的所有晶体管通常都采用相同的栅长,以减小由于边缘扩散所产生的误差。而且,短沟器件的阈值电压对沟道长度有一定的依赖性。因此,电流值之比只能通过调节晶体管的宽度来实现。而本题就是利用这一原理来实现的。 目录 1设计目标 (1) 2相关背景知识 (2) 3设计过程 (6) 3.1 电路结构设计 (6) 3.2 主要电路参数的手工推导 (6) 3.3 参数验证(手工推导) (7) 4 电路仿真 (9) 4.1 用于仿真的电路图 (9) NMOS: (9) PMOS (9) 整体电路图 (10) 4.2 仿真网表(注意加上注释) (10) 4.3 仿真波形 (13) 5 讨论 (17) 6 收获和建议 (17) 参考文献 (19)

1设计目标 设计一个电流镜负载的差分放大器,参考电路图如下:

2相关背景知识 据题目所述,电流镜负载的差分放大器的制作为0.35um CMOS 工艺,要求在5v 的电源电压下,负载电容为2pF 时,增益带宽积大于25MHz ,低频开环增益大于100,同时功耗和面积越小表示性能越优。 我们首先根据0.35um CMOS 工艺大致确定单个CMOS 的性能,即在一定值的W/L 下确定MOS 管在小信号模型中的等效输出电阻和栅跨导,然后记下得到的参数并将其带入到整体电路中计算,推导电流镜负载的差分放大器电路中的器件参数,例如,小信号模型的增益、带宽、功耗等,再分析是否满足题目中的各项指标的要求。若不满足,则依据摘要理所说的,调节晶体管的宽度,然后用调整后的参数进行仿真、验证,直到符合要求为止。 相关背景知识: 1. 差分式放大器 差分式放大器是由两个各项参数都相同的三端器件(包括BJT 、FET )所组成的差分式放大电路,并在两器件下端公共接点处连接一电流源。差分式又分为差模和共模信号:输入电压Vid 为Vi1和Vi2的差成为共模电压;另外,若输入电压Vic 为VI1和Vi2的算术平方根,则称为共模电压。当输入电压是共模形式时,,即在两个输入端各加入相同的信号电压,在差分放大电路中,无论是温度变化,还是电源波动引起的变化,其效果相当于在两个输入端加入了共模信号,两输出端输出的共模电压相同,故双端输出时输出电压为零;当输入电压是差模形式时,即在电路的两个输入端各加一个大小相等、极性相反的信号电压,一管电流将增加,另一管电流则减小,所以在两输出端间有信号电压输出。而差分放大器正是利用共模输入的特点来克服噪声信号和零点漂移的。此题要求用双端差模信号输入,单端输出,相应的计算公式如下: 1. 差模输入电压:12 id i i v v v =- 2. 共模输入电压:() 122 i i ic v v v += 3. 差模输出电压: 12 od o o v v v =- 4. 共模输出电压:12 2 o o oc v v v += 5. 双端输入——单端输出的差模电压增益: 2(2|| v d m d s d s A g r r = 6. 双端输入——单端输出的等效栅跨导: