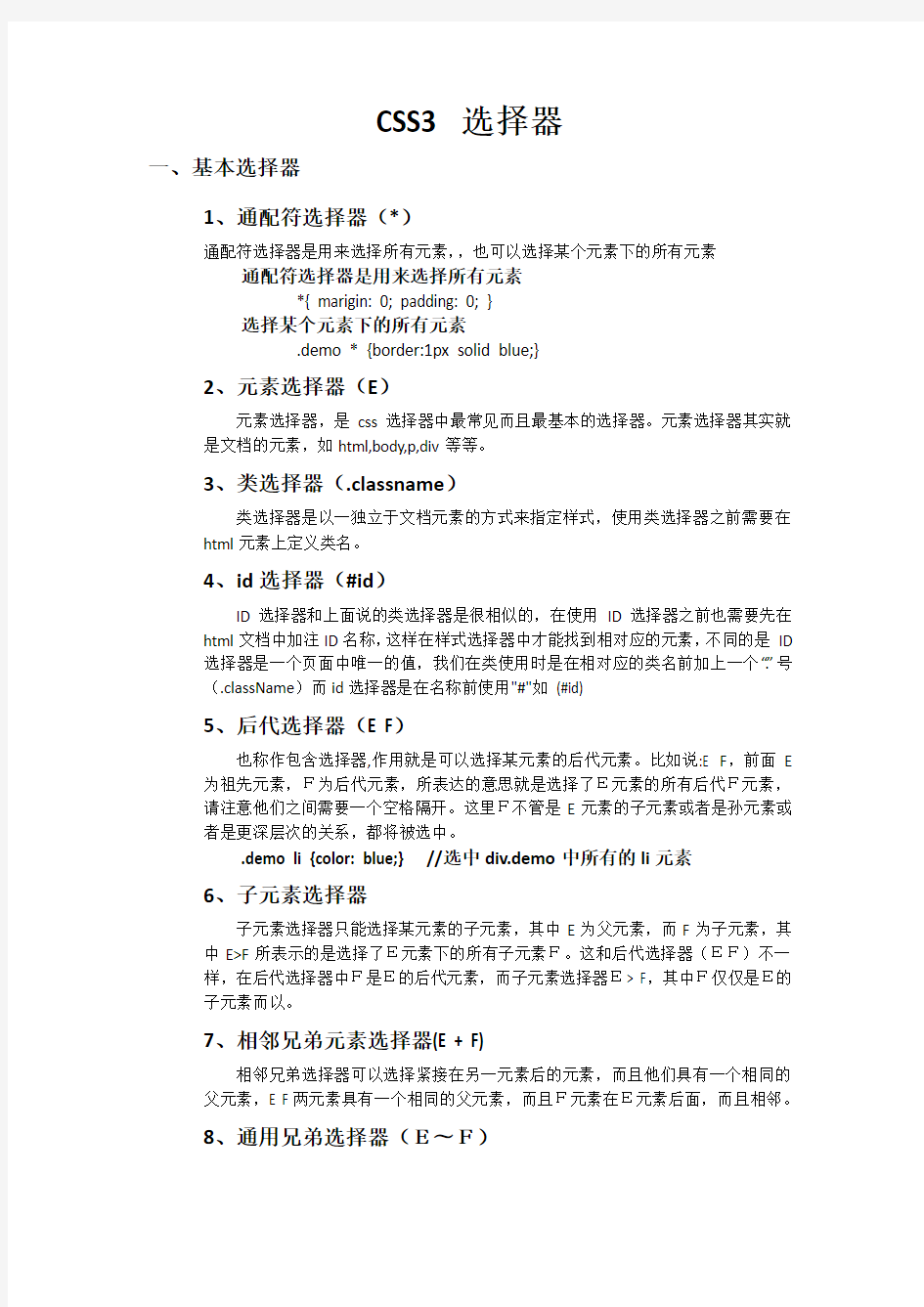

CSS3 选择器

一、基本选择器

1、通配符选择器(*)

通配符选择器是用来选择所有元素,,也可以选择某个元素下的所有元素

通配符选择器是用来选择所有元素

*{ marigin: 0; padding: 0; }

选择某个元素下的所有元素

.demo * {border:1px solid blue;}

2、元素选择器(E)

元素选择器,是css选择器中最常见而且最基本的选择器。元素选择器其实就是文档的元素,如html,body,p,div等等。

3、类选择器(.classname)

类选择器是以一独立于文档元素的方式来指定样式,使用类选择器之前需要在html元素上定义类名。

4、id选择器(#id)

ID选择器和上面说的类选择器是很相似的,在使用ID选择器之前也需要先在html文档中加注ID名称,这样在样式选择器中才能找到相对应的元素,不同的是ID 选择器是一个页面中唯一的值,我们在类使用时是在相对应的类名前加上一个“.”号(.className)而id选择器是在名称前使用"#"如(#id)

5、后代选择器(E F)

也称作包含选择器,作用就是可以选择某元素的后代元素。比如说:E F,前面E 为祖先元素,F为后代元素,所表达的意思就是选择了E元素的所有后代F元素,请注意他们之间需要一个空格隔开。这里F不管是E元素的子元素或者是孙元素或者是更深层次的关系,都将被选中。

.demo li {color: blue;} //选中div.demo中所有的li元素

6、子元素选择器

子元素选择器只能选择某元素的子元素,其中E为父元素,而F为子元素,其中E>F所表示的是选择了E元素下的所有子元素F。这和后代选择器(EF)不一样,在后代选择器中F是E的后代元素,而子元素选择器E> F,其中F仅仅是E的子元素而以。

7、相邻兄弟元素选择器(E + F)

相邻兄弟选择器可以选择紧接在另一元素后的元素,而且他们具有一个相同的父元素,E F两元素具有一个相同的父元素,而且F元素在E元素后面,而且相邻。

8、通用兄弟选择器(E?F)

选择某元素后面的所有兄弟元素,需要在同一个父元素之中,E和F元素是属于同一父元素之内,并且F元素在E元素之后,那么E ~ F 选择器将选择中所有E元素后面的F元素

二、属性选择器

1、E[attr]

E[attr]属性选择器是CSS3属性选择器中最简单的一种。如果你希望选择有某个属性的元素,而不论这个属性值是什么,你就可以使用这个属性选择器。

2、E[attr="value"]

E[attr="value"]是指定了属性值“value”,而E[attr]只是选择了有对应的属性,并没有明确指其对应的属性值"value",这也是这两种选择器的最大区是之处。

E[attr="value"]这种属性值选择器有一点需要注意:属性和属性值必须完全匹配。

3、E[attr~="value"]

E[attr~="value"],这种属性选择器是属性值是一个或多个词列表,如果是列表时,他们需要用空格隔开,只要属性值中有一个value相匹配就可以选中该元素。

4、E[attr^="value"]

[attr^="value"]属性选择器,指的是选择attr属性值以“value”开头的所有元素,换句话说,选择的属性其以对应的属性值是以“value”开始的。

5、E[attr$="value"]

E[attr$="value"]表示的是选择attr属性值以"value"结尾的所有元素,换句话说就是选择元素attr属性,并且他的属性值是以value结尾的。

6、E[attr*="value"]

E[attr*="value"]属性选择器表示的是选择attr属性值中包含子串"value"的所有元素。也就是说,只要你所选择的属性,其属性值中有这个"value"值都将被选中。

7、E[attr|="value"]

E[attr|="value"]被称作为特定属性选择器。这个选择器会选择attr属性值等于value或以value-开头的所有元素。

三、伪类选择器

伪类选择器是css中已经定义好的选择器,不能随便起名字。在css中我们常用的伪类选择器是使用在a元素上的几种选择器,它们的使用方法如下:a:link{color:gray;}/*链接没有被访问时前景色为灰色*/

a:visited{color:yellow;}/*链接被访问过后前景色为黄色*/

a:hover{color:green;}/*鼠标悬浮在链接上时前景色为绿色*/

a:active{color:blue;}/*鼠标点中激活链接那一下前景色为蓝色*/

1、UI元素状态伪类

我们把":enabled",":disabled",":checked"伪类称为UI元素状态伪类,这些主要是针对于HTML中的Form元素操作,最常见的比如我们"type="text"有enable和disabled两种状态,前者为可写状态后者为不可状态;另外"type="radio" 和"type="checkbox""有"checked"和"unchecked"两种状态。来看两个实例,比如说你想将"disabled"的文本框与别的文本框区别出来,你就可以这样应用:input[type="text"]:disabled{border:1px solid

#999;background-color:#fefefe;}

2、CSS3的:nth选择器

:first-child选择某个元素的第一个子元素;

:last-child选择某个元素的最后一个子元素;

:nth-child()选择某个元素的一个或多个特定的子元素;

:nth-child(length);/*参数是具体数字*/

:nth-child(n);/*参数是n,n从0开始计算*/

:nth-child(n*length)/*n的倍数选择,n从0开始算*/

:nth-child(n+length);/*选择大于length后面的元素*/

:nth-child(-n+length)/*选择小于length前面的元素*/

:nth-child(n*length+1);/*表示隔几选一*/

//上面length为整数

:nth-last-child()选择某个元素的一个或多个特定的子元素,从这个元素的最后一个子元素开始算;

:nth-of-type()选择指定的元素;

:nth-last-of-type()选择指定的元素,从元素的最后一个开始计算;

:first-of-type选择一个上级元素下的第一个同类子元素;

:last-of-type选择一个上级元素的最后一个同类子元素;

:only-child选择的元素是它的父元素的唯一一个子元素;

:only-of-type选择一个元素是它的上级元素的唯一一个相同类型的子元素;

:empty选择的元素里面没有任何内容。

本科学生设计性实验报告 项目组长_学号__ 成员 专业班级_ 实验项目名称_8-3选择器的设计 指导教师及职称讲师 开课学期2011 至2012 学年_第二学期 上课时间2012 年03 月31 日

一、实验设计方案 实验名称:8-3选择器的设计实验时间:2012-3-31 小组合作:是○否●小组成员: 1、实验目的: 熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。 实验要求: 用三种不同的Verilog语言设计一个8-3选择器,并选择其中一种用实验箱进行硬件测试。 2、实验场地及仪器、设备和材料: 实验场地:W201 设备:一台安装了QuartusⅡ的电脑,实验箱 3、实验思路(实验内容、数据处理方法及实验步骤等): 实验内容: (1)首先利用QuartusⅡ完成文本编辑输入和仿真测试等步骤,给出仿真波形。 (2)将此多路选择器看成是一个元件,利用元件例化语句描述图,并将此文件放在同一目录中。 (3)引脚锁定以及硬件下载测试。若选择目标器件是EP1C12,选实验电路模式5,用键1(PIO43,引脚号为135)控制s2;用键2(PIO48,引脚号为128)控制s1;用键3(PIO41,引脚号为132)控制s0;a、b、c、d、e、f、g、h分别接I/O7(引脚号为240)、I/O6(引脚号为 (4)在实验系统上进行硬件测试,验证本项设计的功能。 实验步骤: 1、8-3选择器的文本编辑输入 a、新建工程:File→New Quartus Project b、新建Verilog HDL 文本:File→Verilog HDL File,并编写程序,代码如下:

EDA实验报告 学生姓名:asfmla;m 学号:eafvpa[cv专业班级:电子3班 组合电路设计 一、实验目的 熟悉quartusⅡ的VHDL文本设计全过程,学习简单组合电路的设计、多层次电路设计、仿真。 二、实验内容 实验内容:首先利用quartusⅡ完成2选1多路选择器(例4-3)的文本编译输入(mux21a.vhd)和仿真测试等步骤,最后在实验系统上硬件测试,验证此设计的功能。将此多路选择器看成一个元件mux21a,利用元件例化语句描述成三选一,然后进行编译、综合、仿真。引脚锁定以及硬件下载测试。建议选实验电路模式5,用键1(PIO0)控制s0;用键2(PIO1)控制s1;a3、a2和a1分别接clock5、clock0和clock2;输出信号outy仍接扬声器spker。通过短路帽选择clock0接256HZ信号,clock5接1024HZ信号,clock2接8HZ信号。最后选行编译、下载和硬件测试实验。 三、实验器材 Quartus II软件。 四、设计思路/原理图 五、实验程序 实验内容1:二选一: library ieee; use ieee.std_logic_1164.all; entity mux21a is port(a,b: in std_logic; s: in std_logic; y: out std_logic); end entity; architecture dataflow of mux21a is begin

y<=a when s='0' else b; end architecture; 实验内容2:三选一 library ieee; use ieee.std_logic_1164.all; entity mux31a is port(a1,a2,a3: in std_logic; s0,s1: in std_logic; outy: out std_logic); end entity mux31a; architecture m31a of mux31a is component mux21a port( a,b: in std_logic; s: in std_logic; y: out std_logic); end component; signal tmp: std_logic; begin u1: mux21a port map(a=>a2,b=>a3,s=>s0,y=>tmp); u2: mux21a port map(a=>a1,b=>tmp,s=>s1,y=>outy); end architecture; 六、实验步骤 在E盘新建一个文件夹,用于存放工程。打开quartus,新建工程,然后选择新建VHDL 文件,命名为mux21a。在VHDL编辑窗口中输入实验程序后,进行编译、仿真;在实验一的基础上,新建VHDL文件,命名为mux31a。在VHDL编辑窗口中输入实验程序后,进行编译、综合、仿真;最后进行硬件测试。 七、仿真波形分析 二选一波形: 分析:当s=0时,y=a;当s=1时,y=b。 三选一综合图形及其波形

课程设计报告 课程名称数字逻辑课程设计 课题任务一 16选1选择器设计 课题任务二 JK触发器的设计 专业 班级

学号 姓名 指导教师 2013-12-8

课程设计任务书 课程名称数字逻辑课程设计课题任务一 16选1选择器设计课题任务二 JK触发器的设计

专业班级网络工程 学生 学号 指导老师 审批 任务书下达日期: 2011年 12月 14日 任务完成日期:2011年 12月 31日 前言 Quartus® II design 是最高级和复杂的,用于system-on-a-programmable-chip (SOPC)的设计环境。 QuartusII design 提供完善的timing closure 和LogicLock? 基于块的设计流程。QuartusII design是唯一一个包括以timing closure 和基于块的设计流为基本特征的programmable logic device (PLD)的软件。 Quartus II 设计软件改进了性能、提升了功能性、解决了潜在的设计延迟等,在工业领域率先提供FPGA与mask-programmed devices开发的统一工作流程Quartus II 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多种设计输入形 式,嵌自有的综合器以及仿真器,可以完成 从设计输入到硬件配置的完整PLD设计流程。 Quartus II可以在XP、Linux以及Unix 上使用,除了可以使用Tcl脚本完成设计流

CSS选择器笔记 阮一峰整理 参考网址:456 Berea Street 一、基本选择器 实例: * { margin:0; padding:0; } p { font-size:2em; } .info { background:#ff0; } https://www.doczj.com/doc/d63712793.html, { background:#ff0; } https://www.doczj.com/doc/d63712793.html,.error { color:#900; font-weight:bold; } #info { background:#ff0; } p#info { background:#ff0; } 二、多元素的组合选择器

实例: div p { color:#f00; } #nav li { display:inline; } #nav a { font-weight:bold; } div > strong { color:#f00; } p + p { color:#f00; } 三、CSS 2.1 属性选择器 实例: p[title] { color:#f00; } div[class=error] { color:#f00; }

td[headers~=col1] { color:#f00; } p[lang|=en] { color:#f00; } blockquote[class=quote][cite] { color:#f00; } 四、CSS 2.1中的伪类 实例: p:first-child { font-style:italic; } input[type=text]:focus { color:#000; background:#ffe; } input[type=text]:focus:hover { background:#fff; } q:lang(sv) { quotes: "\201D" "\201D" "\2019" "\2019"; } 五、 CSS 2.1中的伪元素

计算机组成原理实验报告 ——实验一多路选择器的设计与实现 专业:计算机科学与技术(师范) 姓名:XXX 学号: 指导老师: 完成日期:

实验目的 1、回顾多路选择器的原理 2、熟悉Logisim软件的使用方法 3、熟悉ISE软件的开发过程 4、锻炼使用VHDL语言面熟硬件的能力 5、熟悉Digilent Nexy3 FPGA开发板 一、实验内容 用两种方法实现一个两位数据的2选1多路选择器 1、用Logisim软件设计2选1多路选择器并进行仿真 2、使用VHDL语言设计2选1多路选择器,并在ISE环境下进行综合、仿真、调试,并下载到Digilent Nexy3 FPGA开发板进行验证 二、实验过程 第一部分:用Logisim实现2选1多路选择器 Step 1:创建工程 2选1多路选择器的逻辑表达式:Z=(A* S)+ (B*S),由此可知一个2选1多路选择器需要 用到与、或、非三种逻辑门电路 Step 2:添加元件 添加U1、U2、U3、U4四个与门电路,U5一个

非门电路,U6、U7两个或门电路 添加A0、A1、B0、B1、S五个输入端口,Z0、 Z1两个输出端口 完成后如下图所示: Step3:连线 完成后如下图所示:

Step 4:仿真 Step 5:编辑电路外观 Step 6: 电路应用 三、实验结果 第一部分:用Logisim实现2选1多路选择器实验结果 1、表格: 序号 输入输出 A1A0B1B0S Z1Z0(预期)Z1Z0(实际) 1000110101 2001011010 3001110011 4010000101 5100001010

选多路选择器 部门: xxx 时间: xxx 整理范文,仅供参考,可下载自行编辑

EDA实验二4选1多路选择器设计实验 一、实验目的 进一步熟悉 QuartusII 的 VHDL 文本设计流程、组合电路的设计仿真和测试。 二、实验内容 实验内容一:根据4.1流程,利用 QuartusII 完成四选一多路选择器的文本编辑输入和仿真测试等步骤,给出仿真波 形。 b5E2RGbCAP 实验内容二:对 VHDL 不同描述方式的四选一多路选择器进行硬件实验,比较他们的特性。 三、实验记录 1.when-else语句设计的4选1多路选择器 a>.利用when-else语句的vhdl程序 library ieee。 use ieee.std_logic_1164.all。 entity mux41a is port( a,b,c,d,s0,s1:in std_logic。 y:out std_logic>。 end entity mux41a。 architecture one of mux41a is begin

y<= a when s0='0' and s1='0' else b when s0='1' and s1='0' else c when s0='0' an d s1='1' else d。 end architecture one。 备注 以上是when-else语句设计的4选1多路选择器的vhdl描述。程序中应该注意的有以下几点 A.一:实体的命名要和工程名相同,并且不能是中文的或者以数字 开头; B.二:when-else语句具有最高赋值优先级; b>.when-else语句设计的4选1多路选择器的RTL图 图<1)when-else语句设计的4选1多路选择器的RTL图 c>.when-else语句设计的4选1多路选择器的时序仿真波形图

CSS选择器 1.常用选择器 常用的选择器有类型选择器和后代选择器。 1.1类型选择器 类型选择器用来选择特定类型的元素。可以根据三种类型来选择。 1)ID选择器,根据元素ID来选择元素。 前面以”#”号来标志,在样式里面可以这样定义: #demoDiv{ color:#FF0000; } 这里代表id为demoDiv的元素的设置它的字体颜色为红色。 我们在页面上定义一个元素把它的ID定义为demoDiv,如:

这个段落字体颜色为红色

最后,用浏览器浏览,我们可以发现所有class为demo的元素都应用了这个样式。包括了页面中的div元素和p元素。 上例我们给两个元素都定义了class,但如果有很多个元素都会应用这个元素,那个一个个的定义元素,就会造成页面重复的代码太多,这种现象称为“多类症”。 我们可以改成这样来定义。

4选1多路选择器的VHDL描述 要求:THEN语句和CASE语句实现4选1多路选择器,其中选择控制信号s1和s0的数据类型为STD_LOGIC_VECTOR;当s1=?0?,s0=?0?;s1=?0?,s0=?1?;s1=?1?,s0=?0?和s1=?1?,s0=?1?时,分别执行y<=a、y<=b、y<=c、y<=d。 一、解法1:用IF_THEN语句实现4选1多路选择器 (1)程序: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux41 IS PORT (a,b,c,d: IN STD_LOGIC; s0: IN STD_LOGIC; s1: IN STD_LOGIC; y: OUT STD_LOGIC); END ENTITY mux41; ARCHITECTURE if_mux41 OF mux41 IS SIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0);--定义标准逻辑位矢量数据BEGIN s0s1<=s1&s0; --s1相并s0,即s1与s0并置操作 PROCESS(s0s1,a,b,c,d) BEGIN IF s0s1 = "00" THEN y <= a; ELSIF s0s1 = "01" THEN y <= b; ELSIF s0s1 = "10" THEN y <= c; ELSE y <= d; END IF; END PROCESS; END ARCHITECTURE if_mux41; (2)编译的结果如下:

编译报告: 二、解法2:用CASE语句实现4选1多路选择器(1)程序: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux41 IS PORT (a,b,c,d: IN STD_LOGIC;

实验二 4选1数据选择器的设计 实验学时:2学时 实验类型:设计 实验要求:必做 一、实验目的 通过实验让学生掌握组合逻辑电路的EDA原理图输入设计法,通过电路的仿真和硬件验证,让学生进一步了解4选1数据选择器的功能。 二、实验原理 数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。数据选择器的功能类似一个多掷开关。数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、16选1等类别。数据选择器的电路结构一般由于活门阵列而成,也有用传输门开关和门电路混合而成的。 图1 4选1数据选择器原理图 图1是一个4选1数据选择器,d3—d0是数据输入端,s1和s0是控制输入端,y是4选1数据输出端。 三、实验内容 设计并实现一个4选1数据选择器,要求根据原理图写出它的逻辑关系,并利用开发工具软件对其进行编译和仿真,最后通过实验开发系统对其进行硬件验证。

四、实验步骤 1)在Maxplus2的图形编辑方式下,从prim元件库中调出4选1数据选择器电路所需要的元件。并按照图1所示的原理电路,完成4选1数据选择器原理图的输入设计。 2)保存好原理图文件,以为文件名保存在工程目录中。执行Compiler命令对设计文件进行编译。执行Create Default Symbol命令,可为4选1数据选择器生成一个元件符号。 3)在波形编辑方式下,编辑的波形文件,并完成输入信号d3,d2,d1和d0,控制信号s1和s0电平的设置。波形文件编辑结束后以为波形文件名存盘。执行仿真器Simulator命令,仿真开始,观察仿真波形进行设计电路的功能验证。 五、实验结果 1. 4选1数据选择器的逻辑功能及真值表 2.仿真波形

CSS选择器的声明与嵌套 使用CSS选择器控制HTML标记的时候,每个选择器的属性可以一次声明多个,选择器本身也可以同时声明多个。 并且,任何形式的选择器,都是合法的,标记选择器,class选择器和ID选择器都可以集体声明。 集体声明 在声明CSS选择器时,如果某些选择器的风格是完全相同的,或者部分相同,这时便可以使用集体声明的方式,将风格相同的选择器同时声明。 [html]view plain copy print? 1. 2. 3.

17. 18. 19.

20.集体声明p2 27.

集体声明p3 28. 29. 30. 全局声明 对于实际网站中,如果希望页面中所有的标记都使用同一种CSS样式,但是,又不希望逐个来集体声明,这是可以使用全局声明符号*来声明。 [html]view plain copy print? 1. 2. 3.