上海聚锐电子科技有限公司

Focus On Excellence & Satisfaction An EDA Comprehensive Services Company

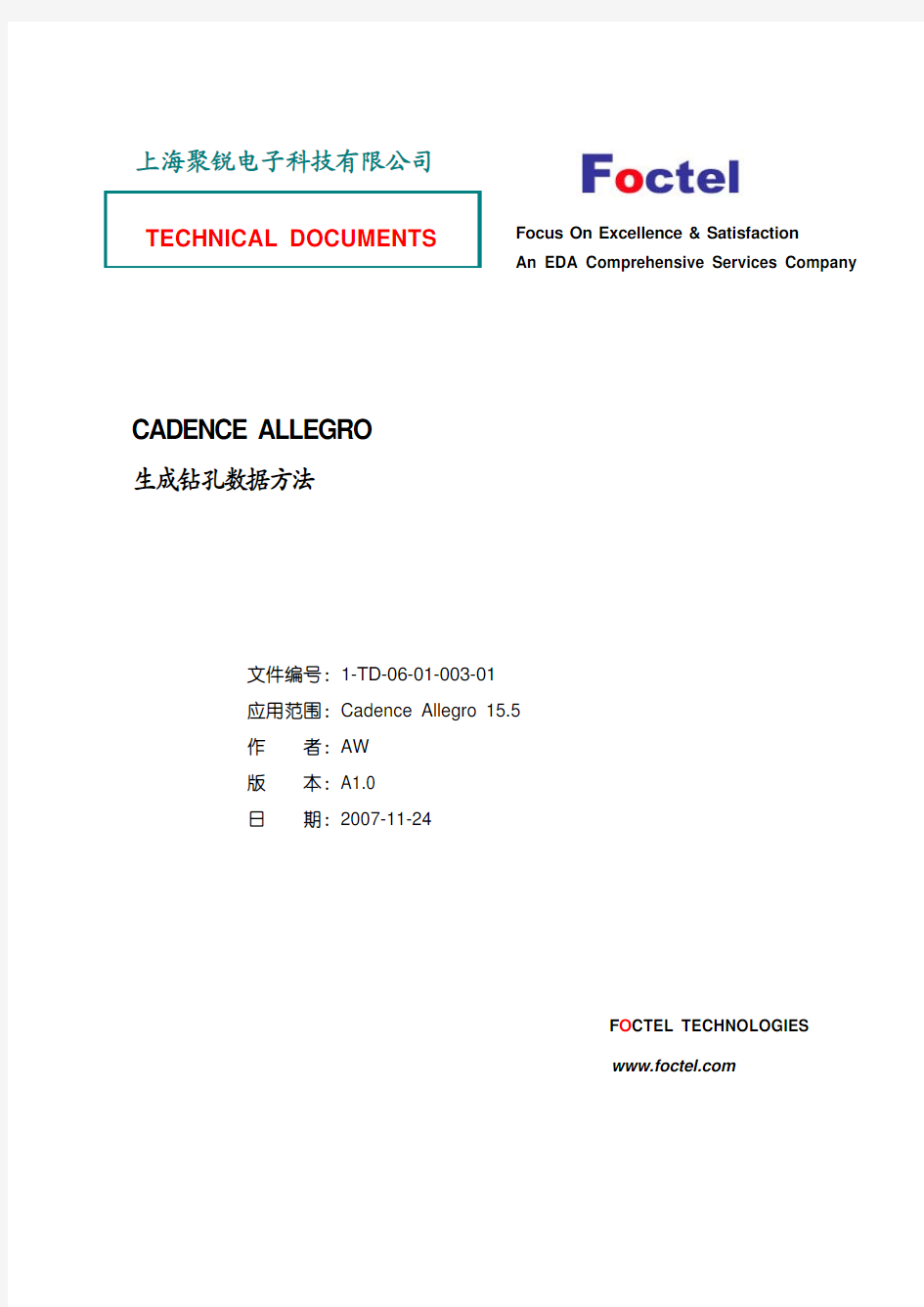

CADENCE ALLEGRO 生成钻孔数据方法

文件编号:1-TD-06-01-003-01 应用范围:Cadence Allegro 15.5 作 者:AW 版 本:A1.0 日 期:2007-11-24

F O CTEL TECHNOLOGIES

https://www.doczj.com/doc/dc7034667.html,

TECHNICAL DOCUMENTS

生成Drill Legend

√这里默认为

即便在非常复杂的项目中,也能保证精度。值得

CAM350

勾选这一项,这样系统会自动把钻头直径信息加入到数控文件中。更多详细信息,可以点击

点击Route后,系统会生成一个.rou 文件

Allegro等长线Xnet约束设置 2010-11-11 11:31:00| 分类:cadence,orcad,al | 标签:|字号大中小订阅 Allegro中等长约束: 1排阻等设置为Xnet:Analyze->SI/EMI Sim->Model YES 2, 直接在DevType Value/Refdes中选择要设定Model 的器件或直接在板子上点选要设置Model的器件; 3, 点选Create Model,建立该零件的Model,(如果已经有该零件的Model,并在前面定义,然后 Find Model即可,这里主要介绍没有的情况) 在出现对话框中选择Create ESpiceDevice model,点击OK ModelName: 输入产生Model的名字 Circuit type: 选择Type, 电阻,电感或电容 Value: 值 Single Pin: 各Pin的连接顺序, 中间为空格, 这里要注意要看零件的pin的排列, 1 2 3 4 5 6 7 8,就是: 1和2是一个电阻,其它同理 所以如果就是普通电阻电容那就更简单了. Common Pin: 这里不用管它,空着就可以. 上面都输入好了就点击OK,完成Model的建立. 点击OK退出就可以发现连接该排阻的两边的Net都有了个Xnet属性: 这样就可以搞定Xnet,很简单吧! 下面就开始等长设置吧! 第二部分针对Xnet部分的等长设置 设置好了Xnet后就可以在Allegro中设置该Xnet的等长了,有两种方法可以设置Xnet的等 长. 第一种, 使用Edit>Properties定义 注意必须使用Pin Pair 才能定义Xnet等长 RELATIVE_ PROPAGATION_DELAY= GroupX : G : U1.5 : U2.4 : 0 : 20 在没有定义Xnet之前这样定义时会提示错误的 其它的和前面的等长设置方法都一样. 第二种, Constraint Manager 设置 1, 开启Constraint Manager, 点选菜单Setup>Electrical Constraint Spreadsheet或直接点击工具栏 出现Constraint Manager 窗体:

Introduction to Cadence Customer IC Design Environment 熊三星徐太龙编写 安徽大学电子信息工程学院微电子学系

目录 1. Linux 常用命令 (3) 2. 软件的启动 (5) 3. 建立工程 (7) 4. 画原理图 (9) 5. 原理图仿真 (17) 6. 生成symbol (25) 7. 版图 (30) 8. DRC检查 (50) 9. LVS检查 (54) 10. PEX参数提取 (58) 11. 后仿真 (61)

1.Linux 常用命令 目前,电子设计自动化(Electronic Design Automation, EDA)工具多数都基于Linux操作系统,因此在学习使用EDA之前,有必要掌握一些Linux操作系统的基本命令。 1.mkdir mkdir命令让用户在有写权限的文件夹(目录)下建立一个或多个文件夹(目录)。其基本格式如下: mkdir dirname1 dirname2 ... (dirname 为文件夹或者目录的名字) 2.cd cd命令让用户进入一个有权限的文件夹(目录)。其基本格式如下: cd Filename (Filename为文件夹或者目录的名字) cd .. (.. 表示上一层文件夹或者目录) 3.ls ls命令用以显示一个文件夹(目录)中包含的文件夹(目录)或者文件。其基本格式如下: ls Filename (Filename为文件夹或者目录的名字) 如果ls命令后没有跟文件夹(目录)名字,显示当前文件夹(目录)的内容。 ls 命令可以带一些参数,给予用户更多相关的信息: -a : 在UNIX/Linux中若一个文件夹(目录)或文件名字的第一个字元为"." ,该文件为隐藏文件,使用ls 将不会显示出这个文件夹(目录)或文件的名字。如cshell 的初始化文件.cshrc,如果我们要察看这类文件,则必须加上参数-a。格式如下:ls –a Filename -l : 这个参数代表使用ls 的长(long)格式,可以显示更多的信息,如文件存取权,文件拥有者(owner),文件大小,文件更新日期,或者文件链接到的文件、文件夹。 4.cp cp命令用于文件夹(目录)或文件的复制。其基本格式如下: cp source target 将名为source的文件复制一份为名为target的文件。如果target 文件不存在,则产生文件名为target 的文件,如果target 文件存在,缺省时自动覆盖该文件。 cp file1 file2…dir 将文件file1 file2 ... 都以相同的文件名复制一份放到目录dir 里面。

对于专业的PCB layout人员,等长的 置自然如 家常小菜般常见 而对于一些硬 程师,由于不 常lay比较复杂PCB般,通常又要忙些其他的事情,在 一块儿就涉及的比较少了,不熟悉等长的 置就显得一点儿也不奇怪了 而有时,衡 性 比 ,硬 程师感觉没必要把一些简单的高速 外包,就亲自操刀, 时就会遇到各种他们感觉很奇怪的问题 曾 过几个客户,他们都向 请教过 一个问题 allegro怎 置等长 当时向他们讲解如何操作,根据 来 馈的结果,貌似效果不好 于是就准备亲自动手整理一篇相对比较全的等长 置文档,希望 次碰到客户需求时, 篇文档能搞定等长 置的问题 开始之前,先说一 什 置等长 方面的理论, 并没有深入地探究过,只知其然 数 逻辑中,数据的传输是按规定的时序进行的,信号在传输线 有自己的延时,如果信号线长度差别较大,对应的延时就会有较大的差别, 时信号间时序可能会紊乱,导 芯 不能 常收发数据 简单的说,信号线间的等长控制,就是 了时序的 配 在 计中,比较常见的就是信号线和时钟之间的误差 关于误差值, 再探讨一 接 来进入 题 需要控制等长的信号线,绝不是一根, 样 们可 根据情况进行分类处理 里 DDR2 例,介绍如何通过BUS来 置等长 束 打开CM,进行电气规 置,如 图 想必 个 计者,哪些信号应 分在一组,自己应 心里很清楚 在 们打开CM的电气规 ,先进行分组,如 的案子,有两 DDR2,就把数据线 8根分一组,然 在加 组信号的数据锁 信号和掩码信号 关于BUS的 置操作,如 图

简单说一 骤 选中信号---右键选择create---接着选择 菜单中的BUS 接 来会弹 一个对话框,如 图 在BUS栏中填 合适的 称,点 OK就完 了BUS的 建 如果 建BUS ,发现某一个信号或者几个信号漏选了, 时再把它们添加进 才的BUS就可 了 如 图 样会弹 对话框,如 如 就完 了BUS的 建 个人认 在 里对信号 建BUS进行 分,显得更加有条理

关于岩土工程勘察图例图示的规定 2004年9月20日稿

目录 1、总则 (1) 2、岩土工程勘察图例 (1) 2.1地质年代 (1) 2.2土的图例 (3) 2.3 岩石的图例及符号 (5) 2.4、第四系分层及成因符号 (7) 2.5 地层代号 (8) 2.6 勘察工作图例 (8) 2.7 地质图例 (11) 2.8 常用地形图图例(1:500、1:1000、1:2000) (13) 2.9 工程建(构)筑物及常用建筑总图图例 (15) 3、岩土工程勘察图示 (16) 3.1 一般规定 (16) 3.2 图例图示 (18) 3.3 平面图图示 (18) 3.4工程地质剖面图图示 (21) 3.5、柱状图图示 (24) 3.6动力触探成果图表图示 (25) 3.7 钻孔抽、提水试验成果图表图示 (26) 3.8钻孔压水试验成果图表图示 (26) 3.9 勘探点数据一览表 (26) 3.10 线路工程平面图、剖面图、柱状图 (26) 附录: A 勘探点平面布置图 B 工程地质剖面图 C钻孔柱状图 D探井展示图 E动力触探成果图表 F抽水试验成果图表 G压水试验成果图表 H 线路工程纵断面图 I 桥工程地质纵断面图 J 隧道工程地质纵断面图

1、总则 1.0.1 为保证岩土工程勘察文件编制质量,统一岩土工程勘察图例图示,制定本规定。 1.0.2 本规定适用于重庆市建筑工程和市政工程岩土工程勘察计算机制图,其它工程勘察可参考使用。 1.0.3 本规定适用于绘制岩土工程勘察平面图、剖面图、柱状图以及其它岩土工程勘察成果图表。 1.0.4岩土工程勘察图例图示除应符合本规定以外,还应符合国家现行有关标准的规定。 1.0.5 本规定以外的图例图示可在相关的技术标准及手册中查找采用。 2、岩土工程勘察图例 2.1地质年代 2.1.1 在岩土工程勘察图件中地质年代应表示到组或段,系的第一个字母使用正体大写,其下标数字表示统,其后小写斜体字母表示组,组后的数字上标表示段,如:J2s(侏罗系中统沙溪庙组)、J2s1(侏罗系中统沙溪庙组第一段) 2.1.2

Cadence_SPB16.3入门教程——元器件布局 2012-03-07 13:50:28| 分类:cadence | 标签: |字号大中小订阅 在摆放元件的时候可以与OrCAD Capture交互来完成。在OrCAD Capture中打开原理图,选择菜单 Options->Perferences,如图3.11所示。 图3.11 OrCAD Capture交互 弹出Preferences对话框,如图3.12所示。 图3.12 Preferences 对话框 点击Miscellaneous标签,将Enable Intertool Communication复选框选中。点击确定关闭对话框。 之后在allegro中打开Placement 对话框的状态下,首先在原理图中点击需要放置的元件使之处于选中状态下,然后切换到allegro中,把鼠标移到作图区域内,就会发现该元件跟随着鼠标一起移动了,在想要放置的位置单击鼠标左键即可将该元件放置在PCB中,cadence的这个交互功能非常的好用,不仅在布局的时候可以这样,在布线仿真的时候都能使用该功能来提高效率。 PCB布局是一个很重要很细心的工作,直接影响到电路信号的质量。布局也是一个反复调整的过 程。一般高速PCB布局可以考虑以下几点: ·CPU或者关键的IC应尽量放在PCB的中间,以便有足够的空间从CPU引线出来。

·CPU与内存之间的走线一般都要做等长匹配,所以内存芯片的放置要考虑走线长度也要考虑间隔是 否够绕线。 ·CPU的时钟芯片应尽量靠近CPU,并且要远离其它敏感的信号。 ·CPU的复位电路应尽量远离时钟信号以及其它的高速信号。 ·去耦电容应尽量靠近CPU电源的引脚,并且放置在CPU芯片的反面。 ·电源部分应放在板子的四周,并且要远离一些高速敏感的信号。 ·接插件应放置在板子的边上,发热大的元器件应放在置在通风条件好的位置,如机箱风扇的方向。 ·一些测试点以及用来选择的元件应放在顶层,方便调试。 ·同一功能模块的元件应尽量放在同一区域内。 在布局的过程中,如果某一元件的位置暂时固定了,可以将其锁住,防止不小心移动以提高效率。Allegro提供了这个功能。点击工具栏的图标按钮,然后点击一下元件,右键选择Done,然后该元件就 再也无法选中了,如果要对已经锁定的元件解锁,可以点击工具栏的图标按钮,然后点击右键Done。 也可以点击该按钮后在PCB画图区域点击右键,选择Unfix All选项来解锁所有的元件。 摆放元件的时候,如果需要将元件放置在对面那一层,可以选中元件后单击右键选择菜单Mirror这时 候该元件就被放置到相反的那一层。 在完成元件的布局后,还要重新画板框以及禁止布线层与禁止摆放层。可以参考上面的画板框方法来 完成这些工作,这里就不重复了。

所有常用电气元件图形符号 原理、接线图图形符号 温度开关 液位开关 热继电器的热元件 电钟 电流表 电压表 V 电度表 kwh 欠流继电器线圈 热继电器常闭触点 点 点 三极断路器 ××× QF KI 过流继电器线圈 KI 过压继电器线圈 欠压继电器线圈 KV 动断(常闭)触点 动合(常开) 触点 KM KI KV KA 延时断开的动断常闭)触点 延时闭合的动合 (常开)触 动合(常开)钮 动断(常闭)钮 断路器 × QF 熔断器 三级熔断器式隔离开关 QS 电流互感器 或 TA 电压互感器 继电器线圈 KA 接触器线圈 KM

电动机 M 接地 接机壳 或 变换器 同轴电缆 屏蔽电缆 导线的连 电感器 电容器一般符号 或 电阻器的一般符号 或 放大器 或 桥式全波整流器 电嗽叭 电铃 蜂鸣器 或 信号灯 可变电阻器 滑线式电阻器 滑动触点电位器 压敏电阻器 注:U 可用V 代替 热敏电阻器 注:Q 可用t °代替 加热元件 可变电容 器 具有两个电极的压电晶体 发光二极管一般符号 极性电容器 或 半导体二极管一般符 号 或 单向击穿二极管 双向击穿二极管 光敏电阻 光电池

安装图图形符号 气功或液压操作 导线的不连接 端子 插头和插座 三个独立绕组 三角形连接的三相绕组 中性点引出的星形 连接的三相绕组 三相串励换向器电动机 机 双绕组变压 三绕组变压 或 自耦变压器 避雷针 热电器 或 天线一般符号 无线电的一般符 号 动力或动力—照明配电箱 注:需要时符号可标示电流种类符号 屏、台、箱、号 照明配电箱(屏) 注:需要时允许涂红 信号板、信号箱(屏) 阀的一般符号 电滋阀 按钮一般符号 墨 单相插座 暗装的单相插座 密闭(防水)座 座 暗装的单相插座 密闭(防水)的单相插座 带接地插孔的三相插座 暗装的带接地插孔的三相插座 开关的一般符号 单极开关 双极开关

Allegro16.6约束规则设置详解 前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。 目录: 一、基本约束规则设置 1、线间距设置 2、线宽设置 3、设置过孔 4、区域约束规则设置 5、设置阻抗 6、设置走线的长度范围 7、设置等长 7.1、不过电阻的NET等长 7.2、过电阻的XNET等长 7.3、T型等长 8、设置通用属性 9、差分规则设置 9.1、创建差分对 9.2、设置差分约束 10、Pin Delay

二、高级约束规则设置 11、单个网络长度约束 12、a+b类长度约束 13、a+b-c类长度约束 14、a+b-c在最大和最小传播延迟中的应用

1、线间距设置 (1)、设置默认间距规则 点击CM图标,如下图所示,打开约束管理器。 单击Spacing,再点击All Layers,如下图所示。右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示 (2)、定义特殊的间距约束 点选Default按鼠标右键,执行Create-Spacing CSet

加入新规则。取一个有意义点的名字,如下图所示,单击OK。 其值是从默认规则拷贝的,先修改其值。 按住Shift键选中所有,输入12,回车。 然后为所需要设置的网络分配规则 单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示

本文介绍cadence软件的入门学习,原理图的创建、仿真,画版图和后仿真等一全套过程,本教程适合与初学着,讲到尽量的详细和简单,按照给出的步骤可以完全的从头到尾走一遍,本教程一最简单的反相器为例。 打开终端,进入文件夹目录,输入icfb&启动软件,主要中间有个空格。 启动后出现下图: 点击Tools的Library Manager,出现如下: 上面显示的是文件管理窗口,可以看到文件存放的结构,其中Library就是文件夹,Cell就是一个单元,View就是Cell的不同表现形式,比如一个mos管是一个Cell,但是mos管有原理图模型,有版图模型,有hspice参数模型,有spectre参数模型等,这就列举了Cell的4个View。他们之间是树状的关系,即,Library里面有多个Cell,一个Cell里面有多个View。应该保持一个好习惯就是每个工程都应该建立一个Library,Cell和View之间的管理将在后面介绍。

现在建立工程,新建一个Library,如下左图,出现的对话框如下有图: 在上右图中选择合适的目录,并敲入名字,这里取的是inv,这就是新建的文件夹的名字,以后的各种文件都在这个文件夹下。OK后出现下面对话框 这个对话框是选择是否链接techfile,如果只是原理图仿真而不用画版图,就选择Dont need a techfile,这里我们要画版图,而且有工艺库,选择Attach to an existing techfile,OK 后出现下面对话框:

在technology Library选择tsmc18rf,我们使用的是这个工艺库。Inv的文件夹就建好了,在Library Manager就有它了,如下图: 文件夹建好了后,我们要建立原理图,在inv的Library里面新建Cell如下:

常用低压电气图形符号和文字符号公司图纸常用电气图形符号和文字符号 FU 熔断器 HL 信号灯 EL 照明灯 PA A 电流表 PV V 电压表 PJ KWh 有功电度表 QF 断路器 QS 隔离开关

V 二极管 ~U 逆变器 ~ U 整流器 TA 形式1形式2 电流互感器 电压互感器 QL 负荷开关 QS 刀熔开关 T KM KM 接触器

文字符号 电气的文字符号目前执行国家标淮GB 5094—85《电气技术中的项目代号》和GB 7159—87《电气技术中的文字符号制定通则》。这两个标准都是根据IEC国际标准而制定的。 在GB 7159—87《电气技术中的文字符号制定通则》中将所有的电气设备、装置和元件分成23个大类,每个大类用一个大写字母表示。文字符号分为基本文字符号和辅助文字符号。基本文字符号分为单字母符号和双字母符号两种。单字母符号应优先采用,每个单字母符号表示一个电气大类,如表1-4所示。如C表示电容器类,R表示电阻器类等。 双字母符号由一个表示种类的单字母符号和另一个字母组成,第一个字母表示电器的大类,第二个字母表示对某电器大类的进一步划分。例如G表示电源大类,GB表示蓄电池,S表示控制电路开关,SB表示按钮,SP表示压力传感器(继电器)。 文字符号用于标明电器的名称、功能、状态和特征。同一电器如果功能不同,其文字符号也不同,例如照明灯的文字符号为EL,信号灯的文字符号为HL。 辅助文字符号表示电气设备、装置和元件的功能、状态和特征,由1~3位英文名称缩写的大写字母表示,例如辅助文字符号BW(Backward的缩写)表示向后,P(Pressure的缩写)表示压力。辅助文字符号可以和单字母符号组合成双字母符号,例如单字母符号K(表示继电器接触器大类)和辅助文字符号AC(交流)组合成双字母符号KA,表示交流继电器;单字母符号M(表示电动机大类)和辅助文字符号SYN(同步)组合成双字母符号MS,表示同步电动机。辅助文字符号可以单独使用,例如图1-29中的RD表示信号灯为红色。 图形符号 电气的图形符号目前执行国家标准GB 4728—85《电气图用图形符号》,也是根据IEC国际标准制定的。该标准给出了大量的常用电器图形符号,表示产品特征。通常用比较简单的电器作为一般符号。对于一些组合电气,不必考虑其内部细节时可用方框符号表示,如表1-4中的整流器、逆变器、滤波器等。 国家标准GB 4728—85的一个显著特点就是图形符号可以根据需要进行组合,在该标准中除了提供了大量的一般符号之外,还提供了大量的限定符号和符号要素,限定符号和符号要素不能单独使用,它相当于一般符号的配件。将某些限定符号或符号要素与一般符号进行组合就可组成各种电气图形符号,例如图1-8所示的断路器的图形符号就是由多种限定符号、符号要素和一般符号组合而成的,如图1-32所示。

CS/EE 5720/6720 – Analog IC Design Tutorial for Schematic Design and Analysis using Spectre Introduction to Cadence EDA: The Cadence toolset is a complete microchip EDA (Electronic Design Automation) system, which is intended to develop professional, full-scale, mixed-signal microchips. The modules included in the toolset are for schematic entry, design simulation, data analysis, physical layout, and final verification. The Cadence tools at our university are the same as those at most every professional mixed-signal microelectronics company in the United States. The strength of the Cadence tools is in its analog design/simulation/layout and mixed-signal verification and is often used in tandem with other tools for digital design/simulation/layout, where complete top-level verification is done in the Cadence tools. An important concept is that the Cadence tools only provide a framework for doing design. Without a foundry-provided design kit, no design can be done. The design rules used by Cadence set up in this class is based for AMI’s C5N process (0.5 micron 3 metal 2 poly process). So, how is Cadence set up? Broadly, there are three sets of files that need to be in place in order to use Cadence. 1)The Cadence tools These are the design tools provided by the Cadence company. These tools are located in the /home/cadence directory. They are capable of VLSI integration, project management, circuit simulation, design rule verification, and many other things (most of which we won't use). 2)The foundry-based design kit As mentioned before, the Cadence tools have to be supported by a foundry-based design kit. In this class, we use Cadence design kit developed by the North Carolina State University (NCSU CDK). NCSU CDK provides an environment that has been customized with several technology files and a fair amount of custom SKILL code. These files contain information useful for analog/full- custom digital CMOS IC design via the MOSIS IC fabrication service (https://www.doczj.com/doc/dc7034667.html,). This information includes layer definitions (e.g. colors, patterns, etc.), parasitic capacitances, layout cells, SPICE simulation parameters, Diva rules for Design Rule Check (DRC), extraction, and Layout Versus Schematic (LVS) verification, with various GUI enhancements. For more information on the capability of the NCSU CDK, go to https://www.doczj.com/doc/dc7034667.html,/CDKoverview.html

序号元件名称新符号旧符号 1 继电器K J 2 电流继电器 KA LJ 3 负序电流继电器KAN FLJ 4 零序电流继电器KAZ LLJ 5 电压继电器 KV YJ 6 正序电压继电器KVP ZYJ 7 负序电压继电器KVN FYJ 8 零序电压继电器KVZ LYJ 9 时间继电器 KT SJ 10 功率继电器KP GJ 11 差动继电器KD CJ 12 信号继电器KS XJ 13 信号冲击继电器 KAI XMJ 14 继电器 KC ZJ 15 热继电器 KR RJ 16 阻抗继电器KI ZKJ 17 温度继电器KTP WJ 18 瓦斯继电器KG WSJ 19 合闸继电器KCR或KON HJ 20 跳闸继电器KTR TJ

21 合闸继电器 KCP HWJ 22 跳闸继电器 KTP TWJ 23 电源监视继电器 KVS JJ 24 压力监视继电器 KVP YJJ 25 电压继电器 KVM YZJ 26 事故信号继电器 KCA SXJ 27 继电保护跳闸出口继电器 KOU BCJ 28 手动合闸继电器 KCRM SHJ 29 手动跳闸继电器 KTPM STJ 30 加速继电器KAC或KCL JSJ 31 复归继电器KPE FJ 32 闭锁继电器KLA或KCB BSJ 33 同期检查继电器 KSY TJJ 34 自动准同期装置 ASA ZZQ 35 自动重合闸装置 ARE ZCJ 36 自动励磁调节装置AVR或AAVR ZTL 37 备用电源自动投入装置 AATS或RSAD BZT 38 按扭 SB AN 39 合闸按扭 SBC HA 40 跳闸按扭 SBT TA 41 复归按扭 SBre或SBR FA

Allegro PCB Editor如何绕等长 在高速PCB设计中,解决信号完整性中相对传输延迟最通常的做法就是对关键信号进行绕等长处理!该解决方案就是来看怎么在PCB Editor中实现绕等长布线。 关键字: cadence、cadence PCB SI、相对传输延迟、等长 ◆上海库源电气科技有限公司 ◆PSpice技术支持中心: https://www.doczj.com/doc/dc7034667.html, ◆技术支持热线:4006-535-525 ◆Mail: support@https://www.doczj.com/doc/dc7034667.html, ◆Web:https://www.doczj.com/doc/dc7034667.html, 2012-6-18

Allegro PCB Editor绕等长布线 所需软件:Cadence PCB Editor 在开始真正绕等长的步骤之前需要我们解答两个问题: 1、需不需要绕等长? 只有高速信号才会产生信号匹配的问题,才需要绕等长,一般界定速度超过100M或者信号上升时间小于50ps的为高速信号。 2、为什么要绕等长? 由上面简图可以看到,由于信号速度很快,如果同组信号(比如地址线)之间传输延迟相差太大,发送端的信号传送到接收端时就会产生bit位错误或者在接收端无法达到足够的建立保持时间而导致接收端无法正确接收发送端的信号,对同组线要约束其相对传输延迟,所以才要绕等长使同组线间传输延迟在一定的范围内,保证信号正确传输。 步骤: 1、使用PCB Editor打开工程文件。 2、打开约束管理器,在相应网络上右击,选择“SigXplorer”提取需要设置等长的拓扑结 构

3、提取拓扑结构,在“SigXplorer”中设置约束并返回到PCB中, 红框中是设置约束规则的快捷键,为返回约束的快捷键。 图中最大红框的位置是设置拓扑约束的对话框。在“Pins/Tees”中选择需要设置等长约束的起始Pin和终止Pin,因为本例中提取拓扑结构时是一束总线,所以本例中“From”处选择“ALL DRVRS”,“TO”处选择“ALL RCVRS”,意为对提取的这束线的所有发送端到接收端设置约束,在“Delta Type”中选择约束用的单位(时间,或者长度)。然后在Delta中输入本束线中所有线之间的误差值,在“Tol Type”中输入基于这个“Delta”值的误差值的单位。“Tolerance”是在“Delta”基础上的误差值。

地质像素符号常有助于钻探数据的记录与解读,本规范「工程地质像素符号」主要是用在钻孔柱状图上,以「目视判别」的结果为主。目前国内各相关单位现行所使用之「工程地质像素符号」并不一致,为建立一致之共识,并争取广泛的支持,本规范「工程地质像素符号」乃依据我国中央标准局所制订之国家标准「CNS6589」、「CNS6590」、「CNS 6591」等编订之。本次工程地质像素符号之修订工作,期配合行政院公共工程委员会之制图手册加以整合(如对照表备注所列),而使「国土信息系统自然环境基本数据库分组—工程地质探勘数据库」更能得到政府机关及工程实务界之支持与使用。 本规范将地质像素分为「土壤或沉积物」、「沉积岩」、「变质岩」及「火成岩」等四大类,再将每一类像素区分为「基本型」及「混合衍生与变异型」两个类别,并将其分别表列。对于某些业务,如果「基本型」之地质像素符号即已够用,那么「混合衍生与变异型」之像素符号,即可将其视为「备而不用」,如此将可有助于相关作业的简化。 为了方便用户选用像素符号,我们也配合设计了分类代码表。「0」代表粗分类,如果相关数据只需记录其为岩石或土壤,则可采用此粗分类记录方式。「奇数前缀」的代码,代表「基本型像素」,「偶数前缀」的代码为「混合衍生及变异型像素」。因此,本规范「工程地质像素符号」共可分为以下九大类: 0、粗分类(基本型) 1、土壤或沉积物类(基本型) 2、土壤或沉积物类(混合衍生与变异型) 3、沉积岩类(基本型) 4、沉积岩类(混合衍生与变异型)

5、变质岩类(基本型) 6、变质岩类(混合衍生与变异型) 7、火成岩类(基本型) 8、火成岩类(混合衍生与变异型)

Cadence 系列软件从schematic到layout入门 一.客户端软件使用及icfb启动 要使用工作站上的软件,我们必须在PC中使用xwinpro等工具连接到工作站上。从开始菜单中,运行xwinpro的xSettings,按照下图设置: 点击上图的Settings在出现的窗口中按如下设置(connect host选择为192.168.1.137):

设置完后,从开始菜单中运行xwinpro的xsessions,应该就可以进入登陆界面,用户名为user1,密码为root。 二、Schematic Cadence系列软件包含了电路图工具Schematic,晶体管级电路仿真工具Spectre,以及版图工具Virtuoso等。一般来说,我们先用Schematic画好电路原理图然后进行仿真,最后用Virtuoso手动画版图或者直接进行版图综合,最后对版图进行L VS,DRC等验证。 在登陆进工作站后,点击鼠标右键,选择tools——>terminal,在弹出的terminal窗口中敲入命令icfb&就可以启动cadence了。 图1 icfb的主界面 我们以建立一个反相器电路为例子: 在icfb中,任何一个电路,不论是已经存在的可以引用的库,还是用户新建立的一个电路,都是一个library. 一个library一般有若干个Cell(单元电路),每个cell有若干个

schematic(电路原理)和若干个layout(版图)。所以,我们要做的第一步,就是先创建一个自己的“库”,File菜单->new->library 图2 新建一个库的界面 从这个新建一个library的界面,我们必须输入新建立的库的名称,并且选择好这个库应该存放的目录,然后注意看右边的三个选项,关于新建立的库是否需要链接到Technology File 的问题。首先,这个Technology File一般是指工艺库,由Foundry提供。如果最终做的电路是需要画出Layout(版图)的,就必须要有工艺库,如果不需要画Layout,那就可以不需要工艺库。由于我们需要演示这一步,所以就选择Attach to an existing techfile。(也可以在建立之后,再Attach to an existing techfile)。 输入name: testinv, (大家在做的时候自己起一个名字)。 现在,我们就已经建立好了一个新的“库”,为了给这个库增加schematic(电路图)和Layout(版图)我们就必须对这个库进行“管理”,从icfb的主菜单(图1)中的Tools菜单->Library Manager.

开关 多级开关一般符号单线表示 多级开关一般符号多线表示 接触器 位置触点断开 接触器 位置触点闭合 负荷开关 离开关 具有自动释放功能的负荷开关 熔断器式断路器断路器 隔离开关 熔断器一般符号跌落式熔断器 熔断器式开关 熔断器式隔离开关熔断器式负荷开关

当操作器件被吸合时延时闭合的动合触点 当操作器件被释放时延时闭合的动合触点 当操作器件被释放时延时闭合的动断触点 当操作器件被吸合时延时闭合的动断触点 当操作器件被吸合时延时闭合和释放时延时断开的动合触点 按钮开关 旋钮开关、旋转开关 位置开关 点 限制开关 点 位置开关 点 限制开关 点

热敏开关 点 注 代替 热敏自动开关,动断触点 注:注意区别此触点和下图所示热继电器的触点 具有热元件的气体放电管荧光灯起动器 动合 注 作开关一般符号动断 先断后合的转换触点 当操作器件被吸合或释放时 合的过渡动合触点 座 的一个极 插头 头的一个极 插头和插座 的和内孔的

接通的连接片 换接片 双绕组变压器 三绕组变压器 自耦变压器 电抗器 扼流图 电流互感器 脉冲变压器 具有两个铁芯和两个二次绕组的电流互感器 在一个铁芯上具有两个二次绕组的电流互感器 具有有载分接开关的三相三绕组变压器,有中性点引出线的星形 连接 三相三绕组变压器,两个绕组为有中性点引出线的星形,中性点接地,第三绕组为开口三角形连接

三相变压器 星形 具有有载分接开关的三相变压器 形 三相变压器 星形 操作器件一般符号 具有两个绕组的操作器件组合表示法 热继电器的驱动器件 气体继电器 自动重闭合器件电阻器一般符号 可变电阻器 可调电阻器 滑动触点电位器

Cadence等长处理 对于时序处理而言,在板上实现的手段就是绕等长。作为一个合格的layout工程师,首先必须得是一个合格的"绕等长"工程师,毕竟一切从助手做起。 一般来说,我们绕等长在allegro软件就只有一个命令Delay Tune,感觉有点不够用。现在给大家安利一下allegro16.6关于绕等长推出的新功能,所有命令如下图所示。 首先是Timing Vision,个人觉得这真是一个实用的技能,很人性化。以前绕等长的时候,哪一根 最长,哪一根最短,绕到最后,哪一根没有绕好等等,都需要一个个去板子上找,或者去规则管理 器里头选择,简直是神烦。这个功能直接让比基准长的显示一种颜色,比基准短的显示一种颜色, 绕好的显示一种颜色,一目了然,直接绕就好,不需要再去规则管理器里面查看了。 接着是期待已久的自动绕等长了——Auto-interactive Delay Tune。想当年,刚开始学习layout 的时候,就是从绕等长开始,一块又一块的板子,能做的只有绕等长,当时就想,要是有一天机器 可以自动绕等长就好,今天这个愿望果然实现了。自动等长的步骤很简单,设置好等长规则后,只 需要选择Auto-interactive Delay Tune命令,然后框选想要等长的线就好,机器就可以自己运算,然后就可以看到已经绕好的等长了,真是简单粗暴到极点了。不说了,有图有真相。

有了单线的自动等长,那就肯定不会放过板上随处可见的差分了,看大招——Auto-interactive Phase Tune。现在板子的速率越来越高,板上的差分线也就跟着越来越多,对内等长的工作量自然就加大了。但是自从有了绕线新功能,就再也不担心绕等长费时多啦。步骤和单线绕等长一样,简单明了。

A llegro中的约束规则设置 Allegrophan 刚好五个字

修订记录 日期版本描述作者2008-12V1.0初版,学完的总结。适用于Cadence15.5版本。Allegrophan 2009-09-08V1.1小改,修改部分措辞Allegrophan 2009-10-14V1.2小改,更正、修改几个错漏之处。添加一些说明性文字。 感谢群里的佳猪、梦姑娘等朋友的指正! Allegrophan

目录 一:Physical(Line/vias)rule物理特性(线宽和过孔)约束设置: (4) 1)“Set values”设置约束特征值 (5) 2)“Attach property”绑定约束 (6) 3)“Assignment table”约束规则分配 (8) 二“Spacing rule”间距约束设置 (9) 1)“Set values”设置约束特征值 (9) 2)“Attach property”绑定约束 (10) 3)“Assignment table”约束规则分配 (11) 三Constraint areas区域约束设置 (12) 四Allegro中走线长度的设置 (13) 1)差分线等长设置 (13) 2)一组Net等长 (16) 3)XNet等长 (17)

线宽、线距、区域的约束主要在“Constraints Sys ”中设置,点击“Setup/Constraints ”或点击图标打开“Constraints Sys ”窗口,如下: “Constraints Sys ”窗口分两个级别,第一级别有两类:Standard design rules 和Exte Extended nded design rules 。Standard design rules 仅有一级分类,点击“Set standard values ”设置默认约束值,如下:

Cadence SPB15.7 快速入门视频教程目录 第1讲课程介绍,学习方法,了解CADENCE软件 第2讲创建工程,创建元件库 第3讲分裂元件的制作方法 区别(Ctrl+B、Ctrl+N切换Part) 点击View,点击Package可以显示所有的元件Part 1、homogeneous 和heterogeneous 2、创建homogeneous类型元件 3、创建heterogeneous类型元件 第4讲正确使用heterogeneous类型的元件 增加packeg属性。点击Option,选择Part Properties,选择new,增加属性。用于在原理图中确定同一块的元件。 1、可能出现的错误 2、出现错误的原因 3、正确的处理方法 第5讲加入元件库,放置元件 1、如何在原理图中加入元件库 2、如何删除元件库 3、如何在元件库中搜索元件 4、放置元件 5、放置电源和地 第6讲同一个页面内建立电气互连(设置索引编号,Tools里面,Annotate来设置) 1、放置wire,90度转角,任意转角(画线时按住Shift) 2、wire的连接方式 3、十字交叉wire加入连接点方法,删除连接点方法(快捷键J) 4、放置net alias方法(快捷键n) 5、没有任何电气连接管脚处理方法(工具栏Place no Conection) 6、建立电气连接的注意事项 第7讲总线的使用方法 1、放置总线(快捷键B) 2、放置任意转角的总线(按住Shift键) 3、总线命名规则(LED[0:31],不能数字结尾) 4、把信号连接到总线(工具栏Place Bus entry 或者E) 5、重复放置与总线连接的信号线(按住Ctrl向下拖) 6、总线使用中的注意事项 7、在不同页面之间建立电气连接(工具栏Place off-page connector) 第8讲browse命令的使用技巧(选中dsn文件,选择Edit中的browse) 1、浏览所有parts,使用技巧(浏览元件<编号,值,库中的名字,库的来源>,双击元件可在原理图上找到元件) 2、浏览所有nets,使用技巧(浏览网络) 3、浏览所有offpage connector,使用技巧(页面间的连接网络,一般一个网络至少会在两个页面中出现) 4、浏览所有DRC makers,使用技巧(DRC检测)

附件是一篇网上找到的文章,此文详细介绍了如何设置Xnet以及进行等长设置走线。本人的应用相对更简单,由于不是经常画板子,所以对于如何使用Xnet常常忘记,而本文介绍的相对复杂,为了在每次画板子的时候相对快速的使用Xnet,特记录本人使用Xnet的过程于此。 首先,介绍本人为何要使用Xnet。本人使用Xnet的场合主要有两种场合,一种是走线路径阻抗匹配,所以走线中串接了一个匹配电阻,如果需要等长,所以要给这一组走线设置Xnet;另一种是高速差分走线以及像Altera的高速Transciever的差分走线一般都需要对高速差分线进行AC耦合,所以每根线上串接了一个0.1uF的电容,而差分走线都需要进行等长,所以需要计算电容两端走线之和来进行等长控制。 如果没有建立Xnet,如图1所示的差分走线的每一根就会分为2段net。那么在Allegro的约束管理器中进行等长设置的时候需要首先建立差分对(Diff pair),这时候你会发现有图2所示的情况出现。从图2能发现什么呢?即RX1_T_N和RX2_T_N的“type”是不一样的,显然RX1_T_N的type是net而RX2_T_N 的type是Xnet,也就是在建立差分对约束的时候前者只是约束了一部分,而后者是约束了整根线。 图1 Altera的GXB高速接收通道 图2 在Allegro16.3的约束管理器中建立建立差分对 根据文章介绍,第一步是要建立Xnet,建立Xnet的过程如下所示 第1步,在Allegro的PCB Editor的Analyze菜单下选择SI/EMI Sim->Model Assignment命令,如图3所示