《数字信号处理》课程设计报告 设计课题滤波器设计与实现 专业班级电信1101班 姓名 学号 201105 报告日期2013年12月

《数字信号处理》 课程设计任务书 题目滤波器设计与实现 学生姓名甘源滢学号201105020103 专业班级电信1101班 设计内容与要求一、设计内容: 设计一个模拟低通巴特沃斯滤波器,技术指标:通带截止频率1000rad,通带最大衰减1dB;阻带起始频率5000rad,阻带最小衰减30dB,画出其幅度谱和相位谱。 二、设计要求 1 设计报告一律按照规定的格式,使用A4纸,格式、封面统一给出模版。 2 报告内容 (1)设计题目及要求 (2)设计原理(包括工作原理、涉及到的matlab函数的说明) (3)设计内容(设计思路,设计流程、仿真结果) (4)设计总结(收获和体会) (5)参考文献 (6)程序清单 起止时间2013年12 月16日至2013年12月23 日指导教师签名2013年12月10日系(教研室)主任签名2013年12 月12 日学生签名2013年12月13日

目录 1课题描述 (1) 1.1报告介绍 (1) 2设计原理 (2) 2.1巴特沃斯低通模拟滤波器的设计原理 (2) 2.2低通巴特沃斯滤波器的设计步骤如下 (3) 2.3函数说明 (3) 2.3.1buttord函数 (3) 2.3.2butter函数 (4) 2.4模拟低通滤波器的性能指标 (4) 3设计内容 (5) 3.1MATLAB简介 (5) 3.2巴特沃斯滤波器的设计步骤 (6) 3.3对巴特沃斯低通模拟滤波器的仿真 (6) 4实验结果分析 (7) 5实验心得体会 (7) 6程序清单 (8) 7参考文献 (9) 1.课题描述 1.1报告介绍 模拟滤波器的理论和设计方法已经发展的相当成熟,且有多种典型的滤波器供我们选择,如巴特沃斯(butterworth)滤波器,切比雪夫(chebyshev)滤波器,椭圆(ellipse)滤波器,贝塞尔(bessel)滤波器等。这些滤波器都有着严格的设计公式,现成的曲线和图表供设计人员使用,而且所设计的系统函数都满足电路实现条件。这些典型的滤波器各有特点:巴特沃斯滤波器具有单调下降到幅频特性;切比雪夫滤波器的幅频特性在带通或者阻带有等波纹特性,可以提高选择性;贝塞尔滤波器通带内有较好的线性相位特性;椭圆滤波器的选择性相对前三种是

数字信号处理实验报告 设计题目:数字信号处理设计与仿真分析 学院:电子工程学院 专业: 班级: 学号: 姓名: 电子邮件: 日期: 成绩: 指导教师:

题目:数字信号处理设计与仿真分析 1. 引言 实验要求 (1) 建立两个模拟信号的数学模型s a1(t)和s a2(t),其中s a1(t)是有用信号,s a2(t) 是干扰信号。两个信号的中心频率、信号带宽等参数由学生自己选定,要求两个信号的频谱不重叠,s a2(t)的幅度比s a1(t)的幅度高20dB ,两个信号时域叠加得到合成信号x a (t),即 x a (t)= s a1(t)+ s a2(t) 设计计算机程序仿真产生s a1(t)、s a2(t)、x a (t)信号,分别画出三个模拟信号的时域波形和频谱图; (2) 根据x a (t)的中心频率和带宽,按照奈奎斯特采样定理选择采样频率f s ,分 别对信号s a1(t)、s a2(t)、x a (t)进行时域采样,得到离散信号s 1(n)、s 2(n)、x(n)。利用FFT 算法分析离散信号的频谱,分别画出三个离散信号的时域波形和频谱图; (3) 设计数字滤波器H(z),要求该滤波器对干扰信号s 2(n)的衰减大于40dB 。提 出滤波器的设计指标,并设计滤波器,给出滤波器的设计结果,绘制滤波器的幅频特性和相频特性曲线,验证滤波器的设计结果是否达到设计指标要求; (4) 选择实现数字滤波器H(z)的结构,画出结构信号流图; (5) 将合成信号x(n)输入数字滤波器H(z),按照所选择的滤波器结构,设计计 算机程序计算滤波器的输出响应y(n),画出y(n)的时域波形和频谱图; (6) 分析、总结设计结果,提交课程设计报告。 实验目的 (1) 深入理解信号的采样过程、模拟信号与离散信号的特点、时域采样定理。 (2) 熟悉数字滤波的基本概念、数字滤波器的主要技术指标及其物理意义。 (3) 了解模拟和数字滤波器的频率变换、IIR 数字滤波器的直接(优化)设计方 法。

PCB设计挑战和建议作为PC、服务器和消费电子产品中重要的硬盘驱动器接口,串行ATA(SATA)发展迅猛并日益盛行。随着基于磁盘的存储在所有电子市场领域中变得越来越重要,系统设计工程师需要知道采用第一代SATA(1.5Gbps)和第二代SATA(3.0Gbps)协议的产品设计中的独特挑战。此外,系统设计工程师还需要了解新的SATA特性,以使其用途更广,功能更强,而不仅仅是简单地代替并行ATA。充分利用这些新特性并克服设计中存在的障碍,对成功推出采用SATA接口的产品非常关键。 日趋复杂的PCB布局布线设计对保证高速信号(如SATA)的正常工作至关重要。由于第一代和第二代SATA的速度分别高达1.5Gbps和3.0Gbps,因此铜箔蚀刻线布局的微小改动都会对电路性能造成很大的影响。SATA信号的上升时间约为100ps,如此快的上升时间,再加上有限的电信号传输速度,所以即使很短的走线也必须当成传输线来对待,因为这些走线上有很大部分的上升(或下降)电压。 高频效应处理不好,将会导致PCB无法工作或者工作起来时好时坏。为保证采用FR4 PCB板的SATA设计正常工作,必须遵守下面列出的FR4 PCB布局布线规则。这些规则可分为两大类:设计使用差分信号和避免阻抗不匹配。 高速差分信号设计规则包括: 1.SATA是高速差分信号,一个SATA连接包含一个发送信号对和一个接收 信号对,这些差分信号的走线长度差别应小于5mil。使差分对的走线长度保持一致非常重要,不匹配的走线长度会减小信令之间的差值,增加误码率,而且还会产生共模噪声,从而增加EMI辐射。差分信号线对应该 在电路板表层并排走线(微带线),如果差分信号线对必须在不同的层走 线,那么过孔两侧的走线长度必须保持一致。 2.差分信号线对的走线不能太靠近,建议走线间距是走线相对于参考平面高 度的6至10倍(最好是10倍)。 3.为减少EMI,差分对的走线间距不要超过150mil。 4.SATA差分对的差分阻抗必须为100欧姆。 5.为减少串扰,同一层其它信号与差分信号线对之间的间距至少为走线相对 于参考平面高度的10至15倍。 6.在千兆位传输速度的差分信号上不要使用测试点。 避免阻抗不匹配的设计规则包括:

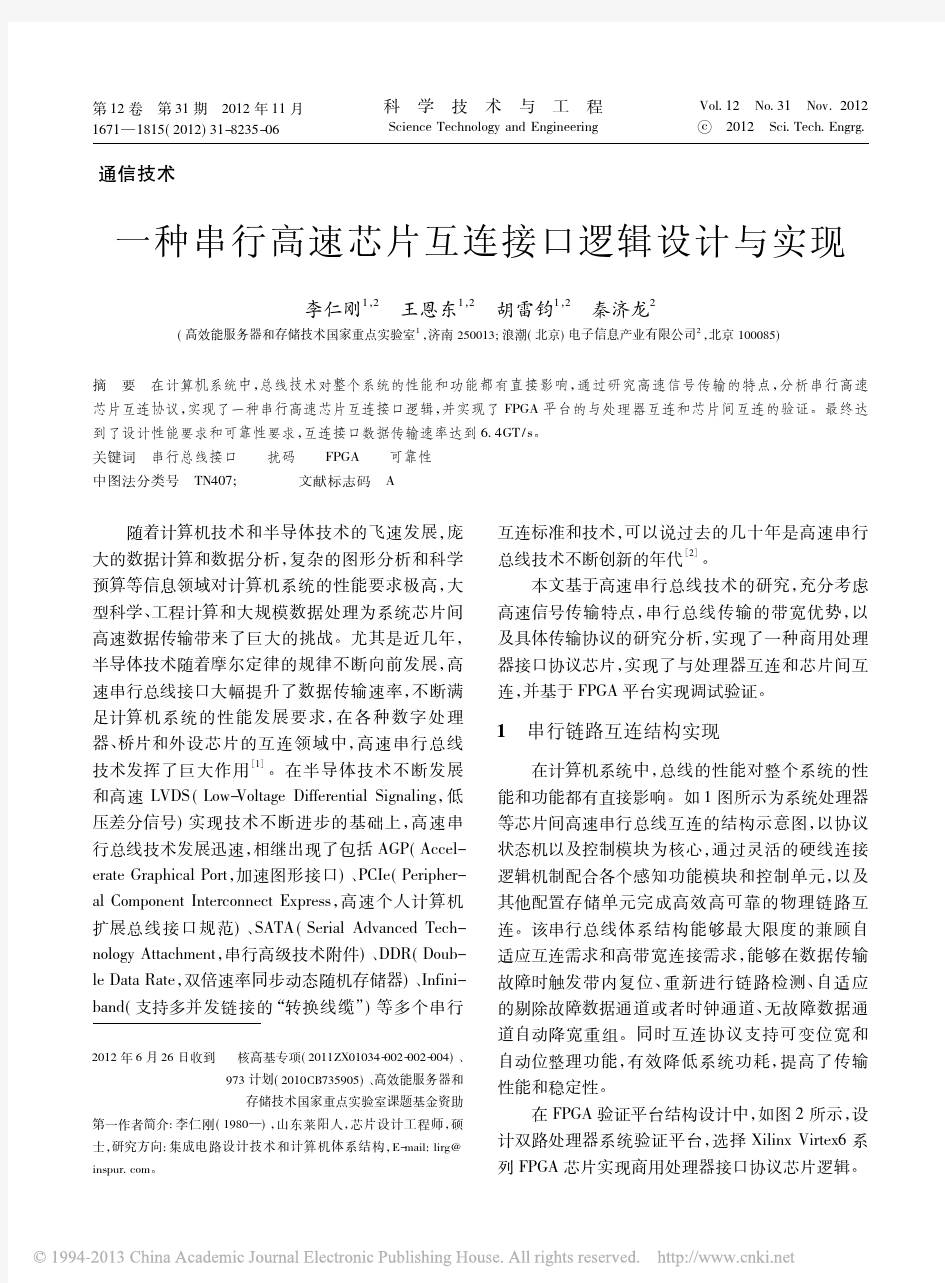

随着对信息流量需求的不断增长,传统并行接口技术成为进一步提高数据传输速率的瓶颈。过去主要用于光纤通信的串行通信技术——SERDES正在取代传统并行总线而成为高速接口技术的主流。本文阐述了介绍SERDES收发机的组成和设计,并展望了这种高速串行通信技术的广阔应用前景。 SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。它是一种时分多路复用(TDM)、点对点的通信技术,即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本。 SERDES技术最早应用于广域网(WAN)通信。国际上存在两种广域网标准:一种是SONET,主要通行于北美;另一种是SDH,主要通行于欧洲。这两种广域网标准制订了不同层次的传输速率。目前万兆(OC-192)广域网已在欧美开始实行,中国大陆已升级到2.5千兆(OC-48)水平。SERDES技术支持的广域网构成了国际互联网络的骨干网。 SERDES技术同样应用于局域网(LAN)通信。因为SERDES技术主要用来实现ISO模型的物理层,SERDES通常被称之为物理层(PHY)器件。以太网是世界上最流行的局域网,其数据传输速率不断演变。IEEE在2002年通过的万兆以太网标准,把局域网传输速率提高到了广域网的水平,并特意制订了提供局域网和广域网无缝联接的串行WAN PHY。与此同时,SERDES技术也广泛应用于不断升级的存储区域网(SAN),例如光纤信道。 随着半导体技术的迅速发展,计算机的性能和应用取得了长足进步。可是,传统并行总线技术——PCI 却跟不上处理器和存储器的进步而成为提高数据传输速率的瓶颈。新一代PCI标准PCI Express正是为解决计算机IO瓶颈而提出的(见表1)。PCI Express是一种基于SERDES的串行双向通信技术,数据传输速率为2.5G/通道,可多达32通道,支持芯片与芯片和背板与背板之间的通信。国际互联网络和信息技术的兴起促成了计算机和通信技术的交汇,而SERDES串行通信技术逐步取代传统并行总线正是这一交汇的具体体现。 SERDES系统的组成和设计 基于SERDES的高速串行接口采用以下措施突破了传统并行I/O接口的数据传输瓶颈:一是采用差分信号传输代替单端信号传输,从而增强了抗噪声、抗干扰能力;二是采用时钟和数据恢复技术代替同时传输数据和时钟,从而解决了限制数据传输速率的信号时钟偏移问题。 一个典型SERDES收发机由发送通道和接收通道组成(见图1):编码器、串行器、发送器以及时钟产生电路组成发送通道;解码器、解串器、接收器以及时钟恢复电路组成接收通道。顾名思义,编码器和解码器完成编码和解码功能,其中8B/10B、64B/66B和不规则编码(scrambling)是最常用的编码方案。串行器和解串器负责从并行到串行和从串行到并行的转换。串行器需要时钟产生电路,时钟发生电路通常由锁相环(PLL)来实现。解串器需要时钟和数据恢复电路(CDR),时钟恢复电路通常也由锁相环来实现,但有多种实现形式如相位插植、过剩抽样等。发送器和接收器完成差分信号的发送和接收,其中LVDS和CML是最常用的两种差分信号标准。另外还有一些辅助电路也是必不可少的,例如环路(loopback)测试、内置误码率测试等等。 通信标准制订了严格的性能指标以确保系统的可靠性和互用性。SERDES芯片的主要性能指标包括抖动产生、抖动容忍、抖动转移以及系统误码率(BER)等。抖动产生取决于时钟发生电路特别是压控振荡器(VCO)的相位噪声;抖动容忍取决于时钟恢复电路容忍抖动的能力,而抖动转移是在用作中继器时必须满足的指

《DSP技术与应用---基于TMS320C54X》 实验指导书 湘潭大学信息工程学院 姚志强 2010.09.23

TMS320VC5402 DSK使用注意事项 1) 先用并口电缆和串口线(用到的话)将TMS320VC5402DSK与PC机相连, 而后再将电源接上,打开Code Composer Studio(简称CCS)后有可能报TMS320VC5402DSK和PC机未能连上的错误,可在PC机的CMOS_BIOS重新设置并行口的特性。 2) 将TMS320VC5402DSK上的DIP Switches的5、6置ON,其它置OFF。 3) 要在关闭CCS后及在断电的情况下插拔USB电缆线和串口线。 4) 强烈建议不要带电插拨串口,插拨时至少有一端是断电的,否则串口容 易损坏。 5) TMS320VC5402DSK电路板上大多是CMOS集成电路,为防止静电击毁, 在拿出实验电缆后请立即将玻璃盖复原,任何时候都请不要用手及其它带电物体直接和电路板接触。 实验报告的撰写 1) 每个实验都单独写实验报告。 2) 实验要求和目的; 3) 实验主要内容; 4) 看懂程序代码,并画出程序流程图; 5) 作出硬件描述(如果与DSK板硬件有关); 6)实验结果和心得。 实验注意事项 1) 实验项目所建工程文件统一放在F:\TI\CCS\myprojects下,其余盘在重启后会复原。 2) 实验过程中,不要涉及到中文路径(CCS不支持),包括CCS程序安装路径、文件添加路径、实验源文件名称等。 3) 实验七CODEC语音回放实验用到DSK板,需要自带耳麦,请准备好。

实验一 CCS的安装与CCS操作界面的熟悉 一、实验目的 学会安装与设置Code Composer Studio。 熟悉CCS软件的操作界面。 二、实验设备 CCS安装光盘(本次安装程序在D:\DSP\ccs2.0ForC5000)、装有Windows 98以上操作系统的PC机 三、实验内容及步骤 https://www.doczj.com/doc/d014329679.html,S的安装 安装前需要卸载系统原来的C5000,进入控制面板进行卸载完毕后,再开始下面的步骤。 (1)找到CCS的安装软件,点击安装程序setup.exe,双击启动安装。安装完成后在 桌面上会有“CCS 2 C5000”和“SETUP CCS 2 C5000”两个快捷方式图标,分别对应CCS应用程序和CCS配置程序。 (2)双击运行“SETUP CCS 2 C5000”配置程序,配置驱动程序。本次实验没有用到实验箱,只需配置软件驱动程序。在弹出的“Import Configurantions”对话框中,先点击“Clear”键,清除以前的配置,然后选择“C5402 Simulator”,点击“Import”,最后点击“Save and Quit”按钮,完成配置。 https://www.doczj.com/doc/d014329679.html,S操作界面的熟悉 (1)在桌面上双击“CCS 2 C5000”,弹出一个TI仿真器并行调试管理器窗口。 (2)在管理器窗口的“open”菜单下选择“C54xx(C5402) Simulator”命令,将弹出一个CCS运行主窗口(如果直接弹出CCS运行主窗口,此步可略)。 (3) 点击Help_>Contents打开TMS320C54x Code Composer Stdio Help,在左边Contents列表中点击最后一个TMS320C5402 DSK,浏览了解其下所有子列表的内容,熟悉DSK板的基本硬件、配置及功能。 (4)对照教材介绍CCS的地方,逐一熟悉CCS中的12项菜单的功能,包括File、Edit、View、Project、Debug、Profiler、Option、GEL、Tools等菜单(结合实验二建立项目熟悉更好)。 (5)对照教材,逐一熟悉CCS的五种工具栏:Standard Toolbar、GEL Toolbar、Project Toolbar、Debug Toolbar、Edit Toolbar(结合实验二建立项目熟悉更好)。

高速信号走线规则 随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的关注。 高速PCB设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。 规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。如上图所示。 规则二:高速信号的走线闭环规则 由于PCB板的密度越来越高,很多PCB LAYOUT工程师在走线的过程中,很容易出现这种失误,如下图所示: 时钟信号等高速信号网络,在多层的PCB走线的时候产生了闭环的结果,这样的闭环结果将产生环形天线,增加EMI 的辐射强度。 规则三:高速信号的走线开环规则 规则二提到高速信号的闭环会造成EMI辐射,同样的开环同样会造成EMI辐射,如下图所示:

时钟信号等高速信号网络,在多层的PCB走线的时候产生了开环的结果,这样的开环结果将产生线形天线,增加EMI 的辐射强度。在设计中我们也要避免。 规则四:高速信号的特性阻抗连续规则 高速信号,在层与层之间切换的时候必须保证特性阻抗的连续,否则会增加EMI的辐射,如下图: 也就是:同层的布线的宽度必须连续,不同层的走线阻抗必须连续。 规则五:高速PCB设计的布线方向规则 相邻两层间的走线必须遵循垂直走线的原则,否则会造成线间的串扰,增加EMI辐射,如下图: 相邻的布线层遵循横平竖垂的布线方向,垂直的布线可以抑制线间的串扰。 规则六:高速PCB设计中的拓扑结构规则 在高速PCB设计中有两个最为重要的内容,就是线路板特性阻抗的控制和多负载情况下的拓扑结构的设计。在高速的情况下,可以说拓扑结构的是否合理直接决定,产品的成功还是失败。 如上图所示,就是我们经常用到的菊花链式拓扑结构。这种拓扑结构一般用于几Mhz的情况下为益。高速的拓扑结构我们建议使用后端的星形对称结构。

基于FPGA的键盘接口设计 专业:电子信息科学与技术系作者:李先仙指导老师:刘强摘要:现场可编程逻辑门阵列FPGA (Field Programmalbe Gate Array)具有掩膜可编程门阵列的通用结构,由逻辑功能块排成阵列组成,并由可编程的互联资源连接这些逻辑功能块以及相应的输入/输出单元来实现不同的设计。在电子产品中,键盘是最基本的输入设备,然而在应用中都采用通用的键盘扫描器件是不现实的,需要单独设计成专用的小键盘。随着电子技术和EDA (Electronic Design Automatic,电子设计自动化)技术的发展,大规模可编程逻辑器件PLD(Programmable Logic Device)、现场可编程门阵列FPGA完全可以取代大规模集成电路芯片,实现计算机可编程接口的功能,并可将若干接口电路的功能集成到一片PLD或FPGA芯片中。鉴于大规模PLD或FPGA的计算机接口电路不仅具有集成度高、体积小和功耗低等优点,而且还具有独特的用户可编程能力,从而实现计算机系统的功能重构。本文设计首先介绍行列式键盘的原理和应用,通过对其接口电路的详细分析;然后利用VHDL硬件描述语言和FPGA器件并采用模块化设计的方法完成了基于FPGA的行列式键盘接口电路的设计;最后通过计算机仿真,对本文设计的行列式键盘接口电路的正确性进行了验证。 关键词:键盘;仿真;VHDL语言;FPGA;模块化设计 Based on FPGA Keyboard Connection Design Major:Electronic Information Science and Technology Author: Li Xianxian Instructor: Liu Qiang Abstract: The Filed Programmmalbe Gate Array,shorted by FPGA,which has a mask-programmable gate array of generic structure and function blocks in the logic array of line,through a programmable logic of internet resources connecting these function blocks and the corresponding input/output modules to achieve different design.In electronic products,the keyboard is the most basic input device,however,it’s unrealistic of using general keyboard scanning device in the application ,we need for the separate designing of the small keyboard. With the development of Electronic and EDA(Electronic Design Automatic)technology,Large Scale Integration chips can be replaced by PLD(Programmable Logic Device)and FPGA ,which can realize the function of the Programmable Interface chips and feature a number of interface circuits integated into one of the PLD or FPGA chips.The computer interface circuit based on the technology of PLD and FPGA not only has the virtue of high integration,low volume and low power loss, but also has the unique programmable function,which can realize

目前ADDA的常用芯片简介 目前AD/DA的常用芯片简介 目前生产AD/DA的主要厂家有ADI、TI、BB、PHILIP、MOTOROLA等,武汉力源公司拥有多年从事电子产品的经验和雄厚的技术力量支持,已取得排名世界前列的模拟IC生产厂家ADI、TI公司代理权,经营全系列适用各种领域/场合的AD/DA器件。 1.AD公司AD/DA器件 AD公司生产的各种模数转换器(ADC)和数模转换器(DAC)(统称数据转换器)一直保持市场领导地位,包括高速、高精度数据转换器和目前流行的微转换器系统(MicroConvertersTM)。 1)带信号调理、1mW功耗、双通道16位AD转换器:AD7705 AD7705是AD公司出品的适用于低频测量仪器的AD转换器。它能将从传感器接收到的很弱的输入信号直接转换成串行数字信号输出,而无需外部仪表放大器。采用Σ-Δ的ADC,实现16位无误码的良好性能,片内可编程放大器可设置输入信号增益。通过片内控制寄存器调整内部数字滤波器的关闭时间和更新速率,可设置数字滤波器的第一个凹口。在+3V电源和1MHz主时钟时,AD7705功耗仅是1mW。AD7705是基于微控制器(MCU)、数字信号处理器(DSP)系统的理想电路,能够进一步节省成本、缩小体积、减小系统的复杂性。应用于微处理器(MCU)、数字信号处理(DSP)系统,手持式仪器,分布式数据采集系统。 2)3V/5V CMOS信号调节AD转换器:AD7714 AD7714是一个完整的用于低频测量应用场合的模拟前端,用于直接从传感器接收小信号并输出串行数字量。它使用Σ-Δ转换技术实现高达24位精度的代码而不会丢失。输入信号加至位于模拟调制器前端的专用可编程增益放大器。调制器的输出经片内数字滤波器进行处理。数字滤波器的第一次陷波通过片内控制寄存器来编程,此寄存器可以调节滤波的截止时间和建立时间。AD7714有3个差分模拟输入(也可以是5个伪差分模拟输入)和一个差分基准输入。单电源工作(+3V或+5V)。因此,AD7714能够为含有多达5个通道的系统进行所有的信号调节和转换。AD7714很适合于灵敏的基于微控制器或DSP的系统,它的串行接口可进行3线操作,通过串行端口可用软件设置增益、信号极性和通道选择。AD7714具有自校准、系统和背景校准选择,也允许用户读写片内校准寄存器。CMOS结构保证了很低的功耗,省电模式使待机功耗减至15μW(典型值)。 3)微功耗8通道12位AD转换器:AD7888 AD7888是高速、低功耗的12位AD转换器,单电源工作,电压范围为2.7V~5.25V,转换速率高达125ksps,输入跟踪-保持信号宽度最小为500ns,单端采样方式。AD7888包

数字信号处理课程设计报告《应用Matlab对信号进行频谱分析及滤波》 专业: 班级: 姓名: 指导老师: 二0 0五年一月一日

目录 设计过程步骤() 2.1 语音信号的采集() 2.2 语音信号的频谱分析() 2.3 设计数字滤波器和画出其频谱响应() 2.4 用滤波器对信号进行滤波() 2.5滤波器分析后的语音信号的波形及频谱() ●心得和经验()

设计过程步骤 2.1 语音信号的采集 我们利用Windows下的录音机,录制了一段开枪发出的声音,时间在1 s内。接着在C盘保存为WAV格式,然后在Matlab软件平台下.利用函数wavread对语音信号进行采样,并记录下了采样频率和采样点数,在这里我们还通过函数sound引入听到采样后自己所录的一段声音。通过wavread函数和sound的使用,我们完成了本次课程设计的第一步。其程序如下: [x,fs,bite]=wavread('c:\alsndmgr.wav',[1000 20000]); sound(x,fs,bite); 2.2 语音信号的频谱分析 首先我们画出语音信号的时域波形;然后对语音信号进行频谱分析,在Matlab中,我们利用函数fft对信号进行快速傅里叶变换,得到信号的频谱特性性。到此,我们完成了课程实际的第二部。 其程序如下: n=1024; subplot(2,1,1); y=plot(x(50:n/4)); grid on ; title('时域信号') X=fft(x,256); subplot(2,1,2); plot(abs(fft(X))); grid on ; title('频域信号'); 运行程序得到的图形:

串行通信技术SERDES正成为高速接口的主流 串行通信技术SERDES正成为高速接口的主流 2009-08-21 13:44随着对信息流量需求的不断增长,传统并行接口技术成为进一步提高数据传输速率的瓶颈。过去主要用于光纤通信的串行通信技术——SERDES正在取代传统并行总线而成为高速接口技术的主流。本文阐述了介绍SERDES 收发机的组成和设计,并展望了这种高速串行通信技术的广阔应用前景。 ? SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。它是一种时分多路复用(TDM)、点对点的通信技术,即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本。 ? SERDES技术最早应用于广域网(WAN)通信。国际上存在两种广域网标准:一种是SONET,主要通行于北美;另一种是SDH,主要通行于欧洲。这两种广域网标准制订了不同层次的传输速率。目前万兆(OC-192)广域网已在欧美开始实行,

中国大陆已升级到2.5千兆(OC-48)水平。SERDES技术支持的广域网构成了国际互联网络的骨干网。 ? SERDES技术同样应用于局域网(LAN)通信。因为SERDES 技术主要用来实现ISO模型的物理层,SERDES通常被称之为物理层(PHY)器件。以太网是世界上最流行的局域网,其数据传输速率不断演变。IEEE在2002年通过的万兆以太网标准,把局域网传输速率提高到了广域网的水平,并特意制订了提供局域网和广域网无缝联接的串行WAN PHY。与此同时,SERDES技术也广泛应用于不断升级的存储区域网(SAN),例如光纤信道。 ? 随着半导体技术的迅速发展,计算机的性能和应用取得了长足进步。可是,传统并行总线技术——PCI却跟不上处理器和存储器的进步而成为提高数据传输速率的瓶颈。新一代PCI标准PCI Express正是为解决计算机IO瓶颈而提出的(见表1)。PCI Express是一种基于SERDES的串行双向通信技术,数据传输速率为2.5G/通道,可多达32通道,支持芯片与芯片和背板与背板之间的通信。国际互联网络和信息技术的兴起促成了计算机和通信技术的交汇,而SERDES串行通信技术逐步取代传统并行总线正是这一交汇的具体体现。

74LS244:3态8位缓冲器,一般用作总线驱动器。74LS244没有锁存的功能。地址锁存器就是一个暂存器,它根据控制信号的状态,将总线上地址代码暂存起来。 当微处理器与存储器交换信号时,首先由CPU发出存储器地址,同时发出允许锁存信号ALE 给锁存器,当锁存器接到该信号后将地址/数据总线上的地址锁存在总线上,随后才能传输数据。 锁存器是一个很普通的时序电路。一般的,它在时钟上升沿或者下降沿来的时候锁存输入,然后产生输出,在其他的时候输出都不跟随输入变化,这就是所谓边缘触发的D触发器。它主要用于三态输出,作为地址驱动器、时钟驱动器、总线驱动器和定向发送器等。其真值表如下:74Ls244真值表 74LS245:用来驱动led或者其他的设备,它是8路同相三态双向总线收发器,既可以输出,也可以输入数据。当8051单片机的P0口总线负载达到或超过P0最大负载能力时,必须接入74LS245等总线驱动器。当片选端/CE低电平有效时,DIR=“0”,信号由B 向A 传输(接收);DIR=“1”,信号由A 向 B 传输(发送);当CE为高电平时,A、B均为高阻态。由于P2口始终输出地址的高8位,接口时74LS245的三态控制端1G和2G接地,P2口与驱动器输入线对应相连。P0口与74LS245输入端相连,E端接地,保证数据线畅通。8051的/RD 和/PSEN相与后接DIR,使得RD且PSEN有效时,74LS245输入(P0.1←D1),其它时间处于输出(P0.1→D1)。 74LS273:是一种带清除功能的8D触发器,1D~8D为数据输入端,1Q~8Q为数据输出端,正脉冲触发,低电平清除,常用作数据锁存器,地址锁存器。D0~D7:出入;Q0~Q7:输出第一脚WR:主清除端,低电平触发,即当为低电平时,芯片被清除,输出全为0(低电平);CP(CLK):触发端,上升沿触发,即当CP从低到高电平时,D0~D7的数据通过芯片,为0时将数据锁存,D0~D7的数据不变。只有在清除端保持高电平时,才具有锁存功能,CPU 的ALE信号必须经过反相器反相之后才能与74LS273的控制端CLK 端相连。 应用:缓冲/存储寄存器,移位寄存器,图像发生器。 74LS373:为三态输出的八D 透明锁存器。373 的输出端可直接与总线相连。当三态允许控制端OE 为低电平时,Q0~Q7为正常逻辑状态,可用来驱动负载或总线。当OE 为高

语音信号滤波去噪报告书 课程:数字信号处理 指导老师: 完成组员: 完成日期:2013.01.05

摘要本课程设计主要是下载一段语音信号,绘制其波形并观察其频谱。然后在该语言信号中加一个噪音,利用布莱克曼和矩形窗窗设计一个FIR滤波器,对该语音信号进行虑噪处理,然后比较滤波前后的波形与频谱。在本课程设计中,是用MATLAB的集成环境完成一系列的设计。首先对加噪的语音信号进行虑波去噪处理,再比较滤波前后的频率响应曲线,若一样则满足所设计指标,否则不满足。也可以调用函数sound听滤波前后其语音信号是否带有噪声。若无噪声也说明该滤波器的设置也是成功的。 关键词语音信号;MATLAB;FIR滤波器;滤波去噪; 1 引言 人们在语音通信的过程中将不可避免的会受到来自周围环境的干扰,例如传输媒介引入的噪声,通信设备内部的电噪声,乃至其他讲话者的话音等。正因为有这些干扰噪声的存在,接受者接受到的语音已不是原始的纯净语音信号,而是受噪声干扰污染的带噪声语音信号。而本课程设计就是利用MATLAB集成环境用布莱克曼窗的方法设计一个FIR滤波器,对语音信号进行滤波去噪处理,并将虑噪前后的频谱图进行对比。 1.1 课程设计目的

数字信号处理课程设计是数字信号处理课程的重要实践性环节,是学生在校期间一次较全面的工程师能力训练,在实现学生总体培养目标中占有重要地位。综合运用本课程的理论知识进行频谱分析以及滤波器设计,通过理论推导得出相应结论,并利用MATLAB 作为编程工具进行计算机实现,从而复习巩固了课堂所学的理论知识,提高了对所学知识的综合应用能力,并从实践上初步实现了对数字信号的处理。本课程设计能使学生对通信工程领域各种技术的DSP实现的设计有较熟练的掌握。且通过自身的实践,对DSP的设计程序、内容和方法有更深入的掌握,提高实际运用的能力。并可综合运用这些知识解决一定的实际问题,使学生在所学知识的综合运用能力上以及分析问题、解决问题能力上得到一定的提高。 1.2课程设计的要求 (1)、录制一段个人自己的语音信号,并对录制的信号进行采样,画出采样后语音信号的时域波形和频谱图。 (2)、给定滤波器的性能指标,采用窗函数法和双线性变换设计滤波器,并画出滤波器的频率响应。 (3)、用自己设计的滤波器对采集的信号进行滤波,画出滤波后信号的时域波形和频谱,并对滤波前后的信号进行对比,分析信号的变化并回放语音信号; (4)、通过利用各种不同的开发工具实现语音信号的滤波去噪,掌握数字信号的分析方法和处理方法。而且通过课程设计能够培养学生严谨的科学态度,认真的工作作风和团队协作精神。 (5)、在老师的指导下,要求独立完成课程设计的全部内容,并按要求编写课程设计学年论文,能正确阐述和分析设计和实验结果。

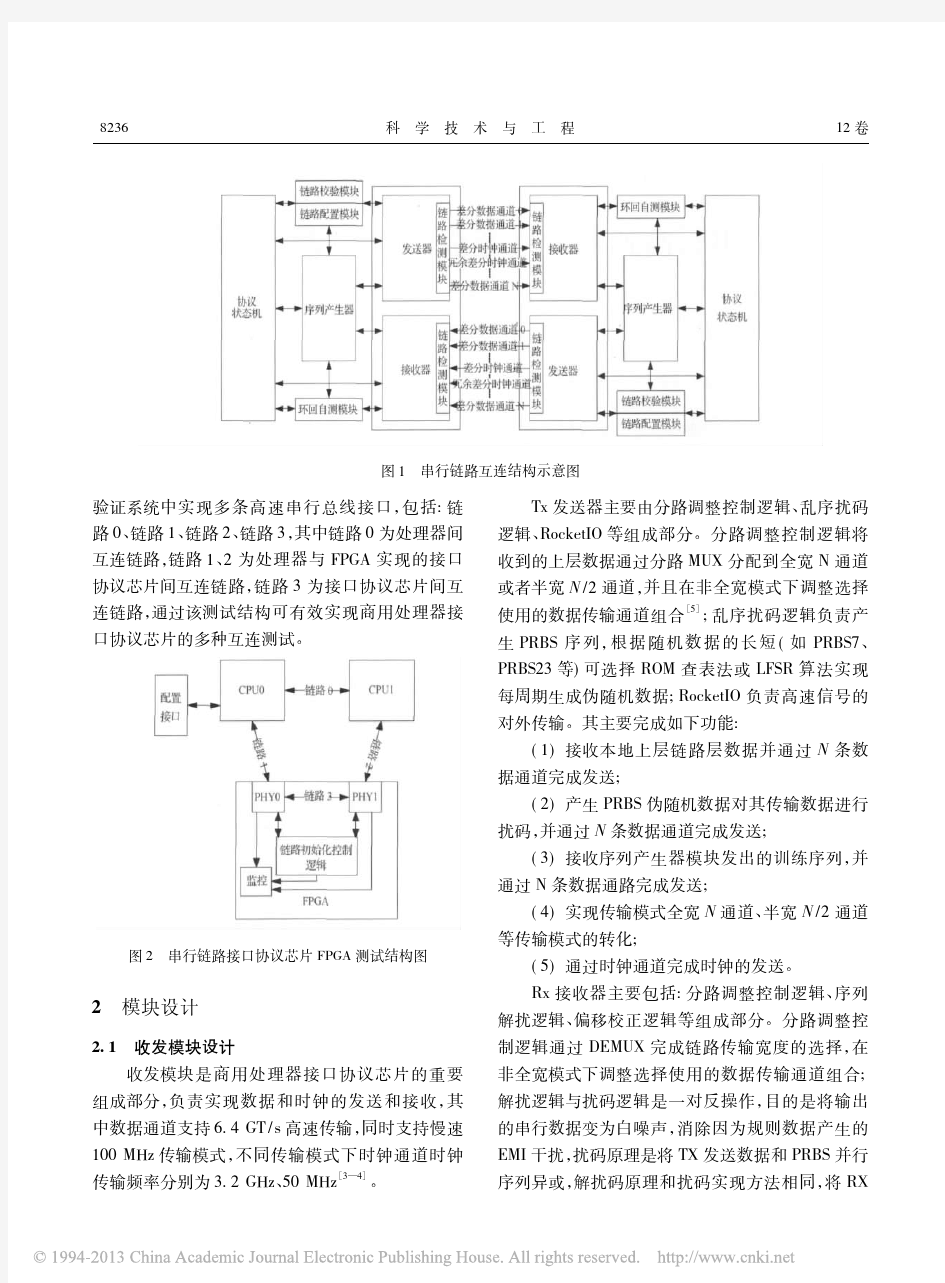

在单片机应用系统中,存在多种形式的外部数据输入接口界面,例如RS-232C串行通信、键盘输入等[1,4]。其中利用键盘接口输入数据,是实现现象实时调试、数据调整和控制最常用的方法。单片机的外围键盘扩展电路有多种实现方式,例如直接利用I/O接口线或外接8255A接口芯片,配合适当的接口管理程序,就可以实现外围键盘扩展功能。但是,在这些方法中,键盘扩展电路需要占用单片机的资源对按键进行监控和处理,这对要求高实时性处理的单片机系统是不实现的。为了解决这一问题,可以使用专用键盘接口芯片(例如Intel8279)[2]来组建键盘子系统。而且,这类专用键盘接口芯片在使用灵活性方面尚有欠缺,尤其当用户需要实现某些特定功能时,其缺点更为明显。针对上述问题,本文提出一种利用复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)设计技术[3]实现专用键盘接口芯片的方案。 1 系统原理 图1是单片机系统中键盘子系统的构成原理框图。其中键盘接口芯片KB-CORE是该子系统的核心部分,它应具备如下功能:第一,产生按键扫描时序,并进行硬件去抖动。如果直按键按下,实现按键编码、中断处理等功能。第二,可以区分处理数字键和功能键。数字键钭由接口芯片暂存,而当功能键被按下时申请CPU中断处理;对多个按键同时按下,按一定的编码优先级处理。第三,提供与MCS-51系列单片机兼容的接口,单片机可以读取芯片中保存的数据或功能代码。第四,提供数据显示接口,可以直接驱动4位七段LED数码管,并进行动态扫描显示。

按键根据键盘子系统的服务对象拟设置子数字键(0~9)、功能键(ROW、COL、DAT)、清零键(CLR)共14个,排成4×4的矩阵,有两个未定义。 2 专用键盘接口芯片功能结构设计 根据上述专用键盘芯片KB-CORE的功能要求,图2示出本芯片内部应有的结构框图。 其工作原理如下:(1)键盘扫描控制及编码电路中内含一个环形计数器。该计数器计数输出至KSL[0~3]端作为键盘扫描信号。每当扫描信号发生变化时,键盘扫描控制器从KRL[0~3]端读入某一行按键的状态信号。如果没有按键被按下,则扫描下一行;如果有按键被按下,则控制器锁定被扫描行,并延迟约10ms去抖动,然后再次扫描被锁定行以确定按键是否误读。如果按键被证实按下,则一直等待直至用户松开该键。与此同时,数字键码将被保存到先进先出存储器,功能键则直接产生中断请求信号IRQ,通知CPU读取键码DBO[0~7]。(2)FIFORAM中数据容量为16位。每4位对应一个字形符,所以七段LED数码管需要4位。(3)扫描发生器一方面产生LED的位选信号DSL[0~3],另一方面产生扫描显示输出控制电路的位数据选通信号。扫描显示输出控制电路根据位数据选通信号读取FIFO RAM中相对应的数据,然后送七段译码电路输出DP[0~6]驱动LED显示屏的段选信号电极。(4)接口控制电路一方面用来识别CPU的读时序;另一方面用来对地址信号线A1A0译码,实现对输出数据的选择。若A0A1=“00”,则输出FIFO RAM中的低字节数据;若A0A1=“01”,

数字信号处理 课 程 设 计 院系:电子信息与电气工程学院 专业:电子信息工程专业 班级:电信班 姓名: 学号: 组员:

摘要 滤波器设计在数字信号处理中占有极其重要的地位,FIR数字滤波器和IIR 滤波器是滤波器设计的重要组成部分。利用MATLAB信号处理工具箱可以快速有效地设计各种数字滤波器。课题基于MATLAB有噪音语音信号处理的设计与实现,综合运用数字信号处理的理论知识对加噪声语音信号进行时域、频域分析和滤波。通过理论推导得出相应结论,再利用 MATLAB 作为编程工具进行计算机实现。在设计实现的过程中,使用窗函数法来设计FIR数字滤波器,用巴特沃斯、切比雪夫和双线性变法设计IIR数字滤波器,并利用MATLAB 作为辅助工具完成设计中的计算与图形的绘制。通过对对所设计滤波器的仿真和频率特性分析,可知利用MATLAB信号处理工具箱可以有效快捷地设计FIR和IIR数字滤波器,过程简单方便,结果的各项性能指标均达到指定要求。 关键词数字滤波器 MATLAB 窗函数法巴特沃斯

目录 摘要 (1) 1 引言 (1) 1.1课程设计目的 (1) 1.2 课程设计内容及要求 (1) 1.3课程设计设备及平台 (1) 1.3.1 数字滤波器的简介及发展 (1) 1.3.2 MATLAB软件简介 (2) 2 课程设计原理及流程 (4) 3.课程设计原理过程 (4) 3.1 语音信号的采集 (4) 3.2 语音信号的时频分析 (5) 3.3合成后语音加噪声处理 (7) 3.3.1 噪声信号的时频分析 (7) 3.3.2 混合信号的时频分析 (8) 3.4滤波器设计及消噪处理 (10) 3.4.1 设计IIR和FIR数字滤波器 (10) 3.4.2 合成后语音信号的消噪处理 (13) 3.4.3 比较滤波前后语音信号的波形及频谱 (13) 3.4.4回放语音信号 (15) 3.5结果分析 (15) 4 结束语 (15) 5 参考文献 (16)

高速USB2.0设备的PCB板设计 通用串行总线(Universal Serial Bus)从诞生发展到今天,USB协议已从1.1过渡到2.O,作为其重要指标的设备传输速度,从1.5 Mbps;的低速和12 Mbps的全速,提高到如今的480 Mbps的高速。USB接口以其速度快、功耗低、支持即插即用、使用安装方便等优点得到了广泛的应用。目前,市场上以USB2.0为接口的产品越来越多,绘制满足USB2.0协议高速数据传输要求的PCB板对产品的性能、可靠性起着极为重要的作用,并能带来明显的经济效益。 USB2.0接口是目前许多高速数据传输设备的首选接口,实践表明:在高速USB主、从设备的研发过程中,正确设计PCB板能充分发挥USB2.O高速性能。但是,若PCB板设计不当,则传输速率可能根本达不到预期目的,甚至会导致高速USB2.0设备只能工作在全速状态。 下面介绍USB2.0设备高速数据传输PCB板设计。 1 USB2.0接口差分信号线设计 USB2.0协议定义由两根差分信号线(D+、D-)传输高速数字信号,最高的传输速率为480 Mbps。差分信号线上的差分电压为400 mV,差分阻抗(Zdiff)为90(1±O.1)Ω。在设计PCB板时,控制差分信号线的差分阻抗对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰电压。差分线2D模型如图1所示。 差分线由两根平行绘制在PCB板表层(顶层或底层)发生边缘耦合效应的微带线(Microstrip)组成的,其阻抗由两根微带线的阻抗及其和决定,而微带线的阻抗(Zo)由微带线线宽(W)、微带线走线的铜皮厚度(T)、微带线到最近参考平面的距离(H)以及PCB板材料的介电常数(Er)决定,其计算公式为:Zo={87/sqrt(Er+1.41)]}ln[5.98H/(0.8W+T)]。影响差分线阻抗的主要参数为微带线阻抗和两根微带线的线间距(S)。当两根微带线的线间距增加时,差分线的耦合效应减弱,差分阻抗增大;线间距减少时,差分线的耦合效应增强,差分阻抗减小。差分线阻抗的计算公式为:Zdiff=2Zo(1-0.48exp(-0.96S/H))。微带线和差分线的计算公式在

一种基于LVDS的高速串行数据传输系统设计 一种基于LVDS的高速串行数据传输系统设计 引言在某型雷达信号处理系统中,要求由上位机(普通PC)实时监控雷达系统状态并采集 信号处理机的关键变量,这就要求在处理机与上位机之间建立实时可靠的连接。同时,上位机也能对信号处理板进行控制,完成诸如处理机复位、DSP程序动态加载等功能。实验中,处理机和上位机之间的数据传输距离不小于8m。在这种前提下,计算机上现有的串口、并口显然不能满足要求,而USB2.0接口工作在高速模式时传输距离只有3m,其它诸如以太网传输的实时性难于满足要求,光纤通道传输的构建成本又太高。基于此,本文提出了一种采用LVDSLVDS高速串行总线技术的传输方案。数据传输系统方案由于系统要求传输距离大于8m,需采用平衡电缆。对于两端LVDS接口,可以采用ASIC和FPGA两种方式实现。由于Xilinx公司生产的Virtex-II系列FPGA直接支持LVDS电平标准,本系统采用XC2V250实现,这不仅省去了专用LVDS电平转换芯片,节省了成本,而且可以将系统中其它控制逻辑集成在单个FPGA芯片内,从而降低了PCB设计的难度,提高了系统的集成度和可靠性。另外,收发接口逻辑采用FPGA, 可以在使用过程中根据需要重新配置传输方向,以动态地改变收发通道的数目,大大增强了系统的可重构能力。整个数据传输系统框图。由于数据传输是双向的,信号处理板 和PCI板都有并/串转换发送模块和串/并转换接收模块(均在FPGA内实现),两块板卡通过平衡电缆连接。此外,在信号处理板上,DSP处理机通过外部总线向FPGA发送缓存区内写入数据,FPGA通过DSP的主机口完成与DSP存储空间的数据交换。在PCI板上,FPGA通过PCI控制器和主机进行数据交换。系统工作原理可表述如下:DSP 处理机将处理结果通过外部总线输出到FPGA缓冲存储器内,在FPGA内完成数据的并/串转换,并通过LVDS串行接口发送出去。数据通过平衡电缆传输至上位机接收卡。在上位机接收卡内,数据经串/并转换后,送至PCI接口控制电路。上位机输出数据到

PCB高速信号电路设计的三大布线技巧详解 PCB 板的设计是电子工程师的必修课,而想要设计出一块完美的PCB 板也并不是看上去的那么容易。一块完美的PCB 板不仅需要做到元件选择和设置合理,还需要具备良好的信号传导性能。本文将会就PCB 高速信号电路设计中的布线技巧知识,展开详细介绍和分享,希望能够对大家的工作有所帮助。 合理使用多层板进行PCB 布线 在PCB 板的实际设计过程中,大部分工程师都会选择使用多层板来完成高速信号布线工作,这种多层板既是必不可少的组成部分,也是帮助工程师降低电路干扰的有效手段。在利用多层板来完成PCB 的高速信号电路设计时,工程师需要合理的选择层数来降低印制板尺寸,充分利用中间层来设置屏蔽,实现就近接地,能有效降低寄生电感,缩短信号传输长度,降低信号间的交叉干扰等等,所有这些方法对高速电路的可靠性工作都是非常有利的。 除了上面所提到的几种利用多层板提升PCB 信号传输可靠性的方法外,还有一部分权威资料显示,同种材料时四层板要比双面板的噪声低20dB。引线弯折越少越好,最好采用全直线,需要转折,可用45 度折线或圆弧转折,可以减小高速信号对外的发射和相互间的耦合,减少信号的辐射和反射。 高速电路器件管脚间的引线越短越好 在进行PCB 高速信号电路的设计和布线过程中,工程师需要尽可能的缩短高速电路器件管脚之间的引线,以为引线越长,带来的分布电感和分布电容值越大,这将会导致高速电路系统发生反射、振荡等。 除了要尽可能的缩短高速电路元件管脚之间的引线之外,在PCB 布线的过程中,各个高速电路器件管脚间的引线层间交替越少越好,就是元件连接过程中所用的过孔越少越好。通常来说,一个过孔可带来约0.5pF 的分布电容,这将