第八届“蓝桥杯”全国软件和信息技术专业人才大赛

模拟试题-嵌入式设计与开发项目

第一部分:客观题

1.STM32F103RBT6单片机具有_________KByte RAM空间,_________Kbyte

Flash空间,__________个USART,_________个_________位ADC。

2.以下哪种方法或工具可以对STM32进行程序下载()

A. J-link

B. Co-Link

https://www.doczj.com/doc/cc17144066.html,ART ISP

https://www.doczj.com/doc/cc17144066.html,ART IAP

3.下面哪些描述是STM32 GPIO具备的特点()

A. 单独的位设置、清除

B. 外部中断线/唤醒线

C. 复用功能和重映射D.GPIO锁定机制

4.模拟信号采集设备,ADC参考电压为5V,要求分辨率达到5mV,ADC至少

应选择()

A. 8位

B.10位

C. 12位

D. 16位

5.STM32 DMA控制器可编程的数据传输数目最大为()

A.65536 B. 4096

C.1024 D. 65535

6.某系统需要永久存放少量(少于1K byte)参数,且需要频繁访问,最合适的

存储器是()

A. SRAM

B. E2PROM

C. Nor Flash

D. Nand Flash

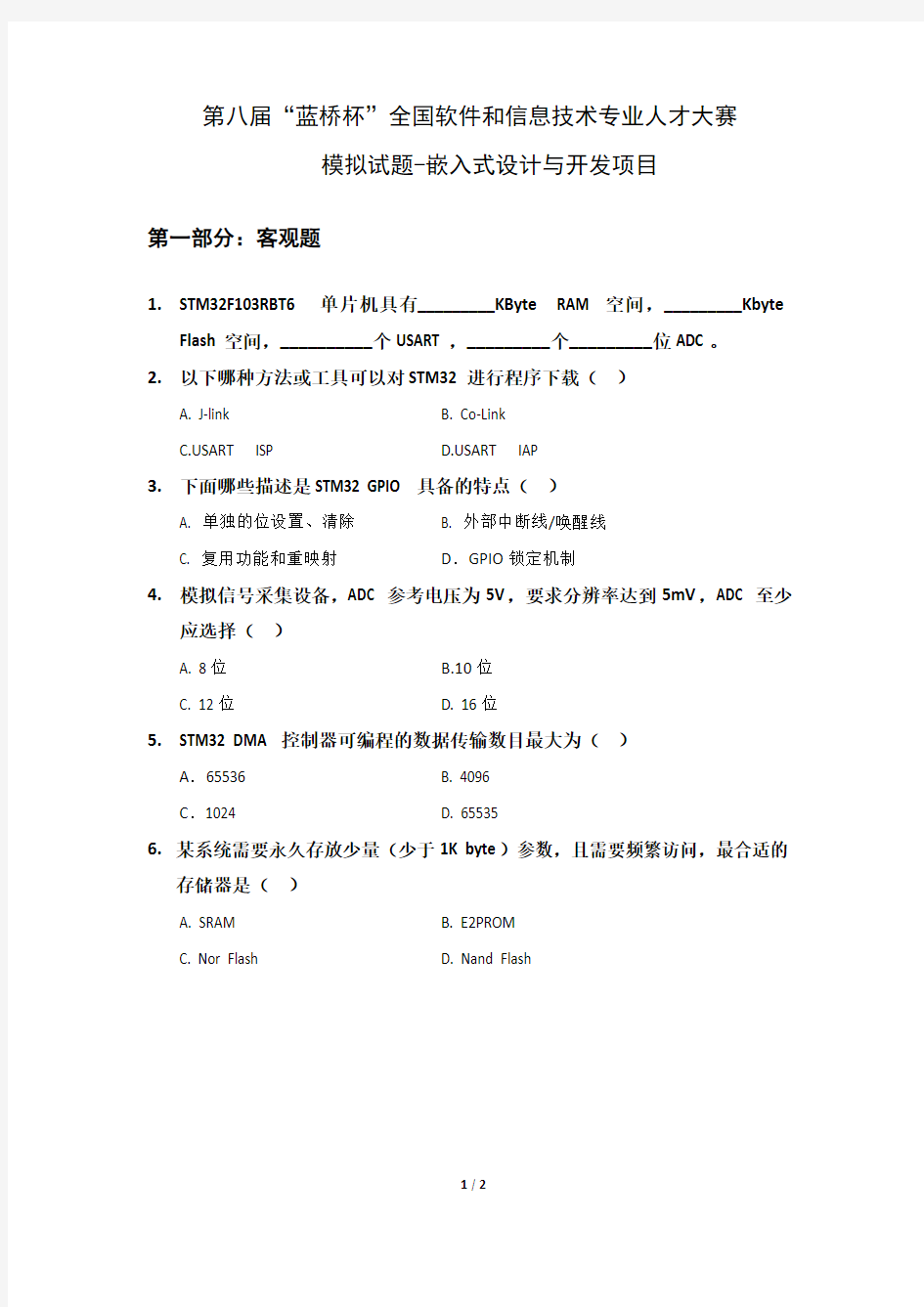

7.运算放大器的电源接入±12V,稳压管的稳定电压为6V,正向导通电压为

0.6V,当输入电压U i = -2V时,输出电压U O应该为()

U i

U O

A. -6V

B. -2V

C. +6V

D. 0.6V

8.以下哪几种操作系统适合在STM32系列微控制器()

A. μCos-II

B. Free RTOS

C. Windows CE

D. Linux

一、单项选择题 1、在CPU和物理内存之间进行地址转换时,(B )将地址从虚拟(逻辑)地址空间映射到物理地址空间。 A.TCB B.MMU C.CACHE D.DMA 2、进程有三种状态:(C )。 A.准备态、执行态和退出态B.精确态、模糊态和随机态 C.运行态、就绪态和等待态D.手工态、自动态和自由态 3、以下叙述中正确的是(C )。 A.宿主机与目标机之间只需要建立逻辑连接即可 B.在嵌入式系统中,调试器与被调试程序一般位于同一台机器上 C.在嵌入式系统开发中,通常采用的是交叉编译器 D.宿主机与目标机之间的通信方式只有串口和并口两种 4、中断向量是指(C )。 A.中断断点的地址B.中断向量表起始地址 C.中断处理程序入口地址D.中断返回地址 5、在微型计算机中,采用中断方式的优点之一是(C )。 A.简单且容易实现B.CPU可以不工作 C.可实时响应突发事件D.传送速度最快 6、在ARM处理器中,(A )寄存器包括全局的中断禁止位,控制中断禁止位就可以打开或者关闭中断。 A.CPSR B.SPSR C.PC D.IR 7、嵌入式系统的三要素下面哪一个不是:(B )。 A、嵌入 B、存储器 C、专用 D、计算机 8、若R1=2000H,(2000H)=0x28,(2008H)=0x87,则执行指令LDR R0,[R1,#8]!后R0的值为()。 A、0x2000 B、0x28 C、0x2008 D、0x87 9、μCOS-II操作系统属于(B )。 A、顺序执行系统 B、占先式实时操作系统 C、非占先式实时操作系统 D、分时操作系统 10、ARM寄存器组有( C )个状态寄存器。 A、7 B、32 C、6 D、37 11、C++源程序文件的默认扩展名为(A )。 A、cpp B、exe C、obj D、lik 12、与十进制数254等值的二进制数是(A )。 A、B、 C、D、

嵌?式系统设计师 2014年下半年试题 上午综合试卷 第1题:三总线结构的计算机总线系统由(1)组成。 A. CPU总线、内存总线和10总线 B. 数据总线、地址总线和控制总线 C. 系统总线、内部总线和外部总线 D. 串?总线、并?总线和PCI总线 参考答案:B 解析: 本题考查计算机系统基础知识。 总线上传输的信息类型分为数据、地址和控制,因此总线由数据总线、地址总线和控制总线组成。 第2题:计筧机采?分级存储休系的主要?的是为了解决(2)的问题。 A. 主存容量不? B. 存储器读写可靠性 C. 外设访问效率 D. 存储容量、成本和速度之间的?盾 参考答案:D

解析: 本题考查计算机系统基础知识。 计算机系统中,?速缓存?般采?SRAM,内存?般??DRAM,外存?般采?磁存储器。SRAM的集成度低、速度快、成本?;DRAM的集成度?,但是需要动态刷新;磁存储器速度慢、容量?,价格便宜。因此,组成分级存储体系来解决存储容量、成本和速度之间的?盾。 第3题:属于CPU中算术逻辑申.元的部件是(3)。 A. 程序计数器 B. 加法器 C. 指令寄存器 D. 指令译码器 参考答案:B 解析: 本题考杏计算机系统基础知识。 程序计数器、指令寄存器和指令译码器都是CPU中控制单元的部件,加法器是算术逻辑运算单元的部件。 第4题:内存按字节编址从A5000H到DCFFFH的区域其存储容量为(4)。 A. 123KB B. 180KB C. 223KB D. 224KB 参考答案:D 解析: 本题考査计算机系统基础知识。 从地址A5000H到DCFFFH的存储单元数冃为37FFFH(即224*1024)个,由于是字节编址,从?得到存储容量为224KB。

嵌入式系统设计大作业 学号:14020520009 姓名:罗翔 1、叙述JTAG接口在嵌入式开发中的作用。 答: (1)用于烧写FLASH 烧写FLASH的软件有很多种包括jatg.exe fluted flashpgm等等,但是所有这些软件都是通过jtag接口来烧写flash的,由于pc机上是没有jtag接口的,所以利用并口来传递信息给目标板的jtag接口。所以就需要并口转jtag接口的电路。 (2)用于调试程序 同时应该注意到jtag接口还可以用来调试程序。而调试程序(如ARM开发组件中的AXD)为了通过jtag接口去调试目标板上的程序,同样是使用pc的并口转jtag接口来实现与目标板的通信。这样,并口转jtag接口的电路就有了两种作用。 (3)仿真器 根据(1)和(2)的总结,并口转jtag接口的电路是两种应用的关键,而这种电路在嵌入式开发中就叫仿真器。并口转jtag接口的电路有很多种,有简单有复杂的,常见的仿真器有Wigger,EasyJTAG,Multi-ICE等。这些所谓的仿真器的内部电路都是并口转jtag接口,区别只是电路不同或使用的技术不同而已。 2、叙述嵌入式平台的搭建过程,以linux为例。 答: 1) 一:建立宿主机开发环境 建立交叉编译的环境即在宿主机上安装与开发板相应的编译器及库函数,以便能够在宿主机上应用开发工具编译在目标板上运行的Linux引导程序,内核,文件系统和应用程序 交叉编译:在特殊的环境下,把嵌入式程序代码编译成不同的CPU所对应的机器代码。

开发时使用宿主机上的交叉编译,汇编及链接工具形成可执行的二进制代码(该代码只能在开发板上执行),然后下载到开发板上运行 2) 下载和安装arm-Linux-gcc编译工具链下载最新的arm-Linux-gcc并解压至当前目录下 在系统配置文件profile中设置环境变量方法:直接在profile文件中加入搜索路径立即使新的环境变量生效:运行source命令,检查是否将路径加入到path,测试是否安装成功, 编译程序,测试交叉工具链 3) 配置超级终端minicom minicom是宿主机与目标板进行通信的终端:在宿主机Linux终端中输入:minicom-s或输入minicom然后按ctrl+A+O对超级终端minicom进行配置,再选择串口并配置串口,最后保存即可 4) 建立数据共享服务:NFS服务是Linux系统中经常使用的数据文件共享服务 5) 编译嵌入式系统内核:内核配置,建立依存关系,建立内核 6) 制作文件系统 3、给出现今有哪些用于嵌入式开发的芯片名称,他们分别是哪些公司的产品? 体系结构是什么? S3C2410X基于ARM的Sumsang; XscalePXA255/PXA270基于ARM的Intel; 摩托罗拉MC基于68k; Power 601基于Power PC; MIPS32Kc基于MIPS 4、现今较流行的嵌入式操作系统有哪些? 答: (1) VxWorks (2)wince (3)linux (4)android

嵌入式系统设计与应用 本文由kenneth67贡献 ppt文档可能在W AP端浏览体验不佳。建议您优先选择TXT,或下载源文件到本机查看。 课程名称:课程名称:嵌入式系统设计与应用 总学时:其中讲课36学时,上机实践环节12 36学时12学时总学时:其中讲课36学时,上机实践环节12学时教材:嵌入式系统设计教程》教材:《嵌入式系统设计教程》电子工业出版社马洪连参考书:参考书:1、《嵌入式系统开发与应用》北航出版社、田泽编著. 嵌入式系统开发与应用》北航出版社、田泽编著. 2、《ARM体系结构与编程》清华大学出版社杜春雷编著ARM体系结构与编程体系结构与编程》嵌入式系统设计与实例开发—ARM ARM与C/OS3、《嵌入式系统设计与实例开发ARM与μC/OS-Ⅱ》清华大学出版社王田苗、魏洪兴编著清华大学出版社王田苗、ARM嵌入式微处理器体系结构嵌入式微处理器体系结构》4、《ARM嵌入式微处理器体系结构》北航出版社、马忠梅等著. 北航出版社、马忠梅等著. 张石.ARM嵌入式系统教程嵌入式系统教程》5、张石.《ARM嵌入式系统教程》.机械工业出版2008年社.2008年9月 1 课程内容 绪论:绪论: 1)学习嵌入式系统的意义2)高校人才嵌入式培养情况嵌入式系统设计(实验课)3)嵌入式系统设计(实验课)内容安排 第1章嵌入式系统概况 1.1 嵌入式系统的定义1.2 嵌入式系统的应用领域及发展趋势1.3 嵌入式系统组成简介 第2章嵌入式系统的基本知识 2.1 2.2 2.3 嵌入式系统的硬件基础嵌入式系统的软件基础ARM微处理器的指令系统和程序设计ARM微处理器的指令系统和程序设计 2 第3章 3.1 3.2 3.3 基于ARM架构的嵌入式微处理器基于ARM架构的嵌入式微处理器ARM 概述嵌入式微处理器的组成常用的三种ARM ARM微处理器介绍常用的三种ARM 微处理器介绍 第4章 4.1 4.2 4.3 4.4 4.5 4.6 嵌入式系统设计 概述嵌入式系统的硬件设计嵌入式系统接口设计嵌入式系统人机交互设备接口嵌入式系统的总线接口和网络接口设计嵌入式系统中常用的无线通信技术 3 第5章嵌入式系统开发环境与相关开发技术 5.1 5.2 5.3 5.4 5.5 6.1 6.2 6.3 6.4 概述嵌入式系统的开发工具嵌入式系统调试技术嵌入式系统开发经验嵌入式系统的Bootloader Bootloader技术嵌入式系统的Bootloader技术μC/OS-II操作系统概述C/OS-II操作系统概述ADS开发环境ARM ADS开发环境C/OS-II操作系统在ARM系统中的移植操作系统在ARM μC/OS-II操作系统在ARM系统

嵌入式系统设计与应用第五章程序设计与分析(1) 西安交通大学电信学院 任鹏举

本章主要内容 Software Design Cycle ●嵌入式软件中的组件(状态机 、循环缓存器、队列) ●编程模型,如数据流和控制图●编译方法介绍 ●根据性能、大小和功耗来分析 和优化程序 ●如何测试程序以验证其正确性

1 嵌入式程序组件 ●状态机(State machine) 用变量来表示内部的状态,根据输入完成状态的转移交通灯控制、CPU design controller ●循环缓冲区(Circular buffer) I/O input buffer ●队列(Queue)

状态机(1) ● 反应系统(reactive system ):响应外部事件的系统。 ●外部输入是间歇到达● 适合使用状态机描述 ● 有限状态机是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。 ●Moore 机:● Mealy 机:输出只由当前状态确定 输出依赖于当前状态和输入

状态机(2) 例子:一个简单的座位安全带控制器 idle buzzer seated belted 未入座/-入座/定时器启动 未系安全带且定时器未超时/- 未系安全带/定时器启动系好安全带/-系好安全带/蜂鸣器关闭 定时器超时/蜂鸣器启动 未入座/-未入座/蜂鸣器关闭输入/输出-= 无动作

状态机(3) #define IDLE 0#define SEATED 1#define BELTED 2#define BUZZER 3switch (state) { case IDLE: if (seat) { state = SEATED; timer_on = TRUE; } break; case SEATED: if (belt) state = BELTED; else if (timer) state = BUZZER; break; case BELTED: if (!seat) state = IDLE; else if (!belt) state = SEATED; break; case BUZZER: if (belt) state = BELTED; else if (!seat) state = IDLE; break; } Inputs :seat, belt, timer Outputs: buzzer

一、选择题(共30分,每题2分) 1.嵌入式处理器指令的执行周期包括() A.启动、运行、退出 B.取指令、指令译码、执行指令、存储 C.启动、运行、挂起、退出 D.取指令、指令译码、执行指令 2.下列不属于嵌入设计处理器本身带有的基本接口是() A.串口; B.并口; C.PCIE; D.AD/DA; 3.以下几个步骤是DMA控制过程的主要节点,请选出正确的DMA控制流程(请求信号HRQ)为() A. CPU让出总线控制权(响应信号HLDA) B. DMA控制器向CPU请求总线使用权 C. DMA控制器控制总线,发总线命令、传送数据 D. DMA总线控制器归还总线控制权 5. CPU重新获取总线控制权 A. 2,1,3,4; B. 1,2,3,4; C. 3,1,4,2; D. 3,4,1,2; 4、一个嵌入式系统可以含有多个总线,以下不属于IO总线的为() A.AGP; B.PCI; C.AHB; D.ISA 5.VHDL是() A.硬件描述语言 B.软件描述语言 C.构件描述语言 D.软件开发工具 6.以下不属于mC/OS-II中支持的中断类型的是() A.硬件中断 B.外部中断 C.陷井中断 D.临界区中断 7.将系统启动代码读入内存是()的主要职责 A.内存管理; B. VFS; C.Boot Loader;D:虚拟内存 8.CAN总线是指()

A.控制器局域网 B.网络传输协议 C.数据标准 D.软硬件接口 9.属于LCD三种显示方式的是() A.投射型、反射型、透射型 B.投射型、透反射型、透射型 C.反射型、透射型、透反射型 D.投射型、反射型、透反射型 10.操作系统内核是指() A.操作系统的调度部分 B.操作系统的驱动 C.操作系统的存储管理 D.操作系统的核心部分 11.ICE在线仿真器上有大量的RAM,()是主要的一种 A SRAM B DRAM C Block RAM D 影子RAM 12.下面是PowerPC架构嵌入式微处理器的不是主要特点是() A.独特的分支出来单元可以让指令预期效率大大提高。 B.超标量的设计。 C.适合大量向量运算,指针现行寻址的智能化算法。 D.可处理“字节非对齐”的数据存储。 13.下列选项中,不是实时操作系统必须满足的条件是() A.具有可抢占的内核 B.中断可嵌套 C.任务调度的公平性 D.具有优先级翻转保护 14.BSP作为一种嵌入式软件,他的主要特点是() A:与硬件无关,与操作系统有关 B:与硬件和操作系统都相关 C:与硬件有关,与操作系统无关D:与操作系统和硬件都无关 15.JTAG的引脚TCK的主要功能是() A.测试时钟输入; B.测试数据输入,数据通过TDI输入JTAG口; C.测试数据输出,数据通过TDO从JTAG口输出; D.测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式。 二、判断题(每题2分,共20分) ( )1.嵌入式系统调试通常可以分为硬件级调试和在线仿真器调试。

嵌?式系统设计师 2015年下半年试题 上午综合试卷 第1题:CPU是在(1)结束时响应DMA请求的。 A. —条指令执? B. —段程序 C. ?个时钟周期 D. —个总线周期 参考答案:D 解析: 本题考查计算机组成基础知识。 DMA控制器在需要的时候代替CPU作为总线主设备,在不受CPU?预的情况下,控制I/O设备与系统主存之间的直接数据传输。DMA操作占?的资源是系统总 线,?CPU并?在整个指令执?期间即指令周期内都会使?总线,故DMA请求的检测点设置在每个机器周期也即总线周期结束时执?,这样使得总线利?率最?。 第2题:虚拟存储体系由(2)两级存储器构成。 A. 主存-辅存 B. 寄存器-Cache C. 寄存器-主存 D. Cache-主存

参考答案:A 解析: 本题考查计算机组成原理的基础知识。 计算机中不同容量、不同速度、不同访问形式、不同?途的各种存储器形成的是?种层次结构的存储系统。所有的存储器设备按照?定的层次逻辑关系通过软硬件连接起来,并进?有效的管理,就形成了存储体系。不同层次上的存储器发挥着不同的作?。?般计算机系统中主要有两种存储体系:Cache存储体系由Cache 和主存储器构成,主要?的是提?存储器速度,对系统程序员以上均透明;虚拟存储体系由主夺储器和在线磁盘存储器等辅存构成,主要?的是扩?存储器容量,对应?程序员透明。 第3题:浮点数能够表?的数的范围是由其(3)的位数决定的。 A. 尾数 B. 阶码 C. 数符 D. 阶符 参考答案:B 解析: 本题考查计算机组成原理的基础知识。? 在计算机中使?了类似于?进制科学计数法的?法来表??进制实数,因其表?不同的数时?数点位置的浮动不固定?取名浮点数表?法。浮点数编码由两部分组成:阶码(即指数,为带符号定点整数,常?移码表?,也有?补码的)和尾数(是定点纯?数,常?补码表?,或原码表?)。因此可以知道,浮点数的精度由尾数的位数决定,表?范围的??则主要由阶码的位数决定。 第4题:在机器指令的地址字段中,直接指出操作数本?的寻址?式称为(4)。 A. 隐含寻址 B. 寄存器寻址 C. ?即寻址

大作业设计报告书 题目:嵌入式系统原理与开发 院(系):物联网工程学院 专业: 班级: 姓名: 指导老师: 设计时间: 10-11 学年 2 学期 20XX年5月

目录 1.目的和要求 (3) 2.题目内容 (3) 3.设计原理 (4) 4.设计步骤 (5) 4.1 交通指示灯设计 (5) 4.2 S3C44B0X I/O 控制寄存器 (6) 4.3 红绿灯过渡代码: (8) 4.4 电源电路设计 (10) 4.5 系统复位电路设计 (11) 4.6 系统时钟电路设计 (11) 4.7 JTAG 接口电路设计 (12) 4.8串口电路设计 (12) 5.引脚分类图 (13) 6.参考文献 (13)

1.目的和要求 ARM技术是目前嵌入式应用产业中应用十分广泛的先进技术,课程开设的目的在于使学生在了解嵌入式系统基础理论的前提下能够掌握ARM处理器的汇编语言和c语言的程序设计方法,掌握S3C44B0X芯片的基本硬件结构特点和接口设计方法,同时熟悉ARM开发环境,学习ARM的硬件设计和软件编程的基本方法,为今后从事相关的应用与研究打下基础。通过大作业要达到如下目的: 一、掌握ARM的开发工具使用和软件设计方法。 二、掌握ARM处理器S3C44B0X的原理和GPIO接口设计原理。 三、掌握C语言与的ARM汇编语言的混合编程方法; 四、培养学生选用参考,查阅手册及文献资料的能力。培养独立思考,深入研 究,分析问题、解决问题的能力。 五、通过课程设计,培养学生严肃认真的工作作风。 2.题目内容 题目:交通指示灯系统设计 功能描述: 1.用S3C44B0X的GPIO设计相关电路; 2.设计相关的软件并注释; 3.实现十字路口2组红、黄、绿交通灯交替显示。 编程提示: 1.交通灯可用发光二极管代替; 2.电路可部分参照实验电路; 3.时间控制可以使用软件循环编程解决。

《嵌入式系统设计与应用》课程设计 题目嵌入式系统的实践教学探讨 1.嵌入式系统设计与应用课程的内容概述 1.1 内容概述 本课程适用于计算机类专业,是一门重要的专业课程。它的任务是掌握嵌入式系统的基本概念;掌握嵌入式处理器 ARM 体系结构,包括ARM总体结构、存储器组织、系统控制模块和I/O外围控制模块;掌握ARM指令集和Thumb指令集;掌握ARM汇编语言和C语言编程方法;了解基于ARM 的开发调试方法。它的目的是了解和掌握嵌入式处理器的原理及其应用方法。 1)介绍嵌入式系统开发的基础知识,从嵌入式计算机的历史由来、嵌入式系统的定义、嵌入式系统的基本特点、嵌入式系统的分类及应 用、嵌入式系统软硬件各部分组成、嵌入式系统的开发流程、嵌入 式技术的发展趋势等方面进行了介绍,涉及到嵌入式系统开发的基 本内容,使学生系统地建立起的嵌入式系统整体概念。 2)对ARM技术进行全面论述,使学生对ARM技术有个全面的了解和掌握,建立起以ARM技术为基础的嵌入式系统应用和以ARM核为基础 的嵌入式芯片设计的技术基础。 3)ARM指令系统特点,ARM 指令系统,Thumb 指令系统,ARM 宏汇编,ARM 汇编语言程序设计,嵌入式 C 语言程序设计。 1.2实践教学探讨 在IEEE 计算机协会2004年6月发布的Computing Curricula Computer Engineering Report, Ironman Draf t 报告中把嵌入式系统课程列为计算机工程学科的领域之一,把软硬件协同设计列为高层次的选修课程。美国科罗拉多州立大学“嵌入式系统认证”课程目录包括实时嵌入式系统导论、嵌入式系统设计和嵌入式系统工程训练课程。美国华盛顿大学嵌入式系统课程名称是嵌入式系统

《网页设计与制作》期末测验试题及答案

————————————————————————————————作者:————————————————————————————————日期:

《网页设计与制作》期末考试试题 一、单项选择题(本大题共30小题,每小题2分,共60分) 1、目前在Internet上应用最为广泛的服务是( )。 A、FTP服务 B、WWW服务 C、Telnet服务 D、Gopher服务 2、域名系统DNS的含义是( )。 A、Direct Network System B、Domain Name Service C、Dynamic Network System D、Distributed Network Service 3、主机域名center. nbu. edu. cn由四个子域组成,其中( )子域代表国别代码。 A、center B、nbu C、edu D、cn 4、当阅读来自港澳台地区站点的页面文档时,应使用的正确文本编码格式是( )。 A、GB码(简体中文)国家标准代码,简称国标码,“GB”在计算机领域中常常表示GB 2312-80或GB 18030-2005。两者是汉语编码系统的标准,在中国大陆和新加坡用于简体中文 B、Unicode码(统一码) Unicode只有一个字符集,中、日、韩的三种文字占用了Unicode中0x3000到0x9FFF的部分Unicode目前普遍采用的是UCS-2,它用两个字节来编码一个字符,比如汉字"经"的编码是0x7ECF,注意字符码一般用十六进制来表示,为了与十进制区分,十六进制以0x开头,0x7ECF转换成十进制就是32463,UCS-2用两个字节来编码字符,两个字节就是16位二进制,2的16次方等于65536,所以UCS-2最多能编码65536个字符。编码从0到127的字符与ASCII编码的字符一样,比如字母"a"的Unicode 编码是0x0061,十进制是97,而"a"的ASCII编码是0x61,十进制也是97, 对于汉字的编码,事实上Unicode对汉字支持不怎么好,这也是没办法的,简体和繁体总共有六七万个汉字,而UCS-2最多能表示65536个,才六万多个,所以Unicode只能排除一些几乎不用的汉字,好在常用的简体汉字也不过七千多个,为了能表示所有汉字,Unicode 也有UCS-4规范,就是用4个字节来编码字符 C、BIG5码(大五码) 是通行于台湾、香港地区的一个繁体字编码方案。地区标准号为:CNS11643,这就是人们讲的BIG-5码。VimIM在Vim环境中,可以直接键入十进制或十六进制Big5码。既不需要启动输入法,也不需要码表。 D、HZ码(简体中文) HZ编码是海外华人创造的一种将含有高位为1 的汉字双字节字串转换成易于在网络中传输的ASCII字符串的变换方式。编码过程中,被转换字符串中的原汉字子字符串各字节高位作清零处理,使之成为ASCII子字符串,并在其前后两端分别添加~{ 和~} 作为标记;而对于原ASCII子字符串,则将其中的~ 改写为~~,其余字符不变。 5、当标记的TYPE属性值为( )时,代表一个可选多项的复选框。 A、TEXT B、PASSWORD C、RADIO 单选框 D、CHECKBOX 6、为了标识一个HTML文件开始应该使用的HTML标记是( )。 A、

B、 C、嵌入式系统设计师练习题及答案解析嵌入式系统设计师练习题及答案第一套 (1) 嵌入式系统设计师练习题及答案第二套 (5) 嵌入式系统设计师练习题及答案第三套 (16) 嵌入式系统设计师练习题及答案解析第四套 (27) 嵌入式系统设计师练习题及答案解析第五套 (45) 嵌入式系统设计师练习题及答案解析第六套 (59) 嵌入式系统设计师练习题及答案解析第七套 (67) 嵌入式系统设计师练习题及答案解析第八套 (75) 嵌入式系统设计师练习题及答案解析第九套 (81) 嵌入式系统设计师练习题及答案解析第十套 (90) 嵌入式系统设计师练习题及答案解析第十一套 (99) 嵌入式系统设计师练习题及答案解析第十二套 (106) 嵌入式系统设计师练习题及答案解析第十三套 (115) 嵌入式系统设计师练习题及答案解析第十四套 (126) 嵌入式系统设计师练习题及答案解析第十五套 (139) 嵌入式系统设计师练习题及答案解析第十六套 (154) 嵌入式系统设计师练习题及答案解析第十七套 (161) 嵌入式系统设计师练习题及答案解析第十八套 (169) 嵌入式系统设计师练习题及答案解析第十九套 (177) 嵌入式系统设计师练习题及答案解析第二十套 (189) 嵌入式系统设计师练习题及答案解析第二十一套 (199) 嵌入式系统设计师练习题及答案解析第二十二套 (212) 嵌入式系统设计师练习题及答案第一套 1、以下关于CPU的叙述中,错误的是 A.CPU产生每条指令的操作信号并将操作信号送往相应的部件进行控制 B.程序计数器PC除了存放指令地址,也可以临时存储算术/逻辑运算结果 C.CPU中的控制器决定计算机运行过程的自动化 D.指令译码器是CPU控制器中的部件 2、以下关于Cache的叙述中,正确的是 A.在容量确定的情况下,替换算法的时间复杂度是影响Cache命中率的关键因素 B.Cache的设计思想是在合理成本下提高命中率 C.Cache的设计目标是容量尽可能与主存容量相等 D.CPU中的Cache容量应大于cPu之外的Cache容量 3、风险预测从两个方面评估风险,即风险发生的可能性以及 A.风险产生的原因 B.风险监控技术 C.风险能否消除 D.风险发生所产生的后果 4、许多程序设计语言规定,程序中的数据都必须具有类型,其作用不包括 A.便于为数据合理分配存储单元 B.便于对参与表达式计算的数据对象进行检查 C.便于定义动态数据结构 D.使于规定数据对象的取值范围及能够进行的运算 5、在计算机系统中,对程序员是透明的。 A.磁盘存储器 B.高速缓存 C.RAM存储器 D.flash存储器 2016年下学期嵌入式系统设计大作业嵌入式系统设计大作业 1、叙述嵌入式系统开发过程中所要解决的两个问题。 2、叙述嵌入式平台的搭建过程,以linux为例。 3、给出现今有哪些用于嵌入式开发的芯片名称,他们分别是哪些公司的产品? 体系结构是什么? 4、现今较流行的嵌入式操作系统有哪些? 5、PXA270嵌入式开发板的接口有哪些? 6、请写出Nor Flash和Nand Flash的区别。 7、冯。诺依曼架构与哈佛架构的区别。 8、单周期3级流水的情况下,第10个指令周期时,第几条指令执行结束? 9、下面是linux下的一个简单的设备驱动程序,写出linux设备驱动常用的数据结构,同时阅读下面代码,请给出测试程序中的每条语句加以注释。 设备驱动程序Keypad.c的源代码: #include 2015下半年嵌入式系统设计师考试真题及答案-上午卷2015下半年嵌入式系统设计师考试真题及答案-上午卷 1、CPU是在(1)结束时响应DMA请求的。 A. —条指令执行 B. —段程序 C. 一个时钟周期 D. —个总线周期 答案: D DMA控制器在需要的时候代替CPU作为总线主设备,在不受CPU干预的情况下,控制I/O设备与系统主存之间的直接数据传输。DMA操作占用的资源是系统总线,而CPU并非在整个指令执行期间即指令周期内都会使用总线,故DMA请求的检测点设置在每个机器周期也即总线周期结束时执行,这样使得总线利用率最高。 2、虚拟存储体系由(2)两级存储器构成。 A. 主存-辅存 B. 寄存器-Cache C. 寄存器-主存 D. Cache-主存 答案: A 本题考查计算机组成原理的基础知识。 计算机中不同容量、不同速度、不同访问形式、不同用途的各种存储器形成的是一种层次结构的存储系统。所有的存储器设备按照一定的层次逻辑关系通过软硬件连接起来,并进行有效的管理,就形成了存储体系。不同层次上的存储器发挥着不同的作用。一般计算机系统中主要有两种存储体系:Cache存储体系由Cache和主存储器构成,主要目的是提高存储器速度,对系统程序员以上均透明;虚拟存储体系由主夺储器和在线磁盘存储器等辅存构成,主要目的是扩大存储器容量,对应用程序员透明。 3、浮点数能够表示的数的范围是由其(3)的位数决定的。 A. 尾数 B. 阶码 C. 数符 D. 阶符 答案: B 在计算机中使用了类似于十进制科学计数法的方法来表示二进制实数,因其表示不同的数时小数点位置的浮动不固定而取名浮点数表示法。浮点数编码由两部分组成:阶码(即指数,为带符号定点整数,常用移码表示,也有用补码的)和尾数(是定点纯小数,常用补码表示,或原码表示)。因此可以知道,浮点数的精度由尾数的位数决定,表示范围的大小则主要由阶码的位数决定。 4、在机器指令的地址字段中,直接指出操作数本身的寻址方式称为(4)。 A. 隐含寻址 B. 寄存器寻址 C. 立即寻址 D. 直接寻址 嵌入式系统基础作业一、简要说明嵌入式系统产品的基本组成、嵌入式系统特点、嵌入式系统开发流程; 答:基本组成:可分为硬件和软件两个组成部分。其中硬件组成结构以嵌入式微处理机为中心,配置存储器I/O设备、通信模块以及电源等必要的辅助借口;软件组成结构包括应用层、OS层、BSP等。 特点:“专用”计算机系统;运行环境差异大;比通用PC系统资源少;功耗低、体积小、集成度高、成本低;具有完整的系统测试和可靠性评估体系;具有较长的生命周期;需要专用开发工具和方法进行设计;包含专用调试电路;多科学知识集成系统。 开发流程:(1)系统定义与需求分析阶段。(2)方案设计阶段。(3)详细设计阶段。(4)软硬件集成测试阶段。(5)系统功能性及可靠性测试阶段。 二、写出教材图1-1嵌入式系统的组成结构中各英文缩写的中文释义; 答:.OS:操作系统 API:应用程序接口 BSP:板级支持包 Boot:启用装载 HAL:硬件抽象层 SoC/SoPC:片上系统/片上可编程系统 GPIO:控制处理器输出接口 USB:通用串行总线 LCD:液晶显示器 ADC/DAC:模数转换和数模转换 FPGA/CPLD:现场可编程门阵列/复杂可编程逻辑器件 UART/IrDA:通用异步收发传输器/红外线接口 DMA:直接内存访问 CAN:控制器局域网络 Timer/RTC:定时器/实时时钟 MMU/Cache:内存管理单元/高速缓冲存储器 三、比较说明FLASH存储器中NOR型和NAND型FLASH的主要区别;比较说明RAM 存储器中SRAM和SDRAM的主要区别; 答:NORFlash的读取和我们常见的SDRAM的读取是一样,用户可以直接运行装载在NORFLASH里面的代码,这样可以减少SRAM的容量从而节约了成本。NANDFlash没有采取内存的随机读取技术,它的读取是以一次读取一块的形式来进行的,通常是一次读取512个字节,采用这种技术的Flash比较廉价。SRAM是靠双稳态触发器来记忆信息的;SDRAM是靠MOS电路中的栅极电容来记忆信息的。由于电容上的电荷会泄漏,需要定时给与补充,所以动态RAM需要设置刷新电路。但动态RAM比静态RAM集成度高、功耗低,从而成本也低,适于作大容量存储器。所以主内存通常采用SDRAM,而高速缓冲存储器(Cache)则使用SRAM,在存取速度上,SRAM>SDRAM。 四、说明嵌入式系统常见硬件平台种类、典型处理器型号; 答:典型的型号有MIPS处理器、PowerPC处理器、Sparc处理器、ARM处理器、Xtensa系列可配置处理器。 五、嵌入式系统中常用的接口或通信方式有RS232、RS485、BlueTooth、CAN、IrDA、GPRS、SPI、GSM、802.11、SPI、IIC、Ethernet、JTAG等,请根据通信介质是否无线或有线对其进行分类;请根据通信距离从近至远依次排序;请根据通信速度从慢至快依次排序; 答:无线:RS485、BlueTooth、CAN、IrDA、GPRS、GSM、802.11、Ethernet 有线:RS232、SPI、IIC、JTAG 传输距离:RS232、SPI、IIC、JTAG、BlueTooTh、IrDA、RS485、CAN、802.11、GSM、GPRS、Ethernet 传输速度:GSM、GPRS、Blueteeth、IrDA、802.11、CAN、RS232、RS485、Ethernet、IIC、SPI、JTAG 六、列举常见嵌入式操作系统及其特点; 答:源代码公开并且遵循GPL协议 有大量的免费的优秀的开发工具,且都遵从GPL,是开放源代码的。 《嵌入式系统》设计方案移动打印终端终嵌入式系统设计方案 阅读目录 一项目概述 (2) 二系统总体架构 (2) 2.1.1 各功能部件作用 (3) 2.2.1 手持式扫描仪 (3) 2.2.2 嵌入式开发板 (4) 2.2.3 微型打印机的选型 (5) 2.2.4.远程服务器 (5) 三软/硬件设计 (5) 3.2 硬件设计 (7) 3.2.1 嵌入式开发板和扫描仪的连接 (7) 3.2.2嵌入式开发板和远程服务器的连接 (7) 3.2.3 嵌入式开发板和微型打印机的连接 (7) 四各驱动程序的设计(软件设计) (7) 4.1 打印机驱动的设计 (7) 4.1.1定义设备号和设备名 (7) 4.1.2 设备驱动初始化函数和清除函数 (8) 4.编译扫描仪制备驱动 (12) 5.加载设备 (12) 4.1.3 扫描仪驱动设计 (13) 4.1.4 网络通信模块及服务器的开发 (14) 4.1.5系统应用程序设计 (15) 五系统调试 (16) 一 项目概述 1.1 系统设计的必要性与PC 终端的比较 在信息社会中,打印终端应用非常广泛,比如超市的收银系统、图书管的借还书系统、移动营业厅的话费打印系统等场合,我们都可以看到打印终端的身影。传统打印终端通常都是由PC 加上一个微型打印机构成,这种架构的打印终端价格比较昂贵,体积庞大,移动笨拙,使用十分不方便。 随着嵌入式技术的发展,许多原来基于PC 的应用都纷纷转向基于嵌入式技术来实现。基于嵌入式技术的产品具有非常明显的优势,如价格便宜、功耗低、体积小及移动方便等。 具体到打印终端这个产品上来说,可以从下表看出基于PC 的打印终端和基于嵌入式的打印 1.2 系统的主要功能 本项目实例中拟开发的嵌入式移动打印终端是解决从数据输入、数据处理和数据输出的一体化系统,它提供下列几个功能 ● 数据录入功能:支持从扫描仪端录入数据; ● 通过网络到数据库查询; ● 数据打印功能 二 系统总体架构 嵌入式移动终端是一套完整的嵌入式应用系统,包括和硬件和软件两部分,这一节先说一下硬件方面的设计。 2.1 系统硬件组成的部件 ● 数据输入部件(手持扫描仪)—完成数据输入功能; ● 数据处理部件(嵌入式开发板和远程服务器)—完成数据处理任务 ● 数据输出部件(微型打印机)—完成数据打印功能; 各个部件之间的关系如图 嵌入式系统设计师 历年试题解析嵌入式系统设计师历年试题解析 本复习题页码标注所用教材为: 嵌入式系统技术张晓林2008年10月第1版高等教育出版社 如学员使用其他版本教材,请参考相关知识点 1. 嵌入式系统调试通常可以分为硬件级调试和在线仿真器调试。 考核知识点:嵌入式系统调试,参见P47 2. 在ARM处理器中,快速中断(FIQ)的优先级高于外部中断(IRQ)。 考核知识点:ARM处理器,参见P62 3. ROM能够永久或半永久地保存数据,ROM内的数据永远不会丢失。 考核知识点:存储器特点,参见P131 4. 内建测试系统(BIST)是SoC片上系统的重要结构之一,JTAG测试接口是IC芯片测试方法的标准。 考核知识点:嵌入式系统测试,参见P43 5. VHDL的基本单元描述不包括库。 考核知识点:SOC主要设计语言,参见P233 6. 嵌入式ARM架构的嵌入式处理器同时支持大端、小端(Big/Little-Endian)数据类型。 考核知识点:嵌入式ARM架构的嵌入式处理器,参见P16 7. 嵌入式操作系统通常采用整体式内核或层次式内核的结构。 考核知识点:嵌入式操作系统内核,参见P249 8. ARM7TDMI中的T代表增强型乘法器。 考核知识点:ARM处理器,参见71 9. 看门狗(Watch Dog)实际是一个简单的定时器,在固定时间内若正常清零,则自动复位处理器。 考核知识点:嵌入式式系统硬件设计,教材无参考答案 10. ARM-CPU由多家不同制造商生产,芯片外部提供的总线是不一致的。 考核知识点:嵌入式总线技术,参见P183 1.嵌入式处理器指令的执行周期包括() A.启动、运行、退出 B.取指令、指令译码、执行指令、存储 C.启动、运行、挂起、退出 D.取指令、指令译码、执行指令 考核知识点: ARM处理器指令周期,参见P69 2.下列不属于嵌入设计处理器本身带有的基本接口是() 嵌入式系统大作业嵌入式系统大作业-标准化文件发布号:(9456-EUATWK-MWUB-WUNN-INNUL-DDQTY-KII 基于嵌入式系统的车载GPS导航系统的设计 1 设计目的与功能 1.1 设计目的 随着人们经济基础增强,安全意识增强的基础上,很多人都会选择车载GPS 导航设备,所以制造功能强大,价格低廉的车载GPS导航设备是有很大市场和发展前景的。由于导航仪投入小,外壳模块、芯片等材料市场供应量大,这也是我选择设计车载GPS导航设备的理由。为了满足不同用户的不同需求,我想设计一款内置四维地图系统。 1.2设计功能 1提供准确无误的全3D实景导航; 2附带全国沿途咨询; 3具有视频、音乐播放等娱乐功能。 2.需求分析调研 2.1 产品的硬件组成(型号、类型、电气特性、选择的理由等) (1)处理器:S3C2440A 400MHz,S3C2440A 是三星公司生产推出的基于ARM920T的32位RISC嵌入式微处理器,S3C2440A采用了ARM920T的内核,0.13um的CMOS标准宏单元和存储器单元。 采用ARM920T CPU内核支持ARM调试体系结构。 (2)储存模块:SDRAM , K4M561633-75 , 64MByte Nand FLASH, K9F1208G 64MByte同步动态随机存储器,工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;存储阵列需要不断的刷新来保证数据不丢失;数据不是线性依次存储,而是自由指定地址进行数据读写。 (3)音频模块:PHILIPS公司的UDA1341TS是一块功能强大的专用语音处理芯片。本设计使用的AT91RM9200处理器具有一个IIS音频接口,此接口 2016年下半年嵌入式系统设计师(中级)上午选择+下午案例真题答案+解析完整版(全国计算机软考)2016年下半年嵌入式系统设计师真题+答案解析 上午选择 1、(1)用来区分在存储器中以二进制编码形式存放的指令和数据。 A. 指令周期的不同阶段 B. 指令和数据的寻址方式 C. 指令操作码的译码结果 D. 指令和数据所在的存储单元 答案:A 指令周期是执行一条指令所需要的时间,一般由若干个机器周期组成,是从取指令、分析指令到执行完所需的全部时间。CPU执行指令的过程中,根据时序部件发出的时钟信号按部就班进行操作。在取指令阶段读取到的是指令,在分析指令和执行指令时,需要操作数时再去读操作数。 2、计算机在一个指令周期的过程中,为从内存读取指令操作码,首先要将(2)的内容送到地址总线上。 A. 指令寄存器(IR) B. 通用寄存器(GR) C. 程序计数器(PC) D. 状态寄存器(PSW) 答案:C CPU首先从程序计数器(PC)获得需要执行的指令地址,从内存(或 高速缓存)读取到的指令则暂存在指令寄存器(IR),然后进行分析和执行。 3、设16位浮点数,其中阶符1位、阶码值6位、数符1位、尾数8位。若阶码用移码表示,尾数用补码表示,则该浮点数所能表示的数值范围是(3)。 A. -264~(1-2-8)264 B. -263~(1-2-8)263 C. -(1-2-8)264~(1-2-8)264 D. -(1-2-8)263~(1-2-8)263 答案:B 浮点格式表示一个二进制数N的形式为N=2E×F,其中E称为阶码,F叫做尾数。在浮点表示法中,阶码通常为含符号的纯整数,尾数为含符号的纯小数。 指数为纯整数,阶符1位、阶码6位在补码表示方式下可表示的最大数为63(26-1),最小数为-64(-26)。尾数用补码表示时最小数为-1、最大数为1-2-8,因此该浮点表示的最小数为-263,最大数为(1-2-8)×263。 4、已知数据信息为16位,最少应附加(4)位校验位,以实现海明码纠错。 A. 3 相关主题

文本预览

|