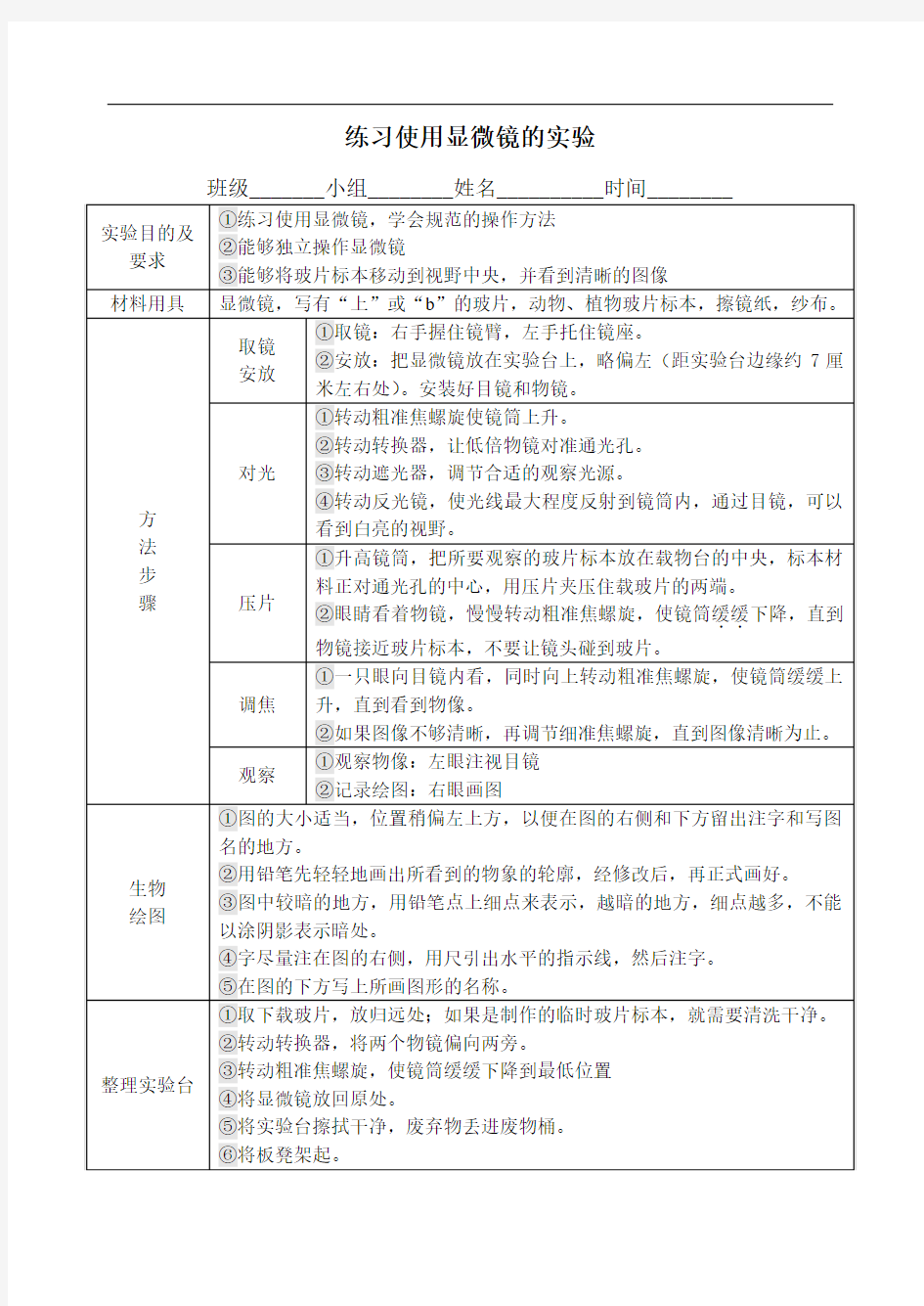

练习使用显微镜的实验

班级_______小组________姓名__________时间________

请将显微镜各部分的结构名称填写在方框内 班级_______小组________姓名__________时间________

实验二组合逻辑电路的设计 一、实验目的 1.掌握组合逻辑电路的设计方法及功能测试方法。 2.熟悉组合电路的特点。 二、实验仪器及材料 a) TDS-4数电实验箱、双踪示波器、数字万用表。 b) 参考元件:74LS86、74LS00。 三、预习要求及思考题 1.预习要求: 1)所用中规模集成组件的功能、外部引线排列及使用方法。 2) 组合逻辑电路的功能特点和结构特点. 3) 中规模集成组件一般分析及设计方法. 4)用multisim软件对实验进行仿真并分析实验是否成功。 2.思考题 在进行组合逻辑电路设计时,什么是最佳设计方案 四、实验原理 1.本实验所用到的集成电路的引脚功能图见附录 2.用集成电路进行组合逻辑电路设计的一般步骤是: 1)根据设计要求,定义输入逻辑变量和输出逻辑变量,然后列出真值表; 2)利用卡络图或公式法得出最简逻辑表达式,并根据设计要求所指定的门电路或选定的门电路,将最简逻辑表达式变换为与所指定门电路相应的形式; 3)画出逻辑图; 4)用逻辑门或组件构成实际电路,最后测试验证其逻辑功能。 五、实验内容 1.用四2输入异或门(74LS86)和四2输入与非门(74LS00)设计一个一位全加器。 1)列出真值表,如下表2-1。其中A i、B i、C i分别为一个加数、另一个加数、低位向本位的进位;S i、C i+1分别为本位和、本位向高位的进位。 A i B i C i S i C i+1 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 10 1 1 1 00 1 1 1 1 1 1 2)由表2-1全加器真值表写出函数表达式。

数字电路实验:基本逻辑门 一、实验目的 研究TTL 门电路的性能及测试方法。 二、实验仪器 (1) 双线示波器 (2)数字万用表 (3) TES-1电子技术学习机 三、实验内容 实验10.1 TTL 与非门7400逻辑功能的测试 1. 将输出Y 接发光二极管(Y=1时二极管亮;否则灭),改变A 、B 的电平值,记录实验结果,并将该结果列成真值表形式。 2. 在A 端加入连续脉冲(频率f=1Hz ),将输出Y 接发光二极管。当B 端分别接+5伏和0伏时,观察Y 端的输出变化,验证逻辑“0”对与非门的封锁作用。 A B Y 图10.1 实验10.2 TTL 与非门7400传输延迟时间的测量 按图10.2接线,输入端接1MHz 连续脉冲,通过用示波器观察其输入、输出波形相位差的办法,测量出四个与非门的累计传输延迟时间。 实验10.3 TTL 与非门7400电压传输特性的测定 按图10.3接线。 U i 接直流稳压电源,调节U i 使之在0~5V 范围内变化(注意:U i 值不能≥6V ,否则将损坏芯片),测出U o 随U i 变化的值,将它们填入表10.1中,并用曲线表示之,试粗糙确定U T 值。 u i u o 图10.2 +5V Uo

实验10.4 TTL 与非门7400输入端特性测试 按图10.4接线。 改变B 端所接的电阻值,分别测量并纪录相应的电压U B 及U o ,将结果填入表10.2中。 四、总结要求 (1) 根据表21.1,画出与非门7400的电压传输曲线。 (2) 根据表21.2,总结与非门7400的输入端特性。 表10.1 表10.2 +5V Uo 图10.4

塞曼效应实验 1.实验目的 (1)学习观察塞曼效应的方法,用法布里-珀罗标准具观测汞546.1nm谱线的塞满分裂。 (2)掌握塞曼效应分裂谱线裂距的测量方法,并与理论值比较烦算某一激励电流下磁感应强度B的大小。 2.实验原理 (1)磁场中的能级分裂——塞曼效应 塞曼效应的产生是由于源自的总磁矩受到磁场作用的结果,其有如下关系: 总磁矩与总角动量不再一条线上,计算后得到有效为 其中g为朗德因子, 当原子处于外磁场中,μ绕外磁场B作旋进,原子获得附加能量: 说明在稳定磁场的作用下,原来的一个能级,分裂成(2J+1)个能级。 (2)塞曼跃迁的选择定则 在外磁场作用下,上下量能级附加能量分别为ΔE2,ΔE1,则

其中 为洛伦兹单位,B的单位是T,L的单位为cm-1. (3)汞546.1nm谱线在磁场中的分裂 汞546.1nm波是汞原子从到能级跃迁时产生的,在磁场中分 裂产生9条谱线,相邻谱线裂距为,垂直于磁场方向观察,中间三条为π线,两边各三条为σ线。 (4)F-P标准具 F-P标准具为多光束干涉装置,单色平行光在其中形成同心圆环等倾干涉。 自由光谱范围: 由此可以确定d,在实验中d取2mm。 设Δ是标准具能分辨的最小波长差,通常定义 为分辨率 Δ 一般为了比较高的精确度取,R为90%以上。 (5)塞曼效应测量公式 用透镜将F-P标准具的干涉环成像在焦平面的圆环直径为D,有 变化得到 对于同一波长相邻级次k,k-1级圆环直径分别为,,其直径平方差

,可见是一个与干涉级次k无关的常数。 对于同一级次有微小波长差的不同波长,而言可以得到 3.实验仪器装置 电磁铁,笔形汞灯,聚光镜,偏振光,滤光片,望远镜测微目镜 4.实验内容及操作 在垂直方向用F-P标准具定性观察Hg546.1nm谱线的塞曼分裂,分析谱线的偏振成分,定量测量塞曼分裂间隔并反算磁感应强度B。 (1)准备工作 (2)光路调节 1)调节聚光镜 2)放置干涉滤光片 3)调节聚光镜、滤光片,标准具与光源大致共轴 4)调整测量望远镜的高度 (3)塞曼效应观测 1)在加磁场前后观察 2)加装偏振片 (4)测量 1)在时,选择子谱线中一对合适的谱线圆环(最好不选相邻环线),和其中之一环对应的低一级次的环,并记录所测子谱线的间隔个数,测量直 径。算出波数差,依据间隔个数算出B。

20090401310074 实验一数字基带信号 一、实验目的 1、了解单极性码、双极性码、归零码、不归零码等基带信号波形特点。 2、掌握AMI、HDB3码的编码规则。 3、掌握从HDB3码信号中提取位同步信号的方法。 4、掌握集中插入帧同步码时分复用信号的帧结构特点。 5、了解HDB3(AMI)编译码集成电路CD22103。 二、实验内容 1、用示波器观察单极性非归零码(NRZ)、传号交替反转码(AMI)、三阶高密度双极性码(HDB3)、整流后的AMI 码及整流后的HDB3 码。 2、用示波器观察从HDB3 码中和从AMI 码中提取位同步信号的电路中有关波形。 3、用示波器观察HDB3、AMI 译码输出波形。 三、基本原理 本实验使用数字信源模块和HDB3 编译码模块。 1、数字信源 本模块是整个实验系统的发终端,模块内部只使用+5V 电压,其原理方框图如图1-1 所示,电原理图见附录一。本单元产生NRZ 信号,信号码速率约为170.5KB,帧结构如图1-2 所示。帧长为24 位,其中首位无定义,第2 位到第8 位是帧同步码(7 位巴克码1110010),另外16 位为2 路数据信号,每路8位。此NRZ 信号为集中插入帧同步码时分复用信号,实验电路中数据码用红色发光二极管指示,帧同步码及无定义位用绿色发光二极管指示。发光二极管亮状态表示1 码,熄状态表示0 码。 图 1-1 数字信源方框图 图 2-2 帧结构

本模块有以下测试点及输入输出点: ?CLK 晶振信号测试点 ?BS-OUT 信源位同步信号输出点/测试点(2个) ?FS 信源帧同步信号输出点/测试点 ?NRZ-OUT(AK) NRZ信号(绝对码)输出点/测试点(4个)图1-1中各单元与电路板上元器件对应关系如下: ?晶振 CRY 晶体;U1:反相器7404 ?分频器 U2 计数器74161;U3:计数器74193;U4:计数器40160 并行码产生器 K1、K2、K3:8位手动开关,从左到右依次 与帧同步码、数据1、数据2相对应;发光二极管:左起分 别与一帧中的24位代码相对应 ?八选一 U5、U6、U7:8位数据选择器4512 ?三选一 U8:8位数据选择器4512 ?倒相器 U20:非门74HC04 ?抽样 U9:D触发器74HC74 下面对分频器,八选一及三选一等单元作进一步说明。 (1)分频器 4161进行13分频,输出信号频率为341kHz。74161是一个4位二进制加计数器,预置在3状态。 74193完成÷2、÷4、÷8、÷16运算,输出BS、S1、S2、S3等4个信号。BS 为位同步信号,频率为170.5kHz。S1、S2、S3为3个选通信号,频率分别为BS信号频率的1/2、1/4和1/8。74193是一个4位二进制加/减计数器,当CPD= PL =1、MR=0时,可在Q0、Q1、Q2及Q3端分别输出上述4个信号。 40160是一个二一十进制加计数器,预置在7状态,完成÷3运算,在Q0和Q1端分别输出选通信号S4、S5,这两个信号的频率相等、等于S3信号频率的1/3。 分频器输出的S1、S2、S3、S4、S5等5个信号的波形如图1-4(a)和1-4(b)所示。 图 1-4 分频器输出信号波形 (2)八选一 采用8路数据选择器4512,它内含了8路传输数据开关、地址译码器和三态驱动器,其真值表如表1-1所示。U5、U6和U7的地址信号输入端A、B、C并连在一起并分别接S1、S2、S3信号,它们的8个数据信号输入端x0 ~ x7分别K1、K2、K3输出的8个并行信号连接。由表1-1可以分析出U5、U6、U7输出信号都是码速率为

实验一常用基本逻辑门电路功能测试 一、实验目的 1.验证常用门电路的逻辑功能。 2.了解常用74LS系列门电路的引脚分布。 3.根据所学常用集成逻辑门电路设计一组合逻辑电路。 二、实验原理 集成逻辑门电路是最简单、最基本的数字集成元件。任何复杂的组合电路和时序电路都可用逻辑门通过适当的组合连接而成。目前已有门类齐全的集成门电路,例如“与门”、“或门”、“非门”、“与非门”等。虽然,中、大规模集成电路相继问世,但组成某一系统时,仍少不了各种门电路。因此,掌握逻辑门的工作原理,熟练、灵活地使用逻辑门是数字技术工作者所必备的基本功之一。 TTL门电路 TTL集成电路由于工作速度高、输出幅度较大、种类多、不易损坏而使用较广,特别对学生进行实验论证,选用TTL电路比较合适。因此,本书大多采用74LS(或74)系列TTL 集成电路。它的工作电源电压为5V土0.5V,逻辑高电平1时≥2.4V,低电平0时≤0.4V。2输入“与门”,2输入“或门”,2输入、4输入“与非门”和反相器的型号分别是:74LS08:2输入端四“与门”,74LS32:2输入端四“或门”,74LS00:2输入端四“与非门”,74LS20:4输入端二“与非门”和74LS04六反相器(“反相器”即“非门”)。各自的逻辑表达式分别为:与门Q=A?B,或门Q=A+B,与非门Q=A.B,Q=A.B.C.D,反相器Q=A。

TTL集成门电路集成片管脚分别对应逻辑符号图中的输入、输出端,电源和地一般为集成片的两端,如14管脚集成片,则7脚为电源地(GND),14脚为电源正(V cc),其余管脚为输入和输出,如图1所示。 管脚的识别方法是:将集成块正面(有字的一面)对准使用者,以左边凹口或小标志点“ ? ”为起始脚,从下往上按逆时针方向向前数1、2、3、…… n脚。使用时,查找IC 手册即可知各管脚功能。 图1 74LS08集成电路管脚排列图 三、实验内容与步骤 TTL门电路逻辑功能验证 (1)与门功能测试:将74LS08集成片(管脚排列图1)插入IC空插座中,输入端接逻辑开关,输出端接LED发光二极管,管脚14接+5V电源,管脚7接地,即可进行实验。将结果用逻辑“0”或“1”来表示并填入表1中。

应物31 吕博成学号:10

塞曼效应 1896年,荷兰物理学家塞曼()在实验中发现,当光源放在足够强的磁场中时,原来的一条光谱线会分裂成几条光谱线,分裂的条数随能级类别的不同而不同,且分裂的谱线是偏振光。这种效应被称为塞曼效应。 需要首先指出的是,由于实验先后以及实验条件的缘故,我们把分裂成三条谱线,裂距按波数计算正好等于一个洛伦兹单位的现象叫做正常塞曼效应(洛伦兹单位 mc eB L π4=)。而实际上大多数谱线的塞曼分裂谱线多于三条,谱线的裂距可以大于也可 以小于一个洛伦兹单位,人们称这类现象为反常塞曼效应。反常塞曼效应是电子自旋假设的有力证据之一。通过进一步研究塞曼效应,我们可以从中得到有关能级分裂的数据,如通过能级分裂的条数可以知道能级的J 值;通过能级的裂距可以知道g 因子。 塞曼效应至今仍然是研究原子能级结构的重要方法之一,通过它可以精确测定电子的荷质比。 一.实验目的 1.学习观察塞曼效应的方法观察汞灯发出谱线的塞曼分裂; 2.观察分裂谱线的偏振情况以及裂距与磁场强度的关系; 3.利用塞曼分裂的裂距,计算电子的荷质比e m e 数值。 二.实验原理 1、谱线在磁场中的能级分裂 设原子在无外磁场时的某个能级的能量为0E ,相应的总角动量量子数、轨道量子数、自旋量子数分别为S L J 、、。当原子处于磁感应强度为B 的外磁场中时,这一原子能级将分裂为12+J 层。各层能量为 B Mg E E B μ+=0 (1) 其中M 为磁量子数,它的取值为J ,1-J ,...,J -共12+J 个;g 为朗德因子;B μ为玻尔磁矩(m hc B πμ4= );B 为磁感应强度。 对于S L -耦合 ) () ()()(121111++++-++ =J J S S L L J J g (2) 假设在无外磁场时,光源某条光谱线的波数为 )(010201~E E hc -=γ (3) 式中 h 为普朗克常数;c 为光速。

实验六 数字基带信号的眼图实验 一、实验目的 1、掌握无码间干扰传输的基本条件和原理,掌握基带升余弦滚降系统的实现方法; 2、通过观察眼图来分析码间干扰对系统性能的影响,并观察在输入相同码率的NRZ 基带信号下,不同滤波器带宽对输出信号码间干扰大小的影响程度; 3、熟悉MATLAB 语言编程。 二、实验原理和电路说明 1、基带传输特性 基带系统的分析模型如图3-1所示,要获得良好的基带传输系统,就应该 图3-1 基带系统的分析模型 抑制码间干扰。设输入的基带信号为()n s n a t nT δ-∑,s T 为基带信号的码元周期,则经过 基带传输系统后的输出码元为 ()n s n a h t nT -∑。其中 1()()2j t h t H e d ωωωπ +∞ -∞ = ? (3-1) 理论上要达到无码间干扰,依照奈奎斯特第一准则,基带传输系统在时域应满足: 10()0,s k h kT k =?=? ? , 为其他整数 (3-2) 频域应满足: ()0,s s T T H πωωω? ≤ ?=? ?? ,其他 (3-3)

图3-2 理想基带传输特性 此时频带利用率为2/Baud Hz ,这是在抽样值无失真条件下,所能达到的最高频率利用率。 由于理想的低通滤波器不容易实现,而且时域波形的拖尾衰减太慢,因此在得不到严格 定时时,码间干扰就可能较大。在一般情况下,只要满足: 222(),s i s s s s i H H H H T T T T T ππ π π ωωωωω?????? +=-+++=≤ ? ? ??????? ∑ (3-4) 基带信号就可实现无码间干扰传输。这种滤波器克服了拖尾太慢的问题。 从实际的滤波器的实现来考虑,采用具有升余弦频谱特性()H ω时是适宜的。 (1)(1)1sin (),2(1)()1,0(1) 0,s s s s s s T T T T H T T ππαπαωωαπαωωπαω???-+--≤≤??? ??? ?-? =≤≤?? ?+>? ?? (3-5) 这里α称为滚降系数,01α≤≤。 所对应的其冲激响应为: ()222sin cos()()14s s s s t T t T h t t t T T παππα= - (3-6) 此时频带利用率降为2/(1)Baud/Hz α+,这同样是在抽样值无失真条件下,所能达到的最 高频率利用率。换言之,若输入码元速率' 1/s s R T >,则该基带传输系统输出码元会产生码

实验一 组合逻辑电路的设计 一、实验目的: 1、 掌握组合逻辑电路的设计方法。 2、 掌握组合逻辑电路的静态测试方法。 3、 加深FPGA 设计的过程,并比较原理图输入和文本输入的优劣。 4、 理解“毛刺”产生的原因及如何消除其影响。 5、 理解组合逻辑电路的特点。 二、实验的硬件要求: 1、 EDA/SOPC 实验箱。 2、 计算机。 三、实验原理 1、组合逻辑电路的定义 数字逻辑电路可分为两类:组合逻辑电路和时序逻辑电路。组合逻辑电路中不包含记忆单元(触发器、锁存器等),主要由逻辑门电路构成,电路在任何时刻的输出只和当前时刻的输入有关,而与以前的输入无关。时序电路则是指包含了记忆单元的逻辑电路,其输出不仅跟当前电路的输入有关,还和输入信号作用前电路的状态有关。 通常组合逻辑电路可以用图1.1所示结构来描述。其中,X0、X1、…、Xn 为输入信号, L0、L1、…、Lm 为输出信号。输入和输出之间的逻辑函数关系可用式1.1表示: 2、组合逻辑电路的设计方法 组合逻辑电路的设计任务是根据给定的逻辑功能,求出可实现该逻辑功能的最合理组 合电路。理解组合逻辑电路的设计概念应该分两个层次:(1)设计的电路在功能上是完整的,能够满足所有设计要求;(2)考虑到成本和设计复杂度,设计的电路应该是最简单的,设计最优化是设计人员必须努力达到的目标。 在设计组合逻辑电路时,首先需要对实际问题进行逻辑抽象,列出真值表,建立起逻辑模型;然后利用代数法或卡诺图法简化逻辑函数,找到最简或最合理的函数表达式;根据简化的逻辑函数画出逻辑图,并验证电路的功能完整性。设计过程中还应该考虑到一些实际的工程问题,如被选门电路的驱动能力、扇出系数是否足够,信号传递延时是否合乎要求等。组合电路的基本设计步骤可用图1.2来表示。 3、组合逻辑电路的特点及设计时的注意事项 ①组合逻辑电路的输出具有立即性,即输入发生变化时,输出立即变化。(实际电路中 图 1.1 组合逻辑电路框图 L0=F0(X0,X1,···Xn) · · · Lm=F0(X0,X1,···Xn) (1.1) 图 1.2 组合电路设计步骤示意图图

实验一基本门电路的逻辑功能测试 一、实验目的 1、测试与门、或门、非门、与非门、或非门与异或门的逻辑功能。 2、了解测试的方法与测试的原理。 二、实验原理 实验中用到的基本门电路的符号为: 在要测试芯片的输入端用逻辑电平输出单元输入高低电平,然后使用逻辑电平显示单元显示其逻辑功能。 三、实验设备与器件 1、数字逻辑电路用PROTEUS 2、显示可用发光二极管。 3、相应74LS系列、CC4000系列或74HC系列芯片若干。 四、实验内容 1.测试TTL门电路的逻辑功能: a)测试74LS08的逻辑功能。(与门)000 010 100 111 b)测试74LS32的逻辑功能。(或门)000 011 101 111 c)测试74LS04的逻辑功能。(非门)01 10 d)测试74LS00的逻辑功能。(两个都弄得时候不亮,其他都亮)(与非门)(如果只接一个的话,就是非门)001 011 101 110 e)测试74LS02(或非门)的逻辑功能。(两个都不弄得时候亮,其他不亮)001 010 100 110 f)测试74LS86(异或门)的逻辑功能。 2.测试CMOS门电路的逻辑功能:在CMOS 4000分类中查询 a)测试CC4081(74HC08)的逻辑功能。(与门) b)测试CC4071(74HC32)的逻辑功能。(或门) c)测试CC4069(74HC04)的逻辑功能。(非门) d)测试CC4011(74HC00)的逻辑功能。(与非门)(如果只接一个的话,就是非门)

e)测试CC4001(74HC02)(或非门)的逻辑功能。 f) 测试CC4030(74HC86)(异或门)的逻辑功能。 五、实验报告要求 1.画好各门电路的真值表表格,将实验结果填写到表中。 2.根据实验结果,写出各逻辑门的逻辑表达式,并分析如何判断逻辑门的好坏。 3.比较一下两类门电路输入端接入电阻或空置时的情况。 4.查询各种集成门的管脚分配,并注明各个管脚的作用与功能。 例:74LS00 与门 Y=AB

塞曼效应实验报告 一、实验目的与实验仪器 1. 实验目的 (1)学习观察塞曼效应的方法,通过塞曼效应测量磁感应强度的大小。 (2)学习一种测量电子荷质比的方法。 2.实验仪器 笔形汞灯+电磁铁装置,聚光透镜,偏振片,546nm滤光片,F-P标准具,标准具间距(d=2mm),成像物镜与测微目镜组合而成的测量望远镜。 二、实验原理 (要求与提示:限400字以内,实验原理图须用手绘后贴图的方式) 1.塞曼效应 (1)原子磁矩和角动量关系 用角动量来描述电子的轨道运动和自旋运动,原子中各电子轨道运动角动量的矢量和即原子的轨道角动量L,考虑L-S耦合(轨道-自旋耦合),原子的角动量J =L +S。量子力学理论给出各磁矩与角动量的关系: L = - L,L = S = - S,S = 由上式可知,原子总磁矩和总角动量不共线。则原子总磁矩在总角动量方向上的分量 为: J = g J,J = J L为表示原子的轨道角量子数,取值:0,1,2… S为原子的自旋角量子数,取值:0,1/2,1,3/2,2,5/2… J为原子的总角量子数,取值:0,1/2,1,3/2… 式中,g=1+为朗德因子。 (2)原子在外磁场中的能级分裂 外磁场存在时,与角动量平行的磁矩分量J与磁场有相互作用,与角动量垂直的磁矩分量与磁场无相互作用。由于角动量的取向是量子化的,J在任意方向的投影(如z方向)为: = M,M=-J,-(J-1),-(J-2),…,J-2,J-1,J 因此,原子磁矩也是量子化的,在任意方向的投影(如z方向)为: =-Mg 式中,玻尔磁子μB =,M为磁量子数。

具有磁矩为J的原子,在外磁场中具有的势能(原子在外磁场中获得的附加能量): ΔE = -J·=Mg B 则根据M的取值规律,磁矩在空间有几个量子化取值,则在外场中每一个能级都分裂为等间隔的(2J+1)个塞曼子能级。原子发光过程中,原来两能级之间电子跃迁产生的一条光谱线也分裂成几条光谱线。这个现象叫塞曼效应。 2.塞曼子能级跃迁选择定则 (1)选择定则 未加磁场前,能级E2和E1之间跃迁光谱满足: hν = E2 - E1 加上磁场后,新谱线频率与能级之间关系满足: hν’= (E2+ΔE2) – (E1+ΔE1) 则频率差:hΔν= ΔE2-ΔE1= M2g2 B -M1g1B= (M2g2- M1g1)B 跃迁选择定则必须满足: ΔM = 0,±1 (2)偏振定则 当△M=0时,产生π线,为振动方向平行于磁场的线偏振光,可在垂直磁场方向看到。 当△M=±1时,产生σ谱线,为圆偏振光。迎着磁场方向观察时,△M=1的σ线为左旋圆偏振光,△M=-1的σ线为右旋圆偏振光。在垂直于磁场方向观察σ线时,为振动方向垂直于磁场的线偏振光。 3. 能级3S13P2 L01 S11 J12 g23/2 M10-1210-1-2 Mg20-233/20-3/2-3汞原子的绿光谱线波长为,是由高能级{6s7s}S1到低能级{6s6p}P2能级之间的跃迁,其上下能级有关的量子数值列在表1。3S1、3P2表示汞的原子态,S、P分别表示原子轨道量子数L=0和1,左上角数字由自旋量子数S决定,为(2S+1),右下角数字表示原子的总角动量量子数J。 在外磁场中能级分裂如图所示。外磁场为0时,只有的一条谱线。在外场的作用下,上能级分裂为3条,下能级分裂为5条。在外磁场中,跃迁的选择定则对磁量子数M的要求为:△M=0,±1,因此,原先的一条谱线,在外磁场中分裂为9条谱线。 9条谱线的偏振态,量子力学理论可以给出:在垂直于磁场方向观察,9条分裂谱线的强度(以中心谱线的强度为100)随频率增加分别为,,75,75,100,75,75,,. 标准具 本实验通过干涉装置进行塞曼效应的观察。我们选择法布里-珀罗标准具(F-P标准具)作为干涉元件。F-P标准具基本组成:两块平行玻璃板,在两板相对的表面镀有较高反射率的薄膜。 多光束干涉条纹的形成

基带传输系统实验报告 一、 实验目的 1、 提高独立学习的能力; 2、 培养发现问题、解决问题和分析问题的能力; 3、 学习matlab 的使用; 4、 掌握基带数字传输系统的仿真方法; 5、 熟悉基带传输系统的基本结构; 6、 掌握带限信道的仿真以及性能分析; 7、 通过观察眼图和星座图判断信号的传输质量。 二、 实验原理 在数字通信中,有些场合可以不经载波调制和解调过程而直接传输基带信号,这种直接传输基带信号的系统称为基带传输系统。 基带传输系统方框图如下: 基带脉冲输入 噪声 基带传输系统模型如下: 信道信号 形成器 信道 接收 滤波器 抽样 判决器 同步 提取 基带脉冲

各方框的功能如下: (1)信道信号形成器(发送滤波器):产生适合于信道传输的基带信号波形。因为其输入一般是经过码型编码器产生的传输码,相应的基本波形通常是矩形脉 冲,其频谱很宽,不利于传输。发送滤波器用于压缩输入信号频带,把传输 码变换成适宜于信道传输的基带信号波形。 (2)信道:是基带信号传输的媒介,通常为有限信道,如双绞线、同轴电缆等。信道的传输特性一般不满足无失真传输条件,因此会引起传输波形的失真。另 外信道还会引入噪声n(t),一般认为它是均值为零的高斯白噪声。 (3)接收滤波器:接受信号,尽可能滤除信道噪声和其他干扰,对信道特性进行均衡,使输出的基带波形有利于抽样判决。 (4)抽样判决器:在传输特性不理想及噪声背景下,在规定时刻(由位定时脉冲控制)对接收滤波器的输出波形进行抽样判决,以恢复或再生基带信号。 (5)定时脉冲和同步提取:用来抽样的位定时脉冲依靠同步提取电路从接收信号中提取。 三、实验内容 1采用窗函数法和频率抽样法设计线性相位的升余弦滚讲的基带系统(不调用滤波器设计函数,自己编写程序) 设滤波器长度为N=31,时域抽样频率错误!未找到引用源。o为4 /Ts,滚降系数分别取为0.1、0.5、1, (1)如果采用非匹配滤波器形式设计升余弦滚降的基带系统,计算并画出此发送滤波器的时域波形和频率特性,计算第一零点带宽和第一旁瓣衰减。 (2)如果采用匹配滤波器形式设计升余弦滚降的基带系统,计算并画出此发送滤波器的时域波形和频率特性,计算第一零点带宽和第一旁瓣衰减。 (1)非匹配滤波器 窗函数法: 子函数程序: function[Hf,hn,Hw,w]=umfw(N,Ts,a)

实验报告 课程名称: 数字电子技术实验 指导老师: 成绩:__________________ 实验名称: 组合逻辑电路 实验类型: 设计型实验 同组学生姓名:__________ 一、实验目的和要求(必填) 二、实验内容和原理(必填) 三、主要仪器设备(必填) 四、操作方法和实验步骤 五、实验数据记录和处理 六、实验结果与分析(必填) 七、讨论、心得 一.实验目的和要求 1. 加深理解典型组合逻辑电路的工作原理。 2. 熟悉74LS00、74LS11、74LS55等基本门电路的功能及其引脚。 3. 掌握组合集成电路元件的功能检查方法。 4. 掌握组合逻辑电路的功能测试方法及组合逻辑电路的设计方法。 5. 熟悉全加器和奇偶位判断电路的工作原理。 二.实验内容和原理 组合逻辑电路设计的一般步骤如下: 1.根据给定的功能要求,列出真值表; 2. 求各个输出逻辑函数的最简“与-或”表达式; 3. 将逻辑函数形式变换为设计所要求选用逻辑门的形式; 4. 根据所要求的逻辑门,画出逻辑电路图。 实验内容: 1. 测试与非门74LS00和与或非门74LS55的逻辑功能。 2. 用与非门74LS00和与或非门74LS55设计一个全加器电路,并进行功能测试。 专业: 电子信息工程 姓名: 学号: 日期: 装 订 线

3. 用与非门74LS00和与或非门74LS55设计四位数奇偶位判断电路,并进行功能测试。 三. 主要仪器设备 与非门74LS00,与或非门74LS55,导线,开关,电源、实验箱 四.实验设计与实验结果 1、一位全加器 全加器实现一位二进制数的加法,他由被加数、加数和来自相邻低位的进数相加,输出有全加和与向高位的进位。输入:被加数Ai,加数Bi,低位进位Ci-1输出:和Si,进位Ci 实验名称:组合逻辑电路 姓名:学号: 列真值表如下:画出卡诺图: 根据卡诺图得出全加器的逻辑函数:S= A⊕B⊕C; C= AB+(A⊕B)C 为使得能在现有元件(两个74LS00 与非门[共8片]、三个74LS55 与或非门)的基础上实现该逻辑函数。所以令S i-1=!(AB+!A!B),Si=!(SC+!S!C), Ci=!(!A!B+!C i-1S i-1)。 仿真电路图如下(经验证,电路功能与真值表相同):

实验一逻辑门电路的基本参数及逻辑功能测试 一、实验目的 1、了解TTL与非门各参数的意义。 2、掌握TTL与非门的主要参数的测试方法。 3、掌握基本逻辑门的功能及验证方法。 4、学习TTL基本门电路的实际应用。 5、了解CMOS基本门电路的功能。 6、掌握逻辑门多余输入端的处理方法。 二、实验仪器 三、实验原理 (一) 逻辑门电路的基本参数 用万用表鉴别门电路质量的方法:利用门的逻辑功能判断,根据有关资料掌握电路组件管脚排列,尤其是电源的两个脚。按资料规定的电源电压值接好(5V±10%)。在对TTL与 非门判断时,输入端全悬空,即全“1”,则输出端用万用表测 应为0.4V以下,即逻辑“0”。若将其中一输入端接地,输出 端应在3.6V左右(逻辑“1”),此门为合格门。按国家标准 的数据手册所示电参数进行测试:现以手册中74LS20二-4输 入与非门电参数规范为例,说明参数规范值和测试条件。 TTL与非门的主要参数 空载导通电源电流I CCL (或对应的空载导通功耗P ON )与非门处于不同的工作状态,电 源提供的电流是不同的。I CCL 是指输入端全部悬空(相当于输入全1),与非门处于导通状态,

输出端空载时,电源提供的电流。将空载导通电源电流I CCL 乘以电源电压就得到空载导通功 耗P ON ,即 P ON = I CCL ×V CC 。 测试条件:输入端悬空,输出空载,V CC =5V。 通常对典型与非门要求P ON <50mW,其典型值为三十几毫瓦。 2、空载截止电源电流I CCh (或对应的空载截止功耗P OFF ) I CCh 是指输入端接低电平,输出端开路时电源提供的电流。空载截止功耗POFF为空载 截止电源电流I CCH 与电源电压之积,即 P OFF = I CCh ×V CC 。注意该片的另外一个门的输入也要 接地。 测试条件: V CC =5V,V in =0,空载。 对典型与非门要求P OFF <25mW。 通常人们希望器件的功耗越小越好,速度越快越好,但往往速度高的门电路功耗也较大。 3、输出高电平V OH 输出高电平是指与非门有一个以上输入端接地或接低电平的输出电平。空载时,输出 高电平必须大于标准高电压(V SH =2.4V);接有拉电流负载时,输出高电平将下降。 4、输出低电平V OL 输出低电平是指与非门所有输入端接高电平时的输出电平。空载时,输出低电平必须低于标准低电压(VSL=0.4V);接有灌电流负载时,输出低电平将上升。 5、低电平输入电流I IS (I IL ) I IS 是指输入端接地输出端空载时,由被测输入端流出的电流值,又称低电平输入短路 电流,它是与非门的一个重要参数,因为入端电流就是前级门电路的负载电流,其大小直 接影响前级电路带动的负载个数,因此,希望I IS 小些。 测试条件: VCC=5V,被测某个输入端通过电流表接地,其余各输入端悬空,输出空载。

1、前言和实验目的 1.了解和掌握WPZ-Ⅲ型塞曼效应仪和利用其研究谱线的精细结构。 2.了解法布里-珀罗干涉仪的的结构和原理及利用它测量微小波长差值。 3.观察汞546.1nm (绿色)光谱线的塞曼效应,测量它分裂的波长差,并计算电子的荷质比的实验值和标准值比较。 2、实验原理 处于磁场中的原子,由于电子的j m 不同而引起能级的分裂,导致跃迁时发出的光子的频率产生分裂的现象就成为塞曼效应。下面具体给出公式推导处于弱磁场作用下的电子跃迁所带来的能级分裂大小。 总磁矩为 J μ 的原子体系,在外磁场为B 中具有的附加能为: E ?= -J μ *B 由于我们考虑的是反常塞曼效应,即磁场为弱磁场,认为不足以破坏电子的轨道-自旋耦合。则我们有: E ?= -z μB =B g m B J J μ 其中z μ为J μ 在z 方向投影,J m 为角动量J 在z 方向投影的磁量子数,有12+J 个值,B μ= e m eh π4称为玻尔磁子,J g 为朗德因子,其值为 J g =) 1(2) 1()1()1(1++++-++ J J S S L L J J 由于J m 有12+J 个值,所以处于磁场中将分裂为12+J 个能级,能级间隔为B g B J μ。当没有磁场时,能级处于简并态,电子的态由n,l,j (n,l,s )确定,跃迁的选择定则为Δs=0, Δl=1±.而处于磁场中时,电子的态由n,l,j,J m ,选择定则为Δs=0,Δl=1±,1±=?j m 。 磁场作用下能级之间的跃迁发出的谱线频率变为: )()(1122' E E E E hv ?+-?+==h ν+(1122g m g m -)B μB 分裂的谱线与原谱线的频率差ν?为: ν?=' ν-ν=h B g m g m B /)(1122μ-、 λ?= c ν λ?2 =2λ (1122g m g m -)B μB /hc =2 λ (1122g m g m -)L ~

电子信息工程晓旭 2011117147 实验一组合逻辑电路设计(含门电路功能测试) 一.实验目的 1掌握常用门电路的逻辑功能。 2掌握用小规模集成电路设计组合逻辑电路的方法。 3掌握组合逻辑电路的功能测试方法。 二.实验设备与器材 数字电路实验箱一个 双踪示波器一部 稳压电源一部 数字多用表一个 74LS20 二4 输入与非门一片 74LS00 四2 输入与非门一片 74LS10 三3 输入与非门一片 三 .实验任务 1对74LS00,74LS20逻辑门进行功能测试。静态测试列出真值表,动态测试画出波形图,并说明测试的门电路功能是否正常。 2分析测试1.7中各个电路逻辑功能并根据测试结果写出它们的逻辑表达式。 3设计控制楼梯电灯的开关控制器。设楼上,楼下各装一个开关,要求两个开关均可以控制楼梯电灯。 4某公司设计一个优先级区分器。该公司收到有A,B,C,三类,A,类的优先级最高,B 类次之,C类最低。到达时,其对应的指示灯亮起,提醒工作人员及时处理。当不同类的同时到达时,对优先级最高的先做处理,其对应的指示灯亮,优先级低的暂不理会。按组合逻辑电路的一般设计步骤设计电路完成此功能,输入输出高低电平代表到

实验一: (1)74LS00的静态逻辑功能测试 实验器材:直流电压源,电阻,发光二极管,74LS00,与非门,开关,三极管 实验目的:静态逻辑功能测试用来检查门电路的真值表,确认门电路的逻辑功能正确与否 实验过程:将74LS00中的一个与非门的输入端A,B分别作为输入逻辑变量,加高低电平,观测输出电平是否符合真值表描述功能。 电路如图1: 图1 真值表1.1: 实验问题:与非门的引脚要连接正确,注意接地线及直流电源 实验结果:由二极管的发光情况可判断出74LS00 实现二输入与非门的功能 (2)71LS00的动态逻辑功能测试 实验器材:函数发生器,示波器,74LS00,与非门,开关,直流电压源 实验目的:测试74LS00与非门的逻辑功能 实验容:动态测试适合用于数字系统中逻辑功能的检查,测试时,电路输入串行数字

近代物理实验报告 塞曼效应实验 学院 班级 姓名 学号 时间 2014年3月16日

塞曼效应实验实验报告 【摘要】: 本实验通过塞曼效应仪与一些观察装置观察汞(Hg)546.1nm谱线(3S1→3P2跃迁)的塞曼分裂,从理论上解释、分析实验现象,而后给出横效应塞满分裂线的波数增量,最后得出荷质比。 【关键词】:塞曼效应、汞546.1nm、横效应、塞满分裂线、荷质比 【引言】: 塞曼效应是原子的光谱线在外磁场中出现分裂的现象,是1896年由荷兰物理学家塞曼发现的。首先他发现,原子光谱线在外磁场发生了分裂;随后洛仑兹在理论上解释了谱线分裂成3条的原因,这种现象称为“塞曼效应”。在后来进一步研究发现,很多原子的光谱在磁场中的分裂情况有别于前面的分裂情况,更为复杂,称为反常塞曼效应。 塞曼效应的发现使人们对物质光谱、原子、分子有更多了解,塞曼效应证实了原子磁矩的空间量子化,为研究原子结构提供了重要途径,被认为是19世纪末20世纪初物理学最重要的发现之一。利用塞曼效应可以测量电子的荷质比。在天体物理中,塞曼效应可以用来测量天体的磁场。本实验采取Fabry-Perot(以下简称F-P)标准具观察Hg的546.1nm谱线的塞曼效应,同时利用塞满效应测量电子的荷质比。 【正文】: 一、塞曼分裂谱线与原谱线关系 1、磁矩在外磁场中受到的作用 (1)原子总磁矩在外磁场中受到力矩的作用: 其效果是磁矩绕磁场方向旋进,也就是总角动量(P J)绕磁场方向旋进。 (2)磁矩在外磁场中的磁能:

由于或在磁场中的取向量子化,所以其在磁场方向分量也量子化: ∴原子受磁场作用而旋进引起的附加能量 M为磁量子数 g为朗道因子,表征原子总磁矩和总角动量的关系,g随耦合类型不同(LS耦合和jj耦合)有两种解法。在LS耦合下: 其中: L为总轨道角动量量子数 S为总自旋角动量量子数 J为总角动量量子数 M只能取J,J-1,J-2 …… -J(共2J+1)个值,即ΔE有(2J+1)个可能值。 无外磁场时的一个能级,在外磁场作用下将分裂成(2J+1)个能级,其分裂的能级是等间隔的,且能级间隔 2、塞曼分裂谱线与原谱线关系: (1) 基本出发点:

数字基带信号实验 一、实验目的: 学会利用MATLAB软件对数字基带信号的仿真。通过实验提高学生实际动手 能力和编程能力,为日后从事通信工作奠定良好的基础。 二、实验内容:利用MATLAB软件编写数字基带信号程序,进一步加强对数字基 带信号的理解。 (1)单极性不归零数字基带信号 (2)双极性不归零数字基带信号 (3)单极性归零数字基带信号 (4)双极性归零数字基带信号 三、程序 (1) 单极性不归零数字基带信号程序 function y=zhou(x) t0=200; t=0:1/t0:length(x); for i=1:length(x) if(x(i)==1) for j=1:t0 y((i-1)*t0+j)=1; end else for j=1:t0 y((i-1)*t0+j)=0; end end end y=[y,x(i)]; M=max(y); m=min(y); subplot(1,1,1) plot(t,y);grid on; axis([0,i,m-0.1,M+0.1]); title('1 0 0 1 1 0 0 0 0 1 0 1'); (2) 双极性不归零数字基带信号 function y=zhou(x) t0=200; t=0:1/t0:length(x); for i=1:length(x) if(x(i)==1) for j=1:t0

y((i-1)*t0+j)=1; end else for j=1:t0 y((i-1)*t0+j)=-1; end end end y=[y,x(i)]; M=max(y); m=min(y); subplot(1,1,1) plot(t,y);grid on; axis([0,i,m-0.1,M+0.1]); title('1 0 0 1 1 0 0 0 0 1 0 1'); (3)单极性归零数字基带信号 function y=zhou(x) t0=200; t=0:1/t0:length(x); for i=1:length(x) if(x(i)==1) for j=1:t0/2 y((2*i-2)*t0/2+j)=1; y((2*i-1)*t0/2+j)=0; end else for j=1:t0 y((i-1)*t0+j)=0; end end end y=[y,x(i)]; M=max(y); m=min(y); subplot(1,1,1) plot(t,y);grid on; axis([0,i,m-0.1,M+0.1]); title('1 0 0 1 1 0 0 0 0 1 0 1') (4)双极性归零数字基带信号 function y=zhou(x) t0=200; t=0:1/t0:length(x);

湖北第二师范学院实验 组合逻辑电路 物机学院-11应用物理学 一、实验目的 1.掌握用与非门组成的简单电路,并测试其逻辑功能。 2.掌握用基本逻辑门设计组合电路的方法。 二、实验原理 数字电路按逻辑功能和电路结构的不同特点,可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路是根据给定的逻辑问题,设计出能实现逻辑功能的电路。用小规模集成电路实现组合逻辑电路,要求是使用的芯片最少,连线最少。一般设计步骤如下: 1.首先根据实际情况确定输入变量、输出变量的个数,列出逻辑真值表。 2.根据真值表,一般采用卡诺图进行化简,得出逻辑表达式。 3.如果已对器件类型有所规定或限制,则应将函数表达式变换成与器件类型相适应 的形式。 4.根据化简或变换后的逻辑表达式,画出逻辑电路。 5.根据逻辑电路图,查找所用集成器件的管脚图,将管脚号标在电路图上,再接线 验证。 三、实验仪器及器件 数字实验箱一台,集成芯片74LS00一块、74LS20三块,导线若干。 四、实验内容 1.用非与门实现异或门的逻辑功能 (1) 用集成电路74LS00和74LS20(74LS20管脚见图1所示),按图2连接电路(自己设计接线脚标),A、B接输入逻辑,F接输出逻辑显示,检查无误,然后开启电源。 图1 74LS20集成电路管脚图 (2) 按表1的要求进行测量,将输出端F的逻辑状态填入表内.

表1 输出真值表 图 2-电路接线图 (3) 由逻辑真值表,写出该电路的逻辑表达式 F= B A B A ?+? 2. 用与非门组成“三路表决器” (1) 用74LS00和74LS20组成三路表决器,按图3连接电路(自己设计接线脚标),A ,B ,C 接输入逻辑,F 接输出逻辑显示,检查无误,然后开启电源。 (2) 按表2的要求进行测量,将输出端F 的逻辑状态填入表内。 A 表 2输出真值表 & B F C 图 3 电路接线图 3. 设计一个“四路表决器”逻辑电路并测试 设计一个四变量的多路表决器。当输入变量A 、B 、C 、D 有三个或三个以上为1时,输出F 为1;否则输出F 为0。 (1)根据设计要求列出表3四人表决器真值表。 (2)用卡诺图化简逻辑函数,写出逻辑 表达,F= D C B D C A D B A C B A ??+??+??+??. (3)用74LS20与非门实现“四人表决器”,画出实验电路,标出接线脚并测试,验证所列真值表。 输 入 输 出 A B F 0 0 0 0 1 1 1 0 1 1 1 0 输 入 输 出 A b CF 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1 & & & & && & & & A B F