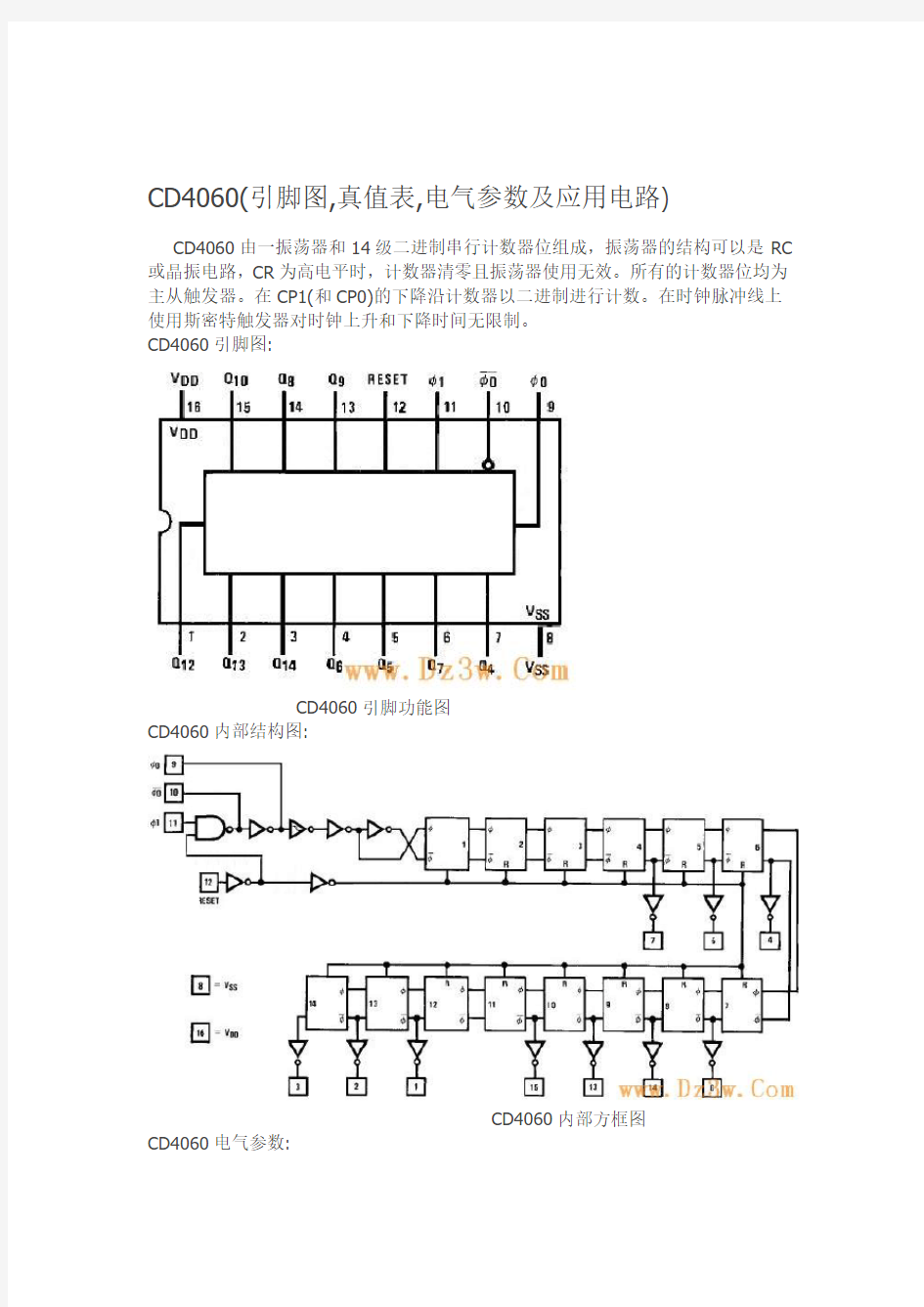

CD4060(引脚图,真值表,电气参数及应用电路) CD4060由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC

或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。所有的计数器位均为主从触发器。在CP1(和CP0)的下降沿计数器以二进制进行计数。在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间无限制。

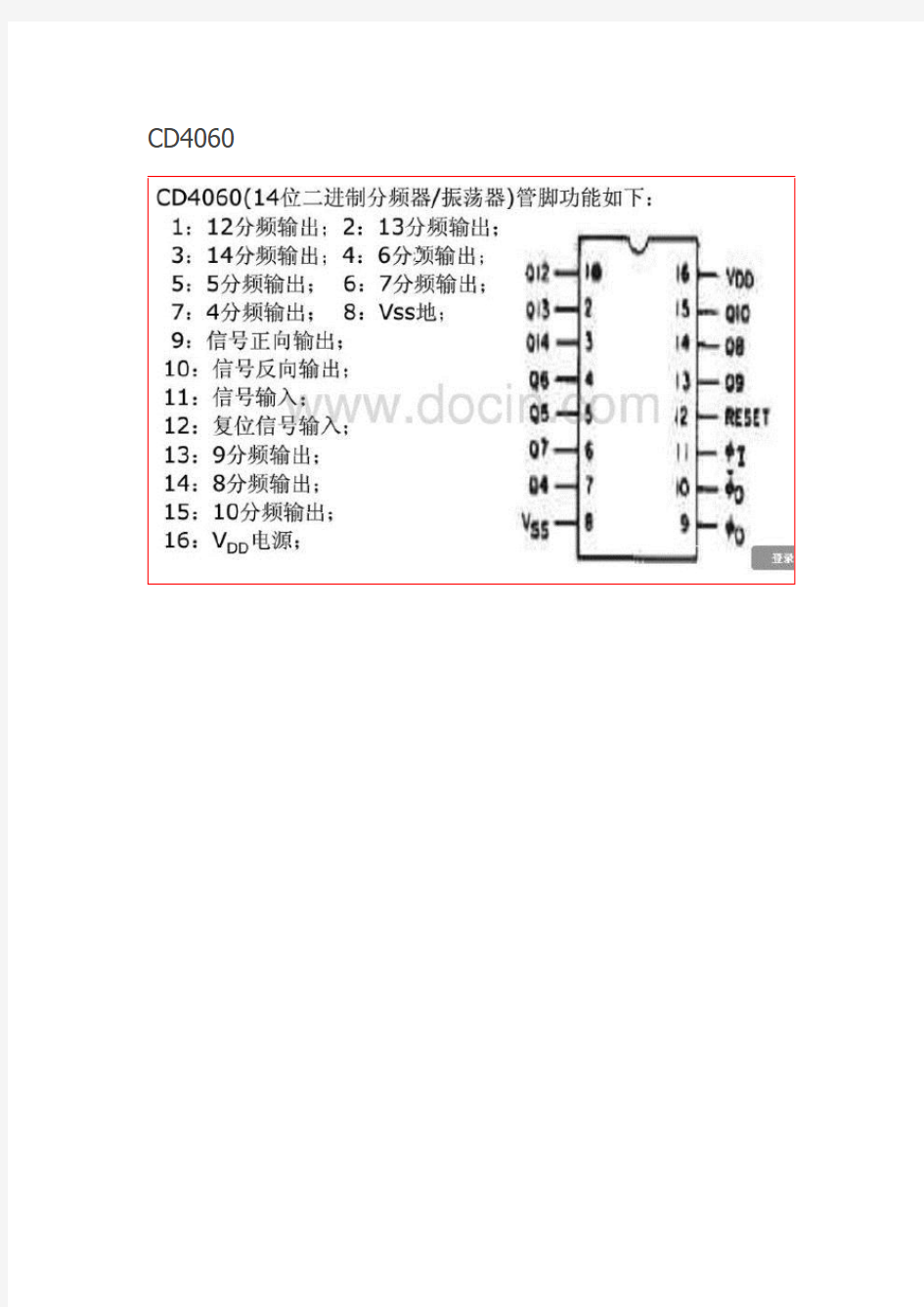

CD4060引脚图:

CD4060引脚功能图

CD4060内部结构图:

CD4060内部方框图

CD4060电气参数:

Recommended Operating Conditions 建议操作条件:

CD4060典型应用电路

CD4060B典型振荡器连接:

上图-RC振荡器下图-晶体振荡器

CD4060秒脉冲发生器电路:

图2 CD4060秒脉冲发生器

脉冲发生器是数字钟的核心部分,它的精度和稳定度决定了数字钟的质量,通常用晶体振荡器发出的脉冲经过整形、分频获得1Hz的秒脉冲。如晶振为32768 Hz,通过15次二分频后可获得1Hz的脉冲输出,电路图如图2所示。

CD4060定时电路

由CD4060和CD4027构成的50Hz振荡器电路本振荡器能产生交变的50Hz脉冲方波,其占空比为50%.可供某些反相器电路应用。

该方波发生器由14级计数、振荡器(CD4060)。双J-K触发器(CD4027);运算放大器(LM324)和少量的分立元件等组成。

电路的振荡由CD4060(IC1)外加晶振3.2768MHz完成,用电阻R1限制振荡回路功耗,R2是偏置电阻。为了启动和维持电路的振荡,用电阻R1提供必需的最小值跨导。

振荡的频率经"14"级分频,得到200Hz,再由CD4060的第③脚输出。200tHz频率又由双J-K触发器进一步"4分频,获得50Hz信号。该50Hz由CDD4027的15出,同时在14脚还产生与15脚的互补(相位差180.)频率信号。频率的占空比仍是50%.

50Hz的方波由运算放大器LM324的A1、A2进行缓冲处理,在其①脚和⑦脚获得相位相反的方波输出,可供一些反相器电路应用。

电源管理芯片引脚定义 1、VCC 电源管理芯片供电 2、VDD 门驱动器供电电压输入或初级控制信号供电源 3、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。 4.RUN SD SHDN EN 不同芯片的开始工作引脚。 5、PGOOD PG cpu内核供电电路正常工作信号输出。 6、VTTGOOD cpu外核供电正常信号输出。 7、UGATE 高端场管的控制信号。 8、LGATE 低端场管的控制信号。 9、PHASE 相电压引脚连接过压保护端。 10、VSEN 电压检测引脚。 11、FB 电流反馈输入即检测电流输出的大小。 12、COMP 电流补偿控制引脚。 13、DRIVE cpu外核场管驱动信号输出。 14、OCSET 12v供电电路过流保护输入端。 15、BOOT 次级驱动信号器过流保护输入端。

16、VIN cpu外核供电转换电路供电来源芯片连接引脚。 17、VOUT cpu外核供电电路输出端与芯片连接。 18、SS 芯片启动延时控制端,一般接电容。 19、AGND GND PGND 模拟地,地线,电源地 20、FAULT 过耗指示器输出,为其损耗功率:如温度超过135度时高电平转到低电平指示该芯片过耗。 21、SET 调整电流限制输入。 22、SKIP 静音控制,接地为低噪声。 23、TON 计时选择控制输入。 24、REF 基准电压输出。 25、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC丧失过压保护功能。 26、FBS 电压输出远端反馈感应输入。 27、STEER 逻辑控制第二反馈输入。 28、TIME/ON 5 双重用途时电容和开或关控制输入 29、RESET 复位输出V1-0v跳变,低电平时复位。 30、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时5v输出在之前。 SEQ接REF上,5v各自独立。SEQ接v1上时输出在5v之前。

电源驱动芯片uc3842引脚图及引脚功能 电流型脉宽调制器UC3842 的主要优点:单端输出,可直接驱动双极型功率管或场效应管;管脚数量少,外围电路简单;电压调整率可达0.01%;工作频率更可高达500 kHz;启动电流小于 1 mA,正常工作电流为12 mA;欠压锁定,带滞后;锁存脉宽调制,可逐周限流;并可利用高频变压器实现与电网隔离。它适用于无工频变压器的低于250w的小功率开关电源,其工作温度为0~+70℃,最高输入电压为36 V,具有最大电流为1 A的拉、灌输出电流。 UC3842外形图 UC3842引脚图和内部电路方框图

UC3842各引脚功能简介如下: ---1脚COMP是内部误差放大器的输出端,通常此脚与2脚之间接有反馈网络,以确定误差放大器的增益和频响。 ---2脚FEED BACK是反馈电压输入端,此脚与内部误差放大器同向输入端的基准电压(一般为+ 2.5V)进行比较,产生控制电压,控制脉冲的宽度。 ---3 脚ISENSE是电流传感端。在外围电路中,在功率开关管(如VMos管)的源极串接一个小阻值的取样电阻,将脉冲变压器的电流转换成电压,此电压送入3 脚,控制脉宽。此外,当电源电压异常时,功率开关管的电流增大,当取样电阻上的电压超过1V时,UC3842就停止输出,有效地保护了功率开关管。 ---4脚RT/CT是定时端。锯齿波振荡器外接定时电容C和定时电阻R的公共端。 ---5脚GND是接地。 ---6脚OUT是输出端,此脚为图滕柱式输出,驱动能力是±lA。这种图腾柱结构对被驱动的功率管的关断有利,因为当三极管VTl截止时,VT2导通,为功率管关断时提供了低阻抗的反向抽取电流回路,加速功率管的关断。 ---7脚Vcc是电源。当供电电压低于+16V时,UC3824不工作,此时耗电在1mA以下。输入电压可以通过一个大阻值电阻从高压降压获得。芯片工作后,输入电压可在+10~+30V之间波

电源管理芯片引脚定义 1 VCC 电源管理芯片供电 2 VDD 门驱动器供电电压输入或初级控制信号供电源 3 VID0- 4 CPU与cpu供电管理芯片VID信号连接引脚,主要指示芯片的输出信号, 使两个场管输出正确的工作电压。 4 RUN SD SHDN EN 不同芯片的开始工作引脚 5 PGOOD PG cpu内核供电电路正常工作信号输出 6 VTTGOOD cpu外核供电正常信号输出 7 UGATE 高端场管的控制信号 8 LGATE 低端场管的控制信号 9 PHASE 相电压引脚连接过压保护端 10 VSEN 电压检测引脚 11 FB 电流反馈输入即检测电流输出的大小 12 COMP 电流补偿控制引脚 13 DRIVE cpu 外核场管驱动信号输出 14 OCSET 12v供电电路过流保护输入端 15 BOOT 次级驱动信号器过流保护输入端 16 VIN cpu外核供电转换电路供电来源芯片连接引脚 17 VOUT cpu外核供电电路输出端与芯片连接 18 SS 芯片启动延时控制端,一般接电容 19 AGND GND PGND 模拟地地电源地 20 FAULT 过耗指示器输出,为其损耗功率:如温度超过135.c时由高电平转到低电平指示该芯片过耗. 21 SET 调整电流限制输入 22 SKIP 静音控制,接地为低噪声 23 TON 计时选择控制输入 24 REF 基准电压输出 25 OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连vcc丧失过压保护功能。 26 FBS 电压输出远端反馈感应输入 27 STEER 逻辑控制第二反馈输入 28 TIME/ON 5 双重用途定时电容和开或关控制输入 29 RESET 复位输出vl-0v跳变,低电平时复位 30 SEQ 选择pwm电源电平转换器的次序 SEQ接地时5v输出在3.3v之前 SEQ 接REF上,3.3v 5v 各自独立 SEQ 接vl上时 3.3v输出在5v之前 31 RT 定时电阻 32 CT 定时电容 33 ILIM 电流限制门限调整 34 SYNC 振荡器同步和频率选择,150khz操作时,sync连接到gnd 300khz时 连接到ref上,用0-5v驱使sync 使频率在340-195khz

电源芯片引脚定义 Document serial number【UU89WT-UU98YT-UU8CB-UUUT-UUT108】

电源管理芯片引脚定义 1、VCC 电源管理芯片供电 2、VDD 门驱动器供电电压输入或初级控制信号供电源 3、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。 4.RUN SD SHDN EN 不同芯片的开始工作引脚。 5、PGOOD PG cpu内核供电电路正常工作信号输出。 6、VTTGOOD cpu外核供电正常信号输出。 7、UGATE 高端场管的控制信号。 8、LGATE 低端场管的控制信号。 9、PHASE 相电压引脚连接过压保护端。 10、VSEN 电压检测引脚。 11、FB 电流反馈输入即检测电流输出的大小。 12、COMP 电流补偿控制引脚。 13、DRIVE cpu外核场管驱动信号输出。 14、OCSET 12v供电电路过流保护输入端。 15、BOOT 次级驱动信号器过流保护输入端。 16、VIN cpu外核供电转换电路供电来源芯片连接引脚。 17、VOUT cpu外核供电电路输出端与芯片连接。 18、SS 芯片启动延时控制端,一般接电容。 19、AGND GND PGND 模拟地,地线,电源地

20、FAULT 过耗指示器输出,为其损耗功率:如温度超过135度时高电平转到低电平指示该芯片过耗。 21、SET 调整电流限制输入。 22、SKIP 静音控制,接地为低噪声。 23、TON 计时选择控制输入。 24、REF 基准电压输出。 25、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC丧失过压保护功能。 26、FBS 电压输出远端反馈感应输入。 27、STEER 逻辑控制第二反馈输入。 28、TIME/ON 5 双重用途时电容和开或关控制输入 29、RESET 复位输出V1-0v跳变,低电平时复位。 30、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时5v输出在之前。 SEQ接REF上, 5v各自独立。SEQ接v1上时输出在5v之前。 31、RT 定时电阻。 32、CT 定时电容。 33、ILIM 电流限制门限调整。 34、SYNC 振荡器同步和频率选择,150Khz操作时,sync连接到GND, 300Khz时连接到RE上,用0-5v驱使sync 使频率在340-195Khz. 35、VIN 电压输入 36、VREFEN 参考电压 37、VOUT 电压输出

常用芯片引脚图 一、单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O接口 无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时 传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O接口,第二功能作为为单片机的控 制信号。 ALE/ PROG:地址锁存允许/编程脉冲输入信号线(输出信号) PSEN:片外程序存储器开发信号引脚(输出信号) EA/Vpp:片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD:复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc:主电源引脚(+5V) Vss:数字电路地引脚(0V) Vpd:内部RAM备用电源引脚(+5V) V REF:A/D转换器基准电源引脚(+5V) AGND:A/D转换器参考地引脚P1.0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 RST RXD/P3.0 TXD/P3.1 INT0/P3.2 INT1/P3.3 T0/P3.4 T1/P3.5 WR/P3.6 RD/P3.7 XTAL2 XTAL1 V SS

1、VCC 电源管理芯片供电 2、VDD 门驱动器供电电压输入或初级控制信号供电源 3、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。 4.RUN SD SHDN EN 不同芯片的开始工作引脚。 5、PGOOD PG cpu内核供电电路正常工作信号输出。 6、VTTGOOD cpu外核供电正常信号输出。 7、UGATE 高端场管的控制信号。 8、LGATE 低端场管的控制信号。 9、PHASE 相电压引脚连接过压保护端。 10、VSEN 电压检测引脚。 11、FB 电流反馈输入即检测电流输出的大小。 12、COMP 电流补偿控制引脚。 13、DRIVE cpu外核场管驱动信号输出。 14、OCSET 12v供电电路过流保护输入端。 15、BOOT 次级驱动信号器过流保护输入端。 16、VIN cpu外核供电转换电路供电来源芯片连接引脚。 17、VOUT cpu外核供电电路输出端与芯片连接。 18、SS 芯片启动延时控制端,一般接电容。 19、AGND GND PGND 模拟地,地线,电源地 20、FAULT 过耗指示器输出,为其损耗功率:如温度超过135度时高电平转到低电平指示该芯片过耗。 21、SET 调整电流限制输入。

22、SKIP 静音控制,接地为低噪声。 23、TON 计时选择控制输入。 24、REF 基准电压输出。 25、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC丧失过压保护功能。 26、FBS 电压输出远端反馈感应输入。 27、STEER 逻辑控制第二反馈输入。 28、TIME/ON 5 双重用途时电容和开或关控制输入 29、RESET 复位输出V1-0v跳变,低电平时复位。 30、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时5v输出在之前。 SEQ接REF上, 5v各自独立。SEQ接v1上时输出在5v之前。 31、RT 定时电阻。 32、CT 定时电容。 33、ILIM 电流限制门限调整。 34、SYNC 振荡器同步和频率选择,150Khz操作时,sync连接到GND, 300Khz时连接到RE 上,用0-5v驱使sync 使频率在340-195Khz. 35、VIN 电压输入 36、VREFEN 参考电压 37、VOUT 电压输出 38、VCNTL 供电

4953芯片脚位定义(2008-04-20 20:32:16) 标签:ic4953脚位定义led资料it分类:电子电路知识APM4953K CEM4953A

GSS4953BDY SI4953ADY SPP4953A

LED上所用的4953管脚定义都是相同的,只是生产厂商不一样 LED电子显示屏的维修资料(芯片) 来源:LED电子屏发布时间:2009-08-27 查看次数:5535 LED电子显示屏的维修资料(芯片)

一、LED电子显示屏的维修芯片资料 74HC04的作用:6位反相器。 第7脚GND,电源地。第14脚VCC,电源正极。信号由A端输入Y端反相输出,A1 与Y1为一组,其它类推。例:A1=“1”则Y1=“0”、A1=“0”则Y1=“1”,其它组功能一样。74HC138的作用:八位二进制译十进制译码器。 第8脚GND,电源地。第15脚VCC,电源正极第1~3脚A、B、C,二进制输入脚。第4~6脚片选信号控制,只有在4、5脚为“0”6脚为“1”时,才会被选通,输出受A、B、C信号控制。其它任何组合方式将不被选通,且Y0~Y7输出全为“1”。 通过控制选通脚来级联,使之扩展到十六位。 例:G2A=0,G2B=0,G1=1,A=1,B=0,C=0,则Y0为“0”Y1~Y7为“1”。 74HC595的作用:LED驱动芯片,8位移位锁存器。 第8脚GND,电源地。第16脚VCC,电源正极第14脚DATA,串行数据输入口,显示数据由此进入,必须有时钟信号的配合才能移入。第13脚EN,使能口,当该引脚上为“1”时QA~QH口全部为“1”,为“0”时QA~QH的输出由输入的数据控制。第12脚STB,锁存口,当输入的数据在传入寄存器后,只有供给一个锁存信号才能将移入的数据送QA~QH口输出。第11脚CLK,时钟口,每一个时钟信号将移入一位数据到寄存器。第10脚SCLR,复位口,只要有复位信号,寄存器内移入的数据将清空,显示屏不用该脚,一般接VCC。第9脚DOUT,串行数据输出端,将数据传到下一个。第15、1~7脚,并行输出口也就是驱动输出口,驱动LED。 4953的作用:行驱动管,功率管。 其内部是两个CMOS管,1、3脚VCC,2、4脚控制脚,2脚控制7、8脚的输出,4脚控制5、6脚的输出,只有当2、4脚为“0”时,7、8、5、6才会输出,否则输出为高阻状态。TB62726的作用:LED驱动芯片,16位移位锁存器。 第1脚GND,电源地。第24脚VCC,电源正极第2脚DATA,串行数据输入 第3脚CLK,时钟输入.第4脚STB,锁存输入.第23脚输出电流调整端,接电阻调整 第22脚DOUT,串行数据输出第21脚EN,使能输入

CD4017引脚图: CD4017 是5 位Johnson 计数器,具有10 个译码输出端,14(CL)、15(CR)、13(INH 或EN)输入端。时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。INH 为低电平时,计数器在时钟上升沿计数;反之,计数功能无效。CR 为高电平时,计数器清零。Johnson 计数器,提供了快速操作、2 输入译码选通和无毛刺译码输出。防锁选通,保证了正确的计数顺序。译码输出一般为低电平,只有在对应时钟周期内保持高电平。在每10 个时钟输入周期CO 信号完成一次进位,并用作多级计数链的下级脉动时钟。 引出端功能符号:CO(12):进位脉冲输渊;CL:时钟输入端;(RESEST)CR:清除端;INH(EN):禁止端;Q0-Q9 计数脉冲输出端;VDD:正电源;VSS:地。 CD40110的引脚:

Ya~Yg:七段码,高电平有效; CPD(CP-):第七脚,减一、脉冲上升沿有效; CPU(CP+):第九脚,加一、脉冲上升沿有效; LE:第六脚,高电平有效,锁存数据; CT(TE):第四脚,高电平有效,禁止计数; CR(R):第五脚,高电平有效,清除计数显示。 数字式频率计 LM317:输出电压连续可调的集成稳压电源,输出电压在1.25-37V之间连续可调,输出最大电流可达1.5A。

工作原理: 电路原理图见图1。LM317输出电流为1.5A,输出电压可在1.25-37V之间连续调节,其输出电压由两只外接电阻R1、RP1决定,输出端和调整端之间的电压差为1.25V,这个电压将产生几毫安的电流,经R1、RP1到地,在RP1上分得的电压加到调整端,通过改变RP1就能改变输出电压。注意,为了得到稳定的输出电压,流经R1的电流小于3.5mA。LM317在不加散热器时最大功耗为2W,加上 200×200×4mm3散热板时其最大功耗可达15W。VD1为保护二极管,防止稳压器输出端短路而损坏IC,VD2用于防止输入短路而损坏集成电路。 (a)图是红外发射电路.NE555电路产生40kHz的脉冲经过VT放大后由红外发射管SE303向外发射. 红外遥控延时灯开关电路:该电路由红外接收器,单稳态延时电路和可控硅组成。

标签:ic4953脚位定义led资 分类:电子电路知识料it APM4953K CEM4953A GSS4953BDY SI4953ADY SPP4953A LED上所用的4953管脚定义都是相同的,只是生产厂商不一样 LED电子显示屏的维修资料(芯片)

来源:LED电子屏发布时间:2009-08-27 查看次数:5535 LED电子显示屏的维修资料(芯片) 一、 LED电子显示屏的维修芯片资料 74HC04的作用:6位反相器。 第7脚GND,电源地。第14脚VCC,电源正极。信号由A端输入Y端反相输出,A1与Y1为一组,其它类推。例:A1=“1”则Y1=“0”、A1=“0”则Y1=“1”,其它组功能一样。74HC138的作用:八位二进制译十进制译码器。 第8脚GND,电源地。第15脚VCC,电源正极第1~3脚A、B、C,二进制输入脚。第4~6脚片选信号控制,只有在4、5脚为“0”6脚为“1”时,才会被选通,输出受A、B、C信号控制。其它任何组合方式将不被选通,且Y0~Y7输出全为“1”。 通过控制选通脚来级联,使之扩展到十六位。 例:G2A=0,G2B=0,G1=1,A=1,B=0,C=0,则Y0为“0”Y1~Y7为“1”。 74HC595的作用:LED驱动芯片,8位移位锁存器。 第8脚GND,电源地。第16脚VCC,电源正极第14脚DATA,串行数据输入口,显示数据由此进入,必须有时钟信号的配合才能移入。第13脚EN,使能口,当该引脚上为“1”时QA~QH口全部为“1”,为“0”时QA~QH的输出由输入的数据控制。第12脚STB,锁存口,当输入的数据在传入寄存器后,只有供给一个锁存信号才能将移入的数据送QA~QH口输出。第11脚CLK,时钟口,每一个时钟信号将移入一位数据到寄存器。第10脚SCLR,复位口,只要有复位信号,寄存器内移入的数据将清空,显示屏不用该脚,一般接VCC。第9脚DO UT,串行数据输出端,将数据传到下一个。第15、1~7脚,并行输出口也就是驱动输出口,驱动LED。 4953的作用:行驱动管,功率管。 其内部是两个CMOS管,1、3脚VCC,2、4脚控制脚,2脚控制7、8脚的输出,4脚控制5、6脚的输出,只有当2、4脚为“0”时,7、8、5、6才会输出,否则输出为高阻状态。TB 62726的作用:LED驱动芯片,16位移位锁存器。

DSP第二次大作业 一、详细描述F240,F2812芯片引脚的符号与功能。 1、TMS320F240芯片引脚与功能 TMS320F240为TI公司所出品的定点式数字信号处理器芯片,具有强大的外围(64k I/O space、10 bit A/D Converter、Digital I/O peripheral) ,芯片内部采用了加强型哈佛架构(Enhanced Harvard Architecture),由三个平行处理的总线─程序地址总线(PAB)、数据读出地址总线(DRAB)及数据写入地址总线(DWAB),使其能进入多个内存空间。由于总线之操作各自独立,因此可同时进入程序及数据存储器空间,而两内存间的数据亦可互相交换,使得其具有快速的运算速度,几乎所有的指令皆可在50ns 周期时间内执行完毕,内部的程控以管线式的方式操作(Pipeline operation),且使用内存映像的方式,使其整体的效能可达到20MIPS,因此非常适用于实时运转控制,而对于速度较慢的外围亦提供了wait-states 的功能。

其引脚及功能如下所示:

2、TMS320F2812芯片引脚与功能 德州仪器所生产的TMS320F2812 数字讯号处理器是针对数字控制所设计的DSP,整合了DSP 及微控制器的最佳特性,主要使用在嵌入式控制应用,如数字电机控制(digital motor control, DMC)、资料撷取及I/O 控制(data acquisition and control, DAQ)等领域。针对应用最佳化,并有效缩短产品开发周期,F28x 核心支持全新CCS环境的C compiler,提供C 语言中直接嵌入汇编语言的程序开发介面,可在C语言的环境中搭配汇编语言来撰写程序。值得一提的是,F28xDSP 核心支持特殊的IQ-math 函式库,系统开发人员可以使用便宜的定点数DSP 来发展所需的浮点运算算法。F28x 系列DSP预计发展至400MHz,目前已发展至150MHz的Flash型式。

电源芯片引脚定义 Company Document number:WUUT-WUUY-WBBGB-BWYTT-1982GT

电源管理芯片引脚定义 1、VCC 电源管理芯片供电 2、VDD 门驱动器供电电压输入或初级控制信号供电源 3、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。 4.RUN SD SHDN EN 不同芯片的开始工作引脚。 5、PGOOD PG cpu内核供电电路正常工作信号输出。 6、VTTGOOD cpu外核供电正常信号输出。 7、UGATE 高端场管的控制信号。 8、LGATE 低端场管的控制信号。 9、PHASE 相电压引脚连接过压保护端。 10、VSEN 电压检测引脚。 11、FB 电流反馈输入即检测电流输出的大小。 12、COMP 电流补偿控制引脚。 13、DRIVE cpu外核场管驱动信号输出。 14、OCSET 12v供电电路过流保护输入端。 15、BOOT 次级驱动信号器过流保护输入端。 16、VIN cpu外核供电转换电路供电来源芯片连接引脚。 17、VOUT cpu外核供电电路输出端与芯片连接。 18、SS 芯片启动延时控制端,一般接电容。 19、AGND GND PGND 模拟地,地线,电源地

20、FAULT 过耗指示器输出,为其损耗功率:如温度超过135度时高电平转到低电平指示该芯片过耗。 21、SET 调整电流限制输入。 22、SKIP 静音控制,接地为低噪声。 23、TON 计时选择控制输入。 24、REF 基准电压输出。 25、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC丧失过压保护功能。 26、FBS 电压输出远端反馈感应输入。 27、STEER 逻辑控制第二反馈输入。 28、TIME/ON 5 双重用途时电容和开或关控制输入 29、RESET 复位输出V1-0v跳变,低电平时复位。 30、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时5v输出在之前。 SEQ接REF上, 5v各自独立。SEQ接v1上时输出在5v之前。 31、RT 定时电阻。 32、CT 定时电容。 33、ILIM 电流限制门限调整。 34、SYNC 振荡器同步和频率选择,150Khz操作时,sync连接到GND, 300Khz时连接到RE上,用0-5v驱使sync 使频率在340-195Khz. 35、VIN 电压输入 36、VREFEN 参考电压 37、VOUT 电压输出

电源管理芯片引脚定义 1、 VCC 电源管理芯片供电 2、 VDD 门驱动器供电电压输入或初级控制信号供电源 3、VID-4 CPU 与 CPU 供电管理芯片 VID 信号连接引脚,主要指示芯片的输出信号,使两 个场管输出正确的工作电压。 4.RUN SD SHDN EN 不同芯片的开始工作引脚。 5、PGOOD PG cpu 内核供电电路正常工作信号输出。 6、VTTGOOD cpu 外核供电正常信号输出。 7、 UGATE 高端场管的控制信号。 8、 LGATE 低端场管的控制信号。 9、 PHASE 相电压引脚连接过压保护端。

10、VSEN 电压检测引脚。 11、FB 电流反馈输入即检测电流输出的大小。 12、COMP 电流补偿控制引脚。 13、 DRIVE cpu 外核场管驱动信号输出。 14、 OCSET 12v 供电电路过流保护输入端。 15、BOOT 次级驱动信号器过流保护输入端。 16、 VIN cpu 外核供电转换电路供电来源芯片连接引脚。 17、 VOUT cpu 外核供电电路输出端与芯片连接。 18、SS 芯片启动延时控制端,一般接电容。 19、 AGND GND PGND 模拟地,地线,电源地 20、FAULT 过耗指示器输出,为其损耗功率:如温度超过 135 度时高电平转到低 电平指示该芯片过耗。 21、SET 调整电流限制输入。

22、SKIP 静音控制,接地为低噪声。 23、TON 计时选择控制输入。 24、REF 基准电压输出。 25、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC 丧失过压 保护功能。 26、FBS 电压输出远端反馈感应输入。 27、STEER 逻辑控制第二反馈输入。 28、 TIME/ON 5 双重用途时电容和开或关控制输入 29、RESET 复位输出 V1-0v 跳变,低电平时复位。 30、SEQ 选择 PWM 电源电平轮换器的次序: SEQ 接地时 5v 输出在 3.3v 之前。 SEQ 接 REF 上, 3.3v 5v 各自独立。 SEQ 接 v1 上时 3.3v 输出在 5v 之前。31、RT 定时电阻。 32、CT 定时电容。

ISL6251AHRZ (笔记本)电池充放电管理芯片引脚定义 21,22脚CSOP/CSON:是电池的充电电流感应正/负输入。在CSOP的差动电压和CSON是用于检测电池的充电电流,并与充电电流限制门限调节充电电流。该CSON管脚也可以用作电池的反馈电压来执行电压调节。 19,20脚CSIP/CSIN: 是AC适配器电流传感正/负输入。CSIP的两端的差分电压和CSIN是用于检测AC适配器电流,并与AC适配器电流限制相比,调节AC适配器电流。 24脚DCIN: 是内部5V LDO输入。它连接到AC适配器的输出。连接DCIN一个0.1μF的陶瓷电容。 2脚ACSET:是一个AC适配器检测输入。连接到从适配器输入电阻分压器。 23脚CACPRN:是AC适配器开漏输出。ACPRN是低电平时ACSET比通常1.26V较高,高电平时ACSET比一般1.26V低。 3脚EN:是充电使输入。连接中文高使充电控制功能,连接中文的充电功能低禁用。使用的热敏电阻来检测并暂停热电池充电。 7脚ICM:是适配器的电流输出。该引脚输出产生的电压成正比适配器的电流。 13脚PGND:是电源地。连接PGND到的低侧MOSFET栅极驱动器低电压端MOSFET源。 1脚VDD:是一个内部LDO输出电源IC的模拟电路。连接一个1μF陶瓷电容接地。 15脚VDDP:是低端MOSFET栅极驱动器电源电压。4.7Ω电阻连接到VDD和1μF陶瓷电容,电源地。 5脚ICOMP:是一个电流环误差放大器输出。 6脚VCOMP:是一个循环放大器的输出电压。 4脚CELLS:这个引脚用于选择电池电压。细胞=内径为4型电池组,电池=接地为3S号电池,电池=浮法为2秒电池组。 11脚V ADJ:调整电池的稳压电压。V ADJ =参考电压为4.2V的5%; V ADJ =为4.2V/cell浮动; V ADJ =接地为4.2V的5%。连接到电阻分压器进行编程至4.2V之间,5%和5%的预期4.2V的电池电压。 9脚CHLIM:是电池的充电电流限制设定引脚。CHLIM输入电压范围为0.1V至3.6V之间。当CHLIM =,对南方东英设定点3.3 - CSON 为165mV。该充电器关闭如果CHLIM低于88mV强迫。 10脚ACLIM:是适配器的电流极限设定引脚。ACLIM =参考电压为100mV时,ACLIM =浮动的仅为75mV @,为50mV的ACLIM =接地。连接一个电阻分压器进行编程与50mV和100mV适配器电流限制门槛。 8脚VREF:参考电压是2.39V基准输出引脚。这是内部补偿。不要连接去耦电容。 16脚BOOT:连接启动到一个0.1μF的陶瓷电容相引脚和连接到自举肖特基二极管的负极。 17脚UGA TE:是高侧MOSFET栅极驱动输出。 14脚LGA TE:是低侧MOSFET栅极驱动输出;摆动0V和VDDP之间。 18脚PHASE:第一阶段的连接引脚连接到高侧MOSFET源,输出电感和低侧MOSFET的漏极。

电源管理芯片引脚定义 1、AGND GND PGND 模拟地地线电源地 2、BOOT 次级驱动信号器过流保护输入端。 3、COMP 电流补偿控制引脚。 4、CT 定时电容。 5、DRIVE cpu外核场管驱动信号输出。 6、FAULT 过耗指示器输出,为其损耗功率:如温度超过135度时高电平转到低电平指示该芯片过耗。 7、FB 电流反馈输入即检测电流输出的大小。 8、FBS 电压输出远端反馈感应输入。 9、ILIM 电流限制门限调整。 10、LGATE 低端场管的控制信号。 11、OCSET 12v供电电路过流保护输入端。 12、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC 丧失过压保护功能。 13、PGOOD PG cpu内核供电电路正常工作信号输出。 14、PHASE 相电压引脚连接过压保护端。 15、REF 基准电压输出。 16、RESET 复位输出V1-0v跳变,低电平时复位。 17、RT 定时电阻。 18、RUN SD SHDN EN 不同芯片的开始工作引脚。 19、SET 调整电流限制输入。 20、SS 芯片启动延时控制端,一般接电容。 21、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时 5v输出在3.3v之前。 SEQ 接REF22、SKIP 静音控制,接地为低噪声。 22、STEER 逻辑控制第二反馈输入。 上,3.3v 5v各自独立。SEQ接v1上时 3.3v输出在5v之前。 23、SYNC 振荡器同步和频率选择,150Khz操作时,sync连接到GND, 300Khz 时连接到REF上,用0-5v驱使sync 使频率在340-195Khz. 24、TIME/ON 5 双重用途时电容和开或关控制输入 25、TON 计时选择控制输入。 26、UGATE 高端场管的控制信号。 27、VCC 电源管理芯片供电 28、VCNTL 供电 29、VDD 门驱动器供电电压输入或初级控制信号供电源 30、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。 31、VIN 电压输入 32、VIN cpu外核供电转换电路供电来源芯片连接引脚。 33、VOUT 电压输出 34、VOUT cpu外核供电电路输出端与芯片连接。 35、VREFEN 参考电压 36、VSEN 电压检测引脚。

555芯片引脚图及引脚描述 555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。 1脚为地。2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。 当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平; 2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。 4脚是复位端,当4脚电位小于0.4V时,不管2、6脚状态如何,输出端3脚都输出低电平。 5脚是控制端。 7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。 555集成电路管脚,工作原理,特点及典型应用电路介绍. 1555集成电路的框图及工作原理 555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体,如图1所示。 2.555芯片管脚介绍 555集成电路是8脚封装,双列直插型,如图2(A)所示,按输入输出的排列可看成如图2(B)所示。其中6脚称阈值端(TH),是上比较器的输入;2脚称触发端(TR),是下比较器的输入;3脚是输出端(Vo),它有O和1两种状态,由输入端所加的电平决定;7脚是放电端(DIS),它是内部放电管的输出,有悬空和接地两种状态,也是由输入端的状态决定;4脚是复位端(MR),加上低电平时可使输出为低电平;5脚是控制电压端(Vc),可用它改变上下触发电平值;8脚是电源端,1脚是地端。图2555集成电路封装图 我们也可以把555电路等效成一个带放电开关的R-S触发器,如图3(A)所示,这个特殊的触发器有两个输入端:阈值端(TH)可看成是置零端R,要求高电平,触发端(TR)可看成是置位端S,要求低电平,有一个输出端Vo,Vo可等效成触发器的Q端,放电端(DIS)可看成是由内部放电开关控制的一个接点,由触发器的Q端控制:Q=1时DIS端接地,Q=0时DIS端悬空。另外还有复位端MR,控制电压端Vc,电源端VDD和

常用IC芯片管脚的定义中引文翻译 1、VOL—Voltage Output Low 低电平输出电压;VIH(Voltage Input High)高 电平输入电压。 2、CLKO(Clock Output) 时钟输出;Vss 数字地。DP:USB端D+信号。 3、VDD—数字电源;Vssp:I/O驱动缓冲数字地。 DM:USB端D-信号。 4、CE:Chip enable input 片使能输出;OE:Output enable input 输出使能输 入。 5、WP:Write protect 写入保护;FWR:Flash write enable input闪存写入 使能信号。 6、VA: analog power 模拟电源输入;LVDS:Low voltage differential signal 低电平微分信号。 7、FB:Output voltage feedback 输出电压返回输入;SW:Power switch input 电源开关输入。 8、SHON:Shutdown control input 关闭信号输入;COMP:comp voltage. 9、TS:Temperature-sense input温度感应信号输入RC:Timer-program input 定时程序信号输入 10. SNS:Current-sense input 电流感应信号输入;CE:使能信号(enable signal). 11 .WE:写入启动信号;RST: reset 复位信号;CLK:时钟控制信号;CKE:时钟控制信号。 12. Vcc:电源信号;CS:片选信号;SCLK:串行时钟输入;RF: 信号输出;FCOM:公共信号端。 :晶振信号输出;XTALI:晶振信号输入。OPOLS:VCOM 信号输出。 :ASCO 时钟、数据输出;RXD:ASCO 数据输入或输出。 :同步脉冲输入; RCT: 振荡器时间常数电路;DC: 占空比控制。 :5V基准电压;VFB: 误差放大器倒相输入;COMP:误差放大器输出。

电源芯片 调压器、DC-DC电路和电源监视器引脚及主要特性 7800系列三端稳压器(正输出) 输出电压固定的三端系列稳压器;输出电压有5V、6V、7V、8V、9V、10V、12V、15V、18V、20V、24V输出电流1A;5~18V输出的最大电压为35V、20V、24V输出的电大输入电压为40V;7800工作温度为-55~+150℃,7800C的为0~+125℃;内含过流限制和安全工作保护电路。类似型号:μA7800、LM7800、MC7800、HA7800、μPC7800M、NJM7800、TA7800AP、AN7800、CW7800。 78HGA5A可调稳压器(正输出) 输出电压可调的四端正输出稳压器;输出电压范围5~24V;输出电流5A;功耗50W;内含输出短路电流限制、热过载和安全工作区保护电路。 78L00AC、78L00C系列三端稳压器(正输出) 输出电压固定;输出电压误差有±4%(78L00AC)、±4%(78L00C);输出电流1~100mA;5V输出的最大输入电压为30V;12V、15V输出的最大输入电压为35V;24V输出的最输入电压为40V;内含过流限制、过热切断功能。类似型号:μA78L00AWC、MC78L00C、 MC78L00AC、LM78L00AC、LM78L00C、μPC78L00J、TA78L00AP、HA78L00P、AN78L00。

78P12稳压器 输出电压固定的三端正输出稳压器;输出电压12V;输出电流10A;功耗70W;内设输出短路电流限制、热过载和安全工作区保护装置。78PGA可调稳压器(正输出) 输出电压可调的四端正输出稳压器;输出电压范围5~24;输出电流10A;功耗70W;内设输出短路电流限制、热过载和安全工作区保护装置。 79N00系列三端稳压器(负输出) 输出电压因定的三端系列稳压器;最大输出电流300mA;79N04~79N18的最大输入电压为-35V;79N04、79N24的最大输入电压为-40V;功耗8W;工作温度-29~+80℃;内含过电流限制、过热和安全工作区限制电路。类似型号AN79N00、μPC79N00H。 AD580基准电压电路(+2.5V) 带宽型三端基准电压电路;输出电压2.5V;AD580M输出电压初期误差±4%;AD580U温度漂移小于10×10^-6/℃;长期稳定性 250μV;输入电压范围4.5~30V;最大输入电压40V;环境温度小于25℃时,功耗350mW。 AD581基准电压电路(+10V) 带宽型三端基准电压电路;输出电压10V;AD581L/581U输出电压初期误差±5mV;0~70℃时AD581L温度漂移5×10^-6/℃,-55~+125℃时AD581U温度漂移10×10^-6/℃, 长期稳定性

MX232 主要作用: MAX232是一种双组驱动器/接收器,片内含有一个电容性电压发生器以便在单5V 电源供电时提供EIA/TIA-232-E电平。 当用单片机和PC机通过串口进行通信,尽管单片机有串行通信的功能,但单片机提供的信号电平和RS232的标准不一样,因此要通过max232这种类似的芯片进行电平转换。 引脚介绍: 第一部分是电荷泵电路。由1、2、3、4、5、6脚和4只电容构成。功能是产生+12v和-12v两个电源,提供给RS-232串口电平的需要。 第二部分是数据转换通道。由7、8、9、10、11、12、13、14脚构成两个数据通道。 其中13脚(R1IN)、12脚(R1OUT)、11脚(T1IN)、14脚(T1OUT)为第一数据通道。 8脚(R2IN)、9脚(R2OUT)、10脚(T2IN)、7脚(T2OUT)为第二数据通道。TTL/CMOS数据从11引脚(T1IN)、10引脚(T2IN)输入转换成RS-232数据从14脚(T1OUT)、7脚(T2OUT)送到电脑DB9插头;DB9插头的RS-232数据从13引脚(R1IN)、8引脚(R2IN)输入转换成TTL/CMOS数据后从12引脚

(R1OUT)、9引脚(R2OUT)输出。 第三部分是供电。15脚GND、16脚VCC(+5v)。 JTAG14 1,13接电源 2,4,6,8,10,14 GND接地 3mode 模式选择 5mosi主输出从输入 7mrst 主复位 9sck 同步时钟 11miso 主出入从输出 Atmegal16

VCC 电源正 GND 电源地 端口A(PA7..PA0) 端口A 做为A/D 转换器的模拟输入端。端口A 为8 位双向I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口A 处于高阻状态。 端口B(PB7..PB0) 端口B 为8 位双向I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口B 处于高阻状态。 端口B 也可以用做其他不同的特殊功能. 端口C(PC7..PC0) 端口C 为8 位双向I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口C 处于高阻状态。如果JTAG接口使能,即使复位出现引脚 PC5(TDI)、 PC3(TMS)与 PC2(TCK)的上拉电阻被激活。端口C 也可以用做其他不同的特殊功能. 端口D(PD7..PD0) 端口D 为8 位双向I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口D 处于高阻状态。端口D 也可以用做其他不同的特殊功能. RESET 复位输入引脚。持续时间超过最小门限时间的低电平将引起系统复位。门限时间见P36Table 15。持续时间小于门限间的脉冲不能保证可靠复位。XTAL1 反向振荡放大器与片内时钟操作电路的输入端。 XTAL2 反向振荡放大器的输出端。 AVCC AVCC是端口A与A/D转换器的电源。不使用ADC时,该引脚应直接与VCC 连接。使用ADC时应通过一个低通滤波器与VCC 连接。 AREF A/D 的模拟基准输入引脚。