VGA图片(动态)显示与乐曲硬件演奏电路设计分析

- 格式:doc

- 大小:404.00 KB

- 文档页数:14

编号:EDA技术实训实训(论文)说明书题目:VGA彩条信号显示控制器设计院(系):信息与通信学院专业:电子信息工程学生姓名:***学号: ********** 指导教师:付强、陈小毛、归发第2013 年1 月4 日本设计采用EDA技术,通过FPGA芯片实现了实现VGA彩条信号的显示的设计,本文采用VHDL 硬件描述语言描述VGA彩条信号的显示电路,完成对电路的功能仿真。

通过按键来实现横彩条、竖彩条、棋盘式方格图案的选择。

显示图像分辨率为640×480,刷新率为60Hz。

与传统的设计方式相比,本设计由于采用了FPGA芯片来实现,它将大量的电路功能集成到一个芯片中,并且可以由用户自行设计逻辑功能,提高了系统的集成度和可靠性。

关键词:电子设计自动化、可编程门阵列、硬件描述语言、状态机This design used the EDA technology, through the FPGA chip realized the realization of the signal that striped VGA is adopted in this paper, the design of the VHDL hardware description language describe VGA striped signal display circuit and the completion of the function of the circuit simulation. By pressing buttons horizontal striped, perpendicular striped, chessboard type pane design choice. Display image resolution for 640 x 480, refresh rate of 60 Hz ac. Compared with the traditional design methods, the design with FPGA chip to achieve, it will be a lot of circuit function integration to a chip, and can be by the user to design logical function, improve the system integrity and reliability.Keywords:Electronic Design Automatic technology,Flied Programmable,Gate Array, Hardware Description Language, State Machine1. 绪论 (1)1.1 EDA技术的发展 (1)1.2 课程设计的任务 (1)2. 系统设计 (2)2.1 系统的工作原理 (2)2.2 VGA显示原理 (2)2.3 键盘驱动 (4)3 系统设计 (4)3.1图像信号产生模块的设计 (4)3.2 视频输出接口电路部分设计 (5)3.3 模式控制与显示部分设计 (6)3.4 VGA显示模块 (6)4 课程设计心得 (9)5 致谢 (10)参考文献 (11)附录 (12)附录A 总原理图 (12)附录B 实验现象 (12)附录C 引脚分布图 (14)附录D 实验程序 (14)1.绪论1.1 EDA技术的发展我们已经进入数字化和信息化的时代,其特点就是各种数字产品的广泛应用。

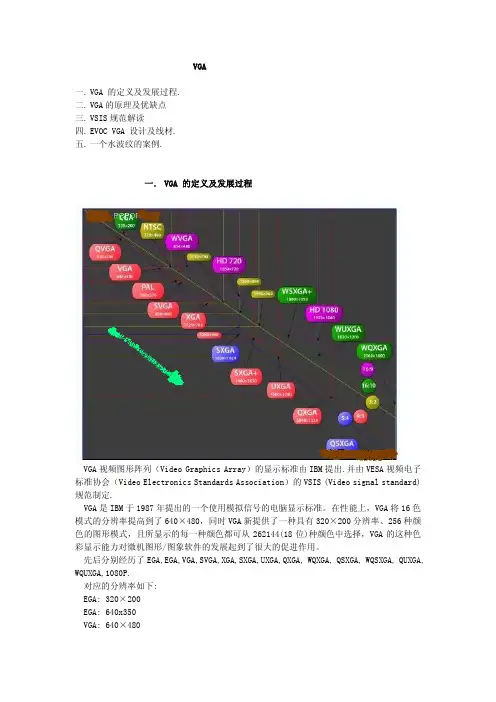

VGA一. VGA 的定义及发展过程.二. VGA的原理及优缺点三. VSIS规范解读四. EVOC VGA 设计及线材.五. 一个水波纹的案例.一. VGA 的定义及发展过程VGA视频图形阵列(Video Graphics Array)的显示标准由IBM提出.并由VESA视频电子标准协会(Video Electronics Standards Association)的VSIS (Video signal standard)规范制定.VGA是IBM于1987年提出的一个使用模拟信号的电脑显示标准。

在性能上,VGA将16色模式的分辨率提高到了640×480,同时VGA新提供了一种具有320×200分辨率、256种颜色的图形模式,且所显示的每一种颜色都可从262144(18位)种颜色中选择,VGA的这种色彩显示能力对微机图形/图象软件的发展起到了很大的促进作用。

先后分别经历了EGA,EGA,VGA,SVGA,XGA,SXGA,UXGA,QXGA, WQXGA, QSXGA, WQSXGA, QUXGA, WQUXGA,1080P.对应的分辨率如下:EGA: 320×200EGA: 640x350VGA: 640×480SVGA: 800x600XGA: 1024x768SXGA: 1280x1024UXGA: 1600x1200QXGA: 2048x1536WQXGA: 2560x1600QSXGA: 2560x2048WQSXGA: 3200x2048QUXGA: 3200x2400WQUXGA: 3840x24001080P: 1920*10801920*1080分辨率是美国电影电视工程师协会(SMPTE)制定的最高等级高清数字电视的格式标准,有效显示格式为:1920*1080,像素数达到207.36万。

美国电影电视协会将数字电视扫描线的不同分为:1080p、1080i和720p。

编号:EDA综合设计实验报告课题:硬件乐曲演奏电路设计专业:智能科学与技术学生姓名:黎良贵学号: 12008502112014 年11 月30 日一、概述:硬件乐曲演奏电路顶层模块图如图1-1所示,电路图由11个子模块组成,能够实现:(1)梁祝乐曲的自动演奏;(2)键盘弹奏歌曲;(3)ROM中能存两首歌曲,并能手动选歌。

二、实验原理:①音符的频率可以由图1-1中的SPKER获得。

这是一个数控分频器。

由其CLK端输入一具有较高频率(1MHz)的时钟,通过SPKER分频后,经由D触发器构成的分频电路,由SPK_KX口输出。

由于直接从分频器中出来的输出信号是脉宽极窄的信号,为了有利于驱动扬声器,需另加一个D触发器分频以均衡其占空比,但这时的频率将是原来的1/2。

SPKER对CLK输入信号的分频比由输入的11位预置数TN[10..0]决定。

SPK_KX的输出频率将决定每一音符的音调;这样,分频计数器的预置值TN[10..0] 与输出频率就有了对应关系,而输出的频率又与音乐音符的发声有对应关系,例如在F_CODE模块中若取TN[10..0]=11'H40C,将由SPK_KX发出音符为“3”音的信号频率。

②音符的持续时间需根据乐曲的速度及每个音符的节拍数来确定,图1-1中模块F_CODE的功能首先是为模块SPKER(11位分频器)提供决定所发音符的分频预置数,而此数在SPKER输入口停留的时间即为此音符的节拍周期。

模块F_CODE是乐曲简谱码对应的分频预置数查表电路,每一音符的停留时间则由音乐节拍和音调发生查表模块MUSIC中简谱码和工作时钟inclock的频率决定,在此为4Hz。

这4Hz频率来自分频模块FDIV,模块MUSIC是一个LPM_ROM。

它的输入频率来自锁相环PLL20的2kHz输出频率。

而模块F_CODE的14个值的输出由对应于MUSIC模块输出的q[3..0]及4位输入值INX[3..0]确定,而INX[3..0]最多有16种可选值。

实践教学要求与任务:输入24bitRGB信号存放于片外SRAM,输出VGA驱动信号(1)显示数据24bit构成MSB为R,LSB为B;(2)构造SRAM访问电路,设计输出驱动时序电路;(3)屏幕800*600;刷新时间33ms;时钟40MHz;(4)使用SMIC工艺库smic18_IP6M完成设计;(5)完成全部流程:设计规范文档、模块设计、代码输入、功能仿真、约束与综合、布局布线、物理验证。

工作计划与进度安排:本设计持续 15 天,其中最后一天(周五)为答辩时间。

第 1-2 天:讲解题目,准备参考资料,检查、调试实验软硬件,进入设计环境,开始设计方案和验证方案的准备;第 3-5 天:完成设计与验证方案,经指导老师验收后进入模块电路设计(验收设计文档);第 6-9 天:完成模块电路设计,进行代码输入,并完成代码的仿真(验收代码与仿真结果);第 9-10 天:约束设计,综合(验收约束与综合结果);第 11-12 天:布局布线,完成版图(验收版图结果);第 13-14 天:物理验证、后仿真,修改设计(验收物理验证结果和时序仿真结果);第 15 天:整理设计资料,验收合格后进行答辩。

摘要VGA是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。

虽然在现如今的计算机领域,VGA显示器接口以略显过时,但因其仍然是最多制造商所共同支持的一个标准。

所以个人电脑在加载自己独特的驱动之前,都必须支持VGA的标准,被也说明了VGA在显示标准中的重要性与兼容性。

在本课设中,设计完成了一个支持分辨率为800*600,刷新频率为60Hz的VGA驱动电路。

并完成全部流程:设计规范文档、模块设计、代码输入、功能仿真、约束与综合、布局布线、物理验证。

关键字:VGA驱动电路;Verilog HDL;半定制目录引言 (1)VGA显示驱动电路设计 (2)1. 电路设计 (2)1.1 设计要求 (2)1.1.1 设计功能 (2)1.1.2 设计环境 (2)1.2 VGA电路基本原理及参数 (2)1.3 设计规范 (4)1.3.1 接口规范 (4)1.3.2 功能规范 (4)1.3.3 性能规范 (4)1.4 电路模块设计 (5)2. 电路仿真与分析 (6)2.1 代码输入 (6)2.2 功能仿真 (6)2.3 FPGA验证 (7)3. 电路逻辑综合 (9)3.1 约束脚本 (9)3.2 时序报告 (9)3.3 面积报告 (10)4. 电路版图设计 (11)4.1 布局 (11)4.2 时钟线优化 (11)5. 物理验证 (13)总结 (14)参考文献 (15)附录一:设计代码 (16)附录二:测试平台 (20)附录三:约束脚本 (22)附录四:管脚文件 (25)引言本文采用Verilog 硬件描述语言描述VGA显示电路,VGA作为一种标准的显示接口得到广泛的应用。

北华航天工业学院课程设计报告(论文)设计课题:乐曲演奏电路的设计专业班级:学生姓名:指导教师:设计时间北华航天工业学院电子工程系乐曲演奏电路的设计课程设计任务书指导教师:胡辉内容摘要在EDA开发工具Quartus II 6.0平台上,采用VHDL语言层次化和模块化的设计方法,通过音符编码的设计思想,预先定制乐曲,实现动态显示乐曲演奏电路的设计,并在此基础上,基于同一原理,使此电路同时具备了简易电子琴的功能,使基于CPLD/FPGA芯片的乐曲播放数字电路得到了更好的优化,提高了设计的灵活性和可扩展性。

关键字:EDA;Quartus II;VHDL;CPLD/FPGA;乐曲演奏电路;简易电子琴目录一概述 (1)二方案设计与论证 (2)三单元电路设计与参数计算 (2)四总原理图 (14)五安装与调试 (14)六性能测试与分析 (14)七结论 (15)八心得体会 (15)九参考文献 (15)一、概述(一)本实验的设计原理是不同的音名对应不同的频率,设计的难点是准确的产生各音名对应的频率。

简谱音名与频率的关系各音名所对应的频率可由一频率较高的基准频率进行整数分频得到,所以实际中产生各音名频率为近似的整数值。

基准频率越高,近似程度越好,音准也越好,但同时分频系数会很大,耗费芯片资源也越多。

本实验选取fo=1MHZ的信号作为基准频率。

分频系数A及n的公式如下:分频系数A=fo÷音名频率分频系数n=分频系数A÷2分频系数n=fo÷音名频率÷2以中音1为例来说明:由fo=1MHZ产生中音1的523.25Hz,其中分频系数A=1000000÷523.25≈1911.13,取整数值为A=1911,此分频系数可由计数器实现。

但若不加处理语句,其分频后的523Hz信号不是对称方波,而占空比很小的方波将很难使扬声器有效的发出声音。

为了得到对称方波,可将分频系数A分解为:分频系数A=分频系数n×2。

《电子系统综合设计》课程设计报告VGA显示系统设计专业:集成电路班级:电子0 6 0 4学号:200681131姓名:高丕龙VGA显示系统设计一.概述本实验采用工业标准的VGA显示模式为:640×480×16×60。

该系统实现的目标是将数据源写入视频存储器中的视频数据通过D/A转换器输出给VGA显示器,从而得到预期的视频显示。

为此,可把FPGA作为整个设计的核心,负责产生正确的行同步信号和场同步信号输出给VGA显示器,使VGA显示器能够正确的同步:负责进行水平、垂直计数,并将计数器的值或行、场同步信号转换成存储器的地址数据输出给视频存储阵列,使视频存储阵列能够正确的输出图像的颜色信息:负责根据同步时序控制D/A转换器及时的把视频存储阵列输出的颜色的数字量转换成模拟量送给VGA显示器。

二.设计任务:1、根据VGA视频信号时序,利用FPGA控制产生视频信号,在普通彩色显示器上显示彩色图像,包括8色横彩条和8色竖彩条。

2、在显示器上显示自行设计的彩色规则图形——棋盘形。

三.VGA显示原理常见的彩色显示器一般由阴极射线管(CRT)构成,彩色由GRB(Green Red Blue)基色组成。

显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB基色,合成一个彩色像素。

扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT、对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。

VGA显示控制器控制CRT显示图象的过程如下图所示。

四.设计方案1.整体设计FPGA是整个系统的中枢,在FPGA内部,主要有两个模块:一个是时序生成模块,另一个是彩条产生模块。

它根据外部时钟CLK进行计数,并根据计数器的值来确定行、场所处的位置,并依此产生以下信号:行同步信号(Hs),场同步信号(Vs)和输出允许信号。

一、设计题目:乐曲硬件演奏电路的VHDL设计二、设计目标:了解一般乐曲演奏电路设计设计方法,学习VHDL语言,熟悉EDA设计软件QuartusII和MAX+plusⅡ,加强独立完成电子设计的能力。

(1)能够播放“梁祝”乐曲。

(2)能够通过LED显示音阶。

(3)(选作)具有“播放/停止”功能,并在此基础上实现“按键演奏”的电子琴功能。

主芯片型号为FLEX10K10LC84-4三、实验电路的工作原理:(演奏电路逻辑图)组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能够连续演奏所需的两个基本要素,设计演奏电路的关键就是获得这两个要素所对应的数值以及通过纯硬件的手段来利用这些数值实现所希望乐曲的演奏效果。

演奏电路逻辑图有三部分:音乐节拍和音调发生器、简谱码对应的分频预置数查表电路、数控分频与演奏发生器。

演奏电路逻辑图:四、设计内容:1.完成程序的编辑工作。

2.将音乐数据制作成LMP_ROM文件.3.将程序加载到MAX+plusⅡ中进行编译、仿真,并保存仿真结果。

4.到实验室进行下载验证。

引脚进行锁定,然后下载到实验芯片中观察实验结果。

五、仿真结果:1.音乐节拍和音调发生器(NoteTabs.VHD)notetabs模块中设置了一个8位二进制计数器(计数最大值138),作为音符数据ROM的地址发生器。

这个计数器的计数频率选为4Hz,即每一个计数值的停留时间为0.25秒,恰为当全音符设为1秒时,四四拍的4分音符持续时间。

随着notetabs模块中的计数器按4Hz的时钟速率作为加法计数时,即随地址值递增时,音符数据ROM中的音符数据将从ROM中通过ToneIndex[3..0]端口输向ToneTaba模块,“梁祝”乐曲就开始连续自然的演奏起来了。

Notetabs模块仿真图:2.简谱码对应的分频预置数查表电路(ToneTaba.VHD)音符的持续时间需根据乐曲的速度及每个音符的节拍数来确定,tonetaba 模块的功能首先是为speakera提供决定所发音符的预置数,而此数在speakera 输入口停留的时间即为此音符的节拍值。

一、课程设计内容1、使用Verilog语言和Modelsim仿真器完成可显示横彩条、竖彩条、棋盘格相间的VGA控制器的设计和验证2、设计并验证可显示英语单词”HIT”的VGA控制器3、使用Quartus II和SOPC实验箱验证设计的正确性4、Verilog代码要符合微电子中心编码标准二、FPGA原理CPLD、FPGA是在PAL、GAL等基础上发展起来的一种具有丰富的可编程I/O 引脚、逻辑宏单元、门电路以及RAM空间的可编程逻辑器件,几乎所有应用门阵列、PLD和中小规模通用数字集成电路的场合均可应用FPGA和CPLD器件。

CPLD 的设计是基于乘积项选择矩阵来实现的,而FPGA基于查找表来设计的。

查找表就是实现将输入信号的各种组合功能以一定的次序写入RAM中,然后在输入信号的作用下,输出特定的函数运算结果。

其结构图如图1所示:图1. FPGA查找表单元一个N输入查找表(LUT,Look Up Table)可以实现N个输入变量的任何逻辑功能,如N输入“与”、N输入“异或”等。

输入多于N个的函数、方程必须分开用几个查找表(LUT)实现(如图2所示)。

图2 FPGA查找表单元内部结构该系统设计中,FPGA芯片用的是ALTERA公司的EP1K30QC208-2,它的系统结构如图3所示。

它由若干个逻辑单元和中央布线池加I/O端口构成图3 EP1K30QC208内部结构三、VGA接口VGA的全称为Video Graphic Array,即显示绘图阵列。

在PC行业发展的初期,VGA以其支持在640X480的较高分辨率下同时显示16种色彩或256种灰度,同时在320X240分辨率下可以同时显示256种颜色的良好特性得到广泛支持。

后来,厂商们纷纷在VGA基础上加以扩充,如将显存提高至1M并使其支持更高分辨率如800X600或1024X768,这些扩充的模式就称之为VESA(Video Electronics Standards Association,视频电子标准协会)的Super VGA模式,简称SVGA,现在的显卡和显示器都支持SVGA模式。

VGA控制显示实验本实验是在VGA基本控制之上的更进一步的对VGA显示进行控制的。

1.VGA显示原理常见的彩色显示器一般由CRT(阴极射线管)构成,彩色是由R(红),G(绿),B(蓝)3基色组成。

显示采用逐行扫描的方式,阴极射线枪发出的电子束打在涂有荧光粉的荧光屏上,产生RGB三色基,最后合成一个彩色图像。

从屏幕的左上方开始自左向右的扫描,每扫完一行电子束回到下一行的最左端,每行结束后电子枪回扫的过程中进行消隐。

然后从新开始行扫描,消隐,直到扫描到屏幕的右下方,电子书回到屏幕的左上方重新开始新的图像扫描,并且在回到屏幕的左上方过程中进行消隐,在消隐的过程中不发射电子束。

每一行扫描结束时,用HS(行同步)信号进行同步;扫描完所有的行后用VS(场同步)信号进行同步。

2.VGA实验功能说明本实验设计是基于FPGA的VGA接口控制器,通过对FPGA硬件编程实现显示驱动,通过VGA接口在显示器上显示彩条,圆环和动态方块信号。

实现显示驱动需要5个信号:R,G,B,hsyncb,vsyncb,其中R,G,B分别为红,绿,蓝颜色的强度信号,hsyncb和vsyncb 为行同步和场同步信号,均为模拟信号。

由实验板将FPGA输出直接与VGA接口相连,中间没有D/A转换电路,因此这五个信号实际上均为数字信号。

hsyncb和vsyncb可用数字信号等效;R,G,B分别用3位数字信号表示。

用于显示驱动的行,场同步信号利用实验板的50MHz系统时钟产生。

VGA接口控制器由三个模块组成,即产生行场同步信号和消隐信号的VGASig模块,产生内容和位置信息的ColorMap模块,产生动态时序信号的count16以及顶层模块VGACore,模块之间的信号连接如图:本设计的整体思想是:首先由系统时钟二分频后作为VGASig模块的时钟输入信号;VGASig 模块的hsyncb信号和vsyncb信号形成顶层模块的hsyncb(行同步)和vsyncb(场同步)信号;VGASig模块的hcnt和vcnt信号作为ColorMap模块的地址控制输入,ColorMap模块根据该信号的值输出相应的RGB颜色信息rgbx,rgby,rgbz和rgbw。

《电子系统综合设计》课程设计报告VGA显示系统设计专业:集成电路班级:电子0 6 0 4学号:200681131姓名:高丕龙一.实验目的:1、根据VGA视频信号时序,利用FPGA控制产生视频信号,在普通彩色显示器上显示8色彩色图像。

2、在显示器上显示自行设计的彩色规则图形——棋盘形。

二.实验原理:1概述该系统实现的目标是将数据源写入视频存储器中的视频数据通过D/A转换器输出给VGA显示器,从而得到预期的视频显示。

按照这个目的,FPGA作为整个设计的核心,负责产生正确的行同步信号和场同步信号输出给VGA显示器,使VGA显示器能够正确的同步:负责进行水平、垂直计数,并将计数器的值或行、场同步信号转换成存储器的地址数据输出给视频存储阵列,使视频存储阵列能够正确的输出图像的颜色信息:负责根据同步时序控制D/A转换器及时的把视频存储阵列输出的颜色的数字量转换成模拟量送给VGA显示器。

FPGA是整个系统的中枢,在FPGA内部,主要有两个模块:一个是时序生成模块,另一个是地址产生模块。

它根据外部时钟CLK进行计数,并根据计数器的值来确定行、场所处的位置,并依此产生以下信号:行同步信号(Hs),场同步信号(Vs),地址信号,和输出允许信号。

其中,行同步信号和场同步信号是严格的周期信号,直接送给通过VGA接口相连的VGA显示器做同步使用。

只要连接这两个信号就完全可以点亮显示器,只不过在显示器上没有任何的颜色信息。

输入允许段一共有两个,一个是视频存储阵列的输出允许端,它控制视频存储阵列锁存地址线上的地址对应单元的数据。

另外一个输出允许端是控制D/A转换阵列的。

视频存储阵列是由三块容量和参数一样的双口RAM堆叠而成,三块RAM是独立的并列关系。

它们每一块负责存储三原色中一种颜色的数字量。

三块RAM 分别存储红(R),绿(G),蓝(B)分量。

双口RAM输入端的地址和数据全部来自CPU或外部的数据采集源,输出端的地址由FPGA产生,而数据则直接输出给视频D/A转换阵列。

视听 2020.0335技术研发与应用一、引言目前在贵港转播台值班房,值班员通常使用收音机监听台站发射的广播节目。

现台站同时发射5套调频广播节目,由于多套节目的声音混淆在一起,因此不容易分辨每套节目是否正常。

为保证安播,机房值班人员提出能否将广播节目音频在电视墙显示监看的想法。

鉴于目前市场上类似的设备较少,较难采购功能符合需求的设备,因此本文使用STM32单片机作用主控,设计了一套广播音频可视化显示方案。

将多路模拟广播节目音频电压信号通过VGA 接口,接显示器在电视墙上进行可视化监看。

实现了当值班员在监视电视节目时,也可以同时监视多路广播节目是否正常,较有效提高了台站广播节目的安全播出效果。

二、整体方案设计本方案的整体设计框图如图1所示。

前端使用广播调谐器或收音头接收台站发射的5套广播节目,解调输出的左、右声道,共10路模拟音频电压信号,输入信号调理电路。

信号调理电路主要作用是把信号调整到0V-3.3V 之间(即单片机的A/D 采样电压范围内)。

然后分别输入到STM32单片机的模数转换器ADC 通道1至通道10。

单片机的ADC 工作于扫描模式,对10个ADC 通道进行轮询扫描转换。

为提高效率,使用单片机的DMA 控制器,将ADC 转换的结果传到RAM 中,以便软件调用。

Micro SD 卡主要作用是存储背景图片和字库数据,单片机完成ADC 数据处理后,单片机通过内部静态存储控制器(FSMC),控制16位并行数据总线把要显示的图像像素RGB 数据,写入到VGA 显卡的显存里。

VGA 显卡自动完成读取显存内的图像数据,并经数模转换成模拟RGB 信号,加入VGA 控制时序信号,输出到VGA 接口,实现显示器实时显示5套广播音频信号的功能。

三、硬件设计(一)单片机与ADC 引脚分配根据系统要求,STM32F 系列是一款基于Cortex-M3内核的ARM 微控制器,芯片具有16个ADC 输入引脚,同时具有静态存储控制器(FSMC),可以快速对外部的SRAM,NAND FLASH,NOR FLASH 和PSRAM 等存储器进行快速读写。

课程设计报告课程名称数字系统设计自动化院部名称电子信息工程学院(筹)专业电子信息工程班级学生姓名学号课程设计地点课程设计学时指导教师金陵科技学院教务处制课程设计报告书写要求课程设计报告原则上要求学生手写,要求书写工整。

若因课程特点需打印的,要遵照以下字体、字号、间距等的具体要求。

纸张一律采用A4的纸张。

课程设计报告书写说明课程设计报告应包含以下七部分内容:1、摘要2、目录3、前言/引言 4.正文 5. 结论 6. 参考文献7. 附录,每部分的书写要求参见具体条目要求。

填写注意事项(1)准确说明,层次清晰。

(2)尽量采用专用术语来说明事物。

(3)外文、符号、公式要准确,应使用统一规定的名词和符号。

(4)应独立完成课程设计报告的书写,严禁抄袭、复印,一经发现,以零分论处。

课程设计报告批改说明课程设计报告的批改要及时、认真、仔细,一律用红色笔批改。

课程设计报告的批改成绩采用五级计分制或百分制,具体评分标准由各院部自行制定。

课程设计报告装订要求报告批改完毕后,任课老师应将课程设计报告以自然班为单位、按学号升序排列,并附上一份该课程设计的教学大纲。

课程设计题目:通过fpga驱动vga输出,实现简单的vga显示一、摘要(所进行设计工作的主旨、缘起、目的,设计工作的主要内容、过程,采用的方法及取得的成果。

关键字(Key Words): 一般3~5个,最能代表报告内容特征,或在报告起关键作用,最能说明问题的词组)本文介绍了一种利用可编程逻辑器件实现VGA图像显示控制的方法,阐述了VGA图像显示控制器中VGA显像的基本原理以及功能演示,利用可编程器件FPGA设计VGA图像显示控制的Verilog设计方案,并在Xilink公司的Xilinx ISE软件环境下完成VGA模块的设计。

而且给出了VGA模块的设计思路和顶层逻辑框图。

最终实现VGA图像显示控制器,VGA图像控制器是一个较大的数字系统,传统的图像显示的方法是在图像数据传输到计算机,并通过显示屏显示出在传输过程中,将图像数据的CPU需要不断的信号控制,所以造成CPU的资源浪费,系统还需要依靠计算机,从而减少了系统的灵活性。

电子信息工程专业综合设计(报告)(课程设计)题目基于FPGA的VGA图形显示二级学院电气与电子工程学院专业电子信息工程班级学生姓名学号同组姓名指导教师时间基于FPGA的VGA图形显示摘要:本次的题目是基于FPGA的VGA图形显示,实现VGA图像显示与控制。

本文介绍的主要内容围绕着显示特定图片,且图片可受控制的相关原理与方法展开。

根据VGA显示原理,利用VHDL作为逻辑描述手段,设计了一种基于现场可编程器件FPGA的VGA接口控制器。

实现VGA图像显示控制器是通过Altera公司的QuartusII软件环境下对VGA模块的设计和顶层逻辑框图设计。

FPGA的嵌入式系统中能代替VGA的专用显示芯片,节约硬件成本,节省计算机处理时间,加快数据处理速度并具有显示面积大,色彩丰富、承载信息量大、接口简单等优点。

除此以外FPGA芯片和EDA设计方法的使用,可根据用户的需求,为设计提供了有针对性的VGA显示控制器,可不需要依靠计算机,它可以大大降低成本,并可以满足生产实践中不断改变的需要。

关键字:FPGA VGA 图像控制器一、前言本次课程设计主要是通过Altera公司的QuartusII软件环境下对VGA模块的设计和顶层逻辑框图设计。

VGA是IBM于1987年提出的一个使用模拟信号的电脑显示标准。

在性能上,VGA将16色模式的分辨率提高到了640×480,同时VGA新提供了一种具有320×200分辨率、256种颜色的图形模式,且所显示的每一种颜色都可从262144(18位)种颜色中选择,VGA的这种色彩显示能力对微机图形/图象软件的发展起到了很大的促进作用先后分别经历了EGA, EGA, VGA, SVGA, XGA, SXGA, UXGA, QXGA, WQXGA, QSXGA, WQSXGA, QUXGA, WQUXGA, 1080P。

目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转变为R,G,B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

基于FPGA动态显示乐曲演奏器片上系统的分析与设计杨国庆【摘要】分析了乐曲演奏设计中音符、频率、节拍、显示与编码的相互关系,并在EDA开发工具QuartusⅡ平台上,采用VHDL语言层次化和模块化的设计方法,通过音符编码的设计思想,实现了基于FPGA片上系统(SoC)动态显示乐曲演奏器的设计,使乐曲演奏数字电路设计得到了更好的优化,同时减少了设计芯片的数量、缩小了体积、降低了功耗、提高了设计的灵活性、可靠性和可扩展性.【期刊名称】《现代电子技术》【年(卷),期】2006(029)019【总页数】3页(P162-164)【关键词】FPGA;片上系统;乐曲演奏器;VHDL;编码;模块化【作者】杨国庆【作者单位】天津城市建设学院,天津,300384【正文语种】中文【中图分类】TP391.721 前言随着微电子技术、集成技术和计算机技术的迅速发展,数字化电子系统的设计方法和手段发生了很大的变化。

特别是可编程逻辑器件的功能和容量的不断扩大,如FPGA(Field Programmable Gate Array,现场可编程门阵列)使集成电路的设计进入片上系统(System on a Chip,SoC)或可编程片上系统(System on a Programmable Chip,SOPC)的设计时代[1]。

同时采用超高速集成电路硬件描述语言VHDL(Very High Speed Integrated Circuit Hardware Description Language),其具有多层次描述系统硬件功能的能力,既支持模块化设计,也支持层次化设计,使各种数字化电子系统的设计通过描述芯片功能实现系统功能,从而有效地缩短了产品开发周期,减少了设计芯片的数量,缩小了系统体积,降低了系统能耗,提高了系统的灵活性和可靠性。

这种基于芯片的设计方法,目前已成为现代电子系统设计的主流。

在美国ALTERA公司QuartusⅡ的EDA (Electronics Design Automation)软件平台上,采用VHDL语言层次化和模块化的设计方法,目标器件选用Cyclone系列FPGA器件中的EP1C3T144C8芯片,实现了基于FPGA动态显示乐曲演奏器的数字化系统设计,该电路采用乐曲音谱编码输出的方式来记录乐曲,具有占用存储空间少,设计方法简便等优点,其代码具有良好的可读性和可移植性,能够演奏一首或几首指定乐曲。

南昌大学实验报告学生姓名:赵震学号: 6103414030 专业班级:生物医学工程141班实验类型:□验证□综合√□设计□创新实验日期: 2016.12.16 实验成绩:实验五:VGA 彩条信号发生器的设计(一)实验目的:1.了解普通显示器正确显示的时序。

2.了解 VHDL 产生 VGA 显示时序的方法。

3.进一步加强对 FPGA 的认识。

(二)实验原理:VGA 显示器在显示过程中主要由五个信号来控制,分别是 R、G、B、HS 和VS。

其中 R、G、B 分别用来驱动显示器三个基色的显示,即红、绿和篮,HS是行同步信号,VS 是场同步信号。

在做本实验时,由于没有任何显示器驱动,所以显示器工作在默认状态,分辨率:640×480,刷新率:60Hz。

在此状态下,当VS和 HS都为低电平时,VGA 显示器显示亮的状态,其正向扫描过程约为 26us。

当一行扫描结束后,行同步信号 HS置高电平,持续约 6us 后,变成低电平,在HS为高电平期间,显示器产生消隐信号,这就是显示器回扫的过程。

当扫描完一场后,也就是扫描完 480行以后,场同步信号 VS置高电平,产生场同步,此同步信号可以使扫描线回到显示器的第一行第一列位置。

显示器显示的时序图如下图 2-22 所示:图 2-22 CRT 显示器时序(三)设计要求:本实验要完成的任务就是通过FPGA在显示器上显示一些条纹或图案,要求CRT显示器上能够显示横条纹、竖条纹以及棋盘格子图案。

实验中系统时钟选择时钟模块的12MHz,用一个按键模块的S1来控制显示模式,每按下一次,屏幕上的图案改变一次,依次为横条纹、竖条纹以及棋盘格子图案。

实验的输出就直接输出到 VGA 接口,通过CRT 显示器显示出来。

实验箱中用到的数字时钟模块、按键开关与 FPGA 的接口电路,以及数字时钟源、按键开关与 FPGA 的管脚连接在以前的实验中都做了详细说明,这里不在赘述。

VGA接口在实验系统的视频输入输出模块。

本科学生设计性实验报告 项目组长 学号 成 员 无 专 业 通信工程___ 班级 101 实验项目名称VGA图片(动态)显示与乐曲硬件演奏电路设计 指导教师及职称 开课学期 2012 至 2013 学年 第二 学期 上课时间 2013 年 05 月 05 日 一、实验设计方案 实验名称:乐曲硬件演奏电路设计与VGA图片(动态)显示 实验时间:20130505

小组合作: 是○ 否○ 小组成员: 实验目的和要求

1.学习利用数控分频器设计硬件乐曲演奏电路 2.掌握模块化和层次化的设计方法以及音符编码的设计思想 3. 学习VGA图像显示控制电路设计

4.根据VGA的工作时序,然后完成VGA图片动态显示。 5.熟悉和掌握基于ROM的VGA显示原理以及ROM的使用方法。

1、实验场地及仪器、设备和材料: PC计算机,Quartus II 9.0软件,EDA/SOPC实验箱 2、实验思路(实验内容、数据处理方法及实验步骤等): 一.VGA图片(动态)显示 1.实验原理:VGA工业标准显示模式要求,行同步,场同步都为负极性,即同步脉冲要求是负脉冲。设计VGA图像显示控制要注意两个问题:一个是时序驱动,这是完成设计的关键,时序有偏差,显示必然不正常;另一个是VGA显示信号电平驱动

我选的是800X600时钟为40MHZ的工业标准显示模式。 所以我的相应的时序控制的程序如下: module vga(clk,hs,vs,r,g,b,rgbin,dout); input clk; output hs,vs; output r,g,b; input [2:0] rgbin; output[14:0] dout; reg [10:0] hcnt; reg[9:0] vcnt; reg r,g,b; reg hs,vs; assign dout={vcnt[6:0],hcnt[6:0]}; always @(posedge clk) begin if(hcnt<1056) hcnt<=hcnt+1; else hcnt<={11{1'b0}};end always @(posedge clk) begin if(hcnt==825)begin if(vcnt<628) vcnt<=vcnt+1; else vcnt<={10{1'b0}};end end always @(posedge clk) begin if((hcnt>=840)&(hcnt<=968)) hs<=1'b0; else hs<=1'b1;end always @(vcnt) begin if((vcnt>=601)&(vcnt<=605)) vs<=1'b0;else vs<=1'b1;end always @(posedge clk) begin if(hcnt<800&vcnt<600) begin r<=rgbin[2];g<=rgbin[1];b<=rgbin[0];end else begin r<=1'b0;g<=1'b0;b<=1'b0;end end endmodule 2. 基于ROM的VGA显示原理

(1)ROM的原理及使用 Altera的器件内部提供了各种存储器模块(RAM、ROM或双口RAM),可以在设计中使用MegaWizard Plug-In Manager,执行【Tools】|【MegaWizard Plug-In Manager】菜单命令来创建所需要的存储器模块。也可以使用Altera提供的宏功能模块LPM_ROM来创建存储器模块。 每个ROM模块有CLOCK(时钟)、address(地址)这两个输入信号和一个q(值)输出信号。ROM在每个时钟上升沿取出由地址信号所指定的存储单元中的值并输出。ROM内的值通过加载MIF(Memory Initialization File,存储器初始化文件)文件来实现。 (2)如何生成MIF文件: 如果已经有BMP格式的图片,则可以使用我们提供的BmpToMif这个软件,从现有的BMP格式图片生成MIF文件。其使用非常简单,注意要适当调整原图片的大小,这可以通过各种图形编辑软件修改,如Windows自带的画图程序、Photoshop等。 BmpToMif软件的功能有: ① 将bmp图片转为mif文件:将黑白图片转换为单色mif文件;将彩色图片转换为三色mif文件。 ② 将二进制文件转为mif文件,如将中英文点阵字库转换为mif文件。 3.实验过程: (1)时序控制子模块vga的设计: 功能:根据VGA显示器的工作原理,提供同步信号和像素位置信息,以及寻址ROM的地址信号。 程序代码如下: module vga(clk,hs,vs,r,g,b,rgbin,dout); input clk; output hs,vs; output r,g,b; input [2:0] rgbin; output[14:0] dout; reg [10:0] hcnt; reg[9:0] vcnt; reg r,g,b; reg hs,vs; assign dout={vcnt[6:0],hcnt[6:0]}; always @(posedge clk) begin if(hcnt<1056) hcnt<=hcnt+1; else hcnt<={11{1'b0}};end always @(posedge clk) begin if(hcnt==825)begin if(vcnt<628) vcnt<=vcnt+1; else vcnt<={10{1'b0}};end end always @(posedge clk) begin if((hcnt>=840)&(hcnt<=968)) hs<=1'b0; else hs<=1'b1;end always @(vcnt) begin if((vcnt>=601)&(vcnt<=605)) vs<=1'b0;else vs<=1'b1;end always @(posedge clk) begin if(hcnt<800&vcnt<600) begin r<=rgbin[2];g<=rgbin[1];b<=rgbin[0];end else begin r<=1'b0;g<=1'b0;b<=1'b0;end end endmodule 注解:本模块是时序控制也就是行与场信号的同步与消隐的问题;还有映射出rom的存储地址并取出相应的图片信号来显示; (2)使用MegaWizard Plug-In Manager创建存储RGB值的ROM模块: 把字长设为32768words也就是128X128的图像,并把相应的mif文件加入进去就可以了; (3)实现动画显示: 动画的本质就是多个静态画面的切换。动画利用了人眼的视觉暂留效应,连续播放内容连续的静止图片而给人以活动的感觉。当一系列形成图像的画面按一定的速度在人的视线中经过时,人脑便会产生物体运动的印象,即产生动画的效果。 实现简单的动画显示的原理是采用一套扫描和输出信号,并通过多路选择器使能多个ROM,这样就可以在多个画面中反复切换,形成动画。 在这里ROM图像集有两个(图像大小为128×128),如图2. 14所示。动态显示控制逻辑由多路选择器和分频器组成。地址转换函数整合在vga中并分别创建tupian和rtupian两个ROM模块,用来分别存储

两幅图像c1.bmp和c21.bmp的颜色值,存储器字数为128×128=27×27=16384,字长为3。它们对应的MIF文件分别为c1.mif和c2.mif。

与 两幅图画显示的时间间隔是1S,由于时钟频率是40MHZ所以要进行40M分频因为这个分频器产 生的信号是用来控制多路选择器的所以要是方波(这里程序的占空比是1:1)分频程序如下: module clk1s(clk,clk1s); input clk; reg [26:0] q; output clk1s; reg clk1s; always @(posedge clk) if (q==40000000) q<=0; else q<=q+1; always @(posedge clk) if(q==40000000) clk1s=~clk1s; endmodule

用元件库来建立多路选择器: 两个ROM模块的输出分别接至多路选择器的输入,使用上面的分频子模块产生周期为2s的输出时钟信号,来选择两个通路,即两幅图像以2s的周期轮换显示。多路选择器可以使用Quartus Ⅱ提供的参数化多路选择器LPM_MUX。 (4)创建顶层图形文件如图:

(5)配置引脚: (6)下载到试验箱

二.乐曲硬件演奏电路设计 ① 先用quartusII 建立相应的演奏的歌曲的mif文件: 这要注意乐谱上的某个音的停留时间以及相应的音符,然后在查F_CODE模块中的对应的音符音准表。 ② 用quartusII生成相应的满足要求的锁相环与存演奏文件的rom ③ 这里要特别提醒一定要注意相应模块的输入的时钟频率,因为时钟频率不对就不可能产生准确的音符。 ④ 并编写如下程序: 并把这些程序生成相应的模块图

module FP16(CLK,Q); output [3:0] Q;