通信工程专业英语论文

- 格式:doc

- 大小:449.50 KB

- 文档页数:36

⽆线通信G介绍英⽂论⽂ABriefIntroductionAboutGNetworkA B r i e f I n t r o d u c t i o n A b o u t5G N e t w o r k JiaAbstractWith the rapid development of wireless technologies, theconcept of the Fifth Generation (5G) wireless communication system started to emerge. But most people know little about 5G,including some aspects of 5G wireless communication networks ,just like what 5G is about: what are the building blocks of core 5G system concept, what are the main challenges and how to tackle them. Besides, A number of countries and organizations working on 5G, 5G development situation in China is of concern to everyone, China also needs to have its own place in such a competitive environment.Keywords:5G Network, history, Core concept, Challenges, Solutions, In chinaTable of Content1. Introduction5G (Fifth-generation mobile communications) is a new generation of mobile communication mobile communication systems for 2020, with high spectral efficiency and low power consumption, in terms of transfer rate and resource utilization improvement over 4G system 10 times, its wireless coverage performance and user experience will be significantly improved. 5G will be closely integrated with other wireless mobile communication technology, constitute a new generation of ubiquitous mobile information network, to meet future mobile Internet traffic 1000x development needs in 10 years.[1] In this paper I will show you some latest research and development history,what are the building blocks of core 5G system concept, what are the main challenges and how to tackle them firstly. In the rest of paper I will show how 5G development in China in recent years and my conclusion after research literature.2. Research and development historyFebruary 2013, the EU announced that it would grant 50 million euros to accelerate the development of 5G mobile technology, plans to launch a mature standard in 2020. [2][3]May 13,2013,South Korea's Samsung Electronics Co., Ltd. announced that it has successfully developed the 5th generation mobile communication (5G) core technology, which is expected to begin in 2020 to commercialization. The technology can transmit data at ultra-high frequency 28GHz to 1Gbps per second speed, and the maximum transmission distance of up to 2 km. In contrast, the current fourth generation Long Term Evolution (4GLTE) and services of only the transmission rate75Mbps. Prior to the transmission bottleneck is widely believed that a technical problem, while Samsung Electronics is the use of 64 adaptive array antenna elements transmission technology to crack this problem. Compared with the transmission speed of 4G technology in South Korea, 5G technology is hundreds of times faster. Using this technique, download a high-definition (HD) movie just need 10 seconds.Back in 2009, Huawei has launched the early research related technologies, and to show the prototype of the 5G base in later November 6, 2013,Huawei announced that it would invest $600 millionin 2018 for the 5G technology development and innovation, and predicted that users will enjoy 20Gbps commercial 5G mobile networks in 2020.May 8, 2014, the Japanese telecom operator NTT DoCoMo announced officially, Ericsson ,Nokia, Samsung and other six manufacturers to work together, began testing override 1000 times than existing 4G networks the carrying capacity of the high-speed network 5G network, the transmission speed is expected to 10Gbps. Outdoor testing scheduled to commence in 2015, and expects to begin operations in 2020.[3]March 1, 2015, the British "Daily Mail" reported that the British 5G network has successfully developed and tested for data transmission within 100 meters per second data transfer of up to 125GB, is times the 4G network, in theory, a 30 seconds to download movies, adding that investment in public test in 2018, 2020 officially put into commercial use.[4]February 11, 2015 in the afternoon news, IMT-2020 (5G) to promote the group (hereinafter referred to as "advance group") held a conference in Beijing 5G concept of white paper. White Paper from the mobile Internet and networking composed mainly of application scenarios, business needs and challenges of starting summedcontinuous wide area coverage, high reliability of the four major technology 5G scene of high capacity, low powerconsumption and low latency connection. Meanwhile, the combination of core technologies and key capabilities 5G and 5G concept proposed by the "flag sexuality index + a set of key technologies" common definition. March 3,2015,the European Economic and Social Commission for Digital Furusawa Ottinge officially announced the EU's vision of public-private partnerships 5G, and strive to ensure that the right to speak in the next generation of mobile technology in Europe in the global said that, 5G vision of public-private partnership involves not only fiber, wireless or satellite communications network integrated with each other, will also use the software-defined networking (SDN), network functions virtualization (NFV), Mobile Edge computing (MEC) and Fog Computing technology. In the spectrum, the EU's vision of public-private partnership will be designated 5G hundreds of megahertz to improve network performance, 60 GHz and higher frequency bands will also be taken into account.A number of countries and organizations announced, 5G network will be operational between 2020 ~ 2025.3. Core ConceptWhat is 5G I believe many people will be so questionable when see 5G. Judging from the word meaning, 5G refers to the fifth generation of mobile communications. However, how should it define Currently, the global industry for 5G concept not yet agreed. China IMT-2020 (5G) group released the White Paper considers the concept 5G, 5G integrated key capabilities and core technology, 5G concept by "important targets" and "a group of key technologies" to a common definition. Among them, the flag indicators "Gbps rate user experience" is a set of key technologies, including large-scale antenna array, ultra-dense networking, new multi-site, full-spectrum access and new network architectures.Recalling the course of development of mobile communications, each generation of mobile communication systems can be defined by sexual performance indicators and signs of key technologies. Wherein, 1G using FDMA, only analog voice services; 2G mainly using TDMA, can provide voice and low-speed digital data services; 3G to CDMA technology is characterized by user peak rate of 2Mbps to reach tens of Mbps, support multimedia data services; 4G OFDMA technology as the core, the user peak rate of up to 100Mbps ~ 1Gbps, can support a variety of mobile broadband data services.5G key competencies richer than previous generations of mobile communications, user experience, speed, density of connections, end to end delay, the peak rate and mobility and so will be the 5G key performance indicators. However, unlike the case in the past only to emphasize different peak rate, the industry generally believe that the rate of the user experience is the most important performance indicators, it truly reflects the real data rate available to the user, and the user experience is the closest performance. Based on the technology needs of the main scene 5G, 5G user experience rate should reach Gbps magnitude.Faced with diverse scenes of extreme performance demands differentiation, 5G cannot have solutions for all scenarios. In addition, the current wireless technology innovation has diversified development trend, in addition to the new multi-access technology, large-scale antenna array, ultra-dense network, the whole spectrum access, the new network architecture, also is considered to be the main technical can play a key role in the major technology scene. [5]4. Challenges and SolutionsIn this part I outline some observed research challengesand directions in the mobile network development and show some may become the future trends and solutions that may lead to improved network performance while meeting the constantly increasing user demands.5G Transport ChallengeIn order to understand the 5G transport challenges one must understand how 5G may evolve the radio access the various initiatives that are looking into 5G, we can defines 5G in terms of scenarios which the next generation wireless access networks will have to support. [6]A total of five future scenarios have been defined,namely amazingly fast (users want to enjoy instantaneous network connectivity), great service in a crowd, ubiquitous things communicating ., effective support to Internet of Things), super real time and reliable connections, and best experience follows you. Each of these scenariosintroduces a challenge .Three of these challenges ., very high data rate, very dense crowds of users and mobility) are more traditional in the sense that they are related to continued enhancement of user experience and supporting increasing traffic volumes and mobility. Two emerging challenges, very low latency and very low energy, cost and massive number of devices, are associated with the application of wireless communications to new areas. Future applications may be associated with one or several of these scenarios imposing different challenges to the network. In METIS twelve specific test cases were defined and mapped onto the five scenarios. The selected test cases essentially sample the space of future applications. Once technical enablers that fulfill there quirements for these test cases are defined, it is expected that other applications subject to the same fundamental challenges, will successfully be supported. As a consequence, defining technical enablers for the 5G test cases means also defining technical solutions to the 5G challenges.While METIS[7] is focused on wireless access, the challenges defined for 5G are expected to impact also the transport. Support for very high data rates will require both higher capacity radio access nodes as well as a densification of radio access sites. This, in turn, translates into a transport network that needs to support more sites and higher capacity per site, . huge traffic volumes. The greatservice in a crowd scenario will put requirements on the transport network to provide very high capacity on-demand to specific geographical locations. In addition, the best experience follows you scenario, suggests a challenge in terms of fast reconfigurability of the transport resources. On the contrary, the other 5G challenges are not expected to play as important role for shaping the transport, as for example the case of very low latency and very low energy, cost and massive number of devices. A properly dimensioned transport network based on modern wireless and/or optical technologies is already today able to provide extremely low latency, ., the end-to-end delay contribution of the transport network is usually almost negligible. In addition, while a huge number of connected machines and devices will create a challenge for the wireless network, it will most probably not significantly impact the transport. This is due to the fact that the traffic generated by a large number of devices over a geographical area will already be aggregated in the transport. The three scenarios for the transport network described above are summarized along with their corresponding challenges and test cases. Note that does not report all the original test cases but only those that pose challenges to the transport network. This information will be used later in the paper to identify the appropriate transport technologies.5G Transport Challenge and some SolutionsThis section provides an overview of a number of transportoptions for 5G wireless networks. A 5G transport network can be divided in two different segments, ., small cell transportand metro/aggregation (Fig. 2). The small cell transport segment aggregates the traffic to/from the wireless small cells towards the metro/aggregation segment. Different solutions in terms of technology ., optics, wireless) and topology ., tree, ring, mesh) are possible depending on the specific wireless access scenario. The metro/aggregation segment, on the other hand, connects different site types ., macro and/or small cells) among themselves and to the core network, the latter via the service edge (service node for the interconnection among different network domains). For the metro/aggregation segment one promising solution is represented by a dense-wavelength-division multiplexing (DWDM)[8] - centric network. In such a network, packet aggregation takes place at the edges of the network ., at small/macro cells sites and at the service edge), while at center ., between access and metro rings) switching is done completely in the optical domain thanks to active optical elements such as wavelength selective switches (WSSs) and reconfigurable optical add-drop multiplexers (ROADMs). It has already been demonstrated that DWDM-centric solutions have the potential to offer high capacity (in the order of tens to hundreds of Gbps) and lower energy consumption than their packet-centric counterparts ., with packet aggregation at the center of the network). [9] For this reason the DWDM-centric metro/aggregation concept may represent a good candidate for future 5G transport networks.[10]Machine to Machine CommunicationMachine to Machine Communication Besides network evolution, we observe also device evolution that become more and more powerful. The future wireless landscape will serve not only mobile users through such devices as smartphones, tablets or game consoles but also a tremendous number of any other devices, such as cars, smart grid terminals, health monitoring devices and household appliances that would soon require a connection to the Internet. The number of connected devices will proliferate at a very high speed. It is estimated that the M2M traffic will increase 24-fold between 2012 and 2017 .[11]M2M communication is already today often used in fleet monitoringor vehicle tracking. Possible future usage scenarios include a wide variety of e-health applications and devices, for instance new electronic and wireless apparatus used to address the needs of elderly people suffering from diseases like Alzheim er’s, o r wearable heart monitors. Such sensors would enable patient monitoring and aid doctors to observe patients constantly and treat them in a better way. It will also reduce the costs of treatment, as it can be doneremotely, without the need of going to a hospital.Remote patient monitoring using a Body Area Network (BAN), where a number of wireless sensors, both on-skin and implanted, record the patient’s health parameter s and sends reports to a doctor, will soon become a reality and an important part of 5G paradigm. Therefore, in order to offer e-health services, 5G will need to provide high bandwidth, meet extremely high Quality of Service (QoS) requirements, ., ultra low latency and lossless video compression for medical purposes, and implement enhanced security mechanisms. Furthermore, extended work will need to be done to efficiently manage radio resources, due to high diversity of traffic types, ranging from the reports sent periodically by the meters, to high quality medical video transmission.Core Network VirtualisationMoving towards 5G imposes changes not only in the Radio Access Network (RAN) but also in the Core Network (CN), where new approaches to network design are needed to provide connectivity to growing number of users and devices. The trend is to decouple hardware from software and move the network functions towards the latter one. Software Defined Networking (SDN) being standardised by Open Networking Foundation (ONF) assumes separation of the control and data plane[12]. Consequently, thanks to centralization and programmability, configuration of forwarding can be greatly automated. Moreover, standardisation efforts aiming at defining Network Functions Virtualisation (NFV) are conducted by multiple industrial partners including network operators and equipment vendors within ETSI.[13] Introducing a new software based solution is much faster than installing an additional specialised device with a particular functionality. Both solutions would improve the network adaptability and make it easily scalable. As a result of simpler operation, one can expect more dynamic and faster deployment of new network features.SummaryI only list a partial of the challenges of 5G networks and possible solutions , in fact, before making a formal universal 5G are still many problems to be overcome, it also requires effort frontline researchers.5. 5G In ChinaWhite paperFebruary 11, 2015,China released White paper about concept of 5G. It instantly make more people are concerned about5G. People eager to 5G network as soon as possible.The White Paper published, the concept from various angles, core competencies, technical characteristics of 5G defined and interpreted. At the same time, this is the IMT-2020 (5G) to promote the group last year after the publication of the White Paper 5G vision and needs another masterpiece. The foreseeable future, as the Chinese government pay more attention to the development of 5G and adopt a more open attitude, with the joint efforts of the industry, and China will play an increasingly important role in the global 5G development, global industry will also be unified 5G standard stride forward.5G standardsChina will actively participate in the development of 5G standards, will help China to further enhance the patent position in international communication standards, escort for our mobile phone manufacturing.China is a big manufacturing country, the state has proposed the creation of a strategic shift to China, 3G and 4G standards successful experience will help us win more patents in the development of 5G standard time, to achieve the transformation of China to create the goal.China communications companiesFebruary 12, 2015, the International Telecommunication Union standard 5G start research work, and clearly the IMT-2020 work plan: will complete the IMT-2020 international standard preliminary studies in 2015, 2016 will be carried out 5G technical performance requirements and evaluation methods Research, by the end of 2017 to start collecting 5G candidate to complete standards by the end of 2020.It is worth noting that, in the 5G standards, Huawei, ZTE and otherChinese telecommunications companies such as Ericsson veteran communications companies also play an important role, in which Huawei from between 2013 to 2018, five years is ho throw $ 600 million 5G conduct research and innovation. Recently, ZTE 5G key technologies to achieve new progress. Following the end of the year to complete Massive MIMO antenna array massive field test, ZTE independently developed the proposed super dense network UDN, multiple users to share access to Multi-User Shared Access and other core technologies through demonstration, in Pre5G phase is expected to be applied.[14]Huawei CEO HuHouKun rotation, said in 2015, the company will spend the equivalent of about 10% in 2014 research and development budget, or $ 60 million, the development of 5G technology. Overall, the company's commitment in the next few years, $ 600 million investment in 5G technology. 5G is a next-generation mobile communications standard, is expected early in the next decade and put into use.[15]SummaryChina needs to have its own place in the 5G market, China's communications companies are also very hard, believe in the future, China's R & D level 5G will lead other countries.6. ConlusionIn this paper,I presented a summary of the concept,chanlleges,solusions and 5G in 2020 and the future of the mobile Internet and networking business needs, 5G will focus on supporting the continuous wide area coverage, hot high-capacity, low power consumption and low latency connection highly reliable four main technical scenario, the use of large scale antenna array , ultra-dense networking, new multi-site, full-spectrum access and new network architectures, such as the core technology, through the evolution of new 4G air interface and two technical routes to achieve Gbps rate user experience, and to ensure consistency in service under a variety of scenarios .5G network to achieve real business there are a lot of unresolved issues. Also faced include how to design network architecture, including many technical challenges. Compared with previous generations of communications technology, 5G era biggest challenge is not how to increase the rate, but the user experience with traffic density, the number of terminals from a series of interwoven problems. As much as possible while also reducing user costs. This is the 5G network must be solved.。

多次反射罐方案DSA用于多跳认知无线电网络的分布式网络编码控制信道Alfred Asterjadhi等著1 前言大多数电磁频谱由政府机构长期指定给公司或机构专门用于区域或国家地区。

由于这种资源的静态分配,许可频谱的许多部分在许多时间和/或位置未使用或未被充分利用。

另一方面,几种最近的无线技术在诸如IEEE802.11,蓝牙,Zigbee之类的非许可频段中运行,并且在一定程度上对WiMAX进行操作;这些技术已经看到这样的成功和扩散,他们正在访问的频谱- 主要是2.4 GHz ISM频段- 已经过度拥挤。

为了为这些现有技术提供更多的频谱资源,并且允许替代和创新技术的潜在开发,最近已经提出允许被许可的设备(称为次要用户)访问那些许可的频谱资源,主要用户未被使用或零星地使用。

这种方法通常被称为动态频谱接入(DSA),无线电设备发现和机会性利用未使用或未充分利用的频谱带的能力通常称为认知无线电(CR)技术。

DSA和CR最近都引起了无线通信和网络界的极大关注。

通常设想两种主要应用。

第一个是认知无线接入(CW A),根据该认知接入点,认知接入点负责识别未使用的许可频谱,并使用它来提供对次用户的接入。

第二个应用是我们在这个技术中研究的应用,它是认知自组织网络(CAN),也就是使用用于二级用户本身之间通信的无许可频谱,用于诸如点对点内容分发,环境监控,安全性等目的,灾难恢复情景通信,军事通信等等。

设计CAN系统比CW A有更多困难,主要有两个原因。

第一是识别未使用的频谱。

在CW A中,接入点的作用是连接到互联网,因此可以使用简单的策略来推断频谱可用性,例如查询频谱调节器在其地理位置的频谱可用性或直接与主用户协商频谱可用性或一些中间频谱经纪人另一方面,在CAN中,与频谱调节器或主要用户的缺乏直接通信需要二级用户能够使用检测技术自己识别未使用的频谱。

第二个困难是辅助用户协调媒体访问目的。

在CW A中存在接入点和通常所有二级用户直接与之通信(即,网络是单跳)的事实使得直接使用集中式媒体接入控制(MAC)解决方案,如时分多址(TDMA)或正交频分多址(OFDMA)。

介绍通信网学科的英语作文English Response:The field of telecommunications encompasses the study of systems and technologies used for transmitting information over long distances. It involves various aspects of communication, including signal processing, network design, information theory, and protocol development. Telecommunication networks enable the transmission of data, voice, and video signals through different media, such as copper wires, fiber optics, wireless links, and satellites.One of the fundamental components of telecommunications is signal processing. Signal processing techniques are employed to encode, modulate, and demodulate signals to ensure their reliable transmission over communication channels. Modulation is the process of varying the characteristics of a carrier signal to represent the information-bearing signal, while demodulation recovers theoriginal signal at the receiving end.Network design plays a crucial role in optimizing the performance and reliability of telecommunication networks. It involves determining the appropriate network topology, routing algorithms, and traffic management strategies to ensure efficient and reliable transmission of data. Network designers consider factors such as bandwidth requirements, latency, and resilience to design networks that meet the specific needs of users.Information theory provides the mathematical foundation for understanding the limits and capabilities of communication systems. It establishes fundamentalprinciples for encoding and decoding information, including concepts such as entropy, redundancy, and channel capacity. Information theory enables the design of communication systems that maximize the efficiency of information transmission while minimizing errors.Protocol development is another essential aspect of telecommunications. Protocols define the rules andprocedures for communication between different devices and networks. They specify the format of data packets, the methods for exchanging data, and the mechanisms for error detection and correction. Protocols ensure interoperability between different devices and networks, allowing them to communicate effectively.中文回答:电信网络学科介绍。

Communication is an essential aspect of our daily lives,and the ability to express oneself clearly and effectively in English is crucial in the globalized world.Here are some key points to consider when writing an essay on communication in English:1.Importance of Communication:Begin your essay by discussing why communication is vital.You can mention how it is the cornerstone of relationships,both personal and professional.2.Cultural Differences:Highlight the role of cultural understanding in communication. Explain how different cultures have unique ways of expressing ideas and emotions, which can affect the clarity and effectiveness of communication.3.Verbal and Nonverbal Communication:Distinguish between verbal and nonverbal forms of communication.Verbal communication includes spoken words,while nonverbal encompasses body language,facial expressions,and tone of voice.4.Active Listening:Emphasize the importance of active listening in communication.It involves not just hearing the words but also understanding the underlying message and responding appropriately.nguage Barriers:Discuss the challenges posed by language barriers and how they can be overcome.Mention the role of translation services,bilingual education,and language learning in bridging these gaps.6.Technology and Communication:Explore how technology has transformed communication.Discuss the impact of social media,email,and instant messaging on the way we interact with one another.7.Effective Communication Skills:Provide tips for effective communication in English. This could include being clear,concise,and respectful,as well as using appropriate language and avoiding jargon.8.Workplace Communication:Discuss the importance of effective communication in the workplace.Explain how it can lead to better collaboration,increased productivity,and a positive work environment.9.Global Communication:Address the role of English as a global language in facilitating international communication.Discuss the benefits and challenges of using English as a lingua franca.10.Conclusion:Conclude your essay by summarizing the key points and reiterating the importance of effective communication in English.You may also suggest ways to improve communication skills,such as engaging in more conversations,practicing public speaking,or taking language courses.Remember to structure your essay with a clear introduction,body paragraphs that explore each point in detail,and a conclusion that wraps up your e a variety of sentence structures and vocabulary to demonstrate your proficiency in English. Additionally,proofread your work to ensure it is free of grammatical errors and typos.。

通讯领域的英语作文Title: The Evolution of Communication Technology: Connecting the World。

In the contemporary era, communication technology plays a pivotal role in shaping the way we interact, share information, and connect with others globally. From the rudimentary methods of communication to the advent of sophisticated digital platforms, the evolution of communication technology has revolutionized the world in unprecedented ways. In this essay, we will delve into the profound impact of communication technology on society and explore its transformative journey.To begin with, the emergence of language as a mode of communication laid the foundation for human interaction. Through verbal exchanges and primitive forms of writing, early civilizations were able to convey messages and preserve their history. However, the evolution of communication technology accelerated with the invention ofwriting systems, such as cuneiform and hieroglyphics, enabling the recording and dissemination of information over vast distances.The invention of the printing press in the 15th century marked a significant milestone in communication technology. Gutenberg's movable type printing press revolutionized the spread of knowledge by making books more accessible and affordable. This invention paved the way for the mass production of literature, fueling the Renaissance and the Age of Enlightenment.The telegraph, introduced in the 19th century, further transformed communication by enabling rapid long-distance transmission of messages through electrical signals. This innovation revolutionized global commerce, diplomacy, and news dissemination, shrinking the world and laying the groundwork for future advancements.The 20th century witnessed an explosion of communication technologies, beginning with the invention of the telephone by Alexander Graham Bell in 1876. Thetelephone revolutionized interpersonal communication, allowing individuals to converse in real-time across great distances. Subsequent innovations, such as radio and television, transformed mass communication, shaping public opinion and culture on a global scale.However, it was the advent of the internet in the late 20th century that truly revolutionized communication. Initially developed as a means of military communication, the internet evolved into a global network connecting billions of people worldwide. The World Wide Web, introduced in 1991 by Tim Berners-Lee, revolutionized access to information, commerce, and social interaction.The proliferation of mobile technology in the 21st century further accelerated the pace of communication evolution. Smartphones, equipped with internet connectivity and an array of communication apps, have become ubiquitous tools for staying connected in today's digital age. Social media platforms like Facebook, Twitter, and Instagram have redefined how we interact, share information, and form communities online.Moreover, the rise of artificial intelligence (AI) and machine learning has ushered in a new era of communication technology. Chatbots, virtual assistants, and language translation tools have made communication more efficient and accessible across language barriers. Additionally, advancements in augmented reality (AR) and virtual reality (VR) are transforming how we perceive and interact with digital content, further blurring the lines between physical and virtual communication.Looking ahead, the future of communication technology holds immense promise and potential. Emerging technologies such as 5G networks, blockchain, and the Internet of Things (IoT) are poised to revolutionize communication in ways we can only imagine. From autonomous vehicles to smart cities, the interconnectedness facilitated by these technologies will reshape industries, societies, and the very fabric of human interaction.In conclusion, the evolution of communication technology has been a remarkable journey, shaping the waywe connect and communicate with one another. From ancient writing systems to the internet age, each innovation has propelled humanity forward, breaking down barriers and expanding the boundaries of possibility. As we stand on the cusp of a new era of technological advancement, it is essential to harness the power of communication technology for the greater good, fostering understanding, collaboration, and progress in an increasingly interconnected world.。

通讯技术英语作文模板英文回答:Communication Technologies。

Communication technologies have revolutionized the way we live, work, and interact with the world. From the early days of the telephone and telegraph to the modern era of smartphones and the internet, communication technology has played a vital role in shaping human history.The Evolution of Communication Technologies。

The history of communication technologies can be traced back to ancient times, with the use of smoke signals, drums, and messengers. The first major breakthrough came in the19th century with the invention of the telegraph, followed by the telephone in the late 19th century. These inventions enabled communication over long distances and paved the way for the modern era of communication.In the 20th century, the development of radio, television, and satellites further expanded the reach of communication. The internet, introduced in the 1990s, has had a transformative impact on communication, providing instant and global connectivity.Types of Communication Technologies。

对移动通信专业课的英文作文Mobile communication has become an integral part of our daily lives, revolutionizing the way we interact, access information, and conduct business. As a field of study, mobile communications encompasses a vast array of technological advancements, innovative applications, and evolving industry trends. In this essay, we will delve into the significance of mobile communications as a professional discipline, exploring its key aspects, the skills and knowledge required, and the exciting career prospects it offers.At the core of mobile communications lies the seamless integration of various technologies, including wireless networks, cellular systems, and mobile devices. The rapid development of 4G and 5G networks, coupled with the widespread adoption of smartphones and tablets, has transformed the way we communicate, access information, and engage with the digital world. Mobile communication professionals play a crucial role in designing, implementing, and optimizing these complex systems, ensuring reliable and efficient connectivity for users.One of the fundamental aspects of mobile communications is the understanding of wireless network architectures. Students in this field must grasp the principles of radio frequency (RF) propagation, antenna design, and cellular network topologies. They learn to analyze and address the challenges posed by factors such as signal interference, coverage, and capacity optimization. Additionally, they delve into the intricacies of network protocols, such as GSM, CDMA, and LTE, and their role in enabling seamless voice, data, and multimedia communication.Beyond the technical foundations, mobile communications professionals must also possess a strong understanding of mobile device technologies. This includes the hardware components, operating systems, and software applications that power modern smartphones and tablets. They need to stay abreast of the latest advancements in mobile processors, memory, sensors, and display technologies, as well as the evolving user interface designs and mobile app development frameworks.Another crucial aspect of mobile communications is the study of mobile data and services. Students in this field explore the various mobile data transmission techniques, such as packet switching and circuit switching, and learn to optimize data throughput and minimize latency. They also examine the role of mobile internet protocols, such as WAP and GPRS, and their integration withtraditional internet technologies.The field of mobile communications also encompasses the study of mobile applications and services. Students delve into the development of mobile apps, exploring user experience design, cross-platform compatibility, and the integration of advanced features like location-based services, augmented reality, and mobile payments. They also learn to navigate the complex ecosystem of mobile app stores, distribution channels, and monetization strategies.In addition to the technical aspects, mobile communications professionals must also possess strong analytical and problem-solving skills. They must be adept at data analysis, network optimization, and performance monitoring to ensure the smooth operation of mobile systems. Furthermore, they need to understand the regulatory frameworks and industry standards that govern the mobile communications landscape, adapting to the ever-evolving landscape of policies and regulations.The career prospects in mobile communications are vast and diverse. Graduates can find employment in a wide range of industries, including telecommunications companies, mobile device manufacturers, software development firms, and IT consulting agencies. They may take on roles such as network engineers, mobile app developers, data analysts, project managers, and technical salesrepresentatives, contributing to the development and deployment of cutting-edge mobile technologies.Moreover, the field of mobile communications is constantly evolving, presenting professionals with opportunities for continuous learning and growth. As new technologies, such as 5G, the Internet of Things (IoT), and edge computing, continue to emerge, mobile communication experts must stay ahead of the curve, constantly updating their skills and knowledge to remain competitive in the job market.In conclusion, mobile communications is a dynamic and multifaceted field that offers a wealth of opportunities for aspiring professionals. By mastering the technical aspects of wireless networks, mobile devices, and data services, as well as developing strong analytical and problem-solving skills, students in this discipline can position themselves for rewarding careers in a rapidly advancing industry. As the world becomes increasingly interconnected and reliant on mobile technologies, the demand for skilled mobile communication professionals will only continue to grow, making it an exciting and promising career path.。

通信技术英文作文1. Communication technology has revolutionized the way we connect with others. From the invention of the telephone to the rise of social media, we now have countless ways to stay in touch.2. One of the most important aspects of communication technology is its ability to bring people together across long distances. With video calls and messaging apps, we can now talk to someone on the other side of the world as if they were right next to us.3. Another key benefit of communication technology is its role in spreading information. News can now be shared instantly, allowing people to stay informed about what's happening in the world around them.4. Communication technology has also transformed the way we do business. With email, online meetings, andproject management tools, we can collaborate withcolleagues from anywhere, making it easier to work remotely.5. However, it's important to remember that communication technology also has its drawbacks. With the constant barrage of notifications and messages, it can be difficult to disconnect and have some time for ourselves.6. Additionally, the rise of social media has brought about new challenges, such as cyberbullying and the spreadof misinformation. It's crucial to use communication technology responsibly and be aware of its potential negative impact.7. Looking to the future, communication technology will continue to evolve and shape the way we interact with the world. Whether it's through virtual reality, artificial intelligence, or other innovations, the possibilities are endless.。

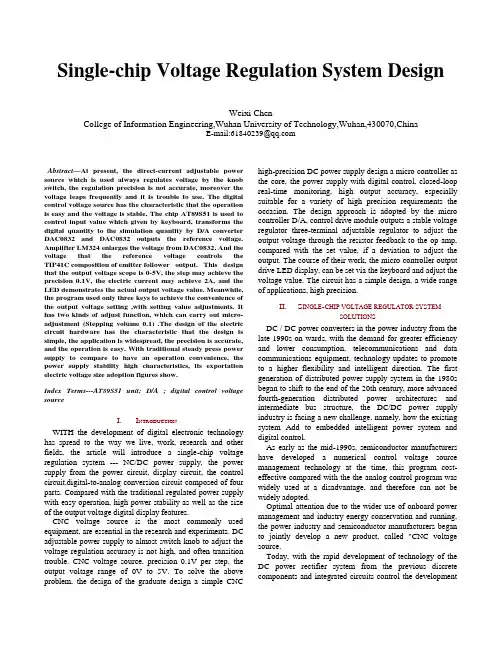

Single-chip Voltage Regulation System DesignWeixi ChenCollege of Information Engineering,Wuhan University of Technology,Wuhan,430070,ChinaE-mail:61840239@Abstract—At present, the direct-current adjustable power source which is used always regulates voltage by the knob switch, the regulation precision is not accurate, moreover the voltage leaps frequently and it is trouble to use. The digital control voltage source has the characteristic that the operation is easy and the voltage is stable. The chip AT89S51 is used to control input value which given by keyboard, transforms the digital quantity to the simulation quantity by D/A converter DAC0832 and DAC0832 outputs the reference voltage. Amplifier LM324 enlarges the voltage from DAC0832. And the voltage that the reference voltage controls the TIP41C composition of emitter follower output. This design that the output voltage scope is 0-5V, the step may achieve the precision 0.1V, the electric current may achieve 2A, and the LED demonstrates the actual output voltage value. Meanwhile, the program used only three keys to achieve the convenience of the output voltage setting ,with setting value adjustments. It has two kinds of adjust function, which can carry out micro-adjustment (Stepping volume 0.1) .The design of the electric circuit hardware has the characteristic that the design is simple, the application is widespread, the precision is accurate, and the operation is easy. With traditional steady press power supply to compare to have an operation convenience, the power supply stability high characteristics, its exportation electric voltage size adoption figures show.Index Terms---AT89S51 unit; D/A ; digital control voltage sourceI.I NTRODUCTIONWITH the development of digital electronic technology has spread to the way we live, work, research and other fields, the article will introduce a single-chip voltage regulation system --- NC/DC power supply, the power supply from the power circuit, display circuit, the control circuit,digital-to-analog conversion circuit composed of four parts. Compared with the traditional regulated power supply with easy operation, high power stability as well as the size of the output voltage digital display features.CNC voltage source is the most commonly used equipment, are essential in the research and experiments. DC adjustable power supply to almost switch knob to adjust the voltage regulation accuracy is not high, and often transition trouble. CNC voltage source, precision 0.1V per step, the output voltage range of 0V to 5V. To solve the above problem, the design of the graduate design a simple CNC high-precision DC power supply design a micro controller as the core, the power supply with digital control, closed-loop real-time monitoring, high output accuracy, especially suitable for a variety of high precision requirements the occasion. The design approach is adopted by the micro controller D/A, control drive module outputs a stable voltage regulator three-terminal adjustable regulator to adjust the output voltage through the resistor feedback to the op amp, compared with the set value, if a deviation to adjust the output. The course of their work, the micro controller output drive LED display, can be set via the keyboard and adjust the voltage value. The circuit has a simple design, a wide range of applications, high precision.II.S INGLE-CHIP VOLTAGE REGULATOR SYSTEMSOLUTIONSDC / DC power converters in the power industry from the late 1990s on wards, with the demand for greater efficiency and lower consumption, telecommunications and data communications equipment, technology updates to promote to a higher flexibility and intelligent direction. The first generation of distributed power supply system in the 1980s began to shift to the end of the 20th century, more advanced fourth-generation distributed power architectures and intermediate bus structure, the DC/DC power supply industry is facing a new challenge, namely, how the existing system Add to embedded intelligent power system and digital control.As early as the mid-1990s, semiconductor manufacturers have developed a numerical control voltage source management technology at the time, this program cost-effective compared with the the analog control program was widely used at a disadvantage, and therefore can not be widely adopted.Optimal attention due to the wider use of onboard power management and industry energy conservation and running, the power industry and semiconductor manufacturers began to jointly develop a new product, called "CNC voltage source.Today, with the rapid development of technology of the DC power rectifier system from the previous discrete components and integrated circuits control the developmentcomputer control, so that the DC power supply intelligent, telemetry, remote, remote control three remote functions, the basic realization of the DC power supply unattended.With the development of digital electronic technology has spread to the way we live, work, research and other fields, the article will introduce a single-chip voltage regulation system --- NC DC power supply, the power supply from the power circuit, display circuit, the control circuit, digital-to-analog conversion circuit composed of four parts. Compared with the traditional regulated power supply with easy operation, high power stability as well as the size of the output voltage digital display features.CNC voltage source is the most commonly used equipment, are essential in the research and experiments. DC adjustable power supply to almost switch knob to adjust the voltage regulation accuracy is not high, and often transition trouble. CNC voltage source, precision 0.1V per step, the output voltage range of 0V to 5V.This design uses AT89S51 control unit, and D/A converter DAC0832 is connected to the data interface, and the DAC in a single buffer mode. The DAC 8 pin reference voltage, reference voltage of 5V. Therefore, in the resolution of the DAC output voltage is 5V/256 = 0.02V, that the DACinput data terminal of each additional 1, the voltage is increased to 0.02V. Magnification the LM324 input terminal of the DAC voltage output end of the amplifier, the amplifier 5. Output to the voltage of the emitter follower resolution = 0.02V ×5 = 0.1V. Therefore, when the the the AT89S51 output data increases by 1 when the final output voltage increase 0.1V when the adjustment voltage may increase or decrease the voltage amplitude of 0.1V each.Of the circuit design of the three buttons A, B and C, A voltage + B voltage -, C key is used to reset of the micro controller control unit. The principle of the main circuit is controlled by AT89S51 DAC output voltage magnitude, change the LM324 the output voltage i.e. the output voltage of the emitter follower TIP41C, the whole chip is the final output voltage of the voltage regulation system.III.S INGLE-CHIP VOLTAGE REGULATION SYSTEMHARDWARE CIRCUIT DESIGNA.The micro controller AT89C52 and its clock circuitAT89C52 is a low-voltage, high-performance CMOS 8-bit micro controller, tablets containing 8K bytes of read-only can be repeatedly erased Flash program memory and 256 bytes of random access data memory (RAM), high-density device uses ATMEL Corporation non-volatile memory technology to produce compatible with the standard MCS-51 instruction set, on-chip built-purpose 8-bit central processor and Flash memory cell AT89C52 micro controller has a wide range of applications in the electronics industry.The clock circuit for generating a the the micro controller operating clock signal, while the timing of the study is the instruction is executed between the respective signals. Micro controller itself as a complex synchronous sequential circuits, in order to ensure the realization of synchronization circuit should only clock signal under the control of strict chronological.B. D / A transform circuitDAC0832 8-resolution D/A converter chip. Is fully compatible with the microprocessor. DA chip with its low price, the interface is simple, easy conversion control, has been widely used in the SCM application system. D/A converter by the 8-bit input latch, an 8-bit DAC register, 8 D / A converter circuit and the switching control circuit structure.The DAC032 has three kinds of work:Single buffering, Double buffering and Direct way.This design uses a Single buffer.\Fig. 1. System hardware circuit\Fig. 3 Voltage adjustment circuitC. Voltage adjustment circuitThis part of the design works as follows: the previous step reverse voltage of the output circuit draw a line on an op amp LM324 zoom previous LM324 output voltage Vout1 negative voltage, so that part connected to the LM324 as a negative feed back the reverse amplification circuit on the output voltage amplification, and then adjust the voltage amplification factor of the operational amplifier through an adjustable slide rheostat RV2.Next, the output terminal of the op-amp LM324 through a resistor to the base of the transistor TIP41C TIP41C by changing the output voltage of LM324 i.e. the output voltage of the emitter follower, which is the final output voltage of the voltage regulation system of the whole chip, the Vout2 output.D. Chip reset circuit and keyboard circuitCircuit to ensure that the computer system is stable and reliable work, reset circuit is an essential part of the first function of the reset circuit is a power-on reset. General microcomputer circuit to work power supply of 5V ± 5%, that is 4.75 to 5.25V. Microcomputer circuit is sequential digital circuit, it needs a stable clock signal, so when the power is turned on only when VCC exceeds 4.75V below 5.25V and the crystal oscillator is stable work, the reset signal was only removal, computer circuit begins normal working.The keyboard interface usually consists of both hardware and software. The hardware is the structure of the keyboard and its connection to the host; software refers to the identification and analysis of the operation of the keyboard, the keyboard management program.When no key is pressed, the MCU P1.0 and P1.1 is high. When a key is pressed, the corresponding port of themicro controllerline connected through the key groundpulled into low, other port line level unchanged. Therefore, by detection I / O port line level status, you can determine which key was pressed on the keyboard.E. Digital display circuitOften referred to as the LED display is composed of seven light emitting diode, and therefore also referred to as the seven-segment LED display, In addition, the display there is a dot-type light emitting diode (in the figure expressed in dp) for displaying decimal point. By their different combinationsof the 7-segment light emitting diode and a variety of numbers, letters or other symbols can be displayed. There are two light-emitting diode LED display connection method :Common anode connection and Common cathode connection.In this design, we have adopted a common cathode LED TrinityF. power supply circuitIn this design, because it will give a lot of different chip supply, so home-made power. In this design, I designed a plus or minus 12 volts and ± 5V power output. Mainly made of 7800 series (output positive voltage) and 7900 series (negative output voltage) power supply circuit. Linear power supply from 12V transformer full-wave rectifier, capacitor rectifier filter, three-terminal regulator The 7812,7912 regulator chip AT89S52, DAC0832, LM324, digital tube voltage.Fig. 2 D / A transform circuit\Fig. 4 Voltage adjustment circuitIV. S INGLE -CHIP VOLTAGE REGULATION SYSTEMSOFTWARE DESIGN The working process of the main program is: After system initialization, the default output voltage of 0V, digital tube display 0.0V; Scan A, B key, when the A or B key is pressed, the program jumps to the key processing subroutine; after key processing subroutine processing, set the corresponding flag bit and deal with the value of the corresponding register; then sent back to the main program, depending on the flag corresponding digital DAC0832, and the corresponding data into the display buffer, and finally display the output voltage of the power supply; program continues to scan the A, B key, recycling the previous steps. The software is designed mainly to complete the three functions: · A button control voltage increases and B buttoncontrol voltage to reduce· The voltage set to the DA, DA operations. ·Set the voltage to the LED digital tube.Fig. 5 Single-chip voltage regulation system software main programR EFERENCES[1] Behzad Razavi.Design of Analog CMOS Integrated Circuits[M]. .2001[2] JLee Jri.High-Speed Circuit Designs for Transmittersin Broad-bandData Links. IEEE Journal of Solid-State Circuits[J]. 2006[3] Adrian Maxim,Ramin K.Poorfard,Richard A.Johnson,et al.A FullyIntegrated 0.13-μm CMOS Digital Low -IF DBS Satellite Tuner Using a Ring Oscillator-Based Frequency Synthesizer. IEEE Journal of Solid State Circuits. 2007[4] George Lee,Karina Ng,Edmond Kwang.Design of ring oscillatorbased voltage controlled oscillator. Project Final Report[R]. 2005 [5] V. Yu. Teplov,A. V. Anisimov. Thermostatting System Using aSingle-Chip Microcomputer and Thermoelectric Modules Based on the Peltier Effect[J] ,2002 [6] 李群芳.张士军.黄建.单片机型计算机与接口技术.北京电子工业出版社.2005[7] William H.Hayt,Jr.Engineering Circuit Analysis. 北京电子工业出版社.2006[8] 李光飞.51系列单片机设计实例. 北京:北京航空航天大学出版社,2003.[9] Meehan Joanne,Muir Lindsey.SCM in Merseyside SMEs:Benefitsand barriers[J].. TQM Journal. 2008 [10] 高伟. 单片机AT89单片机原理及应用,国防工业出版社,2008。

毕业设计(论文)外文文献翻译文献、资料中文题目:无线通信基础文献、资料英文题目:文献、资料来源:文献、资料发表(出版)日期:院(部):专业:通信工程班级:姓名:学号:指导教师:翻译日期: 2017.02.14毕业设计(论文)外文资料翻译外文出处无线通信基础(Fundamentals ofwireless communications by DavidTse)附件:1.外文资料翻译译文;2.外文原文附件1:外文资料翻译译文7.mimo:空间多路复用与信道建模本书我们已经看到多天线在无线通信中的几种不同应用。

在第3章中,多天线用于提供分集增益,增益无线链路的可靠性,并同时研究了接受分解和发射分解,而且,接受天线还能提供功率增益。

在第5章中,我们看到了如果发射机已知信道,那么多采用多幅发射天线通过发射波束成形还可以提供功率增益。

在第6章中,多副发射天线用于生产信道波动,满足机会通信技术的需要,改方案可以解释为机会波束成形,同时也能够提供功率增益。

章以及接下来的几章将研究一种利用多天线的新方法。

我们将会看到在合适的信道衰落条件下,同时采用多幅发射天线和多幅接收天线可以提供用于通信的额外的空间维数并产生自由度增益,利用这些额外的自由度可以将若干数据流在空间上多路复用至MIMO信道中,从而带来容量的增加:采用n副发射天线和接受天线的这类MIMO信道的容量正比于n。

过去一度认为在基站采用多幅天线的多址接入系统允许若干个用户同时与基站通信,多幅天线可以实现不同用户信号的空间隔离。

20世纪90年代中期,研究人员发现采用多幅发射天线和接收天线的点对点信道也会出现类似的效应,即使当发射天线相距不远时也是如此。

只要散射环境足够丰富,使得接受天线能够将来自不同发射天线的信号分离开,该结论就成立。

我们已经了解到了机会通信技术如何利用信道衰落,本章还会看到信道衰落对通信有益的另一例子。

将机会通信与MIMO技术提供的性能增益的本质进行比较和对比是非常的有远见的。

通信原理论文(中英文版)Optimized Pulse Shaping for Intra-channelNonlinearities Mitigation in a 10 Gbaud Dual-Polarization 16-QAM SystemBeno?t Chatelain1, Charles Laperle2, Kim Roberts2, Xian Xu1, Mathieu Chagnon1, Andrzej Borowiec2, Fran?ois Gagnon3, John C. Cartledge4, and David V. Plant11McGill University, Montreal, Quebec, Canada, H3A 2A7 2Ciena Corporation, Ottawa, Ontario, Canada, K2H 8E93école de technologie supérieure, Montreal, Quebec, Canada, H3C 1K34Queen’s University, Kingston, Ontario, Canada, K7L3N6 Email: benoit.chatelain@mail.mcgill.caAbstract: An optimized pulse shape is shown to reduce intra-channel nonlinear effects in a 10 Gbaud dual-polarization 16-QAM EDFA-amplified system without optical dispersion compensation.OCIS codes: (060.2330) Fiber optics communications; (060.4080) Modulation1. IntroductionIntra-channel nonlinear distortion is an important source of signal degradation in opticalcommunication systems using advanced modulation formats such as quadrature amplitude modulation (QAM). Its main impact is to reduce the maximal powerthat can be launched into the fiber, thereby limiting optical signal-to-noise ratio (OSNR) levels at the receiver, reducing system margins and reducing the maximum propagation distance that can be achieved. In this paper, thenonlinear tolerance of an optimized pulse and a root-raised cosine (RRC) pulse is compared in terms of bit error rate (BER) performance, for varying propagation distances and launch powers. Experimental results show that the optimized pulse considerably reduces intra-channel nonlinear effects in a long haul, 10 Gbaud dual-polarization (DP) 16-QAM system relying on erbium-doped fiber amplifiers (EDFAs) and G.652 fiber (no optical dispersion compensation).The improved nonlinear tolerance of the return-to-zero (RZ) pulse shape was recently highlighted in [1], for a 112 Gb/s DP-quadrature phase shift keying (QPSK) system without optical dispersion compensation. Comparing the RZ pulse to the non return-to-zero (NRZ) pulse, the authors reported an increase in single channel maximum propagation distance of 18%. However, the improved nonlinear tolerance achieved using the RZ pulse comes at the expense of increased spectral content. For instance, the bandwidth of a 50% RZ pulse is twice the bandwidth of the NRZ pulse or the RRC pulse with a roll-off factor (α) of 1. The use of a RZ pulse thus reduces spectral efficiency by a factor of two, and for a system using digital signal processing at the transmitter and receiver, at the Nyquist rate, it doubles the required bandwidth and sampling frequency of the digital-to-analog converters (DACs) and analog-to-digital converters (ADCs).(a)(b)Figure 1. Impulse (a) and frequency (b) responses of the RRC and optimized pulses.In comparison to the RRC pulse, the optimized pulse shape presented in [2] was shown to improvethe nonlinear performance of DP-QPSK systems without optical dispersion compensation and to increase the maximum transmission distance by as much as 22%. The specialized pulse was obtained by numerical optimization, with the primary objective formulated to reduce its width, but constrained to have a bandwidth equal to the bandwidth of a NRZ or RRC pulse (α = 1). Therefore,the optimized pulse can be used without penalizing spectral efficiency and without using higher speed DACs and ADCs. Fig. 1 exhibits the time and frequency characteristics of the optimized and RRC pulses. It can be seen that the optimized pulse is narrower than the RRC pulse with α = 1, and that its first-null bandwidth is equal to the baud rate. It is also apparent that the reduced width of the optimized pulse translates in higher energy content for frequencies between 6 GHz and 10 GHz. Through dispersion, the higher energy frequencycomponents produce a propagating pulse and a propagating waveformthat is more broadened, with lower peak power excursions. Since intra-channel nonlinear distortion is proportional to peak power, the optimized pulse makes the system more tolerant to nonlinear effects. In this work and as in [2?5], the RRC pulse is used as the reference pulse for its ability to minimizepulse-induced intersymbol interference (ISI) and to minimize out-of-band power.2. Experimental SetupFig. 2 illustrates the experimental setup. The symbol sources consist of random symbol sequences of length 214 and were followed by pulse shapingfinite impulse response (FIR) filters. DACs with 6-bit resolution drive thein-phase-quadrature (I-Q) modulators associated with the two polarizations. The emitting wavelength was set to 1547.715 nm. A polarization scrambler (PS) was inserted after the polarization beam combiner (PBC) in order to randomly rotate the polarization state. A fiber link consisting of 15 spans of 80 km G.652 fiber was used, together with EDFAs at each span. At the receiver, a noise source was used to adjust the OSNR. The optical spectrum analyzer (OSA) served the purposes of measuring the OSNR. A coherent front-end integrates polarization beam splitters, optical hybrids, a local oscillator and photodetectors [6]. It provides four signals corresponding to the in-phase and quadrature components of the two polarizations. These baseband signals were sampled using a 50 GSa/s oscilloscope with 8-bit ADCs and post-processed in a personal computer. The linewidth of the transmitter and receiver lasers was 100 kHz, and their frequency offset was below 200 MHz. The same clockreference was used for the DACs and ADCs. The receiver signal processingfunctions include matched filtering and chromatic dispersion compensation (CD-1) by FIR filters, polarization recovery by a 13-tap fractionally spaced (T/2) butterfly equalizer (EQ), carrier offset removal and carrier phase recovery by a second order phase lock loop (PLL) and finally, detection. The constant modulus algorithm (CMA) is used for the equalizer coefficients pre-convergence. Once the signal is recovered, the system switches to a decision-directed modulus algorithm (DDMA) [7]. Two symbol pattern periods, totaling 215 symbols for each polarization, were used to produce BER statistics.In what follows, the system performance is studied using either the RRC pulse or the optimized pulse presented in Fig. 1 as transmit FIR filters and receive matched filters.Figure 2. Experimental setup.3. Results and DiscussionFig. 3 displays the electrical eye diagrams of the signal in-phase component taken at the transmitter, after the FIR pulse shaping filter. The inner eye openings of the optimized 16-QAM sequence eye diagram are reduced compare to those in the eye diagram obtained using the RRC pulse, indicating, as mentioned in [2], that the optimized pulse may be more sensitive to timing jitter. Fig. 3 (b) further shows that the eye diagram obtained with the optimized pulse is very similar to the eye diagram that would be obtainedusing an RZ pulse, and that the optimized pulse sequence returns close to azero level between each symbol period. Since the RRC and the optimized pulses are designed to be used as matched filter, it is expected to visualize on the eye diagrams at the transmitter a certain amount of ISI. The RRC and optimized pulses produce a filtered sequence with zero pulse-induced ISI only at the receiver, after matched filtering.Fig. 4 (a) reports the measured BER in a back-to-back configuration for a system using RRC filters and for a system using optimized filters. The linear performance of the RRC and optimized pulses is very similar and for the considered range of OSNR, the minimal and maximal penalty is 2.5 dB and 6.5 dB, respectively. Fig. 4 (b) and (c) show propagation results for 800 km and for 1200 km. At 800 km and considering a BER threshold of 8×10-3, the optimized pulse reduces the OSNR penalty by 0.6 dB and 2.8 dB, for launch powers of �C2 dBm and 0 dBm, respectively. At 1200 km and for a launch power of �C2 dBm an improvement of 1.2 dB is observed. At 1200 km and for a launch power of 0 dBm, the system with optimized pulse shaping almost reaches the BER threshold,while the system using RRC pulses is limited to a BER of 1.8×10-2. At this level, the optimized pulse outperforms the RRC pulse by 4.3 dB. It should be noted that the introduction of soft-decision forward error correction (FEC) [8] would be required to be able to operate at the considered BER threshold.感谢您的阅读,祝您生活愉快。

通信工程英语论文3800字_通信工程英语毕业论文范文模板通信工程英语论文3800字(一):关于通信工程专业科技英语教学探析论文论文摘要:结合通信工程专业的特点及自身教学实践,从教学目标、教学内容、教学模式及重视程度几方面分析现有教学中存在的问题,探讨科技英语课程的教学改革方法,实践证明改革效果较好。

论文关键词:科技英语;通信工程;教学改革通信技术和通信产业是20世纪80年代以来发展最快的领域之一,新技术的更新非常快。

近年来,三网融合、物联网、云计算、移动互联网、智能终端、无线射频识别、td—lte等新技术不断涌现。

其中,除td—lte由我国主导并拥有自主知识产权外,其他技术基本由国外垄断。

要提高国际竞争力就要提高创新水平,必须跟踪、掌握国外先进技术,在此基础上才有可能开发更多我国自主知识产权的核心技术。

这对高校通信专业人才的培养提出了更高的要求:不仅要具有扎实的专业基础,同时要具有检索、跟踪、掌握国外新技术、新理论的能力。

科技英语作为通信专业课程体系的一部分,是实现该目标至关重要的一个环节。

如何使科技英语的教学跟上国家、企业对通信专业人才的需求是值得思考的问题。

本文结合教学实践分析通信工程专业科技英语教学现状,针对存在的问题,提出了一些可行的教学改革方法。

一、教学现状分析1。

教学目标模糊科技英语是通信工程本科专业大学四年级开设的一门专业选修课,其教学目标为通过课文的精读,掌握基本的通信专业的英语词汇、科技英语的语言特点、句子特点和基本翻译技巧。

具备基本的查阅、翻译、理解本专业英语文献的能力,能够用英文进行基本的专业表达。

同时,也通过课文学习扩大学生的专业知识面,了解通信的基本技术、最新动向及新的英文专业术语。

这一目标对不同层次的高校没有进行明确的区分。

以应用型人才为培养目标的地方性本科、高职院校与以研究型人才为培养目标的重点高校的教学目标目差别不大,普遍存在各学校教学内容与教学模式千篇一律,互相之间照搬套用的现象。

GPS in the grain plots to forestry (grass) engineering applicationIn 2001, the state forestry administration promulgated for implementation the state forestry administration on afforestation quality accidents of administrative responsibility system of regulations, afforestation quality accidents of 3 standards, the foundation of a content is ZaoLinDe area, at the same time, the provisions on the quantity and quality of the false forestation project legal person, unit and the legal representative, the person-in-charge directly responsible and other personnel directly responsible shall be given administrative sanctions according to law. In addition, intensivism from the grain plots to forestry (grass) engineering in recent years, the afforestation in each check and accept, acceptance of the key is one of the most important content is the area ZaoLinDe verification issues. Therefore, in the forestry market practice correctly to measure is the basis of all forestation practice.1 the GPS navigators profileGPS Positioning System is Global, namely the Global Positioning System, it is the space station, by users and the three parts. According to the user's work, the influence of regional satellite state of the satellite distribution situation, GPS positioning precision machine, namely 15m less than hm2 0.023 area. GPS positioning error mainly comes from star alex error, satellite receiver error distribution and the three parts, in the correct orientation, under the situation of the error in LuoPanYi with far less node board quadrature instrument error of calculating area.2 the current situation in huzhuIn the forestry production practice needs a lot of work, as measured ZaoLinDe investigation and survey, forest road.based etc, involves the measurement technology and content is very wide. But the current situation in huzhu measurement, one is to measure the work, such as in the grain plots to forestry (grass) engineering afforestation design process, scientific and technological personnel outside work assignments must never take on some related measuring instrument measuring data by experience, even for ZaoLinDe area is roughly estimated, Second is the existing measuring instrument less and humble, currently existing instruments are mainly huzhu PiChe, level, LuoPanYi, handheld altimeter, etc. Three is scientific and technical personnel in the knowledge of measurement, can correctly use measuring instruments are measured by the existing GPS navigators area is a lot.3 the current methods of artificial measurementThe content of the involved in various forest is quite widespread, survey, design and planning of the correctness of data directly influences the precision of planning and design. The method of measuring area: one is the plan or topographic map measurement area, such as graphic method, the quadrature instrument, network, electronic instrument; quadrature etc. 2 in the field measurement instrument, such as using method, wire etc. But through years of practice, the present method widely used in huzhu outlets, on-the-spot quadrature method etc exist great errors,especially in the topographic map criticize the area after the general error rate reached more than 15%, mainly from error topographic map scale, criticize error caused by excessive error and calculation error. On-the-spot quadrature method mainly from the error estimation terrain and terrain on the error caused by different shapes. With LuoPanYi Settings for closed wires, although high precision of law, but ZaoLinDe area of waste hillsides, large amounts of time, and low working efficiency. GPS navigators applications for new vitality into forestry measurement.4 in the grain plots to forestry (grass) engineering measurement adviceThe grain plots to forestry (grass) for verification of engineering problems, Suggestions of scientific and technical personnel in the homework carefully to the attitude of the assignments, outside the instrument must be in as far as possible, restored in map with surrounding barren hills, waste slope area with GPS navigators measurements.5 GPS navigators purchase and use of attentionGPS navigators two big main function is positioning and navigation, presently available on the purchase of GPS navigators basically has two functions, but the navigator varieties have the auxiliary function are different. If the company GPS315 Magellan GPS320 / o area with the navigator type Garmin production function, GPS12C/GPS12 x LC type navigators without area function. Therefore, in the choose and buy of forestry production practice of GPS navigators when required, must pay attention to the auxiliary function navigator. GPS315 navigators in 12 main picture, in the forestry area is measured only three pictures can be initialized, therefore in the picture will need not closed. In the initialization, must pay attention to the choice of area and the correctness of the longitude, to ensure the positioning of the fast and accurate. When the navigators "satellite" condition, should pay attention to when the screen is a satellite signal indications of selected location navigator began. When the navigator in "pictures", to place wait patiently until after completely correct orientation, can enter "track", general picture 4 ~ 6min positioning need time 10min, if not more, to initialize or change some parameters Settings. Judging from the correct orientation, except the latitude and longitude and altitude of judgment, still can use to judge the value orientation heading the correctness of the course is to exercise the speed of direction, it is for the Angle of 0 °, north, east is clockwise 90 °, ZhengXi for 270 °, the size of the numerical value in north for judging according to judge whether the correct positioning. Data is a variable data, when the longitude and altitude of floating in 2 ~ 3m, estimate error in 20m when can enter "within the picture." track When positioning in measurement, should pay attention to when the dot, line boundary between two and optional, curve more dense at designated points, and will try to set in border, obvious turning point for the first began to do so as to track, closed, According to the measured at the area of chosen by rod, after the end of the area to be converted to ha. Square在201年国家林业局颁布实施了《国家林业局关于造林质量事故行政责任追究制度的规定》,就造林质量事故划分的3个标准来看,最基础的一项内容是造林地面积,同时《规定》对虚报造林数量和质量的,将对项目法人单位和法人代表、直接负责的主管人员和其他直接责任人员,依法给予行政处分。

The Evolution and Impact of ModernCommunication TechnologiesIn the fast-paced world of today, communication technologies have transformed the way we interact, learn, and conduct business. The evolution of these technologies, from the early days of telegraph and radio to the current era of smartphones and the internet, has been nothing short of remarkable. The profound impact of these advancements in communication has reshaped societies, economies, and cultures across the globe.The advent of the telegraph in the 19th century marked a significant milestone in the history of communication. This invention allowed messages to be transmitted over long distances almost instantaneously, revolutionizing the way people stayed connected. It facilitated the exchange of critical information in real-time, enabling fasterdecision-making and enhancing the efficiency of various industries.The subsequent invention of the radio further expanded the horizons of communication. Radio broadcasts enabled the dissemination of news, entertainment, and educationalcontent to a wide audience. This medium not only provided a platform for entertainment but also served as a powerful tool for social and political mobilization.The 20th century saw the emergence of television, which further enhanced the visual and auditory experience of communication. Television brought people closer to events happening across the world, making them feel more connected and engaged. It became a household fixture, shapingpeople's entertainment preferences and cultural identities. However, the real revolution in communication began with the advent of the internet in the late 20th century. The internet has completely transformed the way we communicate, learn, and interact. It has打破了地理和时间的限制,允许人们在全球范围内即时交换信息和想法。

通信英语作文Title: The Evolution of Communication: Embracing English as a Lingua Franca。

Communication is the cornerstone of human interaction, serving as the conduit for the exchange of ideas, emotions, and information. In today's interconnected world, mastering English as a lingua franca has become increasingly essential. This essay explores the significance of English in communication and its evolution in various spheres of life.Firstly, English has emerged as the global language of business. In an era of globalization, companies operate across borders, necessitating effective communication among diverse teams and stakeholders. English facilitates seamless collaboration, enabling organizations to transcend linguistic barriers and reach a broader audience. Whetherit's negotiating deals, drafting contracts, or delivering presentations, proficiency in English enhances one'sprofessional competence and marketability.Moreover, English plays a pivotal role in academia and research. As the language of scholarly discourse, it enables scholars from different countries to share their findings, collaborate on projects, and contribute to the advancement of knowledge. Academic journals, conferences, and publications predominantly use English as the medium of communication, ensuring accessibility and dissemination of research on a global scale. By embracing English, researchers can engage with a broader community, fostering innovation and intellectual exchange.In addition, English serves as the language of technology and innovation. From software programming to digital marketing, proficiency in English is indispensable for navigating the digital landscape. The internet, often dubbed the "lingua franca of the digital age," predominantly operates in English, with a vast majority of online content available in the language. Command over English empowers individuals to leverage technology, access online resources, and participate in the digital economy,thereby bridging the digital divide and fostering digital inclusion.Furthermore, English facilitates cultural exchange and mutual understanding. Through literature, films, music, and art, English serves as a window to diverse cultures and perspectives. By engaging with English-language media, individuals gain insights into different societies, values, and traditions, promoting empathy, tolerance, and global citizenship. Additionally, proficiency in English enables cross-cultural communication and fosters meaningful connections with people from around the world, enriching personal experiences and expanding horizons.However, the prevalence of English as a lingua franca also raises concerns about linguistic diversity andcultural hegemony. While English proficiency offers numerous benefits, it can inadvertently marginalize non-native speakers and undermine indigenous languages. Efforts to promote multilingualism and preserve linguistic heritage are crucial for safeguarding cultural diversity and ensuring inclusive communication.In conclusion, English has emerged as the lingua franca of the modern world, permeating various aspects of society, including business, academia, technology, and culture. Mastery of English empowers individuals to navigate the complexities of a globalized world, fostering collaboration, innovation, and mutual understanding. However, it is imperative to recognize the importance of linguistic diversity and promote inclusive communication practicesthat respect and celebrate all languages and cultures. By embracing English as a tool for communication while valuing linguistic plurality, we can forge a more connected, inclusive, and harmonious global community.。

外文翻译(原文) 1 The General Situation of AT89C51 The AT89C51 is a low-power, high-performance CMOS 8-bit microcomputer with 4K bytes of Flash Programmable and Erasable Read Only Memory (PEROM) and 128 bytes RAM. The device is manufactured using Atmel’s high density nonvolatile memory technology and is compatible with the industry standard MCS-51™ instruction set and pin out. The chip combines a versatile 8-bit CPU with Flash on a monolithic chip; the Atmel AT89C51 is a powerful microcomputer which provides a highly flexible and cost effective solution to many embedded control applications. Features: • Compatible with MCS-51™ Products • 4K Bytes of In-System Reprogrammable Flash Memory • Endurance: 1,000 Write/Erase Cycles • Fully Static Operation: 0 Hz to 24 MHz • Three-Level Program Memory Lock • 128 x 8-Bit Internal RAM • 32 Programmable I/O Lines • Two 16-Bit Timer/Counters • Six Interrupt Sources • Programmable Serial Channel • Low Power Idle and Power Down Modes The AT89C51 provides the following standard features: 4K bytes of Flash, 128 bytes of RAM, 32 I/O lines, two 16-bit timer/counters, a five vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator and clock circuitry. In addition, the AT89C51 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. 外文翻译(原文) 2 The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt system to continue functioning. The Power Down Mode saves the RAM contents but freezes the oscillator disabling all other chip functions until the next hardware reset. Block Diagram

Pin Description: VCC Supply voltage. GND Ground. Port 0:Port 0 is an 8-bit open drain bidirectional I/O port. As an output port each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high impedance inputs. (Sink/flow) Port 0 may also be configured to be the multiplexed low order address/data bus during accesses to external program and data memory. In this mode P0 has 外文翻译(原文) 3 internal pull-ups. Port 0 also receives the code bytes during Flash programming, and outputs the code bytes during program verification. External pull-ups are required during program verification. Port 1:Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. Port 1 also receives the low-order address bytes during Flash programming and verification. Port 2:Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that uses 16-bit addresses (MOVX @ DPTR). In this application it uses strong internal pull-ups when emitting 1s. During accesses to external data memories that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register. Port 2 also receives the high-order address bits and some control signals during Flash programming and verification. Port 3:Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL) because of the pull-ups. 外文翻译(原文) 4 Port 3 also serves the functions of various special features of the AT89C51 as listed below:

Port 3 also receives some control signals for Flash programming and verification. RST:Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device. ALE/PROG:Address Latch Enable output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming. In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory. If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode. PSEN:Program Store Enable is the read strobe to external program memory. When the AT89C51 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.