Cortex-M系列

M0:

Cortex-M0是目前最小的ARM处理器,该处理器的芯片面积非常小,能耗极低,且编程所需的代码占用量很少,这就使得开发人员可以直接跳过16位系统,以接近8 位系统的成本开销获取32 位系统的性能。Cortex-M0 处理器超低的门数开销,使得它可以用在仿真和数模混合设备中。

M0+:

以Cortex-M0 处理器为基础,保留了全部指令集和数据兼容性,同时进一步降低了能耗,提高了性能。2级流水线,性能效率可达1.08 DMIPS/MHz。

M1:

第一个专为FPGA 中的实现设计的ARM 处理器。Cortex-M1 处理器面向所有主要FPGA 设备并包括对领先的FPGA 综合工具的支持,允许设计者为每个项目选择最佳实现。

M3:

适用于具有较高确定性的实时应用,它经过专门开发,可使合作伙伴针对广泛的设备(包括微控制器、汽车车身系统、工业控制系统以及无线网络和传感器)开发高性能低成本平台。此处理器具有出色的计算性能以及对事件的优异系统响应能力,同时可应实际中对低动态和静态功率需求的挑战。

M4:

由ARM 专门开发的最新嵌入式处理器,用以满足需要有效且易于使用的控制和信号处理功能混合的数字信号控制市场。

M7:

在ARM Cortex-M 处理器系列中,Cortex-M7 的性能最为出色。它拥有六级超标量流水线、灵活的系统和存接口(包括AXI 和AHB)、缓存(Cache)以及高度耦合存(TCM),为MCU 提供出色的整数、浮点和DSP 性能。

互联:64位AMBA4 AXI, AHB外设端口(64MB 到512MB)

指令缓存:0 到64kB,双路组相联,带有可选ECC

数据缓存:0 到64kB,四路组相联,带有可选ECC

指令TCM:0 到16MB,带有可选ECC

数据TCM:0 到16MB,带有可选ECC

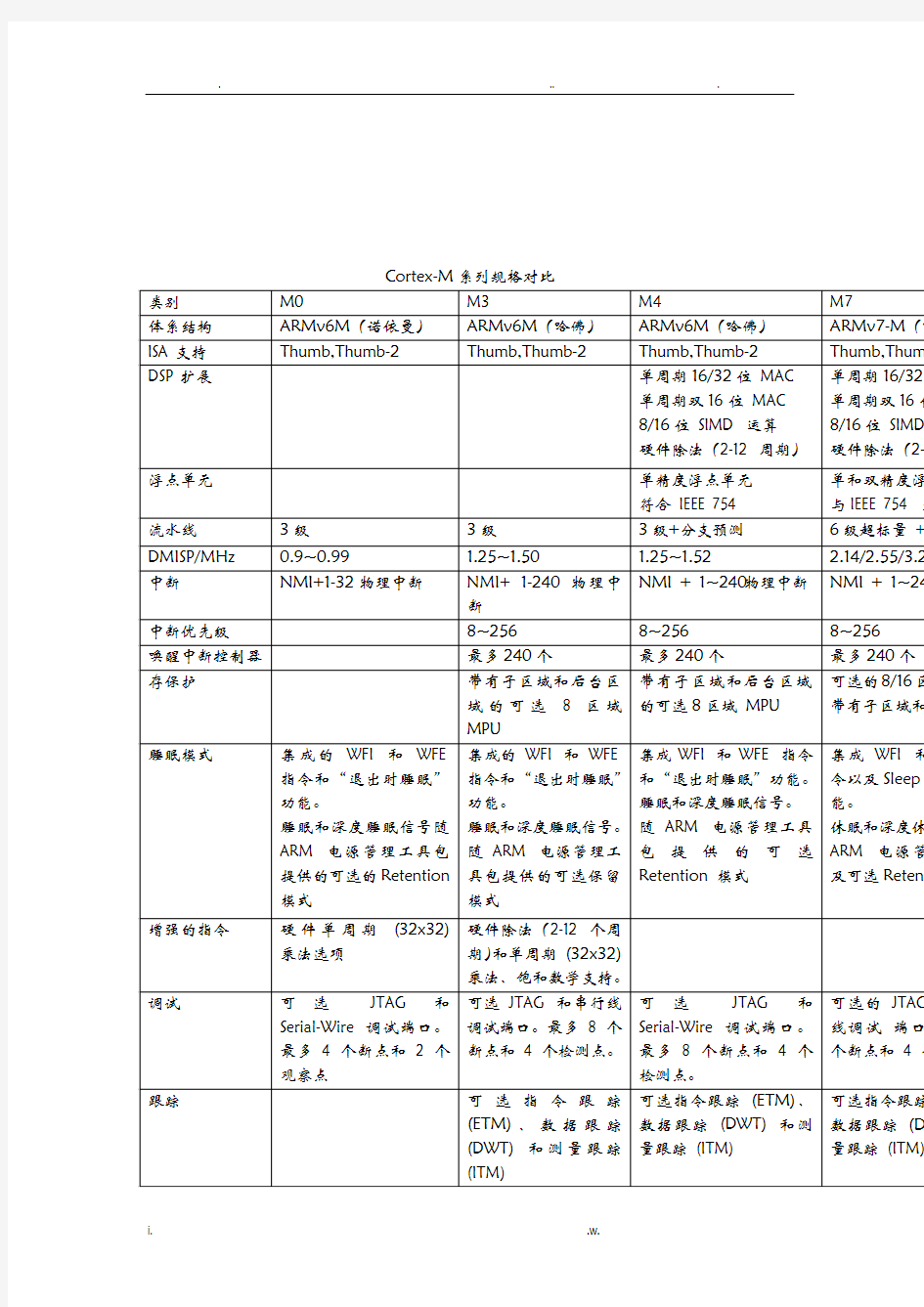

Cortex-M系列规格对比

Cortex-A系列:

ARM Cortex-A 系列是一系列用于复杂操作系统和用户应用程序的应用程序处理器。Cortex-A 系列处理器支持ARM、Thumb 和Thumb-2 指令集。

A5:

一个高性能、低功耗的ARM宏单元,带有L1高速缓存子系统,能提供完全的虚拟存功能。Cortex-A5 处理器实现了ARMv7 体系结构并运行32 位ARM 指令、16 位和32 位Thumb 指令,还可在Jazelle 状态下运行8 位Java 字节码。Cortex A-5 是最小以及最低功耗的Cortex-A 处理器,但处理性能比其他A系列差。

A7:

Cortex-A7 处理器的功耗和面积与超高效Cortex-A5 相似,但性能提升15~20%,Cortex-A7是ARM的大小核设计中的小核部分,并且与高端Cortex-A15 CPU 体系结构完全兼容。Cortex-A7处理器包括了高性能处理器Cortex-A15的一切特性,包括虚拟化(virtualization)、大容量物理存地址扩展(Large Physical Address Extensions (LPAE),可以寻址到1TB的存储空间)、NEON、VFP以及AMBA 4 ACE coherency (AMBA4 Cache Coherent Interconnect (CCI))。Cortex-A7支持多核MPCore的设计以及Big+Little的大小核设计。小型高能效的Cortex-A7 是最新低成本智能手机和平板电脑中独立CPU 的理想之选,并可在big.LITTLE 处理配置中与Cortex-A15 结合。

A8:

第一个使用ARMv7-A架构的处理器,很多应用处理器以Cortex-A8为核心。

Cortex-A8处理器是一个双指令执行的有序超标量处理器,针对高度优化的能效实现可提供 2.0Dhrystone MIPS(每MHz),这些实现可提供基于传统单核处理器的设备所需的高级别的性能。Cortex-A8在市场中构建了ARMv7体系结构,可用于不同应用,包括智能手机、智能本、便携式媒体播放器以及其他消费类和企业平台。分开的L1指令和数据cache大小可以为16KB或者32KB,指令和数据共享L2cache,容量可以到1MB。L1和L2cache的cache数据宽度为128比特,L1cache是虚拟索引,物理上连续,而L2完全使用物理地址。Cortex-A8的L1cache行宽度为64byte,L2cache在片集成。另外和Cortex-A9相比,由于Cortex-A8支持的浮点VFP运算非常有限,其VFP的速度非常慢,往往相同的浮点运算,其速度是Cortex-A9的1/10。Cortex-A8能并发某些NEON指令(如NEON的load/store和其他的NEON指令),而Cortex-A9因为NEON位宽限制不

能并发。Cortex-A8的NEON和ARM是分开的,即ARM核和NEON核的执行流水线分开,NEON访问ARM寄存器很快,但是ARM端需要NEON寄存器的数据会非常慢。

A9:

Cortex-A9MPCore或者单核处理器单MHz性能比Cortex-A5或者Cortex-A8高,支持ARM,Thumb,Thumb-2,TrustZone,Jazelle RCT,Jazelle DBX技术。L1的cache 控制器提供了硬件的cache一致性维护支持多核的cache一致性。核外的L2cache控制器(L2C-310,or PL310)支持最多8MB的cache。Cortex-A9的L1cache行宽度为32byte,L2cache因为多核的原因在核外集成,即通过SCU来访问多核共享的L2cache。

常见的Cortex-A9处理器包括nVidia's双核Tegra-2,以及TI's OMAP4平台。使用Cortex-A9处理器的设备包括Apple的ipad2(apple A5处理器),LG Optimus2X(nVidia Tegra-2),Samsung Galaxy S II等

A15:

Cortex-A15MPCore处理器是目前Cortex-A系列中性能最高的处理器,一个突出的特性是其硬件的虚拟化技术(Hardware virtualization)以及大物理存的扩展(Large Physical Address Extension(LPAE),能寻址到1TB的存)。

目前集成Cortex-A15的处理器量产的只有Samsung的Exynos5系列处理器,但TI的OMAP5系列处理器也采用Cortex-A15的核。具体的设备有Arndale Board。

A17:

A12的提升版,也就将A12合并到A17中,最新的高性能ARMv7-A核处理器,以更小和更节能的优势,提供与A15相仿的性能。相比A9 有60%的性能提升。

仍为32位ARMv7

Cortex-A17处理器提供了优质的性能和高端的特性使它理想的适合每一个屏幕,从智能手机到智能电视。Cortex-A17处理器架构上与广泛使用Cortex-A7处理器一致,促使下一代中档设备基于big.LITTLE技术。

A53:

最低功耗的ARMv8处理器,能够无缝支持32和64位代码。是世界上能效最高,面积最小的64位处理器。

使用高效的8-stage顺序管道和提升的获取数据技术性能平衡。

Cortex-A53提供比Cortex-A7更高的性能,并能作为一个独立的应用处理器或在big.LITTLE 配置下,搭配Cortex-A57处理器,达到最优性能、可伸缩性和能效。

A57:

最高效的64位处理器,用于扩展移动和企业计算应用程序功能,包括计算密集型64位应用,比如高端电脑、平板电脑和服务器产品。

性能比A15提升一倍。

A72:

Cortex-A72 是ARM 性能最出色、最先进的处理器。于2015 年年初正式发布的Cortex-A72是基于ARMv8-A 架构、并构建于Cortex-A57 处理器在移动和企业设备领域成功的基础之上。在相同的移动设备电池寿命限制下,Cortex-A72 能相较基于Cortex-A15 处理器,28纳米工艺节点的设备,提供3.5倍的性能表现,展现优异的整体功耗效率。Cortex-A72 的强化性能和功耗水平重新定义了2016 年高端设备为消费者带来的丰富连接和情境感知(context-aware)的体验。

Cortex-A72 可在芯片上单独实现,也可以搭配Cortex-A53 处理器与ARM CoreLinkTM CCI高速缓存一致性互连(Cache Coherent Interconnect)构成ARM big.LITTLETM 配置,进一步提升能效。

Cortex-A列规格对比

Classic处理器:

ARM7:

1994年推出,使用围最广的32 位嵌入式处理器系列。

0.9MIPS/MHz的三级流水线和诺依曼结构

ARM9:

ARM9 系列技术特点

?基于ARMv5TE 架构

?高效的5 级流水线,更快的吞吐量和系统性能,哈佛结构

o提取/解码/执行/存/写回

?同时支持ARM和Thumb指令集

o高效ARM-Thumb 交互工作允许最佳组合性能和代码密度?哈佛架构- 独立的指令和数据存接口

o可用存带宽增加

o同时访问I & D 存

o更高性能

?31 x 32 位寄存器

?32 位ALU 和桶行移位器

?32 位MAC 块增强

CoreSight?ETM9接口用于增强调试和trace

?标准AMBA?AHB?接口

?协处理器接口

存控制器

?存操作受MMU 或MPU 控制

?MMU 提供

o虚拟存支持

o快速上下文切换扩展(FCSE)

?MPU 支持

o存保护和边界

o应用沙坑效应

?写缓冲

o从外部存解耦部处理器

o可在4 个独立地址中存储16 个字

o清除缓冲脏行

灵活的缓存设计

?硬件缓存架构

?大小可从4 KB 到128 KB(以2 的方幂形式增长)

?I & D 缓存可具有独立大小

?行长度固定为8 个字

?固定4 向集关联

?零等待状态存取

?关键词首先缓存行填充

?无阻塞

?虚拟寻址

灵活的TCM 设计

?哈佛机构

?大小可为0 KB 或4 KB 到1 MB(以二次方形式增长)

?可具有独立大小

?可为RAM 或ROM

?允许等待状态

?ARM968上的双存储TCM

?物理寻址

o将非顺序存取停止一个周期以允许地址转换

DSP 增强

?单周期32x16 乘法器实现

o加快所有乘法指令

o流水线设计允许一个16x16 或32x16 开始每个周期

?新的32x16 和16x16 乘法指令

o允许独立存取16 位半寄存器

o允许压缩的16 位操作数高效使用32 位带宽

o ARM ISA 提供32x32 乘法指令

?有效微小数字饱和算法

o QADD、QSUB、QDADD、QDSUB

?前导零计数指令

o CLZ 加快标准化和除法

ARM11:

ARM11处理器系列所提供的引擎可用于当前生产领域中的很多智能手机,还广泛用于消费类、家庭和嵌入式应用程序。该处理器的功耗非常低,提供的性能围为小面积设计中的350 MHz 到速度优化设计中的1 GHz(45 纳米和65 纳米)。ARM11 处理器软件可以与以前所有ARM 处理器兼容,并引入了用于媒体处理的32 位SIMD、用于提高操作系统上下文切换性能的物理标记cache、强制实施硬件安全性的TrustZone 以及针对实时应用的紧密耦合存。

ARM11 处理器系列功能:

?强大的ARMv6 指令集架构

?ARM Thumb?指令集可以减少高达35% 的存带宽和大小需求

?用于执行高效嵌入式Java 的ARM Jazelle?技术

?ARM DSP 扩展

?SIMD(单指令多数据)媒体处理扩展可提供高达2 倍的视频处理性能

?作为片上安全基础的ARM TrustZone?技术(ARM1176JZ-S和ARM1176JZF-S 处理器)

?Thumb-2 技术(仅ARM1156(F)-S),可提高性能、能效和代码密度

?低功耗:

o0.21 mW/MHz (65G),包括cache 控制器

o节能关闭模式能够处理高级工艺中的静态漏电情况

?高性能整数处理器

o8 级整数流水线可提供高时钟频率(对于ARM1156T2(F)-S 为9 级)

o单独的加载-存储和算术流水线

o分支预测和返回栈

?高性能存系统设计

o支持4-64k cache 大小

o针对多媒体应用领域的、带DMA 的可选紧密耦合存

o对于媒体处理和网络应用领域,高性能64 位存系统加快了数据存取速度

o ARMv6 存系统架构加快了操作系统上下文切换速度