汇编知识点的要求:

1、能看的懂

2、可以做修改

3、不需要用汇编直接编写程序

汇编代码的应用场合:

1、ARM的启动代码必须要汇编,如:uboot最开始初始化硬件的代码

2、核在最开始初始化的位置。。。。

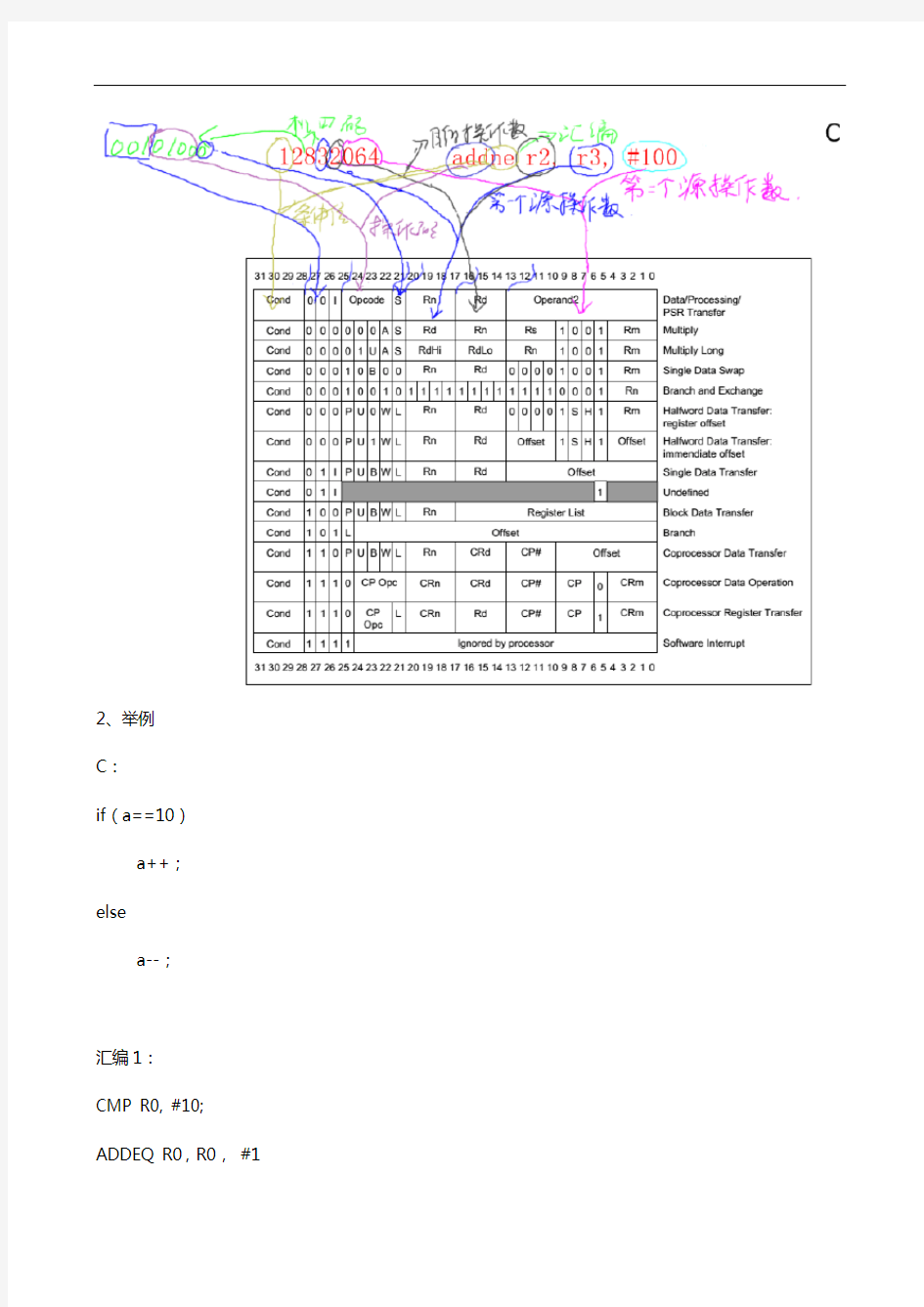

一、ARM汇编指令的编码格式

1、编码格式

ARM汇编指令编译成机器码以后,机器码的长度是32bits,这32bits的编码有一个固定的格式。不同ARM汇编指令,编码格式不同。

2、举例

C:

if(a==10)

a++;

else

a--;

汇编1:

CMP R0, #10; ADDEQ R0,R0,#1

SUBNE R0,R0,#1

汇编2

SUBS R1, R0, #10; //S ---运算的结果会影响条件码标志位:CPSR:NZCV ADDEQ R0,R0,#1

SUBNE R0,R0,#1

提示:

空指令NOP,实际上是占用CPU的时间,但是执行后,没有什么意义。NOP ----MOV R0,R0

3、条件码标识

10 -10

Z = 1

C = 0

N = 0

V = 0

============================================================= ====================

二、ARM的寻址方式

1、立即数寻址

操作数,有立即数。

ADD R0,R0,#1

MOV R1,#10

ORR R1,R1,#0xf R1=R1 | 0xf

BIC R1,R1,#0xf R1 = R1&(~(0xf))

错误:

ADD R1,#1,#2

注意:立即数合法的条件

在ARM汇编指令中,并不是所有的立即数,立即数是有一定的限制的。

什么样的立即数是合法的???

1、如果一个立即数是小于256的(即该立即数是8bits以的,0~255),该立即数是合法的。

2、如果一个立即数是大于等于256,该立即数经过循环左移偶数位,可以得到一个小于256的数,则该立即数合法。

256 = 0x100 ------左移20位0x10000000----左移4 0x1 合法

0x111 非法

0x102 非法

0x104 合法

0xfff

0xff00

0x12000

0x450000

0xab

原因:

在数据处理指令编码的时候,立即数用12bits来表示:

高4bits:循环左移左移偶数位除以2

低8bits:循环左移后的结果。

重要问题:

ADD R1,R0,#0xffff 非法

解决:

LDR R2,=0xffff // R2=0xffff,将立即数0xffff的值传送给R2 ADD R1, R0, R2

2、寄存器寻址

所有的操作数都是寄存器,没有立即数

ADD R0,R0,R1

MOV R1,R0

ORR R1,R1,R0 R1=R1 | 0xf

BIC R1,R1,R0 R1 = R1&(~(0xf))

3、寄存器间接寻址

本质上,相当于C语言的指针

问题:读取0x30008000地址下的容,该容是int型的???

C:

int a;

a = *(int *)0x30008000

汇编:

LDR R0,=0x30008000

LDR R1,[R0] //LDR = loader,数据加载指令,加载一个地址下的容

STR R2,[R1] //STR---store,数据存储指令,将一个数据存放到一个地址下。

错误的写法:

LDR R1, [0x30008000]

注意:间接寻址的地址需要存放到一个通用寄存器中,然后在使用。

4、寄存器的偏移寻址

MOV R0, R2,LSL #3 //LSL—逻辑左移。R0 = R2<<3

ADD R0,R1,R2,LSL #4 //R0 = R1 + (R2<<4)

SUB R0, R1, R2,LSL R3 //R0= R1- (R2< 5、基址变址寻址 是一个间接寻址的变形,地址是由基地址和偏移量组成的 1)先变址 LDR R0, [R1, #4] //将R1+4作为新地址,将新的地址下的容加载给R0 2)后变址 LDR R0, [R1],#4 //先将R1地址下的容加载给R0,然后R1=R1+4 3)自动变址 LDR R0, [R1, #4]! //!---》自动变址,将R1+4作为新地址,将新的地址下的容加载给R0;然后R1=R1+4 6、栈的寻址 栈有四种寻址方式 对栈的操作: STM --多个STR,一次可以完成多个数据的存储 LDM--多个LDR,一次可以完成多个数据的加载 例: 在操作满递减栈的时候: 出栈:LDMFD 入栈:STMFD 7、相对寻址 BL delay B loop 三、ARM的汇编指令 1、跳转指令(B)---分支指令branch B :单纯的跳转 BL :跳转的同时保存返回地址 BX :带状态切换的跳转 BLX:带状态切换的跳转,并保存返回地址 注意:受跳转指令编码格式的限制,跳转的围是-32MB~32MB。 例: BL delay //delay与跳转指令的不能超过32MB 注意,如果跳转的围超过32MB,使用: LDR PC, =delay 2、数据处理指令 需要注意: 立即数合法的要求 1)传送指令 mov R1,R0 mov R2,#10 mvn R3,#10 //将10取反,然后再传给R3 2)算术逻辑运算指令 ADD R1,R2,R0 //R1=R2+R0 SUB R2,R1,#10 //R2 = R1 -10 ORR R1,R1,#0xf // 将R1的低四位置1,其它位保持不变BIC R2,R2,#0xf //将R2的低四位清0,其它位保持不变AND R3,R3,#0xf //保留R3的低四位,其它位都清0 EOR R4,R4,#10 // R4 =R4^10 3)比较指令 CMP R0, #10 //R0-10,然后根据运算的结果自动影响标志位CMN R0, #10 //R0+10,然后根据运算的结果自动影响标志位 TST R0, #8 // R0 & 8,然后根据运算的结果自动影响标志位TEQ R0, #8 // R0 ^ 8,然后根据运算的结果自动影响标志位 3、乘法指令和乘加指令 MUL R3,R2,#10 //R3=R2*10 MLA R2,R1, R0, #10 //R2=R1*R0 + 10 4、存储器访问指令 根据存储器的地址访问该地址下的容: LDR R1,[R0] //R0—存储器的地址 STR R2,[R0] STMFD SP!, {R0-R8,LR} LDMFD SP!, {R0-R8,PC} SWP R2, R1, [R0] //通用寄存器和存储器之间的字类型数据交换 相当于: LDR R2, [R0] STR R1, [R0] 5、协处理器指令 在ARM核中,有一个协处理器(CP15),协处理器有16个寄存器C0~C15,我们对协处理器中寄存器进行访问的时候,使用的是协处理器指令,不能使用ARM汇编指令。 协处理器的作用:设置MMU、设置cache、读取芯片的ID,设置ARM的大小端格式 6、软件中断指令 SWI :ARM ---linux的系统调用 7、通用寄存器和状态寄存器的访问指令 MRS :将S(status register)move 到R(register)中 MSR 例: MRS R0,CPSR BIC R0,R0,#0x80 MSR CPSR,R0 上面程序的目的:将CPSR[7]清0,将所有的IRQ中断都打开。 四、ARM汇编伪指令 1、什么是伪指令 伪指令并不是真正的ARM汇编指令,当我遇到一些应用的时候,这些应用的场景并不能使用汇编指令实现,所以提出伪指令的概念。 伪指令相当于汇编指令的序列,一条伪指令在编译的时候,会被编译成一条或几条汇编指令。 伪指令相当于C语言的小函数。 2、LDR 1)ARM汇编指令 加载某地址上的数据。如:LDR R2,[R0] 2)ARM汇编伪指令 (1)传输不能使用mov来传递的立即数 MOV R1,#0xffff //非法 替代: LDR R1,=0xffff (2)获取一个标示符的地址,大围的 BL delay //当delay与BL delay指令,距离超过了32MB,跳不过去替代: LDR PC,=delay //围在4GB 3、NOP 是一个空指令,相当于MOV R0,R0 ,占用CPU的执行时间,没有作用。nop指令占用的时间:(1/MIPS)us 如:MIPS = 998 ----(1/998) us 4、ADR 小围的地址读取指令,-1020 ~ 1020