实验五计数、译码、显示电路

一、实验目的

掌握中规模集成计数器74LS161及七段译码器CD4511的逻辑功能,掌握共阴极七段显示器的使用方法,熟悉用示波器测试计数器输出波形的方法。

二、实验原理

计数、译码、显示电路就是由计数器、译码器与显示器三部分电路组成的逻辑电路。下面分别加以介绍。

1.计数器:计数器就是一种中规模集成电路,其种类有很多。如果按照触发器翻转的次序分类,可分为同步计数器与异步计数器两种;如果按照计数数字的增减可分为加法计数器、减法计数器与可逆计数器三种;如果按照计数器进位规律又可分为二进制计数器、十进制计数器、可编程N进制计数器等多种。

常用计数器均有典型产品,不须自

己设计,只要合理选用即可。

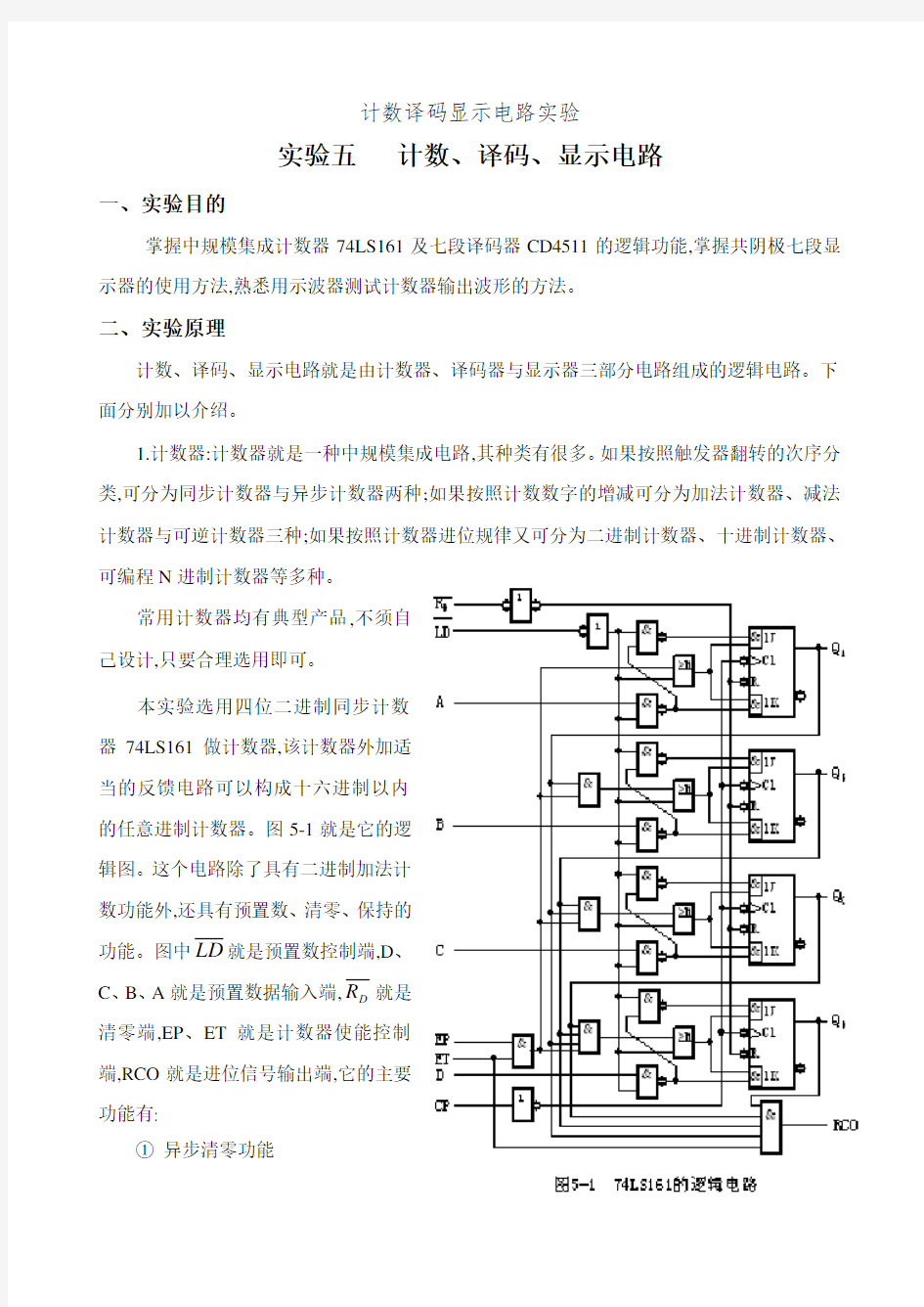

本实验选用四位二进制同步计数

器74LS161做计数器,该计数器外加适

当的反馈电路可以构成十六进制以内

的任意进制计数器。图5-1就是它的逻

辑图。这个电路除了具有二进制加法计

数功能外,还具有预置数、清零、保持的

功能。图中LD就是预置数控制端,D、

R就是

C、B、A就是预置数据输入端,

D

清零端,EP、ET就是计数器使能控制

端,RCO就是进位信号输出端,它的主要

功能有:

①异步清零功能

R=0(输出低电平),则输出QDQCQBQA=0000,除EP、ET信号外,与其它输入信号无若

D

关,也不需要CP脉冲的配合,所以称为“异步清零”。

②同步并行置数功能

R=1,且LD=0的条件下,当CP上升沿到来后,触发器QDQCQBQA同时接收D、C、在

D

B、A输入端的并行数据。由于数据进入计数器需要CP脉冲的作用,所以称为“同步置数”,由于4个触发器同时置入,又称为“并行”。

③保持功能

R=1,LD=1的条件下,EP、ET两个使能端只要有一个低电平,计数器将处于数据保在

D

持状态,与CP及D、C、B、A输入无关。

④计数功能

R=1、LD=1、EP=1、ET=1的条件下,计数器对CP端输入脉冲进行计数,计数方式在

D

为二进制加法,状态变化在QDQCQBQA=0000~1111间循环。74LS161的功能表详见表5-l 所示。

表5-1 74LS161的功能表

本实验所需计数器就是十进制计数器,必须对74LS161外加适当的反馈电路构成十进制计数器,状态变化在QDQCQBQA=0000~1001间循环。

用反馈的方法构成十进制计数器一般有两种形式,即与反馈置数法。反馈置零法就是利用R构成,即:当Q D Q C Q B Q A=1010(十进制数10)时,通过反馈线强制计数器清零,如图

清除端

D

5-2(a)所示。由于该电路会出现瞬间1010状态,会引起译码电路的误动作,因此很少被采用。反

馈置数法就是利用预置数端LD构成,把计数器输入端D1D2D2D3全部接地,当计数器计到1001(十进制数9)时,利用Q D Q A反馈线使预置端LD=0,则当第十个CP到来时,计数器输出端等于输入端电平,即:Q D=Q C=Q B=Q A=0,这样可以克服反馈置零法的缺点。利用预置端LD构成的计数器电路如图5-2(b)所示。

以上介绍的就是一片计数器工作的情况。在实际应用中,往往需要用多片计数器构成多位计数器。下面介绍计数器的级联方法,级联可分串行进位与并行进位两种。二位十进制串行进位计数器的级联电路如图5-3所示,其缺点就是速度较慢。二位十进制并行进位(也称超前进位)计数器的级联电路如图5-4所示,后者的进位速度比前者大大提高。