HDB3编解码电路设计

- 格式:doc

- 大小:194.50 KB

- 文档页数:13

hdb3译码实验报告HDB3译码实验报告引言:HDB3(High Density Bipolar of Order 3)是一种常用于数字通信中的编码和解码技术。

在本次实验中,我们将对HDB3译码进行实验,并对实验结果进行分析和讨论。

一、实验背景数字通信中,编码和解码技术起着至关重要的作用。

编码技术可以将数字信号转换为适合传输的信号形式,而解码技术则将接收到的信号重新转换为原始的数字信号。

HDB3编码和解码技术广泛应用于数字通信系统中,具有较高的传输效率和抗干扰能力。

二、实验目的本次实验的目的是通过对HDB3译码的实验,深入理解HDB3编码和解码的原理,并验证其在数字通信中的可行性和有效性。

三、实验原理HDB3编码和解码是基于Bipolar编码的一种技术。

在HDB3编码中,每个二进制位被编码为一个符号,符号可以是正脉冲、负脉冲或零脉冲。

解码过程则是将接收到的符号转换为原始的二进制位。

四、实验步骤1. 准备实验所需材料:计算机、数字信号发生器、示波器等。

2. 设计并生成HDB3编码的测试信号。

3. 将测试信号输入到HDB3译码器中进行解码。

4. 使用示波器观察解码后的信号波形,并记录观察结果。

5. 对比解码结果与原始信号进行分析和比较。

五、实验结果与分析通过实验我们得到了解码后的信号波形,并与原始信号进行了对比。

观察结果显示,HDB3译码器能够准确地将接收到的信号转换为原始的二进制位,且在传输过程中具有较好的抗干扰能力。

这验证了HDB3编码和解码技术在数字通信中的可行性和有效性。

六、实验总结本次实验通过对HDB3译码的实验,我们深入理解了HDB3编码和解码的原理,并验证了其在数字通信中的可行性和有效性。

HDB3编码和解码技术在数字通信中具有重要的应用价值,能够提高传输效率和抗干扰能力。

在今后的研究和实践中,我们将进一步探索和应用HDB3编码和解码技术,为数字通信的发展做出更大的贡献。

结束语:通过本次实验,我们对HDB3译码有了更深入的了解,并验证了其在数字通信中的可行性和有效性。

hdb3码型变换实验实验报告

HDB3码型变换实验实验报告

实验目的:

通过实验掌握HDB3码型变换的原理和方法,了解其在数字通信中的应用。

实验设备:

1. 信号发生器

2. 示波器

3. HDB3编码解码器

实验原理:

HDB3码(High Density Bipolar of Order 3)是一种常用的数字信号编码方式,

它通过对传输的二进制数据进行编码,实现了数据的高密度传输和抗干扰能力。

HDB3码的编码规则是在传输的数据中插入特定的控制比特,通过对控制比特

的处理,实现了数据的传输和恢复。

实验步骤:

1. 将信号发生器的输出连接到HDB3编码解码器的输入端,将HDB3编码解码

器的输出连接到示波器。

2. 设置信号发生器的输出频率和幅度,生成一个二进制数据序列。

3. 将生成的二进制数据序列输入到HDB3编码解码器中,观察编码后的信号波形。

4. 调整信号发生器的频率和幅度,再次观察编码后的信号波形。

5. 通过对比编码前后的信号波形,分析HDB3码型变换的效果和特点。

实验结果:

经过实验,我们观察到HDB3码型变换后的信号波形具有较高的密度和较好的抗干扰能力。

在不同频率和幅度下,HDB3码型变换都能有效地保持数据的传输质量。

通过对比实验结果,我们进一步了解了HDB3码型变换在数字通信中的重要性和应用价值。

结论:

HDB3码型变换实验通过实际操作和观察,使我们更加深入地理解了数字信号编码的原理和方法。

掌握了HDB3码型变换的应用技巧,为我们今后在数字通信领域的工作提供了重要的参考和指导。

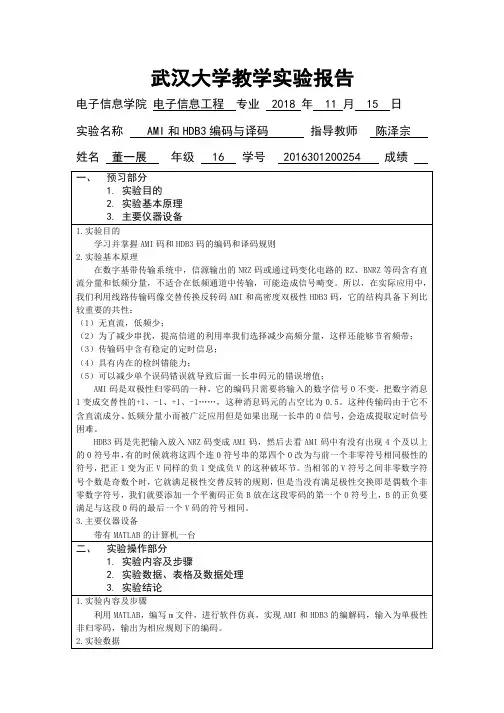

武汉大学教学实验报告电子信息学院 电子信息工程 专业 2018 年 11 月 15 日实验名称 AMI和HDB3编码与译码 指导教师 陈泽宗姓名 董一展 年级 16 学号 2016301200254 成绩一、预习部分1.实验目的2.实验基本原理3.主要仪器设备1.实验目的学习并掌握AMI码和HDB3码的编码和译码规则2.实验基本原理在数字基带传输系统中,信源输出的NRZ码或通过码变化电路的RZ、BNRZ等码含有直流分量和低频分量,不适合在低频通道中传输,可能造成信号畸变。

所以,在实际应用中,我们利用线路传输码像交替传换反转码AMI和高密度双极性HDB3码,它的结构具备下列比较重要的共性:(1)无直流,低频少;(2)为了减少串扰,提高信道的利用率我们选择减少高频分量,这样还能够节省频带;(3)传输码中含有稳定的定时信息;(4)具有内在的检纠错能力;(5)可以减少单个误码错误就导致后面一长串码元的错误增值;AMI码是双极性归零码的一种,它的编码只需要将输入的数字信号0不变,把数字消息1变成交替性的+1、-1、+1、-1……,这种消息码元的占空比为0.5。

这种传输码由于它不含直流成分、低频分量小而被广泛应用但是如果出现一长串的0信号,会造成提取定时信号困难。

HDB3码是先把输入放入NRZ码变成AMI码,然后去看AMI码中有没有出现4个及以上的0符号串,有的时候就将这四个连0符号串的第四个0改为与前一个非零符号相同极性的符号,把正1变为正V同样的负1变成负V的这种破坏节。

当相邻的V符号之间非零数字符号个数是奇数个时,它就满足极性交替反转的规则,但是当没有满足极性交换即是偶数个非零数字符号,我们就要添加一个平衡码正负B放在这段零码的第一个0符号上,B的正负要满足与这段0码的最后一个V码的符号相同。

3.主要仪器设备带有MATLAB的计算机一台二、实验操作部分1.实验内容及步骤2.实验数据、表格及数据处理3.实验结论1.实验内容及步骤利用MATLAB,编写m文件,进行软件仿真,实现AMI和HDB3的编解码,输入为单极性非归零码,输出为相应规则下的编码。

hdb3编码和译码时延HDB3编码和译码是数据通信中常用的技术,它是一种具有平衡特性的差分编码技术。

HDB3编码主要用于减少信号传输中的噪声和干扰,提高信号的可靠性和稳定性。

然而,这种编码方式也会带来一定的时延,下面我们将详细讨论HDB3编码和译码时延的问题。

一、HDB3编码原理HDB3编码是一种差分编码方式,它通过比较输入信号的变化与参考信号的变化来生成编码信号。

在HDB3编码中,采用了三种类型的比特:0B(零比特)、1B(一比特)和H(高电平)比特。

在发送端,输入数据经过HDB3编码后,会生成具有特定规律的编码信号。

这种编码方式能够有效地减少噪声和干扰对信号的影响,提高信号的可靠性和稳定性。

二、编码时延HDB3编码过程中会产生一定的时延,主要原因包括编码过程本身需要的时间、编码器的处理速度以及比特分配等因素。

一般来说,HDB3编码器通常需要一定的处理时间才能完成对输入数据的编码,这个过程本身就会带来一定的时延。

另外,在数据传输过程中,为了确保信号的稳定性和可靠性,可能需要采用多级编码器,这也会增加编码时延。

三、译码时延HDB3译码是解码过程,其时延主要取决于解码器的处理速度和比特分配等因素。

解码器需要正确地识别并还原出原始数据,这需要解码器具备较高的性能和准确性。

在某些情况下,如果解码器处理速度较慢或者出现误判,可能会增加译码时延。

四、优化措施为了减少HDB3编码和译码的时延,我们可以采取以下措施:1.优化编码器和解码器的硬件性能:提高编码器和解码器的处理速度和精度,可以降低时延。

2.减少编码器和解码器的层级:采用更少的编码器和解码器层级,可以减少处理过程中的时延。

3.使用缓存技术:在解码过程中使用缓存技术,可以暂存部分编码数据,降低解码时延。

4.优化比特分配:合理分配比特资源,可以减少解码过程中的处理时延。

五、总结HDB3编码和译码在数据通信中具有重要意义,它可以提高信号的可靠性和稳定性。

实验七AMI/HDB3/CMI码型变换实验一、实验原理在实际的基带传输系统中,并不是所有码字都能在信道中传输。

例如,含有丰富直流和低频成分的基带信号就不适宜在信道中传输,因为它有可能造成信号严重畸变。

同时,一般基带传输系统都从接收到的基带信号流中提取收定时信号,而收定时信号却又依赖于传输的码型,如果码型出现长时间的连“0”或连“1”符号,则基带信号可能会长时间的出现0电位,从而使收定时恢复系统难以保证收定时信号的准确性。

实际的基带传输系统还可能提出其他要求,因而对基带信号也存在各种可能的要求。

归纳起来,对传输用的基带信号的主要要求有两点:1.对各种代码的要求,期望将原始信息符号编制成适合于传输用的码型;2.对所选码型的电波波形要求,期望电波波形适宜于在信道中传输。

前一问题称为传输码型的选择;后一问题称为基带脉冲的选择。

这是两个既有独立性又有互相联系的问题,也是基带传输原理中十分重要的两个问题。

传输码(传输码又称为线路码)的结构将取决于实际信道特性和系统工作的条件。

在较为复杂的基带传输系统中,传输码的结构应具有下列主要特性:1.能从其相应的基带信号中获取定时信息;2.相应的基带信号无直流成分和只有很小的低频成分;3.不受信息源统计特性的影响,即能适应于信息源的变化;4.尽可能地提高传输码型的传输效率;5.具有内在的检错能力,等等。

满足或部分满足以上特性的传输码型种类繁多,主要有:AMI、HDB3、CMI码等等。

(一)AMI码AMI码的全称是传号交替反转码。

这是一种将消息代码0(空号)和1(传号)按如下规则进行编码的码:代码的0仍变换为传输码的0,而把代码中的1交替地变换为传输码的+1、–1、+1、–1…由于AMI码的传号交替反转,故由它决定的基带信号将出现正负脉冲交替,而0电位保持不变的规律。

由此看出,这种基带信号无直流成分,且只有很小的低频成分,因而它特别适宜在不允许这些成分通过的信道中传输。

由AMI码的编码规则看出,它已从一个二进制符号序列变成了一个三进制符号序列,即把一个二进制符号变换成一个三进制符号。

---------------------------------------------------------------------------------------西电021213班-------------------- 根据教材有:B总是与其前面的1或V符号相反,V总是与前面的1或B相符号相同,1总是与前面的V或B符号相反,就可以编符号了。

对上述的说明(参考自樊昌信版《通信原理》):取代节:根据解码规则第一条,破坏交替性的1或-1出现时,将此符号和前面3个符号替换为0000。

V为破坏脉冲,即破坏交替性的1或-1出现的位。

B为调节脉冲,B可以是0,1或-1。

将0000替换为B00V。

调节脉冲的作用:在破坏脉冲的极性也交替的情况下保证破坏脉冲对整个序列极性交替的破坏性。

正确的步骤为:1、写AMI码2、把"0000"换为取代节。

"0000"分离开来,替换为B00V3、V的取值:第一个V取值与AMI码的第一个-1相同,即取-V,以后交替取+V,-V。

4、B的取值:根据V和V前面存在的1或-1,写B,若+V前面是-1或-V,则取B=+B,即B 没有破坏极性,但V破坏了极性,下同;若+V前面是+1或+V,则取B=+B;若-V前面是+1或+V,则取B=-B;若-V前面是-1或-V,则取B=+B。

附简单方法快速的编码方法:取节:相邻V之间奇数个非0码就取000V;偶数个非0码就取B00V,定符号:V的取值第一个V取值与AMI码(见上)的第一个数+1相同,即取+V,以后交替取+V,-V。

然后1与B的符号交替变化即可快速编码原理:HDB3码的编码中,V相当于破坏码元,B相当于为消除破坏码元影响而引入的调节码元。

为保证输出无直流的特性,破坏码元V的保持交替变化,同理1与B也得保持交替变化。

例如:消息代码:1 0 0 0 0 10 0 0 01 1 0 0 0 0 1 10 0 0 00 0 0 0 1 1 10 0 0 01中间码:1 0 0 0 V 10 0 0 V1 1 B 0 0 V 1 1B 0 0 V B 0 0 V 1 1 10 0 0 V1HDB3码:+1 0 0 0 +V -10 0 0 -V+1 -1 +B 0 0 + V -1 +1 -B 0 0 -V+B 0 0 +V -1 +1 -10 0 0 -V+1 HDB3编码方法∙ 1∙ 2∙ 3分步阅读通信当中常用的HDB3编码规则。

利用FPGA实现HDB3编解码功能摘要:HDB3(三阶高密度双极性)码具有无直流分量、低频成分少、连零个数不超过3个、便于提取时钟信号等特点。

通过对HDB3编解码原理进行分析和研究,提出一种基于FPGA 的HDB3编解码实现方法,给出Verilog HDL语言的实现方法和仿真波形,完成硬件电路的设计和测试,采用该方法设计的HDB3编解码器已应用于相关实验设备中。

广告插播信息维库最新热卖芯片:TOP224YN TDA1519B DTC144EUA EP2C5T144C8SN74LV541APWR GL386CD40193BE EL4422CN ADG511ABR STRS63071 引言数字通信系统的某些应用可对基带信号不载波调制而直接传输,其中传输线路对码型的要求如下:信码中不宜有直流分量,低频分量应尽可能的少,码型要便于时钟信号提取。

根据这些要求,ITU-T(国际电联)在G.703建议中规定,对于2 MHz、8 MHz、32 MHz速率的数字接口均采用HDB3(三阶高密度双极性)码。

HDB3码具有无直流分量,低频成分少,连零个数不超过3个等特点,便于时钟信号的提取和恢复,适合在信道中直接传输。

这里利用Verilog HDL语言设计用于数字通信系统中的HDB3编解码器。

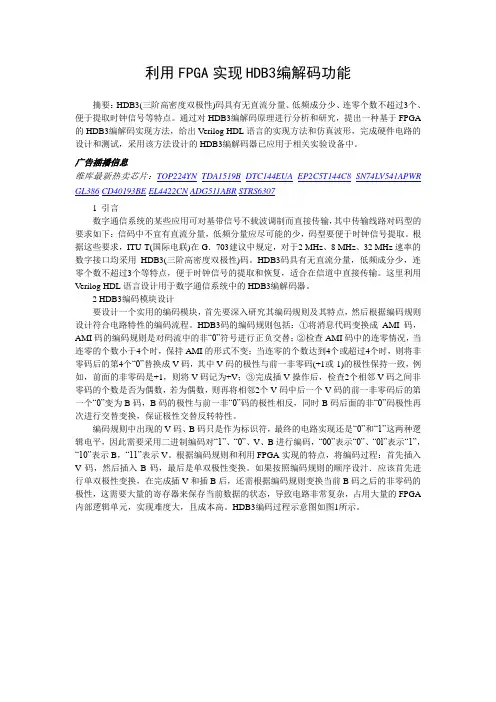

2 HDB3编码模块设计要设计一个实用的编码模块,首先要深入研究其编码规则及其特点,然后根据编码规则设计符合电路特性的编码流程。

HDB3码的编码规则包括:①将消息代码变换成AMI码,AMI码的编码规则是对码流中的非“0”符号进行正负交替;②检查AMI码中的连零情况,当连零的个数小于4个时,保持AMI的形式不变;当连零的个数达到4个或超过4个时,则将非零码后的第4个“0”替换成V码,其中V码的极性与前一非零码(+1或-1)的极性保持一致,例如,前面的非零码是+1,则将V码记为+V;③完成插V操作后,检查2个相邻V码之间非零码的个数是否为偶数,若为偶数,则再将相邻2个V码中后一个V码的前一非零码后的第一个“0”变为B码,B码的极性与前一非“0”码的极性相反,同时B码后面的非“0”码极性再次进行交替变换,保证极性交替反转特性。

HDB3编码方法HDB3编码(High-Density Bipolar-3)是一种用于数字通信中的线路编码方法。

它是一种高密度的双极编码方式,旨在减少数据传输中的直流偏置,并增强时钟同步。

本文将详细介绍HDB3编码的原理、应用和优势。

HDB3编码的原理是将输入的二进制数据进行特定规则的转换,通过使用多种转换规则,有效地控制二进制数据流中的直流分量。

它基于B8ZS(Binary 8 Zero Substitution)二进制代码的改进,通过添加减少的位子将数据转换为多种字节模式。

通过这种方式,HDB3编码可以在传输数据时保持数据流的直流功率接近零,并提供更好的同步机制。

1.如果连续的1的个数为偶数,不进行编码,输出与输入数据相同。

2.如果连续的1的个数为奇数,进行特殊编码:a. 将连续的3个1替换为0V (zero substitution),表示一个零电压信号。

b. 如果无法替换3个连续的1,将下一个连续的1置换为1V (violation),表示一个非零电压信号。

c.替换规则是保证无连续4个零的出现,以避免时钟同步问题。

通过上述规则,HDB3编码可以将数据流有效地转换为包含少量非零电压的数据流,减少直流偏置的问题,并增强时钟同步。

HDB3编码广泛应用于数字通信中,特别是在T1数字传输系统中。

它可在传输系统中提供高质量和高可靠性的信号传输,有效地处理数码信号,并确保传输数据成功地从一个地点传输到另一个地点。

HDB3编码在传输过程中还提供了错误检测和纠正的能力,以提高系统的可靠性。

1.减少直流偏置:HDB3编码能够减少数据传输中的直流偏置,这对于长距离传输和噪声环境下的信号传输非常重要。

直流偏置越小,传输信号的可靠性和品质就越好。

2.高密度编码:HDB3编码可以将输入数据转换为较短的编码序列,这意味着它可以提供更高的数据传输速率和更好的带宽利用率。

这对于高速数字通信系统非常重要。

3.时钟同步:HDB3编码通过特殊的替换规则确保时钟同步问题得到解决。

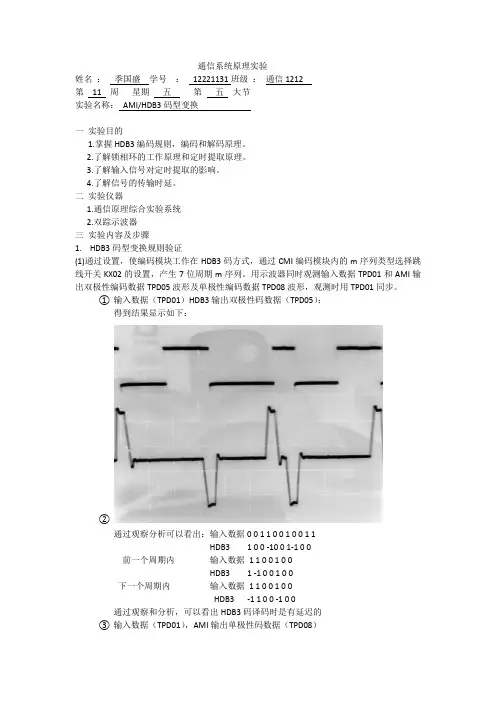

通信系统原理实验姓名:季国盛学号:12221131班级:通信1212第11 周星期五第五大节实验名称:AMI/HDB3码型变换一实验目的1.掌握HDB3编码规则,编码和解码原理。

2.了解锁相环的工作原理和定时提取原理。

3.了解输入信号对定时提取的影响。

4.了解信号的传输时延。

二实验仪器1.通信原理综合实验系统2.双踪示波器三实验内容及步骤1.HDB3码型变换规则验证(1)通过设置,使编码模块工作在HDB3码方式,通过CMI编码模块内的m序列类型选择跳线开关KX02的设置,产生7位周期m序列。

用示波器同时观测输入数据TPD01和AMI输出双极性编码数据TPD05波形及单极性编码数据TPD08波形,观测时用TPD01同步。

①输入数据(TPD01)HDB3输出双极性码数据(TPD05):得到结果显示如下:②通过观察分析可以看出:输入数据0 0 1 1 0 0 1 0 0 1 1HDB3 1 0 0 -10 0 1-1 0 0前一个周期内输入数据1 1 0 0 1 0 0HDB3 1 -1 0 0 1 0 0下一个周期内输入数据1 1 0 0 1 0 0HDB3 -1 1 0 0 -1 0 0通过观察和分析,可以看出HDB3码译码时是有延迟的③输入数据(TPD01),AMI输出单极性码数据(TPD08)得到显示结果如下:从显示结果可以得到:输入数据0 0 1 1 0 0 1 0 0 1 1HDB3单极性码数据0 0 -1 0 0-1 -1 0 0在一个周期内,输入数据:输入数据 1 1 0 0 1 0 0HDB3单极性码数据-1 -1 0 0 -1 0 0(2) 使输入数据端口悬空产生全1码,重复步骤(1)。

用示波器观测如下数据:①输入数据(TPD01),HDB3输出双极性码数据(TPD05)得到如下结果:输入数据 1 1 1 1 1HDB3双极性码数据-1 1-1 1-1可以看出,当输入全为1的时候,HDB3双极性码正负极性交替出现②输入数据(TPD01),HDB3输出单极性码数据(TPD08)得到结果如下:输入数据 1 1 1HDB3单极性码数据-1 -1 -1(3)使输入数据为全0码,重复步骤(1)。

hdb3 编码中间过程

HDB3(High Density Bipolar III)编码是一种用于数字通信系统的编码方式,其目的是消除连续多个零的影响,提高信号的频带利用率。

HDB3编码过程可以分为以下几个步骤:

1. 初始化:在编码开始时,首先确定编码规则和初始状态。

通常情况下,第一个编码单元的B取0,第一个非零符号取-1。

2. 编码规则1:当源码为1时,暂时保持不变。

3. 编码规则2:当连续的零个数不超过3个时,保持不变。

如果连续零的个数超过3个,则将每4个连续的零看作一个单元,进行取代节处理。

4. 取代节处理:将连续的四个零替换为B00V的形式,其中B和V需要满足一定的条件。

具体规则如下:

-当连续的两个取代节之间的1的个数为奇数时,B取1,V取-1;-当连续的两个取代节之间的1的个数为偶数时,B取0,V取1。

5. 极性交替:在确定B和V的值后,需要确保V码的极性交替。

具

体方法是:

-检查V码之前的非零符号的极性;

- V码与前一个非零符号的极性相反;

- V码之间的极性交替。

6. 后续编码:在完成取代节处理和极性交替后,按照上述规则继续对后续位进行编码。

需要注意的是,HDB3编码的解码过程相对简单,主要是找到原始的取代节,并根据取代节还原原始信号。

HDB3编码具有较低的直流分量和较小的低频分量,有利于节省频带资源和降低传输误差。

hdb3码型变换实验报告HDB3码型变换实验报告引言:HDB3码型是一种高密度双极性三零码,广泛应用于数字通信系统中的信号编码。

本实验旨在通过对HDB3码型的变换过程进行实际操作,深入理解其原理和应用。

一、实验目的本实验的主要目的是通过实际操作,掌握HDB3码型的变换过程,并了解其在数字通信系统中的应用。

二、实验原理HDB3码型是一种基于双极性三零码的信号编码方式。

它的原理是通过对信号进行特定规则的变换,将原始数据转换为HDB3码型。

在HDB3码型中,每个数据位通过特定规则的变换后,可以表示为正脉冲、负脉冲或无脉冲。

这种编码方式可以有效地降低传输线上的直流成分,并提高传输效率。

三、实验步骤1. 准备实验设备:计算机、信号发生器、示波器等。

2. 连接信号发生器和示波器,并设置合适的参数。

3. 打开计算机上的信号发生器软件,并选择HDB3码型。

4. 输入原始数据,并观察示波器上的信号波形。

5. 分析示波器上的波形,观察HDB3码型的变换规律。

6. 记录实验数据,并进行数据分析。

四、实验结果与分析通过实验操作,我们成功地将原始数据转换为HDB3码型,并观察到了信号波形的变化。

根据实验数据和示波器上的波形,我们可以得出以下结论:1. HDB3码型的变换规律:根据HDB3码型的规则,连续两个零位之间的脉冲数目不能超过三个。

当连续两个零位之间的脉冲数目为偶数时,HDB3码型中会插入一个反向脉冲,以保持脉冲数目为偶数;当连续两个零位之间的脉冲数目为奇数时,HDB3码型中会插入一个反向脉冲,并使其后的一个脉冲变为无脉冲,以保持脉冲数目为偶数。

2. HDB3码型的优点:HDB3码型通过特定的编码规则,使得信号波形中的直流成分降低,从而提高了传输效率。

同时,HDB3码型具有较好的抗噪声性能,能够有效地减少传输过程中的误码率。

3. HDB3码型的应用:HDB3码型广泛应用于数字通信系统中,特别是在高速传输环境下。

它可以用于数字电话网络、数字广播、数字电视等领域,有效地提高信号传输的可靠性和稳定性。

通信原理实验指导书思考题答案实验一思考题P1-4:1、位同步信号和帧同步信号在整个通信原理系统中起什么作用?答:位同步和帧同步是数字通信技术中的核心问题,在整个通信系统中,发送端按照确定的时间顺序,逐个传输数码脉冲序列中的每个码元,在接收端必须有准确的抽样判决时刻(位同步信号)才能正确判决所发送的码元。

位同步的目的是确定数字通信中的各个码元的抽样时刻,即把每个码元加以区分,使接收端得到一连串的码元序列,这一连串的码元序列代表一定的信息。

通常由若干个码元代表一个字母(符号、数字),而由若干个字母组成一个字,若干个字组成一个句。

帧同步的任务是把字、句和码组区分出来。

尤其在时分多路传输系统中,信号是以帧的方式传送的。

克服距离上的障碍,迅速而准确地传递信息,是通信的任务,因此,位同步信号和帧同步信号的稳定性直接影响到整个通信系统的工作性能。

2、自行计算其它波形的数据,利用U006和U005剩下的资源扩展其它波形。

答:在实验前,我们已经将四种波形在不同频段的数据写入了数据存储器U005(2864)并存放在固定的地址中。

当单片机U006(89C51)检测到波形选择开关和频率调节开关送入的信息后,一方面通过预置分频器调整U004(EPM7128)中分频器的分频比(分频后的信号频率由数码管M001~M004显示);另一方面根据分频器输出的频率和所选波形的种类,通过地址选择器选中数据存储器U005中对应地址的区间,输出相应的数字信号。

该数字信号经过D/A转换器U007(TLC7528)和开关电容滤波器U008(TLC14CD)后得到所需模拟信号。

自行扩展其它波形时要求非常熟悉信号源模块的硬件电路,最好先用万用表描出整个硬件电路。

此题建议让学生提供设计思路,在设计不成熟的情况很容易破坏信号源。

提示如下:工作流程同已有的信号源,波形的数据产生举例如下:a=sin(2.0*PI*(float)i/360.0)+1.0;/产生360个正弦波点,表示一个周期波形数据/k=(unsigned char)(a/2.0*255.0);/数字化所有点以便存储/将自己产生的360个点追加到数据存储器U005(2864)并存放在后续的固定的地址中,根据单片机U006(89C51)编程选中对应U005的地址,循环周期显示输出即为我们所设计的波形。

HDB3译码原理什么是HDB3编码HDB3编码(High Density Bipolar 3-zero substitution)是一种用于数字通信中的线路编码方式,广泛应用于数字传输系统中。

HDB3编码的主要作用是通过对信号进行特殊编码,来改善数据传输的可靠性和抗干扰性能。

HDB3编码的原理HDB3编码使用一种特殊的规则来对数据进行编码。

其基本原理是通过编码规则将连续的0串以及特定的没有转移极性的1串转换成有规律的短脉冲序列,从而降低电路中的低频成分,提高传输带宽利用效率。

HDB3编码规则为了实现HDB3编码,需要遵循以下规则:规则1:零之前的非零脉冲个数为偶数在HDB3编码中,如果零之前的非零脉冲个数为偶数,那么该零将被编码成一个单极性脉冲,保持原来的极性。

规则2:零之前的非零脉冲个数为奇数如果零之前的非零脉冲个数为奇数,那么该零将被编码成两个单极性脉冲,且最后一个脉冲改变极性。

规则3:零转换规则为了区分数据中的零和由于误码引起的零,HDB3编码引入了零的转换规则(zero substitution rule)。

这个规则指定当输入数据中存在连续的四个零时,使用特殊的编码方式将其转换为一个非零脉冲。

HDB3解码原理HDB3解码是HDB3编码的逆过程。

解码器通过观察输入信号中的脉冲序列以及信号的极性来还原原始的二进制数据。

解码规则1:单脉冲解码解码器首先检测并还原通过规则1编码的零,即将单极性脉冲还原为0。

这是因为在编码过程中,单极性脉冲只能代表零。

解码规则2:双脉冲解码如果解码器检测到两个相邻的脉冲具有相同的极性,那么根据规则2,这两个脉冲应当表示一个零。

解码器将判断这两个脉冲是由数据中的零引起还是由误码引起,并还原原始的二进制数据。

解码规则3:零转换解码如果解码器检测到两个相邻的脉冲具有不同的极性,那么根据规则3,这两个脉冲应当表示一个由误码引起的零。

解码器将把这个零还原为四个连续的零,并还原原始的二进制数据。

姓名:学号:班级:第周星期第大节实验名称:HDB3码型变换一、实验目的1.掌握AMI编码规则,编码和解码原理。

2.掌握HDB3编码规则,编码和解码原理。

3.了解锁相环的工作原理和定时提取原理。

4.了解输入信号对定时提取的影响。

5.了解信号的传输时延。

6.了解AMI/HDB3编译码集成芯片CD22103。

二、实验仪器1.ZH5001A通信原理综合实验系统2.20MHz双踪示波器三、实验内容1.HDB3码变换规则验证(1)通过KX02的设置,产生7位周期m序列。

用示波器观测如下数据:(3)拔除KD01,输入数据为全1码。

用示波器观测如下数据:(4)KD01跳线中间接地,输入数据为全0码。

用示波器观测如下数据:♦输入数据(TPD01),HDB3输出单极性码数据(TPD08)2.HDB3码译码和时延测试(2)KD01设置为M;通过KX02的设置,产生7位周期m序列;KP02设置在HDB3位置。

用示波器观测如下数据:输入数据(TPD01),HDB3译码输出数据(TPD07)8个时钟周期3.HDB3编码信号中同步时钟分量定性观测(1)通过KX02的设置,产生7位周期m序列;KP02设置在HDB3位置;KD01设置为输入m序列;KD02分别设置为单极性码输出和双极性码输出。

用示波器观测如下数据:♦M序列,单极性码时同步时钟分量(TPP01)♦M序列,双极性码时同步时钟分量(TPP01)♦M序列,双极性码时放大后同步时钟分量(TPP02)(2)KD01设置为输入全1序列。

用示波器观测如下数据:♦全1序列时单极性码时同步时钟分量(TPP01)(3)KD01设置为输入全0序列。

用示波器观测如下数据:得到了正弦信号。

结论:●HDB3单极性码含有时钟分量;双极性码不含有时钟分量或是较少的时钟分量。

●HDB3码是否含有时钟分量与发送的序列无关,无论是M序列,全0码,全1码4.HDB3译码位定时恢复测量(1)通过KX02的设置,产生7位周期m序列;KP02设置在HDB3位置。

hdb3码型变换实验实验报告HDB3码型变换实验实验报告引言:HDB3码型变换是一种常用的数字信号处理技术,用于在数字通信中传输数据。

本实验旨在通过实际操作,探索HDB3码型变换的原理和应用。

一、实验目的本实验的主要目的是通过实际操纵,了解HDB3码型变换的基本原理和应用,掌握其编码和解码的过程,并通过实验验证其正确性和可靠性。

二、实验原理HDB3码型变换是一种常用的数字信号处理技术,用于在数字通信中传输数据。

它通过对原始数据进行编码,将其转换为特定的信号格式,以便在传输过程中保持信号的稳定性和可靠性。

HDB3码型变换的原理基于两个基本概念:零值替代和脉冲宽度调制。

在HDB3编码中,连续的零值被替换为特定的非零值,以保持传输信号的直流平衡。

同时,脉冲宽度调制技术用于保持信号的稳定性,通过对信号的脉冲宽度进行调整,确保传输过程中的信号完整性。

三、实验步骤1. 准备实验所需材料和设备,包括计算机、HDB3码型变换器等。

2. 连接计算机和HDB3码型变换器,确保信号传输的正常连接。

3. 打开HDB3码型变换器软件,进入编码界面。

4. 输入待编码的原始数据,根据实验要求选择编码方式。

5. 点击“编码”按钮,开始进行HDB3码型变换编码。

6. 观察编码结果,并记录下来。

7. 进行解码实验,将编码结果输入到解码界面。

8. 点击“解码”按钮,进行HDB3码型变换解码。

9. 观察解码结果,并与原始数据进行对比。

10. 分析实验结果,总结HDB3码型变换的特点和应用。

四、实验结果与分析通过实验,我们得到了一组编码结果和解码结果。

经过对比和分析,我们发现HDB3码型变换具有以下特点:1. HDB3码型变换能够有效地保持信号的直流平衡,避免了传输过程中信号的漂移和失真。

2. HDB3码型变换通过替换连续的零值,减少了传输信号中的冗余信息,提高了信号传输的效率。

3. HDB3码型变换的解码过程较为简单,能够快速还原原始数据。

第30卷 第6期2007年12月电子器件Ch inese Jou r nal Of Elect ro n DevicesVol.30 No.6D ec.2007Encoder Circuits Im plementation of H DB3B a sing on FP GAC H E Ron g1,2,33,L IU Bo 1,CA O J i an 2zho n g11.Xi ’an Insti t ute of Opt ics an d P recisi on Mechanics ,Chi nese Academy of Sci ences ,Xi ’an 710068,Chi na;2.Gra duate s chool of t he Chi nese Academy of Sci ences ,B ei j i ng 100039,Chi na;3.Xi ’an Communicati ons Ins ti t ute of P.L.A ,Xi ’an 710106,Chi naAbstract :In order to meet demands in t he wireless t ransmi ssion syst em ,e g.no di rect current ,less low f re 2quence spect rum ,picki ng 2up ti ming signal easily ,and capable to correct i t self ,choo se high densit y bina ry 23(HDB3)code.Int roduce t he e ncoder principle and anal yse t he advantage s of HDB3.Then ,ba si ng Field Programmable Gate Ar ra y (F P G A),Cyclone EP1C3T100of AL TERA.i nc ,i mplement t he encoder cir 2cuit s of HDB3.Through sim ulati ng ,it have bee n fo und t hat output wave f rom si mulat ing circuit s are ac 2cording wit h t he encoder t heo ry.Thi s met hod ca n appl y t o t he com municat ion t ransmi ssion system.K ey w or ds :wirel ess t ransmission ;code sel ection ;HDB3;FP GA EEACC :6120B基于FPGA 的H D B3编解码电路的实现车 嵘1,2,33,刘 波1,曹剑中11.中国科学院西安光学精密机械研究所,西安710119;2.中国科学院研究生院,北京100039;3.中国人民解放军西安通信学院,西安710106收稿日期226作者简介车 嵘(2),女,硕士研究生,讲师,年于中国人民解放军张家口通信学院获无线通信专业军事学学士学位,现就读于中国科学院西安光学精密机械研究所,研究方向为无线通信、硬件电路设计,5@y 摘 要:为了满足无线信道中传输码型无直流分量、较少低频分量,以及便于提取定时信息和具有检错能力等要求,选择了三阶高密度双极性码(H DB3).介绍了HD B3码的编解码原理,分析了H D B3码较其它码型所具有的优势,结合可编程逻辑器件集成度高,速度快,功耗低的特点,选用ALTERA 公司的Cy clon e 系列FPG A 芯片EP1C3T100进行HD B3编解码电路的实现.通过仿真,观察到电路各点的仿真输出波形与H DB3码的理论输出值一致.该方法可满足实际的通信系统传输要求,具有实际应用价值.关键词:无线传输;码型选择;HD B3;FP GA ;中图分类号:TM787 文献标识码:A 文章编号:100529490(2007)0622148204 在一般的数字通信系统中首先将消息变为数字基带信号,称为信源编码[123],经过调制后进行传输,在接收端解调后恢复出基带信号,再进行解码转换为原始消息.实际的基带传输系统中,并不是所有电波均能在信道中传输.基带信号频谱中含有丰富的低频分量乃至直流分量,当数字信号进行长距离传输时,高频分量的衰减又随距离的增大而增大,电缆中线对之间的电磁辐射也随着频率的增高而加剧,从而限制了信号的传输距离和传输质量.同时信道中存在的隔直流电容和耦合变压器,阻止了直流分量的传输并对低频分量有较大的衰减.因此,对于一般信道高频和低频部分均是受限的.这就出现了基带信号码型的选择问题.对于传输信道,要求线路传输码型的频谱不含直流分量,并且只有很少的低频分量和高频分量.其次,一般的传输系统中,为了节省频带是不传输定时信息的,必须在接受端从相应的基带信号中加以提取.因而传输码型应利于收端定时时钟的提取,满足接收端再生原始信息时的需要.再次,码型应具有一定的规律性,有一定的误码检测能力.8:2007010:19792001cherr 4ahoo.co .现场可编程门阵列FP GA(Fiel d Progra mma2 bl e G at e A rray)是可以由电路设计者根据设计要求,借助于F P G A开发工具对其编程,以实现各种数字电路逻辑功能[728].确定逻辑功能的逻辑器件利用F P G A内部的逻辑结构,可以实现任何复杂的组合逻辑电路和时序电路,是实现数字电路的理想器件,在现代数字通信领域有着极其广阔的应用前景.本文选择的传输码型为HDB3码,由NRZ码经编码电路得到,硬件电路是基于AL TERA公司的Cy2 clone系列F P G A芯片EP1C3T100实现的.Cy2 clone系列F P G A基于成本优化的、全铜工艺的1.5 V SRAM工艺,但依然能够提供强大的功能. EP1C3T100提供了2910个逻辑单元,59904个RAM,并提供1个全功能的锁相环(PLL),最大I/O 达到了104个,完全满足本设计的要求.1 传输码型单极性非归零码NRZ,采用高电平和低电平(一般为零电平)分别表示二进制信息“1”和“0”,在整个码元期间电平保持不变,由于直流分量的存在将导致信号失真、畸变且无法使用一些交流耦合的线路和设备,另外,不能直接提取位同步信息,以及抗噪性能较差等,所以不适合在信道中传输,必须将其转换成适合的码型.传号交替反转码AMI(Alt er2 nat e Mark Inve rsion),信码“0”用0电平表示,信码“1”交替用“+1”和“-1”的归零码表示,其脉冲宽度τ与码元宽度T s的关系是τ=0.5T s,所以AMI码无直流分量,低频分量也较小,经过必要的非线性处理可提取定时信号,并具有一定的检错能力,所以适合于信道传输.但是,AMI码有一个重要的缺点,当它用来获取定时信息时,由于可能出现长的连0串,会造成提取定时信号的困难.三阶高密度双极性码HD B3(H i gh Densit y Bina2 ry23)码是AMI码的一种改进型,主要是为了克服AMI码中连“0”时所带来的提取定时信息的困难.其编码原理是:检查已变换为AMI码后的信码序列中连“0”的情况.当输入码流连“0”小于或等于3个时,用0表示信息“0”,用B+和B-交替表示信息“1”;当输入码流中出现4个或4个以上连“0”码时,以每4个连“0”码为一组,将每组中第4个“0”位变换成非“0”码.这个由“0”码改变来的非“0”码称为破坏符号,用符号V表示,而原来的二进制码元序列中所有的“1”码(用符号B表示)称为信码.当信码序列中加入破坏符号以后,信码B与破坏符号V的正负极性必须满足如下两个条件:①B码和V码各自都应始终保持极性交替变化的规律,以便确保编好的码中没有直流成分;②V码必须与前一个非“”码(信码B)同极性,以便和正常的MI码区分开来如果这个条件得不到满足,那么应该在4个连“0”码的第一个“0”码位置上加一个与V码同极性的补信码,也用符号B 表示,并做调整,使B码满足条件①中信码极性交替变换的规律.总结以上,即每4个连“0”码组用取代码“000V-”、“000V+”、“B-00V-”和“B+00V+”来代替.其中取代码的选取规则是:使任意两个相邻破坏点V码间的B码个数为奇数(0算偶数).其表格形式如图1所示.前一个"V"码的极性前一个取代码后"1"的个数奇数 偶数V+000V-B-00V-V-000V+B+00V+图1 HDB3码取代规则假设信息码为0000000110100001,对应的NR Z码、AMI码、HDB3码码型如图2示.图2 NR Z,AMI,HD B3码型图HDB3码保持了AMI码的优点,克服了AMI码在遇到连“0”长时难以提取定时信息的困难,因而获得广泛应用,已成为CCITT推荐使用的码型之一.AMI码及HDB3码的功率谱如图3所示,他们都不含有离散谱f s成份(f s=1/T s,等于位同步信号频率).但为了译码时能够提供位同步信号使得在通信终端将他们译码为NR Z码,送给数字终端机或数/模转换电路,一般将AMI或HDB3码数字信号先进行整流处理,得到占空比为0.5的单极性归零码(RZ|τ=0.5T s),这种信号的功率谱也在图3中给出.由于整流后的AMI,HDB3码中含有离散谱f s,故可用一选频网络得到频率为f s的正弦波,经整形、限幅、放大处理后即可得到位同步信号.图3 AM I,HDB3,RZ|τ=0.5T s频谱图 DB3码编解码原理和电路 DB3码编码D B3码编解码原理和电路根据上述D B3码的9412第6期车 嵘,刘 波等:基于FP GA的HDB3编解码电路的实现8A.2H2.1HH H编码规则,可得到如图4所示的H D B3码编码电路.图4 HDB3编码电路 该电路主要由四连“0”检测、取代码选取、输出极性控制和单/双极性变换电路等组成.当码型选择输入HDB3/AM I为高电平时,为HDB3码编码,否则为AMI码编码.触发器D1~D4和门电路YF I、YF2构成四连“0”检测电路,输入为单极性不归零信息码流DA TA2NRZ,码型选择输入HDB3/AMI 为高电平.当输入信息码流中未出现四连“0”时,与非门YF2输出为高电平,与非门YF1输出与输入码流DA TA2N RZ相同.当输入信息码流中出现四个连“0”时,与非门YF2输出宽度为一个时钟周期的负脉冲,该负脉冲作为后接的取代码选取和输出极性控制电路的控制信号;与非门YF1输出宽度为一个时钟周期的正脉冲,完成插入V脉冲的功能.门电路Y1、Y3、H F2、YH2和触发器D6组成取代码选取电路.根据HDB3编码规则,当两次插入的V 脉冲之间“1”脉冲的个数为奇数时,则不插入B脉冲;若“1”的个数为偶数个(包括个数0)时,则需要插入B脉冲.两个V脉冲间的“1”脉冲个数由触发器D6和异或门YH2组成的模2计数器计数.当两个V脉冲间有偶数个“1”时,选“B00V”作为取代码;当两个V脉冲间有奇数个“1”时,选“000V”作为取代码,从而完成取代码的选取功能.门电路Y1、Y2、YH1和触发器D5组成输出极性控制电路,将异或门HF2输出按插入B脉冲极性与前一脉冲极性相反和插入V脉冲极性与前一脉冲极性相同的编码规则,分别送往与门Y4、Y5,以得到正负极性分开的两路单极性归零+HD B3和-HDB3信号.两路单极性+HDB3和-HDB3信号使开关管在正脉冲期间交替导通,经输出脉冲变压器完成单极性.双极性信号变换后,形成双极性HDB3码,送往传输线路.编好的HDB3码在时钟CP的作用下,滞后4bi t 输出.2.2 H DB3码解码虽然HD B3码的编码规则比较复杂,但译码却比较简单.从编码原理可以看出,每一破坏符号总是与前一非“0”符号同极性.据此,从收到的符号序列中很容易找到破坏点V,于是断定V符号及其前面的3个符号必定是连“0”符号,从而恢复4个连“0”码,再将所有的+1、-1变成“1”后便得到原信息代码.其解码电路就是完成上述编码的逆处理,首先将单路双极性HD B3码码流转换成正、负极性分开的两路单极性+HDB3和-HD B3信号,然后检出插入的V脉冲和B脉冲,将取代码“000V”或“B00V”还原成原信息“0000”.HD B3解码电路如图5所示.图5 DB3解码电路 解码电路主要由双单极性变换、V脉冲检测、取代码消除电路等组成码型选择输入DB3MI为高电平,为DB3码解码从传输线路收到的双极性D B3码,先由输入变压器完成D B3码双极性单0512电 子 器 件第30卷8H/.H/AH.H H-极性信号变换,经整形分离成两路单极性+HD B3和-HD B3信号.触发器D 1和D 2将输入的单极性归零+HD B3和-HD B3码转换为单极性不归零码元.触发器D 3和与非门YF 1、YF 2组成V 脉冲检测电路.当HD B3码流中无V 脉冲时,与非门YF 1和YF 2输出为高电平;当HDB3码流中有V 脉冲时,与非门YF 1和YF 2输出为低电平.触发器D 4~D 7和与非门YF 3~YF 5组成取代码消除电路.解码后的数据码流在时钟CP 的作用下滞后4bit 输出.3 H DB3码编解码电路的F P GA 实现HDB3码的编解码硬件实现有很多种方式,这里选用现场可编程门阵列(F P G A )实现其编解码电路.FP GA 是可编程逻辑器件,它是在PAL ,G AL 等逻辑器件的基础之上发展起来的.同以往的PAL ,GAL 等相比较,选用FP GA 器件的主要优点[7]是:①F P G A 集成度高,一片F P G A 可替代大量中小规模的数字电路集成芯片;②提高电路的可靠性;③F P G A 具有可擦除可多次编程的能力,使得在电路设计阶段,由于设计错误和设计要求变更时,只需修改原设计文件再对FP GA 重新编程即可,提高数字电路设计的灵活性;④缩短设计周期,降低设计成本;⑤可建立仿真测试向量,对设计电路进行仿真分析,检验设计电路的正确性.这里借助AL T ERA 公司的Quart usII 开发软件[9],具体设计实现的主要步骤如下所述.3.1 设计输入利用Qua rt usII 的图形编辑器输入HDB3编码和解码的电路,然后进行原理图编译,编译通过后,建立一个逻辑宏元件符号,以供更高层次数字通信系统设计时反复调用.编译完成后再设计一个仿真输入源,以完成对电路逻辑功能及时序的仿真.3.2 设计仿真设计仿真的目的是通过对设计电路施加所有可能的输入来测试其输出响应,以验证设计电路是否符合设计要求.HDB3编码和解码电路设计仿真波形如图6所示.从图中可看到,电路各点的输出波形() DB3编码仿真波形(b) AM I 编码仿真波形(c ) HDB3解码仿真波形(d )AM I 解码仿真波形图6 仿真波形与前述HDB3编解码电路原理相同.3.3 FP G A 编程下载FP G A 下载的目的是让所选器件实现预定的逻辑功能.由Quart us II 的Programmer 功能通过J T AG 接口将设计文件下载到芯片,进行板级功能仿真.4 结论本文给出了HDB3码的编译码电路实现方法,并基于F P G A 进行了实现及仿真.由输出的仿真信号波形及实际硬件电路测试,信号波形、频谱符合理论分析,既可满足教学实验的现象观察,加深对信道编译码原理的理解,也可满足实际通信系统的传输要求,可进一步用于E1等通信系统中的信源编码,具有很实际的应用价值.参考文献:[1] 樊昌信,詹道庸,徐炳祥,等.通信原理[M ].第4版.北京:国防工业出版社,1998.[2] 罗伟雄,韩力,原东昌,等.通信原理与电路[M ].北京:北京理工大学出版社,2000.[3] 曹志刚,钱亚生.现代通信原理[M ].北京:清华大学出版社.1992.[4] 张新政.现代通信系统原理[M ].北京:电子工业出版社,1995.[5] 谢自美.电子线路设计、实验、测试[M ].第2版.武汉:华中科技大学出版社,2001.[6] 郭世满,叶奔和,钱德馨.数字通信[M ].北京:人民邮电出版社,1995.[7] 王诚,吴继华,范丽珍,薛宁,薛小刚,等.Alt era FPGA/CPL D设计[M].北京:人民邮电出版社,2005.[8] 褚振勇,翁木云.FP GA 设计及应用[M ].西安电子科技大学出版社[] Q II V 5[B OL ][] y D F y D S [B OL ]1512第6期车 嵘,刘 波等:基于FP GA 的HDB3编解码电路的实现8a H .2002.9ua rt us er sio n .0Ha ndbook.A lt e ra Corpora tio n E /.ht t p ://w w w.a lt e ra.co m.10C clone evice a mil a t a he et Al t era Corpora tio n E /.ht t p ://w w w.a lt e ra .co m.。

1 一、 设计总体思路 1.引言 随着远距离通讯技术的发展,现代通信通常借助于电和光来传输信息,数字终端产生的数字信息是以“1”和“O”二种状态代表的随机序列,它可以用不同形式的电信号表示,从而构造不同形式的数字信号。在一般的数字通信系统过程中,首先将所需传输的消息信号转化为相对应的数字基带信号,即信源的编码,经过调制信号与信道相匹配后再进行传输,在接收端先进行解调恢复为基带信号,再进行解码转换为原始消息。但在实际的基带传输系统中,信道的低频传输特性差容易受噪声的干扰,可能造成信号严重畸变,甚至可能被噪声完全淹没而分不出信号,因此有必要对传输的信号进行编码,而经过信道编码后的传输码却具有较强的波形抗干扰性。我们比较常用的编码规则有AMI和 HDB3编码。 AMI 码,又名符号交替反转码,其编码规则是:若用“0”和“1”代表传号和空号“, 0”码不变“, 1”码则交替地转换为+1 和-1。通常脉冲宽度为码元宽度的一半, 这种码型交替出现正、负极脉冲,所以无直流分量,低频分量也很少。这种码的反变换也很容易,在再生信码时,只要将信号整流,即可将“-1”翻转为“+1”,恢复成单极性码。AMI 码的缺点是,当原信码出现长连“0”串时,信号的电平长时间不跳变,造成提取定时信号的困难,解决连“0”码问题的有效方法之一是采用HDB3 码。

2.HDB3编译码 HDB3码的全称是3阶高密度双极性码,它是AMI码的一种改进型, 其目的是为了保持AMI码的优点而克服其缺点, 使连“0”个数不超过3个。其编码规则如下:

(1) 当信码的连“0”个数不超过3时,仍按AMI码的规则编,即传号极性交替;

(2)当连“0”个数超过3时,则将第4个“0”改为非“0”脉冲,记为+V或-V,称之为破坏脉冲。相邻V码的极性必须交替出现,以确保编好的码中无直流; 2

(3)为了便于识别, V码的极性应与其前一个非“0”脉冲的极性相同,否则,将四连“0”的第一个“0”更改为与该破坏脉冲相同极性的脉冲,并记为+B或-B;

(4) 破坏脉冲之后的传号码极性也要交替。 例如: 代 码: 1000 0 1000 0 1 1 000 0 l 1 AMI 码: -1000 0 +1000 0 -1 +1 000 0 -1 +1 HDB3码: -1000 -V +1000 +V -1 +1 -B00 -V +1 -1 其中的±V脉冲和±B脉冲与±1脉冲波形相同,用V或B符号的目的是为了示意是将原信码的“0”变换成“1”码。

虽然HDB3码的编码规则比较复杂,但译码却比较简单。 从上述原理看出,每一个破坏符号V总是与前一非0符号同极性(包括B在内)。

这就是说,从收到的符号序列中可以容易地找到破坏点V,于是也断定V符号及其前面的3个符号必是连0符号,从而恢复4个连0码,再将所有-1变成+1后便得到原消息代码。HDB3码保持了AMI码的优点外,还将连“0”码限制在3个以内,故有利于定时信号的提取。

HDB3编译码原理框图如图1-1所示: 3

相加器 0000取代 译码输出 带通

双—单极性变换 (+-两路输出)

破坏点检测

锁相环 译码电路 限幅 放大 译码CLK 图1-1HDB3设计总方框图

连零检测电路 RNZ码输入 000V取代 B00V取代 奇偶判断电路 破坏点产生 单—双极性变换(+-两路输入)

编码电路 4 二、单元电路的设计 1、编码器功能模块电路 编码电路接收终端机来的单极性非归零信码, 并把它变换成为HDB3 码送往传输信道。HDB3 码编码部分的原理框图如图2-1(a) 所示,电路图如2-2(b),(c)所示。

图2-1(a)编码电路方框图 (1)单极性信码进入电路,首先检测有无四连“0”码。没有四连“0”时,信码不改变地通过本电路;有四连“0”时,在第四个“0”码出现时,将一个“1”码放入信号中,取代第四个“0”码,补入“1”码称为V 码。 (2) 取代节选择及补B 码电路(取代节判决)电路计算截至当前时刻所发送的码中1的总数的奇偶性,若1的总数为偶数 ,则当V码来的时候不作改变;若1的总数为奇数,则当V码来的时候将000V 中的第一个“0”改为“1”,即此时用“B00V”取代节,同时也将1码的总数由奇数变成了偶数。这样做保证了两个V码之间的1码的数量始终为奇数。 (3)破坏点形成电路将补放的“1”码变成破坏点。方法是在取代节内第二位处再插入一个“翻转”信号,使单/双极性变换电路多翻转一次,后续的V码就会与前面相邻的“1”码极性相同,破坏了交替反转的规律,形成了“破坏点”。 (4)单/双极性变换电路电路中的输出控制加入了取代节的信号码流, 使其按交替翻转规律分成两路,再通过一个开关电路(CD4052芯片)将两路信号整合成一路便是我们所需要的HDB3码。 图2-2(b) 单-双极性转换电路

连零检测电路 RNZ码输入 000V取代 B00V取代 奇偶判断电路 破坏点产生 单—双极性变换(+-两路输入)

X012X114X215X311Y01Y15Y22Y34A10B9INH6X13Y3405240525V-5VHDB3+HDB3-HDB3 5

图2-2(c)编码电路 NRZ码:1 0 1 0 0 1 1 0 1 1 0 0 1 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 HDB3-D:0 0 0 1 1 0 1 0 0 1 1 0 1 1 0 0 1 0 0 0 1 1 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 从上图可知,NRZ码经过编码电路后,延时4个时钟信号得到了HDB3码 2、双-单极性变换电路 该部分由整流器和相加器组成,整流器由两个充放电路构成,相加器用一个或门表示。电路如图2-2所示。 (1)整流电路

NRZ +HDB3 -HDB3 6

充放电路的充电和放电的时间常数不同,充电时,C1支路快于C2支路,放电时,C2支路快于C1支路。当输入码元为+1时,通过C1支路充电,当输入码元为0或-1时通过C2支路放电。然后通过非门便将双极性归零码变成了单极性的归零码。 (2)相加电路 用或门将两路信号整合成一路信号后便于位同步信号的提取。

C10.1UF

C20.1UF

R15k

R21k

R35k

R41k

5VHDB3U25NOTU26NOT

U27NOT

U28ORHDB3-D

图2-2双-单极性转换 3、位同步信号的提取 数字信号传输过程中,收发两端一定要有一个时间上同步的问题。发端某一时刻发出一个码元,收端在相应某一时刻(一般滞后一个固定时间)抽样判决后再生这个码元,这样收发两端的码元一一对应不会搞错。在本单元电路中,位同步信号的离散谱来自上一级的整流后的信号,由于位同步频率比较低,很难将有源带通滤波器的带宽做得很窄,它输出的BPF信号是一个幅度和周期都不恒定的正弦信号,对此信号进行限幅放大处理后得到幅度恒定、周期变化的脉冲信号,但仍不能将此信号作为译码器的位同步信号,需要进一步处理,当锁相环自然谐振频率足够小时,对输入的电压信号可等效为窄带带通滤波器,它可以输出一个符合译码要求的位同步信号BS—R。

图2-3(a)位同步信号提取方框图 带通 限幅放大 锁相环 BSR HDB3D 7

R540k

R62k

C31nF

C41nFR740k

R840k3267415U297413267415U30741R940kR1010kR115k

BPFVCC

-5VHDB3-D

VCC

-5V

图2-3(b)带通滤波器电路

32674518U31LM318R125kR135kR14100kCOMPIN3VCOIN9SIGIN14CX16CX27INH5R111R212PP1PC1OUT2PC2OUT13

VCOOUT4DEMOD10ZENER15U324046C5100pFR151kX110uX2100uR16100kBPFVCC

-5VBS-RHD 图2-3(c)放大限幅及锁相环电路 4、译码器功能模块电路 相对于编码电路来说,译码电路显得相对简单很多,当电路检测到破坏点后将破坏点及其前面的三个码元用“0000”取代即可。其原理方框图如图2-4(a)所示,电路图如2-4(b)所示。

图2-4(a)译码电路方框图 相加器 0000取代 译码输出 双—单极性变换 (+-两路输出)

破坏点检测 8

图2-4(b)译码电路图 NRZ码:1 0 1 0 0 1 1 0 1 1 0 0 1 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 解码为:0 0 0 0 0 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 从上图可知,解码输出延时6.5个时钟信号后,得到了原NRZ码。

NRZ 解码输出