安阳工学院

电子信息与电气工程学院

课程大作业:EDA技术

题目:

组数:第11 组

班级:(电子信息工程10-1)

教师成绩由以下评分标准累计得出

1、电路设计和仿真结果正确清晰合理‘25%

2、设计和仿真结果分析正确合理。25%

3、大作业报告重点突出、阐述清晰。25%

4、小组能很好的组织、合作,过程顺利,按时完成大作业。15%

5、陈述清晰正确、有说服力,能够正确回答问题。10%

总分

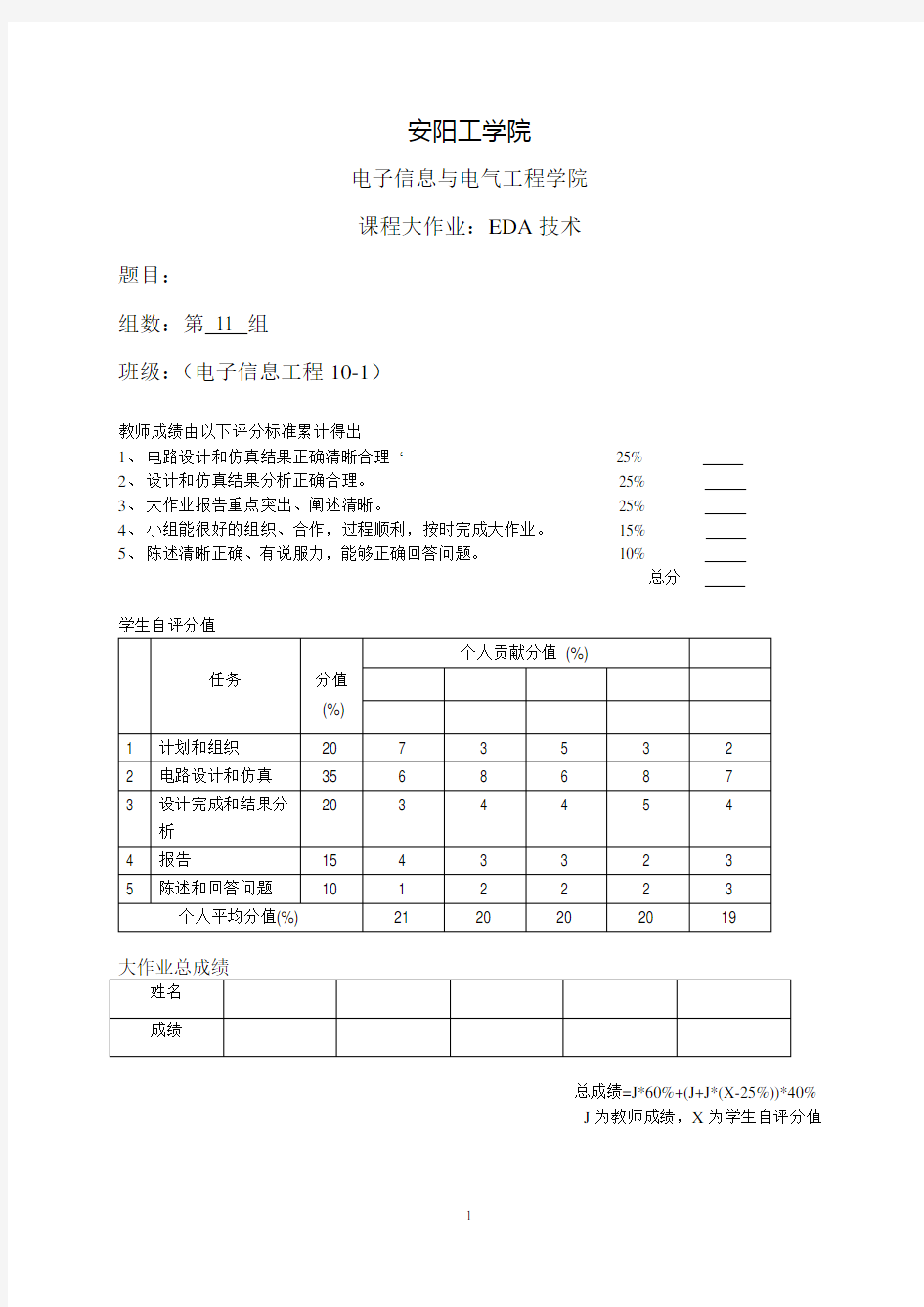

学生自评分值

个人贡献分值(%)

任务分值

(%)

1 计划和组织20 7 3 5 3 2

2 电路设计和仿真35 6 8 6 8 7

3 设计完成和结果分

20 3 4 4 5 4

析

4 报告1

5 4 3 3 2 3

5 陈述和回答问题10 1 2 2 2 3

个人平均分值(%) 21 20 20 20 19

大作业总成绩

姓名

成绩

总成绩=J*60%+(J+J*(X-25%))*40%

J为教师成绩,X为学生自评分值

数字时钟

1. 设计任务和设计方案

1.1设计任务

1、依据预先设定的数字数字时钟的功能,完成对数字钟的设计。

2、通过数字时钟的设计,学习Quartus II 中基于VHDL 设计的流程。

3、通过这次的设计,掌握简单时序逻辑电路的设计方法与功能仿真技巧。

1.2 设计方案

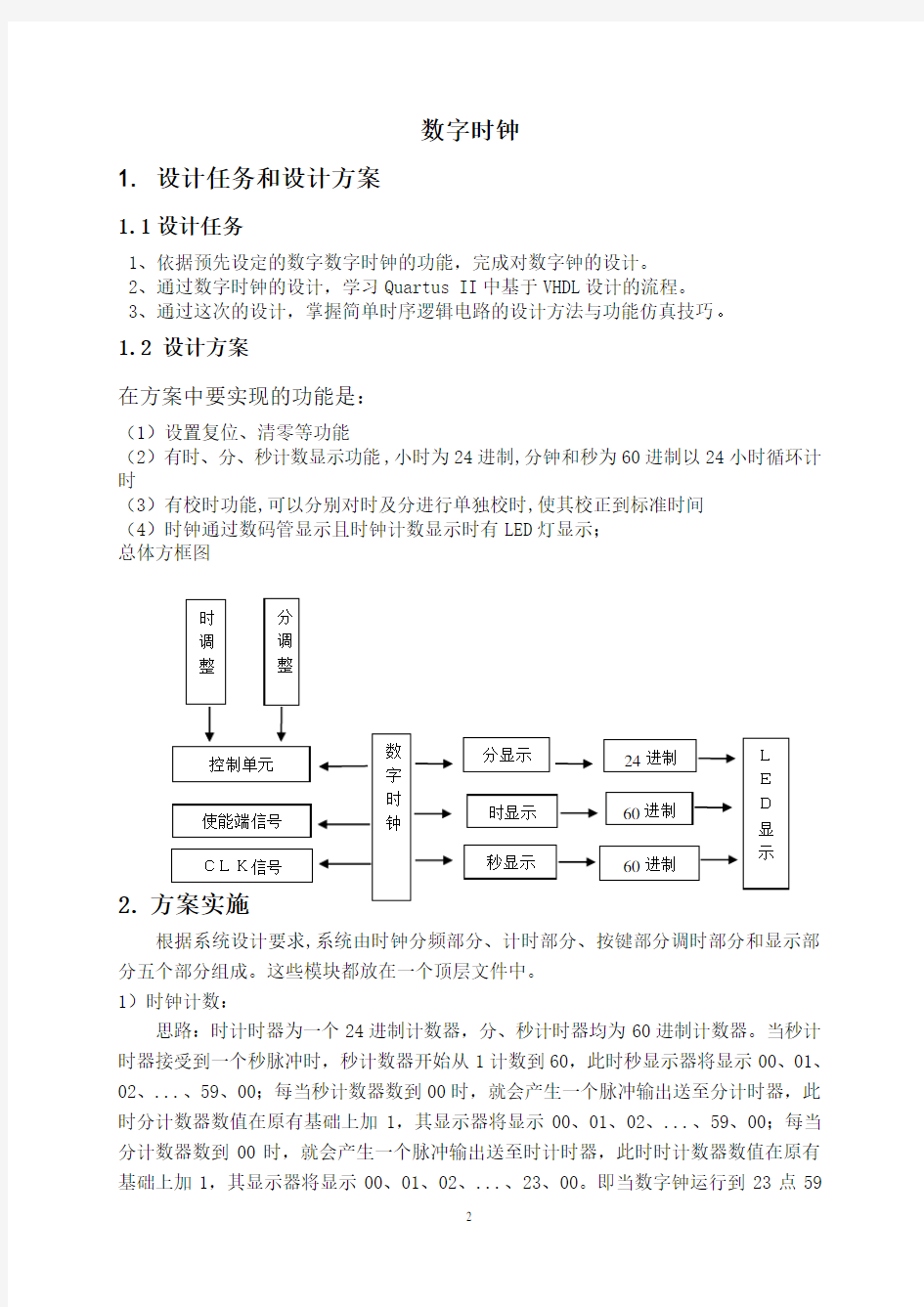

在方案中要实现的功能是:

(1)设置复位、清零等功能

(2)有时、分、秒计数显示功能,小时为24进制,分钟和秒为60进制以24小时循环计时

(3)有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间 (4)时钟通过数码管显示且时钟计数显示时有LED 灯显示; 总体方框图

2. 方案实施

根据系统设计要求,系统由时钟分频部分、计时部分、按键部分调时部分和显示部分五个部分组成。这些模块都放在一个顶层文件中。 1)时钟计数:

思路:时计时器为一个24进制计数器,分、秒计时器均为60进制计数器。当秒计时器接受到一个秒脉冲时,秒计数器开始从1计数到60,此时秒显示器将显示00、01、02、...、59、00;每当秒计数器数到00时,就会产生一个脉冲输出送至分计时器,此时分计数器数值在原有基础上加1,其显示器将显示00、01、02、...、59、00;每当分计数器数到00时,就会产生一个脉冲输出送至时计时器,此时时计数器数值在原有基础上加1,其显示器将显示00、01、02、...、23、00。即当数字钟运行到23点59

时 调 整

分 调 整

控制单元 使能端信号 CLK信号

数字时钟

LED显示

秒显示

时显示 分显示 60进制 60进制

24进制

分59秒时,当秒计时器在接受一个秒脉冲,数字钟将自动显示00点00分00秒。

实现:首先下载程序进行复位清零操作,电子钟从00:00:00计时开始。sethour可以调整时钟的小时部分, setmin可以调整分钟,步进为1。由于电子钟的最小计时单位是1s,因此提供给系统的内部的时钟频率应该大于1Hz,这里取100Hz。CLK端连接外部10Hz的时钟输入信号clk。对clk进行计数,当clk=10时,秒加1,当秒加到60时,分加1;当分加到60时,时加1;当时加到24时,全部清0,从新计时。用6位数码管分别显示“时”、“分”、“秒”,通过OUTPUT( 6 DOWNTO 0 )上的信号来点亮指定的LED七段显示数码管。

2)时间设置:

思路:当开关拨至校时档时,电子钟秒计时工作,通过时、分校时开关分别对时、分进行校对,开关每按1次,与开关对应的时或分计数器加1,当调至需要的时与分时,拨动reset开关,电子钟从设置的时间开始往后计时。

实现:手动调节分钟、小时,可以对所设计的时钟任意调时间,这样使数字钟真正具有使用功能。我们可以通过实验板上的键7和键4进行任意的调整,因为我们用的时钟信号均是1HZ的,所以每LED灯变化一次就来一个脉冲,即计数一次。

3)清零功能:

reset为复位键,低电平时实现清零功能,高电平时正常计数。可以根据我们自己进行任意时间复位。

原理图

3.结果和结论

实验箱使用模式7,键8为复位按键,键8为1时正常工作。键4设置小时,键7

设置分钟。

下载成功后,按下键8,及使六个LED复位清零,显示数秒的自动计时,可以通过4键设置小时数,7键设置分钟数。当秒数满60则进一位,分钟数满60进一位,当显示为23:59:59时,秒数在加一则显示00:00:00,之后从新计时。

仿真结果及分析

时序仿真

建立波形文件:选择 File→New→Other File→Vector Waveform File→Name→Insert Nod or Bus→Node Finder→ Pins→List→单击“>>”(所有输入/输出都被拷贝到右边的一侧,这些正是我们希望的各个引脚,也可以只选其中的的一部分,根据实际情况决定)→OK

设定仿真时间宽度:选择 Edit → End time…在End time选择窗中选择适当的仿真时间域,以便有足够长的观察时间。

波形文件存盘:选择File→Save as 选项,直接存盘即可。

运行仿真器:在菜单中选择项,直到出现,仿真结束。

1.秒时序仿真图

2.分时序仿真图

3.小时时序仿真

4.显示时序仿真

4,分析与心得

这次的EDA实验设计报告我们做的是时钟电路,采用了自顶向下设计方法。由时钟分频部分、计时部分、按键部分调时部分和显示部分五个部分组成。通过手动调节分钟、小时,可以对所设计的时钟任意调时间,这样使数字时钟真正具有使用功能。通过这次实验设计,让我们对EDA有了更深刻的认识,加深了同学之间探讨问题的积极性,增强了动手解决问题的能力。同时,提高了我们学习这门课程的热情。在此,感谢李老师给我们这次机会,能让我们在这貌似枯燥的课本理论知识里发现了甘露。

5.任务分工

翟扬帆进行程序的仿真

曾凡超绘制原理图

杨鹏程序的编写与调试

李许彦依据功能,设计方案模块

仲李岸整理报告

6.参考文献

[1]潘松黄继业EDA技术实用教程(第四版)科学出版社2010年6月7.附录

VHDL源程序

秒计数模块的VHDL源程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity second is

port(clk,reset,semin:in std_logic;

enmin:out std_logic;

daout:out std_logic_vector(6 downto 0));

end second;

architecture one of second is

signal count:std_logic_vector(6 downto 0);

signal enmin_1,enmin_2:std_logic;

begin

daout<=count;

enmin_2<=(semin and clk);

enmin<=(enmin_1 or enmin_2);

process(clk,reset,semin)

begin

if(reset='0')then

count<="0000000";

enmin_1<='0';

elsif(clk'event and clk='1')then

if(count(3 downto 0)="1001")then

if(count<16#60#)then

if(count="1011001")then

enmin_1<='1';count<="0000000";

else

count<=count+7;

end if;

else

count<="0000000";

end if;

elsif(count<16#60#)then

count<=count+1;

enmin_1<='0';

else

count<="0000000";enmin_1<='0';

end if;

end if;

end process;

end one;

分计数模块VHDL程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity minute is

port(clk,reset,clks,sethour:in std_logic;

enhour:out std_logic;

daout:out std_logic_vector(6 downto 0)); end minute;

architecture rtl of minute is

signal count:std_logic_vector(6 downto 0);

signal enhour_1,enhour_2:std_logic;

begin

daout<=count;

enhour_2<=(sethour and clk);

enhour<=(enhour_1 or enhour_2);

process(clk,reset,sethour)

begin

if(reset='0')then

count<="0000000";

enhour_1<='0';

elsif(clk'event and clk='1')then

if(count(3 downto 0)="1001")then

if(count<16#60#)then

if(count="1011001")then

enhour_1<='1';count<="0000000";

else

count<=count+7;

enhour_1<='0';

end if;

else

count<="0000000";

end if;

elsif(count<16#60#)then

count<=count+1;

enhour_1<='0' after 100 ns;

else

count<="0000000";enhour_1<='0';

end if;

end if;

end process;

end rtl;

时计数模块VHDL源程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity hour is

port(clk,reset:in std_logic;

daout:out std_logic_vector(5 downto 0)); end hour;

architecture rtl of hour is

signal count:std_logic_vector(5 downto 0);

begin

daout<=count;

process(clk,reset)

begin

if(reset='0')then

count<="000000";

elsif(clk'event and clk='1')then

if(count(3 downto 0)="1001")then

if(count<16#23#)then

count<=count+7;

else

count<="000000";

end if;

elsif(count<16#23#)then

count<=count+1;

else

count<="000000";

end if;

end if;

end process;

end rtl;

时间设置模块VHDL程序

library ieee;

use ieee.std_logic_1164.all; end process;

process(clk,reset)

begin

if(reset='0')then

daout<="0000";

dp<='0';

sel<="111111";

elsif(clk'event and clk='1')then

case count is

when"000"=>daout<=sec(3 downto 0);

dp<='0';

sel<="111110";

when"001"=>daout(3)<='0';

daout(2 downto 0)<=sec(6 downto 4); dp<='0';

sel<="111101";

when"010"=>daout<=min(3 downto 0);

dp<='1';

sel<="111011";

when"011"=>daout(3)<='0';

daout(2 downto 0)<=min(6 downto 4); dp<='0';

sel<="110111";

when"100"=>daout<=hour(3 downto 0);

dp<='1';

sel<="101111";

when"101"=>daout(3 downto 2)<="00";

daout(1 downto 0)<=hour(5 downto 4); dp<='0';

sel<="011111";

when others=>daout<="0000";

dp<='0';

sel<="111111";

end case;

end if;

end process;

end rtl;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity settime is

port(clk,reset:in std_logic;

sec,min:in std_logic_vector(6 downto 0);

hour:in std_logic_vector(5 downto 0);

dp:out std_logic;

sel:out std_logic_vector(5 downto 0);

daout:out std_logic_vector(3 downto 0));

end settime;

architecture rtl of settime is

signal count:std_logic_vector(2 downto 0);

begin

process(clk,reset)

begin

if(reset='0')then

count<="000";

elsif(clk'event and clk='1')then

if(count>="101"hen

count<="000";

else

count<=count+1;

end if;

end if;

译码显示模块的VHDL程序(deled.vhd)library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity deled is

port(num: in std_logic_vector(3 downto 0);

led: out std_logic_vector(6 downto 0));

end deled;

architecture rtl of deled is

begin

led<="1111110"when num="0000"else

"0110000"when num="0001"else

"1101101"when num="0010"else

"1111001"when num="0011"else

"0110011"when num="0100"else

"1011011"when num="0101"else

"1011111"when num="0110"else

"1110000"when num="0111"else

"1111111"when num="1000"else

"1111011"when num="1001"else

"1110111"when num="1010"else

"0011111"when num="1011"else

"1001110"when num="1100"else

"0111101"when num="1101"else

"1001111"when num="1110"else

"1000111"when num="1111";

end rtl;

题 目: 数据挖掘 学 院: 电子工程学院 专 业: 智能科学和技术 学生姓名: ** 学 号: 02115*** k -means 实验报告 一、 waveform 数据 1、 算法描述 1. 从数据集{X n }n?1N 中任意选取k 个赋给初始的聚类中心c 1, c 2, …,

c k; 2.对数据集中的每个样本点x i,计算其和各个聚类中心c j的欧氏 距离并获取其类别标号: label(i)=arg min ||x i?c j||2,i=1,…,N,j=1,…,k 3.按下式重新计算k个聚类中心; c j=∑x j s:label(s)=j j ,j=1,2,…k 重复步骤2和步骤3,直到达到最大迭代次数为止2、实验结果 二、图像处理 1、算法描述 同上; 2、实验结果

代码: k_means: %%%%%%%%%K_means%%%%%%%% %%%%%%%%%函数说明%%%%%%%% %输入: % sample——样本集; % k ——聚类数目; %输出: % y ——类标(从0开始) % cnew ——聚类中心 % n ——迭代次数 function [y cnew n]=k_means(sample,k) [N V]=size(sample); %N为样本的个数 K为样本的维数 y=zeros(N,1); %记录样本类标 dist=zeros(1,k); rand_num=randperm(N); cnew=(sample(rand_num(1,1:k),:));%随机初始化聚类中心cold=zeros(k,V); n=0;

射频大作业 基于PSpice仿真的振幅调制电路设计数字调制与解调的集成器件学习

目录 题目一:基于PSpice仿真的振幅调制电路设计与性能分析 一、实验设计要求 (3) 二、理论分析 1、问题的分析 (3) 2、差动放大器调幅的设计理论 (4) 2.1、单端输出差动放大器电路 2.2、双端输出差动放大器电路 2.3、单二极管振幅调制电路 2.4、平衡对消二极管调幅电路 三、PSpice仿真的振幅调制电路性能分析 (10) 1、单端输出差动放大器调幅电路设计图及仿真波形 2、双端输出差动放大器调幅电路设计图及仿真波形 3、单二极管振幅调制电路设计图及仿真波形 4、平衡对消二极管调幅电路设计图及仿真波形 四、实验总结 (16) 五、参考文献 题目二数字调制与解调的集成器件学习 一、实验设计要求 (17) 二、概述 (17) 三、引脚功能及组成原理 (18) 四、基本连接电路 (20) 五、参考文献 (21) 六、英文附录 (21)

题目一基于PSpice仿真的振幅调制电路设计 摘要 随着大规模集成电路的广泛发展,电子电路CAD及电子设计自动化(EDA)已成为电路分析和设计中不可缺少的工具。此次振幅调制电路仿真设计基于PSpice,利用其丰富的仿真元器件库和强大的行为建模工具,分别设计了差分对放大器和二极管振幅调制电路,由此对线性时变电路调幅有了更进一步的认识;同时,通过平衡对消技术分别衍生出双端输出的差分对放大器和双回路二极管振幅调制电路,消除了没用的频率分量,从而得到了更好的调幅效果。本文对比研究了单端输出和双端输出的差分对放大器调幅电路及单二极管和双回路二极管调幅电路,通过对比观察时域和频域波形图,可知平衡对消技术可以很好地减小失真。 关键词:PSpice 振幅调制差分对放大器二极管振幅调制电路平衡对消技术 一、实验设计要求 1.1 基本要求 参考教材《射频电路基础》第五章振幅调制与解调中有关差分对放大器调幅和二极管调幅的原理,选择元器件、调制信号和载波参数,完成PSpice电路设计、建模和仿真,实现振幅调制信号的输出和分析。 1.2 实践任务 (1) 选择合适的调制信号和载波的振幅、频率,通过理论计算分析,正确选择晶体管和其它元件;搭建单端输出的差分对放大器,实现载波作为差模输入电压,调制信号控制电流源情况下的振幅调制;调整二者振幅,实现基本无失真的线性时变电路调幅;观察记录电路参数、调制信号、载波和已调波的波形和频谱。 (2) 参考例5.3.1,修改电路为双端输出,对比研究平衡对消技术在该电路中的应用效果。 (3) 选择合适的调制信号和载波的振幅、频率,通过理论计算分析,正确选择二极管和其它元件;搭建单二极管振幅调制电路,实现载波作为大信号,调制信号为小信号情况下的振幅调制;调整二者振幅,实现基本无失真的线性时变电路调幅;观察记录电路参数、调制信号、载波和已调波的波形和频谱。 (4) 参考例5.3.2,修改电路为双回路,对比研究平衡对消技术在该电路中的应用效果。 1.3 写作报告 (1) 按论文形式撰写,包括摘要、正文和参考文献,等等。 (2) 正文包括振幅调制电路的设计原理、理论分析结果、实践任务中各阶段设计的电路、参数、波形和频谱,对观察记录的数据配以图像和表格,同时要有充分的文字做分析和对比,有规律性认识。 (3) 论文结构系统、完备、条理清晰、理论正确、数据翔实、分析完整。 1.4 相关提示 (1) 所有电路和信号参数需要各人自行决定,各人有不同的研究结果,锻炼学生的独立研究和实验分析能力。 (2) 为了提高仿真精度和减小调试难度,可以将调制信号和载波的频率设置得较低。 二、理论分析 1、问题的分析 根据题目的要求,差分对放大器和二极管振幅调制电路目的都是实现基本无

《EDA技术基础》 实验报告 学院:信息科学技术学院 专业:电子信息工程 指导教师:龙翔 完成日期:2013年12月 目录 实验一MAX-plusll 及开发系统使用 (3) 实验二高速四位乘法器设计 (6)

实验三秒表的设计 (9) 实验四序列检测器的设计 (13) 实验五数字频率计的设计 (18) 六实验总结 (20) 实验一 一:实验名称: MAX-plusll 及开发系统使用

二:实验内容 1.利用MAX-plusII中的图形编辑器设计一半加器,进行编译、仿真, 并将其设置成为一元件。 2.建立一个更高的原理图设计层次,利用前面生成的半加器元件设计一个全加器,进行编译、仿真,并将其设置成为一个元件。 3.再建立一个更高的原理图设计层次,利用前面生成的半加器元件设计一个全加器,进行编译、仿真。 4.选择器件“Assign”“Device”“MAX7000S”“EPM7128SLC84-6”,并根据下载板上的标识对管脚进行配置。然后下载,进行硬件测试,检验结果是否正确。 三.实验程序 1).半加器图 2)全加器图

3)四位全加器 四:仿真图 1).半加器仿真图

2).全加器仿真图 3).四位全加器仿真图

实验二 一:实验名称 高速四位乘法器设计 二: 实验内容 1.利用MAX-plusⅡ中的图形编辑器设计1-4的二进制乘法器,进行编译、仿真,并将其设置成为一元件,命名为and14。 2.建立一个更高得原理图设计层次,利用前面生成的1-4的二进制乘法器和调用库中的74283元件设计一高速4位乘法器。 三:实验程序 1.

说明 每个实验题目含有一个main函数和一些函数,与实验题目相关的基本运算的函数定义和main函数定义的代码在附录以及对应的文件夹中给出,供上机实验参考使用。对于每个题目,只需要根据题目要求设计算法,补充函数定义,然后对程序进行编译、调试。

实验一线性表 一、实验目的 1.熟悉线性表的顺序和链式存储结构 2.掌握线性表的基本运算 3.能够利用线性表的基本运算完成线性表应用的运算 二、实验内容 1.设有一个线性表E={e1, e2, … , e n-1, e n},设计一个算法,将线性表逆置,即使元素排列次序颠倒过来,成为逆线性表E’={ e n , e n-1 , … , e2 , e1 },要求逆线性表占用原线性表空间,并且用顺序表和单链表两种方法表示,分别用两个程序来完成。(文件夹:顺序表逆置、单链表逆置) 2.已知由不具有头结点的单链表表示的线性表中,含有三类字符的数据元素(字母、数字和其他字符),试编写算法构造三个以循环链表表示的线性表,使每个表中只含有同一类的字符,且利用原表中的结点空间,头结点可另辟空间。(文件夹:分解单链表) 实验二栈和队列 一、实验目的 1.熟悉栈和队列的顺序和链式存储结构 2.掌握栈和队列的基本运算 3.能够利用栈和队列的基本运算完成栈和队列应用的运算 二、实验内容 1.设单链表中存放有n个字符,试编写算法,判断该字符串是否有中心对称的关系,例如xyzzyx是中心对称的字符串。(提示:将单链表中的一半字符先依次进栈,然后依次出栈与单链表中的另一半字符进行比较。)(文件夹:判字符串中心对称) 2.假设以数组sequ[m]存放循环队列的元素,同时设变量rear和quelen 分别指示循环队列中队尾元素的位置和内含元素的个数。编写实现该循环队列的入队和出队操作的算法。 提示:队空的条件:sq->quelen==0;队满的条件:sq->quelen==m。(文件夹:循环队列)实验三串 一、实验目的 1.熟悉串的顺序存储结构 2.掌握串的基本运算及应用 二、实验内容 1.串采用顺序存储结构,编写朴素模式匹配算法,查找在串中是否存在给定的子串。(文件夹:模式匹配) 2.若S是一个采用顺序结构存储的串,利用C的库函数strlen和strcpy(或strncpy)编写

课程设计任务书设计题目1:数码管显示数字钟设计

院(系)分管领导:教研室主任:指导教师: 2017年6月23日

目录 第1章引言 0 第2章电路原理 0 第3章程序设计 (1) 顶层模块设计 (2) 时钟分频模块设计 (2) 按键驱动模块设计 (2) 时钟计数模块设计 (3) 整点报时模块 (4) LED灯花样显示模块 (5) 数码管显示模块设计 (5) 第4章调试、测试分析及结果 (7)

调试 (7) 测试分析 (7) 结果 (9) 第5章小结 (10) 参考文献 (11) 附录电路图及程序 (11)

第1章引言 EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。 EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL 或者Verilog HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。 Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 此次课程设计我们运用QuartusⅡ这个软件,使用Verilog HDL语言进行编程。 数字钟是一种用数字电路技术实现时、分、秒计时的钟表。与机械钟相比具有更高的准确性和直观性,具有更长的使用寿命,已得到广泛的使用。数字钟的设计方法有许多种,例如可用中小规模集成电路组成电子钟,也可以利用专用的电子钟芯片配以显示电路及其所需要的外围电路组成电子钟,还可以利用单片机来实现电子钟等等。这些方法都各有其特点,其中利用单片机实现的电子钟具有编程灵活,以便于功能的扩展。 本次课程设计要求利用EDA技术,设计一个数码管显示数字钟的样品,数字钟要求具备以下功能: 1、具有时、分、秒,计数显示功能,以24小时循环计时; 2、具有清零,调节小时、分钟功能; 3、具有整点报时功能,整点报时的同时LED花样显示。 第2章电路原理 数码管显示数字钟设计,运用到8位数码管,要求其中6位数码管动态显示,分别显示时、分、秒的计数,同时对时间进行设置,数字钟的总体功能按照要求可以分为基本的数字时钟显示(具有时、分、秒,计数显示功能,以24小时循环计时)、手动校准(具有清零,调节小时、分钟功能)、整点报时、LED灯花样显示

数字水印技术 一、引言 随着互联网广泛普及的应用,各种各样的数据资源包括文本、图片、音频、视频等放在网络服务器上供用户访问。但是这种网络资源的幵放也带了许多弊端,比如一些用户非法下载、非法拷贝、恶意篡改等,因此数字媒体内容的安全和因特网上的侵权问题成为一个急需解决的问题。数字水印作为一项很有潜力的解决手段,正是在这种情况下应运而生。 数字水印(技术是将一些代表性的标识信息,一般需要经过某种适合的变换,变换后的秘密信息(即数字水印),通过某种方式嵌入数字载体(包括文档、音频、软件等)当中,但不影响原载体的使用价值,也不容易被人的知觉系统(如视觉或听觉系统)觉察或注意到。通过这些隐藏在载体中的信息,可以达到确认内容创建者、购买者、传送隐秘信息或者判断载体是否被篡改等目的。在发生产权和内容纠纷时,通过相应的算法可以提取该早已潜入的数字水印,从而验证版权的归属和内容的真伪。 二.算法原理 2.1、灰度图像水印 2.1.1基本原理 处理灰度图像数字水印,采用了LSB(最低有效位)、DCT变换域、DWT变换域三种算法来处理数字水印。在此过程中,处理水印首先将其预处理转化为二值图像,简化算法。 (1)LSB算法原理:最低有效位算法(Least Sig nificant Bit , LSB)是很常见的空间域信息隐藏算法, 该算法就是通过改变图像像素最不重要位来达到嵌入隐秘信息的效果, 该方法隐藏的信息在人的肉眼不能发现的情况下, 其嵌入方法简单、隐藏信息量大、提取方法简单等而获得广泛应用。LSB 信息嵌入过程如下: S′=S+f S ,M 其中,S 和S′分别代表载体信息和嵌入秘密信息后的载密信息;M为待嵌入的秘密信息, 而隐写分析则是从S′中检测出M以至提取M 。 (2)DCT算法原理:DCT 变换在图像压缩中有很多应用,它是JPEG,MPEG 等数据

EDA技术的认识和体会 摘要:本学期我对EDA技术进行了学习,通过学习,我掌握了部分EDA技术的知识。本学期对 EDA 技术的学习为我的专业知识学习打开了一个全新的窗口——微电子技术领域。对EDA 技术,我更是有了全新的认识。微电子技术的进步主要表现在大规模集成电路加工技术即半导体工艺技术的发展上,使得表征半导体工艺水平的线宽已经达到了纳米级。所以,集成电路设计正在不断地向超大规模、极低功耗和超高速的方向发展。而现代电子设计技术的核心已日趋转向基于计算机的电子设计自动化技术,即EDA 技术。 EDA技术的特点和优势 技术就是依赖功能强大的计算机,在EDA 工具软件平台上,对以硬件描述语言 HDL 为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。EDA 技术使得设计者的工作仅限于利用软件的方式,即利用硬件描述语言和EDA 软件来完成对系统硬件功能的实现,这是电子设计技术的一个巨大进步。 EDA 技术在进入21 世纪后,得到了更大的发展。嵌入式处理器软核的成熟,使得SOPC 步入大规模应用阶段。电子技术领域全方位融入EDA 技术,除了日益成熟的数字技术外,传统的电路系统设计建模理念发生了重大的变化。同时,EDA 使得电子领域各学科的界限更加模糊,更加互为包容。这些都利于设计人员利用 EDA 技术进行电子系统设计,如全定制或半定制ASIC 设计,FPGA/CPLD 开发应用和印制电路板。从 EDA 技术的特点不难看出,相比于传统的数字电子系统或 IC 设计,EDA 技术拥有独特的优势。在传统的数字电子系统或 IC 设计中,手工设计占了较大的比例。因此,也存在很多缺点。例如:复杂电路的设计、调试十分困难;由于无法进行硬件系统仿真,如果某一过程存在错误,查找和修改十分不便;设计过程中产生大量文档,不易管理;可移植性差等。相比之下,EDA 技术有很大不同。它运用HDL 对数字系统进行抽象的行为与功能描述到具体的内部线路结构描述,从而可以在电子设计的各个阶段、各个层次进行计算机模拟验证,保证设计过程的正确性,可以大大降低设计成本,缩短设计周期。由于有各类库的支持,能够完成各种自动设计过程。它极大地简化了设计文档的管理,逻辑设计仿真测试技术也日益强大。 VHDL 在现在的EDA 设计中使用最多,也拥有几乎所有主流EDA 工具的支持。 EDA工具 EDA工具在EDA技术应用中占据极其重要的位置,EDA的核心是利用计算机完成电子设计全过程自动化,因此,基于计算机环境的EDA软件的支持是必不可少的。EDA工具大致可以分为如下5个模块:设计输入编辑器;仿真器;HDL综合器;适配器(或布局布线器);下载器。 VHDL语言基础

学校:北京联合大学 系别:信息管理系 姓名:孙超 学号:2013110444006 《餐饮业信息管理系统的开发》 1、本项目的需求分析 随着今年来中国餐饮行业的日益火爆,在强烈的行业竞争中,一个高效的餐饮信息管理系统的应用,无疑是至关重要的。高效,便捷的管理系统,不仅仅极大的方便了食客的就餐,同时对于餐饮公司的各项信息管理有着很大的帮助,同时,我们的餐饮信息管理系统还能帮助餐厅降低错误率,扩大营业范围,增加知名度等。 为了使得系统在操作的过程中,更加便捷,具有针对性,本次系统设计主要分为:员工登陆操作信息系统,以及店主操作管理信息系统。不同的设计从而达到不同的功能,实现信息的有效传达与管理。 第一:在员工使用本餐饮信息管理系统应可以实现以下功能: 1.添加修改查询客户会员信息(修改客户信息需客户确认) 2.查询菜单 3.添加查询预定信息,为老顾客打折 4.客户可以在自己的会员账户里充值 5.顾客可以用现金买单也可以从会员账户里扣取 第二:管理员使用本餐饮信息管理系统应可以实现以下功能: 1.添加修改查询客户会员信息(修改客户信息需客户确认) 2.添加修改查询菜单信息,最好能看到菜品图片 3.添加查询预定信息,为老顾客打折 4.客户可以在自己的会员账户里充值 5.顾客可以用现金买单也可以从会员账户里扣取 6.设定具体的打折方法 7.添加职员信息,权限也可以定为管理员。 8.可以查询使用者的现金收款金额。 二、餐饮业管理数据库管理系统的E-R模型(概念结构设计) 1.用户(员工)的信息:

编号、密码、类型、姓名、电话、收款金额 2.客户信息: 用户编号、客户编号、姓名、电话、密码、开卡时间、卡内余额 3.食谱: 类型、名称、价格、配料、照片 4.预定: 用户编号、日期、预定时间、客户姓名、类型、预定食谱、桌号5桌台管理: 桌号、使用情况、 6.点餐管理: 用户编号、类型、菜品、数量、价格、照片 7.盈利管理: 日期、日支出金额、店内收入、外卖收入、盈利额度 各对象之间的联系图: 用户E-R图 主要存储一些用户信息,如用户的账号、密码和类型地点等等,主要用于用户登录,添加客户和添加预定时会使用到用户信息。

课程设计说明书 课程:EDA技术基础 题目:数字钟的设计 闹钟与整点报时模块 学生姓名:XXX 学号201265110204 班级 :1203班 专业:电子信息与科学 指导教师:XXX 2014年12月20日 长沙理工大学课程设计任务书 物理与电子科学学院电子信息与科学专业1203班姓名王玲课程名称EDA技术基础 题目数字钟的设计

长沙理工大学课程设计成绩评定表

目录 1数字钟设计闹钟模块基本任务要求4 2设计思想4 3简述闹钟模块的输入与输出5 4分进程描述6 5仿真结果与分析7 6简述数字钟的设计总成果10 7总结11 参考文献13 代码附件13

基本任务要求:运用QuartusⅡ13.1软件平台,用VHDL语言描述并设计的闹钟模块满足可调闹钟时间,当时钟时间到达闹钟时间后会响闹铃,(由于实验室权限问题会以FPGA开发板上12个LED灯交替发光来表现);整点报时过程表现为整点的前十秒内响铃,(以FPGA开发板上一个LED灯交替发光来实现)。 设计思想:闹钟模块要以分频模块、计数器模块和译码显示模块为基础,将闹钟模块分为三个进程,一个进程用来实现调闹钟,一个进程来实现闹响闹钟(即实现LED灯交替发光),另一个进程来是实现整点报时。 (上面截图为数字钟整体编译后的RTL电路的闹钟模块) 简述闹钟模块图的输入与输出:上图中的输入粗黑实线为计数器模块输出的小时、分钟的高低位和秒钟的高位(都用四位的二进制表示);输出的粗黑实线为定的闹钟时间(包括小时和分钟),将送到译码显示模块显示闹钟时间,闹钟时间与时钟都在FPGA上的数码管显示,用二选一实现交替显示。clk和clk1都是经过分频器分出的不同频率的信号分别用于整点报时的闪灯脉冲与闹钟调时、闹响的闪灯脉冲。

单元一教学设计 教学内容: 单元一EDA技术 学习任务1 EDA技术 一、认识课程 二、认识EDA技术 三、认识EDA技术的基本特征 学习任务2 可编程逻辑器件芯片 一、认识可编程逻辑器件 二、CPLD基本结构 三、FPGA基本结构 四、Altera公司的可编程逻辑器件汇报总结 评价与考核

教学设计与建议 教学设计:通过学习和查阅资料了解EDA技术,了解EDA技术的基本特征,并熟悉可编程逻辑器件的种类。了解CPLD和FPGA基本结构,熟悉 Altera公司的可编程逻辑器件。 教学建议:建议学生查找EDA技术发展与可编程逻辑器件应用相关资料,进行总结制作PPT,并进行汇报。 知识目标: 1.了解EDA技术 2.了解EDA技术的基本特征 3.了解可编程逻辑器件的种类 4.了解CPLD基本结构 5.了解FPGA基本结构 6.了解Altera公司的可编程逻辑器件 教学重点及难点: 教学重点:可编程逻辑器件种类 教学难点:熟悉Altera公司的可编程逻辑器件 教学载体与资源: 教学资源:教材、PPT、实训室、多媒体设备。 教学方法建议: 讲授与讨论相结合,查阅资料总结汇报。 教学过程: 1.下达任务和要求 2. 教师带领学生共同解析任务 3.学生展开讨论

4.学生查阅资料 5. 总结汇报 考核评价: 1.根据知识掌握情况评价 2.根据资料查找能力和小组汇报情况评价 教学板书: 任务1:EDA技术 认识课程 1.EDA技术是什么? 2.为什么学习EDA技术? 3.EDA技术学什么? 4.EDA技术怎么学? 相关知识 1.认识EDA技术 EDA(Electronic Design Automation,电子设计自动化)技术是帮助电子设计工程师在计算机上完成电路的功能设计、逻辑设计、性能分析、时序测试直至PCB(印制电路板)的自动设计等。 2.认识EDA技术的基本特征 (1)“自顶向下”设计方法 (2)硬件描述语言 (3)逻辑综合和优化 (4)开放性和标准化 (5)库的引入

题目:数据结构上机报告学院:电子工程学院 专业:信息对抗技术 学生姓名:甘佳霖 学号:14020310092

西安电子科技大学 数据结构课程实验报告实验名称线性表 电子工程学院 1402031 班Array姓名甘佳霖学号 14020310092 同作者 实验日期 2017 年 3 月 18 日

实验一线性表 一、实验目的 1.熟悉线性表的顺序和链式存储结构 2.掌握线性表的基本运算 3.能够利用线性表的基本运算完成线性表应用的运算 二、实验要求 1.设有一个线性表E={e1, e2, … , e n-1, e n},设计一个算法,将线性表逆置,即使元素排列次序颠倒过来,成为逆线性表E’={ e n, e n-1 , … , e2 , e1 },要求逆线性表占用原线性表空间,并且用顺序表和单链表两种方法表示,分别用两个程序来完成。 2.已知由不具有头结点的单链表表示的线性表中,含有三类字符的数据元素(字母、数字和其他字符),试编写算法构造三个以循环链表表示的线性表,使每个表中只含有同一类的字符,且利用原表中的结点空间,头结点可另辟空间。 三、设计思路 1.顺序表做逆置操作时将对应的首尾元素位置交换,单链表的指针end指向链表的末尾,指针start指向链表头结点,指针s用来找到指向end节点的节点,将指向链表末尾和头结点的存储内容交换,然后头结点指针指向下一节点,s指针从start节点开始遍历寻找指向end 指针的节点,并将end指针赋值为s指针,就完成了单链表的逆置,可以看出单链表和顺序表都可以完成线性表的逆置。 2.分解单链表的实现思路是首先新建3个循环链表,然后顺序遍历单链表,ASCII码判断链表中的元素属于哪一类元素,然后将这个元素添加到对应的循环链表中,从而实现分解单链表的功能。 四、运行结果 1.单链表逆置:

东北石油大学EDA技术实践课程设计 课程EDA技术实践课程设计 题目24进制计数器 院系电气信息工程学院电气系 专业班级 学生姓名 学生学号 指导教师 年7月25日

EDA技术实践课程设计任务书 课程EDA技术实践课程设计 题目24进制计数器 专业电气工程及其自动化姓名学号 主要内容: 1.熟练掌握Quartus II软件的使用。 2.熟练掌握在QuartusII平台上用原理图或者VHDL语言进行电路设计的方法。 3.学会用例化语句对EDA电路设计中顶层电路进行描述。 基本要求: 1.熟悉仿真开发软件Quartus II的使用; 2.根据功能要求,用原理图或文本输入方式完成设计; 3.用Quartus II做波形仿真调试; 4.下载至EDA试验仪调试设计。 主要参考资料: [1]潘松,黄继业. 《EDA技术实用教程》[M].北京:科学出版社,2002. [2]卢杰,赖毅. 《VHDL与数字电路设计》[M].北京:科学出版社,2001. [3]张明. 《Verilog HDL实用教程》[M].成都:电子科技大学出版社,1999. [4]郑家龙,王小海,章安元.《集成电子技术基础教程》[M].北京:高等教育出版社,2002. [5]王金明,杨吉斌. 《数字系统设计与Verilog HDL》[M].北京:电子工业出版社,2002. 完成期限 指导教师 专业负责人 年7 月18日

目录 1设计 (1) 2方案选择与电路原理图的设计 (1) 2.124进制计数器的基本原理 (1) 2.2设计流程图 (1) 2.3原理图 (1) 374LS161元件说明 (2) 3.1 简介 (2) 3.274ls161管脚图与介绍 (2) 3.374ls161功能表 (3) 3.474ls161主要特点 (3) 4设计过程 (4) 4.1新文件的建立 (4) 4.2宏功能模块的使用 (5) 4.3普通元件的添加 (8) 4.4 电路连接 (9) 5功能仿真 (9) 6出现的问题及调试方法 (11) 7总结 (11) 参考文献 (12) 附录VHDL语言编写的该程序清单 (13)

模式识别大作业 班级 021252 姓名 谭红光 学号 02125128 1.线性投影与Fisher 准则函数 各类在d 维特征空间里的样本均值向量: ∑∈= i k X x k i i x n M 1 ,2,1=i (1) 通过变换w 映射到一维特征空间后,各类的平均值为: ∑∈= i k Y y k i i y n m 1,2,1=i (2) 映射后,各类样本“类内离散度”定义为: 22 ()k i i k i y Y S y m ∈= -∑,2,1=i (3) 显然,我们希望在映射之后,两类的平均值之间的距离越大越好,而各类的样本类内离 散度越小越好。因此,定义Fisher 准则函数: 2 1222 12||()F m m J w s s -= + (4) 使F J 最大的解* w 就是最佳解向量,也就是Fisher 的线性判别式. 从 )(w J F 的表达式可知,它并非w 的显函数,必须进一步变换。 已知: ∑∈= i k Y y k i i y n m 1,2,1=i , 依次代入上两式,有: i T X x k i T k X x T i i M w x n w x w n m i k i k === ∑∑∈∈)1 (1 ,2,1=i (5) 所以:2 21221221||)(||||||||M M w M w M w m m T T T -=-=- w S w w M M M M w b T T T =--=))((2121 (6)

其中:T b M M M M S ))((2121--= (7) b S 是原d 维特征空间里的样本类内离散度矩阵,表示两类均值向量之间的离散度大 小,因此,b S 越大越容易区分。 将(4.5-6) i T i M w m =和(4.5-2) ∑∈= i k X x k i i x n M 1代入(4.5-4)2i S 式中: ∑∈-= i k X x i T k T i M w x w S 22)( ∑∈?--? =i k X x T i k i k T w M x M x w ))(( w S w i T = (8) 其中:T i X x k i k i M x M x S i k ))((--= ∑=,2,1=i (9) 因此:w S w w S S w S S w T T =+=+)(212221 (10) 显然: 21S S S w += (11) w S 称为原d 维特征空间里,样本“类内离散度”矩阵。 w S 是样本“类内总离散度”矩阵。 为了便于分类,显然 i S 越小越好,也就是 w S 越小越好。

EDA课程学习心得 这学期的后半期,我们开了EDA技术这门课程。EDA的中文解释是电子设计自动化,这门课程主要是用于对现代高新电子产品的设计,EDA在硬件方面融合了大规模集成电路技术,是一款综合性很强的工具。 这门课程的学习在教学中应该以实践为主,我们每周有两节课,一节是理论课学习,一节是实践课。刚开始上理论课程的时候,主要是对该软件的使用做介绍,而在实践课程上,我们应该对软件进行运用,但是,有很多的同学却没有干与课程相关的事,只有一部分的同学在练习。开始的时候,对软件很陌生,都是几个同学在一起研究,并且询问老师,才慢慢的掌握了使用方法。在后面的理论学习中,老师主要是讲解编程的一些语法,并且只讲了一些常用的,像信号量,变量,还有PROCESS语句等,这些是编程中常用的一些知识。在实践课上,主要是以实验指导书为主,根据指导书上的内容进行编程,画图仿真来对EDA技术的运用有更深入的理解。在每周一节理论课的学习情况下,很多的时间都是很珍贵的,学习理论的时间就那么一点,那么,肯定就不可能学习的很全面,老师主要是讲方法,更多的是要我们自己努力。这本教材还很不错,讲解的很详细,让初学者也能理解。然后实践课程是可以在课后也能练习,课上发现问题就能及时的询问老师,但是,课后就只能询问同学,或者是将问题留到课堂上再问老师。 这门课程学完最大的感触就是学习的时间太短了,这门课程听老师说对我们的以后工作是有很大的帮助的,但是我们却只学习了半个学期,只用了32个课时就结束了,这肯定是不够的。EDA技术可以完成各种自动设计过程,是目前最为瞩目的一项技术,它有强大的逻辑设计仿真测试技术。它的仿真测试技术只要通过计算机,就能对所设计的电子系统从各种不同层次的系统性能特点完成一系列准确的测试与仿真操作,在完成实际系统的安装后,还能对系统上的目标器件进行所谓的边界扫描测试。这一切都极大的提高了大规模的系统电子设计的自动化程度。现在的很多设计工作都需要先进行计算机仿真,如果没有错误,在运用到实际的硬件中,这不仅能提高设计速度,还能减少因为设计失误而造成的原料浪费。学好一门仿真软件对于我们本科学生是必不可少的,因为以后毕业了如果从事设计方向的工作,那必然要求我们有这样的一门技术。 以下是我在这门课程的学习过程中总结的几点建议,希望老师能够耐心的看

西电排队论大作业 HEN system office room 【HEN16H-HENS2AHENS8Q8-HENH1688】

西安电子科技大学 (2016年度) 随机过程与排队论 班级: XXXXXXX 姓名: XXX XXX 学号: XXXXXXXXXX XXXXXXXXXXX 一步转移概率矩阵收敛快慢的影响因素 作者姓名:XXX XXX 指导老师姓名:XXX (西安电子科技大学计算机学院,陕西西安) 摘要:根据课程教材《排队现象的建模、解析与模拟【西安电子科技大学出版 社曾勇版】》,第[马尔可夫过程]中,马尔可夫过程链n时刻的k步转移概率结 果,当k=1时,得到一步转移概率。进而得到一步转移概率矩阵P(1)。为研究 此一步转移概率矩阵(下称一步矩阵)的收敛特性以及影响其收敛快慢的因素,使 用MATLAB实验工具进行仿真,先从特殊矩阵开始做起,发现规律,然后向普通矩 阵进行拓展猜想,并根据算术理论分析进行论证,最终得出一步矩阵收敛快慢的影 响因素。 关键词:一步转移概率矩阵 MATLAB 仿真猜想 一、问题概述 我们讨论时一步矩阵的特性应从以下两方面来分析: (1)矩阵P(n)在满足什么条件时具有收敛特性; 对于矩阵P(n),当P(n)=P(n+1)时,我们说此矩阵 具有收敛特性,简称矩阵 P(n)收敛。 (2)若一个一步矩阵具有收敛特性,那么其收敛速度与什么有关

首先,我们需要明确什么是一步矩阵收敛: 对于一般的一步矩阵P 、矩阵An+1、矩阵An,若有: An+1=AnP=An 那么称该一步转移矩阵可收敛。 二、仿真实验 1、仿真环境 本次采用的是MATLAB仿真实验软件进行仿真实验 2、结果与分析 【1】、特殊矩阵:单位矩阵与类单位矩阵 从图(1)和图(2)可以看出,单位矩阵不具有收敛特性,类单位矩阵并非单位矩阵但是经过n次后也变为单位矩阵,所以此矩阵也不具有收敛特性。此类矩阵也易证明其不具有收敛性。 图(1)单位矩阵图(2):类单位 矩阵 【2】、一般单位矩阵 图(3):一般一步矩阵Ⅰ 图(4):一般一步矩阵 从图(3)和()可以看出他们分别在18次和4次后收敛到一个稳定的值 3、根据实验的猜想 根据在单位矩阵和一般单位矩阵和一般一步矩阵中得到的结果,可以对得出如下结论:类单位矩阵、单位矩阵是不具有收敛性的,而一般的一步矩阵是有收敛性的,而且收敛速率有快有慢。 对于上面结论中的状况,我们首先观察如上四个矩阵,不难发现,在矩阵收敛的最终结果矩阵中,其每行和均为1,而且每列上的值均为相同值。最终概率分布结果也是矩阵收敛后的一行。 所以根据上述的结果及分析做出如下猜想: 每一列比较均匀的矩阵收敛速度较快;与类单位矩阵类似的矩阵收敛速度较慢。 在极限情况下,有如下情况:

E D A技术实践课程设计 --24进制计数器 -CAL-FENGHAI.-(YICAI)-Company One1

东北石油大学EDA技术实践课程设计 年 7月 25日

EDA技术实践课程设计任务书 课程 EDA技术实践课程设计 题目 24进制计数器 专业电气工程及其自动化姓名学号 主要内容: 1.熟练掌握Quartus II软件的使用。 2.熟练掌握在QuartusII平台上用原理图或者VHDL语言进行电路设计的方法。 3.学会用例化语句对EDA电路设计中顶层电路进行描述。 基本要求: 1.熟悉仿真开发软件Quartus II的使用; 2.根据功能要求,用原理图或文本输入方式完成设计; 3.用Quartus II做波形仿真调试; 4.下载至EDA试验仪调试设计。 主要参考资料: [1]潘松,黄继业. 《EDA技术实用教程》[M].北京:科学出版社,2002. [2]卢杰,赖毅. 《VHDL与数字电路设计》[M].北京:科学出版社,2001. [3]张明. 《Verilog HDL实用教程》[M].成都:电子科技大学出版社,1999. [4]郑家龙,王小海,章安元.《集成电子技术基础教程》[M].北京:高等教育出版社,2002. [5]王金明,杨吉斌. 《数字系统设计与Verilog HDL》[M].北京:电子工业出版社,2002. 完成期限 指导教师 专业负责人 年 7 月18日

目录 1设计 (1) 2方案选择与电路原理图的设计 (1) 2.124进制计数器的基本原理 (1) 2.2设计流程图 (1) 2.3原理图 (1) 374LS161元件说明 (2) 3.1 简介 (2) 3.274ls161管脚图与介绍 (2) 3.374ls161功能表 (3) 3.474ls161主要特点 (3) 4设计过程 (4) 4.1新文件的建立 (4) 4.2宏功能模块的使用 (5) 4.3普通元件的添加 (8) 4.4 电路连接 (9) 5功能仿真 (9) 6出现的问题及调试方法 (11) 7总结 (11) 参考文献 (12) 附录VHDL语言编写的该程序清单 (13)

第二章 2.25 已知线性时不变系统的差分方程为 若系统的输入序列x(x)={1,2,3,4,2,1}编写利用递推法计算系统零状态响应的MATLAB程序,并计算出结果。 代码及运行结果: >> A=[1,-0.5]; >> B=[1,0,2]; >> n=0:5; >> xn=[1,2,3,4,2,1]; >> zx=[0,0,0];zy=0; >> zi=filtic(B,A,zy,zx); >> yn=filter(B,A,xn,zi); >> figure(1) >> stem(n,yn,'.'); >> grid on;

2.28图所示系统是由四个子系统T1、T2、T3和T4组成的,分别用单位脉冲响应或差分方程描述为 T1: 其他 T2: 其他 T3: T4: 编写计算整个系统的单位脉冲响应h(n),0≤n≤99的MATLAB程序,并计算结果。 代码及结果如下: >> a=0.25;b=0.5;c=0.25; >> ys=0; >> xn=[1,zeros(1,99)]; >> B=[a,b,c]; >> A=1; >> xi=filtic(B,A,ys); >> yn1=filter(B,A,xn,xi); >> h1=[1,1/2,1/4,1/8,1/16,1/32]; >> h2=[1,1,1,1,1,1]; >> h3=conv(h1,h2); >> h31=[h3,zeros(1,89)]; >> yn2=yn1+h31; >> D=[1,1];C=[1,-0.9,0.81]; >> xi2=filtic(D,C,yn2,xi); >> xi2=filtic(D,C,ys); >> yn=filter(D,C,yn2,xi); >> n=0:99; >> figure(1) >> stem(n,yn,'.'); >> title('单位脉冲响应'); >> xlabel('n');ylabel('yn');

云南大学软件学院实验报告 课程:数据库原理与实用技术实验学期:任课教师: 专业:学号:姓名:成绩: 期末大作业:Electronic Ventor 数据库设计 一、实验目的 (1)掌握数据库设计的基本方法 (2)掌握各种数据库对象的设计方法 (3)熟练掌握DBA必须具备的技能 二、实验内容 1、根据项目的应用和项目的需求说明文档,进行详细的需求分析,给出需求分析的结果。 (1)客户可以在网站上注册,注册的客户要提供客户的姓名、电话、地址,以方便售后和联系,姓名即作为用户名,和密码一起用于注册和登录,客户编号可唯一识别用户,卡号可网上支付。其中地址、电话以方便联系和寄货; (2)网站管理员可以登记各种商品,供客户查询,订购。登记商品时要提供商品的名称、价格,商店中现有商品量,商品编号可唯一识别商品; (3)类别表示商品所属类别,类别编号可唯一识别类别,其中包含了,商品类别名称和制造厂商,可以对商品进行分类售卖; (4)客户可以在网上下订单,也可以到实体店购物,其在订单上所选择的支付方式不同(信用卡、借记卡、现金,现金代表实体店购物),网站管理员可以查看订单,并及时将订单的处理情况更新(比如货物已寄出的信息,订单状态:0:未处理,1:已处理,2:已发货);订单编号可唯一识别订单,订单中包含订单产生时间,订单状态,支付方式和支付总额; (5)实体商店有自己的店名,卖多种商品,每个商店都有固定的地址,顾客可以到店中买商品,(注:在实体店中购买商品的顾客一律将顾客名默认为佚名),当商店中的库存量小于10时会有提醒到仓库中拿货; (6)配送单中包含查询号可唯一识别配送单,配送人,联系方式; (7)仓库中仓库编号可唯一识别仓库,其中每个仓库都有区号,代表其地址。 (8)各实体间关系 1)一个客户可以购买多种商品,一种商品可以被多个客户购买; 2)一个商品属于且仅属于一种类别,一种类别的商品可以包含多个商品或没有; 3)一种商品放在多个商店中销售,一个商店至少销售一种或销售多种商品; 4)一个订单对应一个客户,一个客户对应多个订单; 5)一个订单对应至少有一件商品或多件,一个商品对应多个订单; 6)一个订单可以有一个商品配送单 7)一个仓库可以存放多种商品,一种商品可以存放在一个仓库;

课程设计任务书 设计题目1:数码管显示数字钟设计 学生姓名 课程名称EDA技术课程设计专业班级 地点起止时间2017年6月19日— 6月23日 设 计 内 容 硬件设计及样品制作 设计参数1、具有时、分、秒,计数显示功能,以24小时循环计时; 2、具有清零,调节小时、分钟功能; 3、具有整点报时功能,整点报时的同时LED花样显示。 设计进度1.2017年6月19日—20日查阅资料,确定设计方案 2.2017年6月21日—22日程序设计和硬件调试 3.2017年6月23日撰写课程设计报告,答辩 设计成果1. 设计说明书一份(不少于2000字); 2. 样品一套。 参考资料1.周润景等,基于Quartus II的FPGA/CPLD数字系统设计实例,电子工业 出版社,2010 2.夏宇闻,Verilog数字系统设计教程(第二版),北京航空航天大学出版 社,2014 说明1.本表应在每次实施前由指导教师填写一式2份,审批后所在系(部)和指导教师各留1份。2.多名学生共用一题的,在设计内容、参数、要求等方面应有所区别。3.若填写内容较多可另纸附后。 院(系)分管领导:教研室主任:指导教师: 2017年 6月 23日

EDA技术课程设计报告 目录 第1章引言 (1) 第2章电路原理 (2) 第3章程序设计 (3) 3.1 顶层模块设计 (3) 3.2 时钟分频模块设计 (4) 3.3 按键驱动模块设计 (4) 3.4 时钟计数模块设计 (4) 3.5 整点报时模块 (5) 3.6 LED灯花样显示模块 (7) 3.7 数码管显示模块设计 (7) 第4章调试、测试分析及结果 (10) 4.1 调试 (10) 4.2 测试分析 (10) 4.3 结果 (12) 第5章小结 (13) 参考文献 (14) 附录电路图及程序 (15)