第五节、电子原器件原理

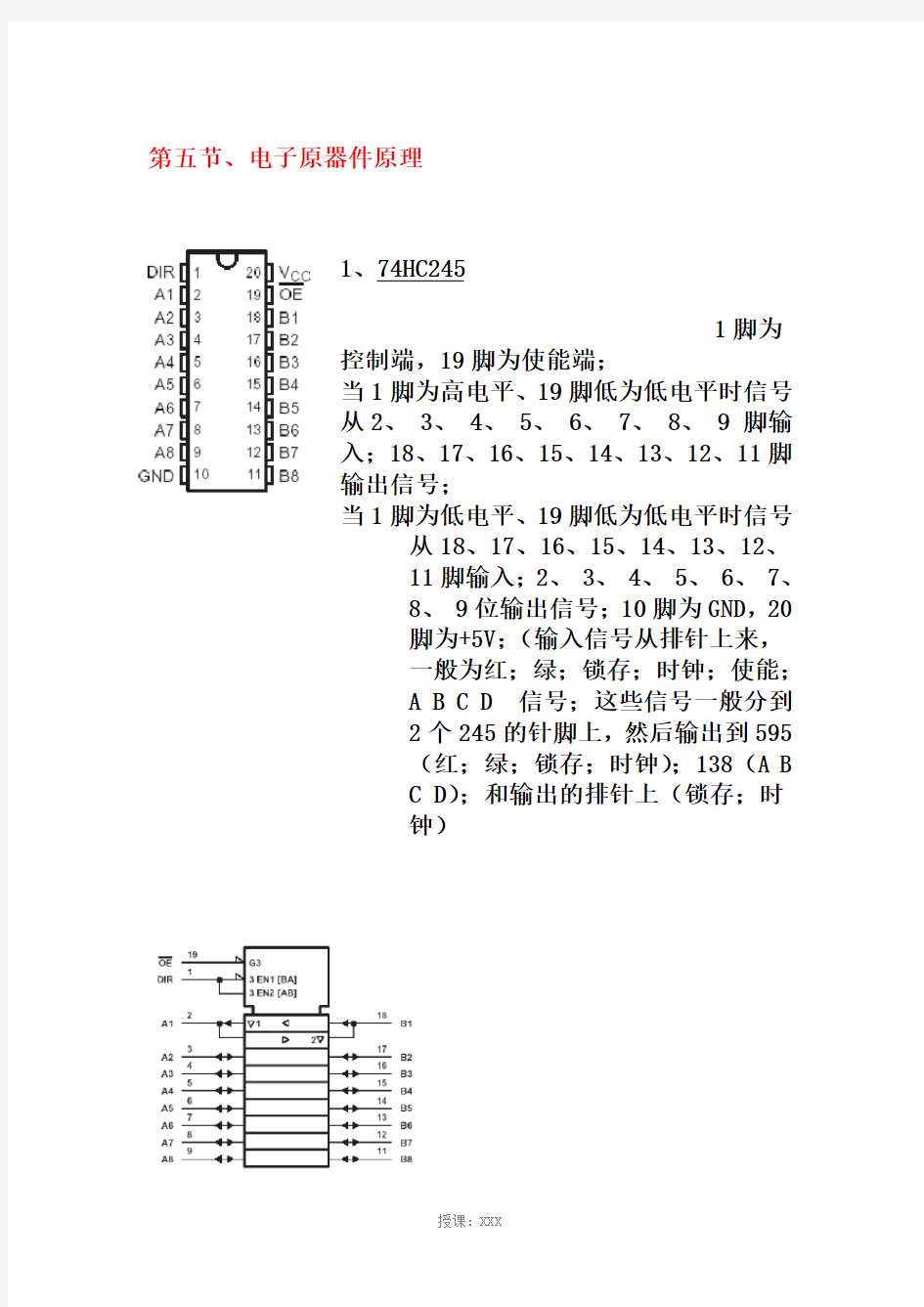

1、74HC245

1脚为

控制端,19脚为使能端;

当1脚为高电平、19脚低为低电平时信号

从2、 3、 4、 5、 6、 7、 8、 9 脚输

入;18、17、16、15、14、13、12、11脚

输出信号;

当1脚为低电平、19脚低为低电平时信号

从18、17、16、15、14、13、12、

11脚输入;2、 3、 4、 5、 6、 7、

8、 9位输出信号;10脚为GND,20

脚为+5V;(输入信号从排针上来,

一般为红;绿;锁存;时钟;使能;

A B C D 信号;这些信号一般分到

2个245的针脚上,然后输出到595

(红;绿;锁存;时钟);138(A B

C D);和输出的排针上(锁存;时

钟)

2、74HC138

3线—8线译码器

HC138有三个地址输入(A0-A2),三个选通输入(STA,-STB,-STC)和八个输出(-Y0 -- -Y7)。当STA为高电平,-STB 和-STC为低电平时器件被选通,A0-A2K可确点-Y0 -- -Y7中的一个以低电平呈现,对于STA,-STB,-STC的其它任何组合,-Y0 -- -Y7均为高电平。

A0---A1地址输入端 STA---选通端 -STB.-STC--选通端(低电平有效)-Y0--- -Y1输出端(低电平有效) GND---地VCC---电源

A0—A2一般为A:B:C信号 Y0—

Y7信号输出端,输出到4953的

2,4脚上;有时使能信号也245

到138(第5脚)上,此信号又

从138上输出到排针。

3、74HC595

8位移位寄存器(串行输入,3S并行锁存输出)

HC595内含8位串入,串/并出移位寄存器和8位三态输出锁存器。寄存器和锁存器分别有各自的时钟输入(CPsr和CPla)。当CPsr从低到高电平跳变时,串行输入数据(DS)移入寄存器。当CPla从低到高电平跳变时,寄存器的数据置入锁存器。清除端(-CR)的低电平仅对寄存器复位(Q7S 为低电平)。而对锁存器无影响。当输出允许控制(-EN)为高电平时,并行输出(Q0—Q7)为高阻态,而串行输出(Q7S)不受影响。

CP1A---锁存器时钟输入端CPSR---寄存器时钟输入端-CR---清除端(低电平有效) DS---串行数据输入端

-EN---输出允许控制端(低电平有效) Q0、Q7---并行数据输出端 Q7s---串行数据输出端 VCC---电源 GND---地

14脚为信号输入端,此信号从245的针脚上输入;Q0----Q7信号输出到模块针脚(红绿信号); 13脚为使能一般接地(低电平有效);12脚为时钟,11脚为锁存,这俩脚信号都从245输入;单元板上的公共信号全是相通的.(使能,锁存.时钟);第10脚为清零信号一般接5V(高电

平有效)

第9脚为信号输出脚,输出到下一个595的第14脚;(单元板上的最后一个595的第9脚把红绿信号输出到排针上)

4、0724C4953

74HC4953中的1、3管脚为VCC—电源,2、4管脚为数据输入端,5、6和7、8管脚是数据输出端。

5、MBI5026GF(或62726)

16位移位锁存器

第1脚GND,电源地。

第24脚VCC,电源正极

第2脚DATA,串行数据输入

第3脚CLK,时钟输入

第4脚STB,锁存输入

第23脚输出电流调整端,接电阻调整

第22脚DOUT,串行数据输出

第21脚EN,使能输入

6、74HC04

六反相器 A--数据输入 Y--数据输出端VCC--电源 GND-地

7、74HC145

8、74HC373

12、32K*8

13、512K*8

AT89C2051

14、74HC154